Professional Documents

Culture Documents

Sistemas Digitales Básicos Trabajo Colaborativo-Proyecto Final

Uploaded by

Nelson QuintanaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sistemas Digitales Básicos Trabajo Colaborativo-Proyecto Final

Uploaded by

Nelson QuintanaCopyright:

Available Formats

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD ESCUELA DE CIENCIAS BSICAS, TECNOLOGIAS E INGENIERA SISTEMAS DIGITALES BSICOS TRABAJO COLABORATIVO-PROYECTO

FINAL

PRESENTA LUIS MANUEL OLIVAR DIAZ CODIGO : 73106391 NELSON QUINTANA ARELLANO CODIGO: 73.076.302

TUTOR JHON LEONARDO SUACHA

GRUPO 201417_16

CEAD SIMN BOLVAR-CARTAGENA DE INDIAS

12 DE DICIEMBRE DE 2012

INTRODUCCIN

En este diseo de circuito lgico, se nos convierte en la base para que nos familiaricemos con el diseo de dispositivos electrnicos, que nos van a permitir en un futuro dar soluciones a necesidades sentidas en nuestro diario vivir. Asi que la ampliacin de ideas renovadas, actualizadas y la bsqueda de senderos vlidos a la hora de tomar decisiones referentes al diseo e implementacin de circuitos electrnicos digitales es grandsima. La temtica a trabajar est en el contenido del mdulo de Sistemas Digitales Bsicos, el cual contiene informacin relevante orientada al diseo e implementacin de circuitos lgicos. En la construccin de estos dos circuitos nos profundizara en temas como operaciones binarias, lgica combinacional, familias de integrados digitales existente, en fin el conocimiento ser extenso y porque no decirlo as, maravilloso.

Actividades a Realizar:

Realizar el diseo e implementacin de los circuitos digitales de los problemas planteados. El grupo colaborativo debe elaborar un documento que contenga lo siguiente: Tabla de Verdad Simplificacin Circuito lgico Diagrama de Conexin Demostracin del funcionamiento del circuito Listado de dispositivos electrnicos utilizadas en el diseo e implementacin de los circuitos electrnicos Especificaciones tcnicas de cada uno de los dispositivos electrnicos utilizados.

OBJETIVO GENERAL Elaborar el diseo de circuitos lgicos mediante problemas planteados, indicando su tabla de verdad, su simplificacin, su circuito lgico, su diagramada de conexin y demostrar su funcionamiento.

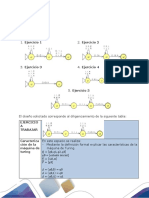

DESARROLLO Problema # 1 En una planta industrial se realiza el proceso de calentamiento de cuatro tanques denominados T1, T2, T3 y T4. Para detectar si el lquido de los tanques T1 y T2 sobrepasa el nivel predeterminado, el sistema cuenta con sensores de nivel de lquido. Existen sensores de temperatura en los tanques T3 y T4, los cuales indican cuando la temperatura en los mismos est por debajo del lmite permitido. En el sensor de nivel de lquido las salidas T1 y T2 son BAJAS, cuando el nivel est dentro del rango permitido y ALTAS cuando el nivel es demasiado alto. Por otro lado, las salidas de los tanques T3 y T4 del sensor de temperatura son BAJAS, cuando est dentro del rango establecido, y ALTAS cuando la El grupo colaborativo debe realizar el diseo, implementacin y puesta en marcha el circuito lgico que cumpla con lo siguiente: El circuito lgico debe detectar cuando el nivel de los tanques T1 o T2 es muy alto, y al mismo tiempo que la temperatura en el tanque T3 o T4 es muy baja.

TABLA DE VERDAD T1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 T2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 T3 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 T4 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 0 0 0 0 0 1 1 1 0 1 1 1 0 1 1 1

Mapas de Karnaugh

00 T3T4 01 11 10

T1T2 00 01 0 0 0 1 0 1 0 1

11 0 1 1 1

10 0 1 1 1

La expresin lgica que rige es: SALIDA=T2T4+T1T4+T2T3+T1T3=T4(T1+T2)+T3(T1+T2)=(T1+T2)(T4+T3)

PLANTA INDUSTRIAL QUE REALIZA EL PROCESO DE CALENTAMIENTO DE CUATRO TANQUES DENOMINADOS T1, T2, T3 Y T4.

Problema # 2 La figura muestra el cruce de una calle principal, existe un cruce alterno. Los carriles X y Y cuentan con sensores de deteccin de vehculos (va principal) y en los carriles X y Z (cruce alterno). El sensor entrega salidas BAJAS, cuando no pasa ningn vehculo. El semforo debe cumplir la siguiente lgica: Si los carriles X y Y estn ocupados, el semforo E-O estar en verde. Si X o Y estn ocupados pero W y Z no lo estn, el semforo E-O estar en verde. Si X y Y estn ocupados pero W y Z no lo estn, el semforo N-S estar en luz verde. Si X o Y estn ocupados en tanto que W y Z no lo estn el semforo N-S tambin estar en verde. Cuando no hayan vehculos transitando, el semforo E-O estar en verde.

El grupo colaborativo debe realizar el diseo, implementacin y puesta en marcha el circuito lgico para controlar el semforo.

Para el desarrollo de los problemas tengan en cuenta lo siguiente: Una salida ALTA corresponde a un uno 1 lgico, una salida BAJA corresponde a un cero 0 lgico. La implementacin de los circuitos lgicos la pueden desarrollar mediante simulador o realizando el montaje en protoboard de los mismos, los importante es que se demuestre el ptimo funcionamiento de los mismo.

De acuerdo con las condiciones del problema se plantea la siguiente tabla de verdad

SENSORES SEMFORO EO X Y Z W VERDE ROJO 0 0 0 0 1 0 0 0 0 1 1 0 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 1 0 0 1 0 1 1 0 0 1 1 0 0 1 0 1 1 1 1 0 1 0 0 0 0 1 1 0 0 1 0 1 1 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 0 1 1 1 0 1 1 0 1 1 1 0 0 1 1 1 1 1 1 0

SEMFORO NS VERDE ROJO 0 1 0 1 1 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1

De acuerdo con la tabla, se plantea el mapa de Karnaugh. Se plantea solo para las luces verdes, ya que se entiende que la luz roja es la negacin de la luz verde. As VERDE EO XY 00 01 1 1 1 1 0 1 0 0 11 0 1 1 0 10 0 0 0 0

Y VERDE NS XY 00 01 0 0 0 0 0 0 1 0

00 ZW 01 11 10

00 ZW 01 11 10

11 0 0 0 0

10 1 0 0 1

La expresin a partir de la tabla es VERDE EO= XZ+YW

Entonces la expresin queda VERDE NS=YZW+XYW=YW(Z+X)

DISEO, IMPLEMENTACIN Y PUESTA EN MARCHA DEL CIRCUITO LGICO PARA CONTROLAR EL SEMFORO

LISTADO DE DISPOSITIVOS ELECTRNICOS UTILIZADAS EN EL DISEO

Para el semforo 4 integrados AND referencia 7408 6 integrados NOT referencia 7404 2 integrados OR referencia 7432 4 pulsadores, normalmente abierto 4 resistencias de 10 K 4 diodos led

Para los tanques 2 integrados OR referencia 7432 1 integrado AND referencia 7408 3 resistencias de 10k 1 resistencia de 100 4 pulsadores, normalmente abierto 1 led

Caractersticas tcnicas de cada componente

Parmetro

7408

Tensin de alimentacin Vcc

5 0.25

Tensin de entrada nivel alto VIH

2.0 a 5.5

Tensin de entrada nivel bajo VIL

-0.5 a 0.8

Tensin de salida nivel alto VOH condiciones de funcionamiento: VCC = 4.75, VIH = 2.0 Tensin de salida nivel bajo VOL

2.4 a 3.4

0.2 a 0.4 condiciones de funcionamiento: VCC = 4.75, VIL = 0.8 Corriente de salida nivel alto IOH Corriente de salida nivel bajo IOL Tiempo de propagacin ]Descripcin de las terminales del CI 7408 mx -0.8 mx 16 15.0

Configuracin 7408

Pin 1: La entrada A de la compuerta 1. Pin 2: La entrada B de la compuerta 1. Pin 3: Aqu veremos el resultado de la operacin de la primer compuerta. Pin 4: La entrada A de la compuerta 2. Pin 5: La entrada B de la compuerta 2.

Pin 6: Aqu veremos el resultado de la operacin de la segunda compuerta. Pin 7 Normalmente GND: Es el polo negativo de la alimentacin, generalmente tierra. Pin 8: Aqu veremos el resultado de la operacin de la cuarta compuerta. Pin 9: La entrada B de la compuerta 4. Pin 10: La entrada A de la compuerta 4. Pin 11: Aqu veremos el resultado de la operacin de la tercer compuerta. Pin 12: La entrada B de la compuerta 3. Pin 13: La entrada A de la compuerta 3. Pin 14 Normalmente VCC: Alimentacin, es el pin donde se conecta el voltaje de alimentacin de 5 0.25 voltios.

Descripcin de las terminales del CI 7404 Parmetro Tensin de alimentacin Vcc Tensin de entrada nivel alto VIH Tensin de entrada nivel bajo VIL Tensin de salida nivel alto VOH condiciones de funcionamiento: V CC = 4.75, VIL = 0.8 Tensin de salida nivel bajo VOL condiciones de funcionamiento: V CC = 4.75, VIH = 2.0 Corriente de salida nivel alto IOH Corriente de salida nivel alto IOL Tiempo de propagacin 7404 5 0.25 2.0 a 5.5 -0.5 a 0.8 2.4 a 3.4

0.2 a 0.4 mx -0.4 mx 16 10.0

Cuadro de propiedades Cicuito Integrado: Operador: Tecnologa: Puertas: Entradas: Cpsula: Comentario: 7404, NOT TTL 6 1 por puerta DIP 14 pins X

CIRCUITO INTEGRADO 7432 DENOMINACIN TCNICA COMPUERTA DIGITAL OR GRUPO/CLASE/FAMILIA Descripcin: Dispositivos semiconductores y equipo relacionado COMPUERTA OR DE DOS ENTRADAS

UNIDAD DE MEDIDA O PRESENTACION chip o pastilla (UND) DESCRIPCIN GENERAL chip o pastilla semiconductor de silicio , la compuerta OR el circuitos base de la serie 74 XX

CONCLUSION

La electrnica digital nos ofrece un vasto conocimiento del mundo moderno, esta es la tesis que se deriva de la realizacin de nuestro proyecto de trabajo y nos deja entre dicho que es un mundo fascinante, lleno de mucha imaginacin, es por esto que este proyecto es de gran importancia en nuestro mundo profesional ya que la enseanza que deja es inconmensurable

REFERENCIAS BIBLIOGRAFICAS Pinto Aparicio, M.(2009).Mdulo Sistemas Digitales Bsicos.Bucaramanga:Unad. Simulador de Circuitos Proteus 7.7.Descargado el 4 de diciembre de 2012.En http://www.tknologyk.net/2011/08/27/proteus-v7-7-portablesimulador-de-circuitos-electronicos-n_n/ Sumadores Lgicos.30 de abril de 20012.En http://www.pdfqueen.com/pdf/74/74ls83-sumador/ Montaje de electrnica(s,f). descargado el 4 de diciembre de 2012 de la pgina web https://rapidshare.com/#!download|881p12|131617006|Montajes_de_Ele ctronica.rar|3895|0|0 Electrnica Digital, Teora, Problemas Y Simulacin 2012 Montaje electrnico para el aficionado. H. Shreiber Electrnica transistorizada e integrada por M. S kIver Circuitos integrados y dispositivos semiconductores Lecciones de electrnica digital. Miguel Blanes

You might also like

- Aprender Arduino, electrónica y programación con 100 ejercicios prácticosFrom EverandAprender Arduino, electrónica y programación con 100 ejercicios prácticosRating: 4.5 out of 5 stars4.5/5 (14)

- Maquina DeshojarDocument6 pagesMaquina Deshojarjlanp3No ratings yet

- Viscosidades y capacidades lubricantesDocument6 pagesViscosidades y capacidades lubricantesDiaz JuanNo ratings yet

- Alergia PDFDocument485 pagesAlergia PDFPepa Aznar PerezNo ratings yet

- Manual Del Cultivo de Maracuya PDFDocument24 pagesManual Del Cultivo de Maracuya PDFmeyerhuaranga100% (1)

- Seres Emplumados El Arte Plumario en La Amazona Colombiana Vision LocalDocument76 pagesSeres Emplumados El Arte Plumario en La Amazona Colombiana Vision LocalNelson QuintanaNo ratings yet

- 6 Circuitos Combinacionales P ImprimirDocument36 pages6 Circuitos Combinacionales P ImprimirFabian AcostaNo ratings yet

- Entregable Número 1 MatematicasDocument6 pagesEntregable Número 1 Matematicasluz andradeNo ratings yet

- Sesion de Aprendizaje de Lineas Abiertas y Cerradas Primer GradoDocument9 pagesSesion de Aprendizaje de Lineas Abiertas y Cerradas Primer GradoGabriela Alemán MonzonNo ratings yet

- MatlabDocument52 pagesMatlabrolitomaxNo ratings yet

- Proyecto Final Sistemas Digitales Grupo 201417-140Document18 pagesProyecto Final Sistemas Digitales Grupo 201417-140Juan Karloz0% (1)

- Proyecto Final Sistemas Digitales 3Document16 pagesProyecto Final Sistemas Digitales 3Anonymous YCxjjpvNo ratings yet

- Arellano Carrera Practica2Document15 pagesArellano Carrera Practica2Alfonso CarreraNo ratings yet

- Examen Parcial Clinica San PabloDocument2 pagesExamen Parcial Clinica San PabloZetate0% (1)

- Experimento 2 - Compuertas Logicas - Circuitos DigitalesDocument8 pagesExperimento 2 - Compuertas Logicas - Circuitos DigitalesBrenda CastilloNo ratings yet

- ELE212 Guia 5Document4 pagesELE212 Guia 5MarisNo ratings yet

- 8 Bit A BCDDocument6 pages8 Bit A BCDDaniel OsoNo ratings yet

- Comparador 2 bits con compuertas lógicasDocument4 pagesComparador 2 bits con compuertas lógicasChistian SanchezNo ratings yet

- La Compuerta or Exclusiva o XorDocument4 pagesLa Compuerta or Exclusiva o XorEdgar Enrique Paez PalominoNo ratings yet

- Laboratorio de MallasDocument8 pagesLaboratorio de MallasJAVIER ANDRES MONCADA DELGADONo ratings yet

- Antenas - Cardama Jofre Rius Romeu Blanch FerrandoDocument460 pagesAntenas - Cardama Jofre Rius Romeu Blanch FerrandojjhuarteNo ratings yet

- Proyecto Sistemas DigitalesDocument8 pagesProyecto Sistemas DigitalesManuel Alexis Santillana GarabitoNo ratings yet

- Contadores digitales con CI estándarDocument33 pagesContadores digitales con CI estándarMiguelTesenRomeroNo ratings yet

- P3 Satuquinga Evelin ContadoresDocument15 pagesP3 Satuquinga Evelin ContadoresEvelin SatuquingaNo ratings yet

- Caso CreditoDocument2 pagesCaso CreditokellyNo ratings yet

- Proyecto Circuito Contador AutomaticoDocument4 pagesProyecto Circuito Contador AutomaticoSantiago Xavier Yepez LeitonNo ratings yet

- SENA automatismo selladoDocument15 pagesSENA automatismo selladoDeiby FernandoNo ratings yet

- OsciloscopioDocument35 pagesOsciloscopioWalther CJNo ratings yet

- Rendimiento Academico en VensimDocument3 pagesRendimiento Academico en VensimLuis Amaya SalazarNo ratings yet

- Practica #1 Compuertas LogicasDocument4 pagesPractica #1 Compuertas LogicasCarlos OrtegaNo ratings yet

- Lab 05 Circuitos Digitales UNMSMDocument7 pagesLab 05 Circuitos Digitales UNMSMBrandon RH ErickBraddNo ratings yet

- Registros de DesplazamientoDocument28 pagesRegistros de DesplazamientoAnonymous ayB4oYNo ratings yet

- Examen 1 Electrónica DigitalDocument1 pageExamen 1 Electrónica DigitalRobert Portocarrero Gamboa100% (1)

- EXAMENFMDDocument7 pagesEXAMENFMDLaura Davila TrujilloNo ratings yet

- Laboratorio9 Contadores CDIIDocument1 pageLaboratorio9 Contadores CDIINikolas BarrazaNo ratings yet

- Practica 1 Histograma en ImagenDocument2 pagesPractica 1 Histograma en ImagenDiego Armando Cruz SeguraNo ratings yet

- Laboratorio n4 de Sumador Multiplexor y DemultiplexorDocument11 pagesLaboratorio n4 de Sumador Multiplexor y DemultiplexorSantos Zosimo Ocas GoicocheaNo ratings yet

- Registros de DesplazamientoDocument17 pagesRegistros de DesplazamientoJULIÁN SAÚL DÁVILA REQUE100% (1)

- Más sobre compuertas lógicas NOR, NAND, XOR y XNORDocument12 pagesMás sobre compuertas lógicas NOR, NAND, XOR y XNORFernando ArenasNo ratings yet

- Clase de PatronesDocument5 pagesClase de PatronesEddy EspinoNo ratings yet

- Ejemplo de Maquina de EstadosDocument7 pagesEjemplo de Maquina de Estadoskaggi0No ratings yet

- Informe-5 8255 FunDocument16 pagesInforme-5 8255 FunSantiago David100% (1)

- Examen parcial de sistemas digitales FIA-USIDocument2 pagesExamen parcial de sistemas digitales FIA-USIchristian lezama cuellarNo ratings yet

- Práctica 5 Circuitos Lógicos CombinatoriosDocument6 pagesPráctica 5 Circuitos Lógicos CombinatoriosBayron A. Pérez AyalaNo ratings yet

- Informe 02Document8 pagesInforme 02Cesar Jean Pierre Gonzales QuinquillaNo ratings yet

- Laboratorio 2Document5 pagesLaboratorio 2Jorge Luis Condori TallacaguaNo ratings yet

- Cuantificadores Uniformes y LogarítmicosDocument7 pagesCuantificadores Uniformes y LogarítmicosRonald BarciaNo ratings yet

- 2021-1 Micro Lab3Document3 pages2021-1 Micro Lab3Alvaro Coronel ArbizuNo ratings yet

- Modelo Osi IndustrialDocument32 pagesModelo Osi IndustrialEduardo HurtadoNo ratings yet

- Trabajo Autonomo 4 Resolucion Ejercicios Utilizando VHDLDocument7 pagesTrabajo Autonomo 4 Resolucion Ejercicios Utilizando VHDLHomeroOjedaNo ratings yet

- Sistema de Control SISODocument3 pagesSistema de Control SISOLaura Marcela Grajales LópezNo ratings yet

- PR03 - Problemas CombinacionalesDocument11 pagesPR03 - Problemas Combinacionalesjaouad el ouahabiNo ratings yet

- Manual Simulacion 19VDocument37 pagesManual Simulacion 19VEduardo OrozcoNo ratings yet

- Automat AsDocument17 pagesAutomat AsDiego AceroNo ratings yet

- PRACTICA 2 Sistemas Digitales IIDocument5 pagesPRACTICA 2 Sistemas Digitales IIArmando Alvarado YucraNo ratings yet

- Guía Practica Álgebra de BooleDocument5 pagesGuía Practica Álgebra de BooleMatias TenelandaNo ratings yet

- Laboratorio Diseño LogicoDocument14 pagesLaboratorio Diseño LogicoOscar Sanchez0% (1)

- Laboratorio 1 Corriente ContinuaDocument10 pagesLaboratorio 1 Corriente ContinuaAnonymous D9U9bUNo ratings yet

- Lab 4 - ADC-DAC-2018 - 2Document3 pagesLab 4 - ADC-DAC-2018 - 2fieeg4No ratings yet

- Series Fourier trigonométricas y exponencialesDocument4 pagesSeries Fourier trigonométricas y exponencialesMaria JuliaNo ratings yet

- T1.1 IO II - UPN - Modelado y SimulaciónDocument41 pagesT1.1 IO II - UPN - Modelado y Simulaciónjoel_va1100% (1)

- Sumador CompletoDocument7 pagesSumador CompletoIrving VazMarNo ratings yet

- Práctica 4 Circuitos DigitalesDocument2 pagesPráctica 4 Circuitos DigitalesalfredocorNo ratings yet

- LABORATORIO 11 Contadores AsincronosDocument5 pagesLABORATORIO 11 Contadores AsincronosJimm AyllónNo ratings yet

- Multiplexor y DemultiplexorDocument13 pagesMultiplexor y DemultiplexorIvOn HerreRaNo ratings yet

- Diseño de circuitos lógicos digitalesDocument9 pagesDiseño de circuitos lógicos digitalesAlejandro QuelalNo ratings yet

- Circuitos Lógicos CombinacionalesDocument5 pagesCircuitos Lógicos CombinacionalesRenzo Bilbao ArceNo ratings yet

- 5 Consejos para Que Tus Hijos Eviten Las DeudasDocument2 pages5 Consejos para Que Tus Hijos Eviten Las DeudasNelson QuintanaNo ratings yet

- Mal Desarrollo y PstdesarrolloDocument36 pagesMal Desarrollo y PstdesarrolloNano Mago McflyNo ratings yet

- AccionesafirmativasDocument901 pagesAccionesafirmativasnestor_mondragonNo ratings yet

- AporofobiaDocument6 pagesAporofobiaNelson Quintana100% (1)

- Valorizacion de Metales PDFDocument6 pagesValorizacion de Metales PDFJorge Patricio Valencia LópezNo ratings yet

- AporofobiaDocument6 pagesAporofobiaNelson Quintana100% (1)

- COncentrados de Minerales S ¡¡¡Document9 pagesCOncentrados de Minerales S ¡¡¡Julio Cesar Jimenez CalopinoNo ratings yet

- Mal Desarrollo y PstdesarrolloDocument36 pagesMal Desarrollo y PstdesarrolloNano Mago McflyNo ratings yet

- Ai 185 S 05Document30 pagesAi 185 S 05Anonymous wekTIAuzPbNo ratings yet

- Puesto de Trabajo para La Venta de Arepas de Maíz en Espacios Públicos de La Ciudad de PereiraDocument97 pagesPuesto de Trabajo para La Venta de Arepas de Maíz en Espacios Públicos de La Ciudad de PereiraNelson QuintanaNo ratings yet

- MINERIAYCOMUNIDADESindepaz 1Document82 pagesMINERIAYCOMUNIDADESindepaz 1Daniela GMNo ratings yet

- CONSEJO DE PLAGUICIDAS DE ANTIOQUIA: GUÍA PARA EL MANEJO DE PLAGAS CASERAS Y RESIDENCIALESDocument23 pagesCONSEJO DE PLAGUICIDAS DE ANTIOQUIA: GUÍA PARA EL MANEJO DE PLAGAS CASERAS Y RESIDENCIALESFerney CaroNo ratings yet

- Obtencion de Hojuelas A Partir de La LentejaDocument85 pagesObtencion de Hojuelas A Partir de La LentejaNelson QuintanaNo ratings yet

- Manual Generador EolicoDocument21 pagesManual Generador EolicoAdrian Martínez GarcíaNo ratings yet

- Ai 185 S 05Document30 pagesAi 185 S 05Anonymous wekTIAuzPbNo ratings yet

- Ficha Tecnica de AlgarrobinaDocument72 pagesFicha Tecnica de AlgarrobinaNiki StevensNo ratings yet

- Descripción de especies: Manilkara zapotaDocument4 pagesDescripción de especies: Manilkara zapotaNelson QuintanaNo ratings yet

- Manual PinaDocument10 pagesManual PinaNelson QuintanaNo ratings yet

- Crecimiento de Dunaliella Salina Con Polvillo de CementoDocument8 pagesCrecimiento de Dunaliella Salina Con Polvillo de CementoNelson QuintanaNo ratings yet

- Mercados verdes y biocomercio sostenibleDocument25 pagesMercados verdes y biocomercio sostenibleNelson QuintanaNo ratings yet

- A5351EDocument48 pagesA5351EOrion GuerreroNo ratings yet

- Los Bivalvos y El HombreDocument24 pagesLos Bivalvos y El HombreNelson QuintanaNo ratings yet

- HorticulturaDocument12 pagesHorticulturaJudithWizenbergNo ratings yet

- Los Deportes Alternativos y LaDocument56 pagesLos Deportes Alternativos y LaNelson QuintanaNo ratings yet

- Fao. Manual para CosechasDocument136 pagesFao. Manual para CosechasFredy Alexander MeloNo ratings yet

- Guía de Disposicion de Excretas Aguas Residuales FINDocument40 pagesGuía de Disposicion de Excretas Aguas Residuales FINBetzabe Quiroa de VelizNo ratings yet

- El Sexto Es Una Obra de José María ArguedasDocument3 pagesEl Sexto Es Una Obra de José María ArguedasJessenia Sandoval100% (1)

- Cinetica Enzimatica 1Document2 pagesCinetica Enzimatica 1Massiel Marley LOPEZ RODRIGUEZNo ratings yet

- Consejeria Pastoral-Manual-Alexis JDocument43 pagesConsejeria Pastoral-Manual-Alexis JErnestoAlvarezNo ratings yet

- 2019A MEC6B5 Clase6 11-Abril-2019Document19 pages2019A MEC6B5 Clase6 11-Abril-2019RosselMedinaNo ratings yet

- Qué Es Una Metodología EjemploDocument7 pagesQué Es Una Metodología Ejemplohelena valentina velasquezNo ratings yet

- Posibilidades y límites en el aprendizaje: evaluación dinámica del WISC-IVDocument231 pagesPosibilidades y límites en el aprendizaje: evaluación dinámica del WISC-IVMONICANo ratings yet

- F 07 - ESPECIFICACIONES TECNICAS - CAMINO JR. LIBERTAD OkDocument19 pagesF 07 - ESPECIFICACIONES TECNICAS - CAMINO JR. LIBERTAD OkLeonardo Francisco Sanchez GuerreroNo ratings yet

- Gabinete # 4Document3 pagesGabinete # 4WILMER VALLEJOS MONTENEGRONo ratings yet

- Portada de ModuloDocument8 pagesPortada de ModuloLina AviñaNo ratings yet

- Importancia de la reglamentación turísticaDocument3 pagesImportancia de la reglamentación turísticaMariana TorresNo ratings yet

- Práctica 9Document5 pagesPráctica 9Fernanda MurguiaNo ratings yet

- Trabajo Final EpidemiologiaDocument15 pagesTrabajo Final EpidemiologiaJhon Faiver Moreno NietoNo ratings yet

- TESIS Enfoque SistemicoDocument123 pagesTESIS Enfoque SistemicoArq. Ruben LaraNo ratings yet

- 1er P.I ÁlgebraDocument4 pages1er P.I ÁlgebraEsperanza GonzalesNo ratings yet

- Proyecto Final Análisis Estructural Tatiana-Luis-ManuelDocument38 pagesProyecto Final Análisis Estructural Tatiana-Luis-ManuelJuan David OsorioNo ratings yet

- Prueba de Hipótesis EstadísticaDocument29 pagesPrueba de Hipótesis EstadísticaBrenditaNo ratings yet

- Albañeleria AporticadaDocument20 pagesAlbañeleria AporticadaRenso Ivan Santos Charaja100% (1)

- La mirada en el espejo: lecciones de Noemí Quezada sobre la antropología y la historiaDocument17 pagesLa mirada en el espejo: lecciones de Noemí Quezada sobre la antropología y la historiaMelissa CobarrubiasNo ratings yet

- Trabalho Prático de BioDocument3 pagesTrabalho Prático de BioPoliana RodriguesNo ratings yet

- EXPOSICIÓNDocument3 pagesEXPOSICIÓNAlicia100% (1)

- Fisica - Tema 1. McuDocument1 pageFisica - Tema 1. McuEdwar Samaniego LazarteNo ratings yet

- Ciudadanía y Diversidades. Cultura Política y Opinión PúblicaDocument8 pagesCiudadanía y Diversidades. Cultura Política y Opinión Públicaval cabreroNo ratings yet

- Check List ISO 14001Document15 pagesCheck List ISO 14001Sebastian Franco Espinoza DuranNo ratings yet

- Práctica Calificada 2 - Formato UTPDocument8 pagesPráctica Calificada 2 - Formato UTPAlan Daniel GuillermoNo ratings yet

- Controles de calderas para optimizar la combustiónDocument46 pagesControles de calderas para optimizar la combustiónJairo Alian ParraNo ratings yet

- Análisis de riesgos enchape balconesDocument2 pagesAnálisis de riesgos enchape balconesNubia Milena RIVERA CARRENO50% (2)

- Plan de Gobierno de Ciriaco Isidro Diaz AresteguiDocument31 pagesPlan de Gobierno de Ciriaco Isidro Diaz AresteguiArturo Jhony LlanosNo ratings yet