Professional Documents

Culture Documents

UART (Verilog Code) With FSM

Uploaded by

सौरभ शुक्लाOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UART (Verilog Code) With FSM

Uploaded by

सौरभ शुक्लाCopyright:

Available Formats

1.

Objective of work

A: Core Objective

Study, Design and Testing Of Universal Asynchronous Receiver / Transmitter using language Verilog.

B: Specific Objective

UART receiver / Transmitter have 8 data bits, one stop bits with one start bit. Baud generator has its baud rate divisor . Interface circuit (FIFO). Tested in Spartan 3 starter kit board (FPGA).

2. Functional Partitioning Of project

Task I :

Design of Baud rate generator for Receiver.

Task II :

Design of UART Receiver sub system.

Task III :

Design of Baud rate generator for transmitter.

Task IV :

Design of Transmitter sub system.

Task IV :

Design of asynchronous FIFO Interface circuit.

3: Functional Task completed of Project

Task I :

Design of Baud rate generator for Receiver.

Task II :

Design of UART Receiver sub system.

Both task I and Task II completed successfully and Tested in Spartan 3 starter kit board (FPGA).

Task III :

Design of Baud rate generator for transmitter. Task completed successfully but have to test in Sparten- 3 starter kit board(FPGA).

Task IV and Task V:

Both Task in process.

4: FSM of Baud Rate generator of receiver:

5: FSM of UART Receiver:

6: Appendices

6.1: Verilog code for Top Module of receiver:

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 10:33:31 12/07/2011 // Design Name: // Module Name: Rx_TOP_code // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // //////////////////////////////////////////////////////////////////////////////////

module Rx_TOP_code(Rst,clk,Rx,Rx_data_out,Rx_data_out_done);

output [7:0]Rx_data_out; output Rx_data_out_done;

input clk; input Rx; input Rst;

wire a;

new_Rx_baud U1(.Rst(Rst),.clk(clk),.Rx_baud(a)); new_Rx U2(.Rst(Rst),.Rx_baud(a),.Rx_data_out(Rx_data_out),.Rx_data_out_done(Rx_data_out_done),.Rx(Rx)) ;

endmodule

6.2: Verilog code of Baud rate Generator of Receiver

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer:

// // Create Date: 00:27:11 12/07/2011 // Design Name: // Module Name: new_Rx_baud // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module new_Rx_baud(clk,Rst,Rx_baud);

parameter S0 = 2'b00; parameter S1 = 2'b01; parameter S2 = 2'b10; parameter S3 = 2'b11;

output Rx_baud; input Rst;

input clk;

reg Rx_baud; reg [1:0]Pr_state; reg [1:0]Nx_state; integer count;

always@(Rst or count or Pr_state) begin case(Pr_state)

S0: begin if(Rst) begin

Nx_state = S0; end else begin

Nx_state = S1; end

end

S1: begin if((count >= 0) && (count <= 81)) begin Nx_state = S1; end else begin Nx_state = S2; end end

S2: begin if((count > 81) && (count < 163)) begin Nx_state = S2; end else begin Nx_state = S0; end end

default: begin Nx_state = S0; end endcase end

always@(posedge clk or posedge Rst) begin if(Rst) begin count = 0; Pr_state = S0; end else begin Pr_state = Nx_state;

case(Nx_state)

S0: begin count = 0;

end

S1: begin Rx_baud = 1; count = count + 1; end

S2: begin Rx_baud = 0; count = count + 1;

end

default: begin count = 0; Rx_baud = 1; end

endcase end end

endmodule

6.3: Verilog code of UART Receiver:

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 01:22:43 12/07/2011 // Design Name: // Module Name: new_Rx // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module new_Rx(Rx_baud,Rst,Rx_data_out,Rx_data_out_done,Rx);

parameter S0 = 3'b000; parameter S1 = 3'b001; parameter S2 = 3'b010; parameter S3 = 3'b011; parameter S4 = 3'b100; parameter S5 = 3'b101; parameter S6 = 3'b110; parameter S7 = 3'b111;

output [7:0]Rx_data_out; output Rx_data_out_done;

input Rx_baud; input Rst; input Rx;

reg [2:0]Pr_state; reg [2:0]Nx_state;

reg [7:0]Rx_data_out; reg Rx_data_out_done;

reg [4:0] count2,count3; reg [3:0] count1,bit_num;

reg data_done; reg [7:0]data;

always@(Pr_state or Rst or count1 or count2 or count3 or data_done or bit_num or Rx) begin case(Pr_state)

S0: begin if(Rst) begin Nx_state = S0; end else begin Nx_state = S1; end end

S1: begin if(Rx) begin Nx_state = S1;

end else begin Nx_state = S2; end end

S2: begin if((count1 >= 0 ) && (count1 < 7)) begin Nx_state = S2; end else begin Nx_state = S3; end end

S3: begin if((count2 >=0) &&(count2 < 15)) begin Nx_state = S3; end

else begin Nx_state = S4; end end

S4: begin if((bit_num >= 0) &&(bit_num <= 7)) begin Nx_state = S3; end else begin Nx_state = S5; end end

S5: begin if((count3 >= 0) &&(count3 < 15)) begin Nx_state = S5; end else

begin Nx_state = S6; end end

S6: begin if(data_done) begin Nx_state = S0; end else begin Nx_state = S6; end end

default: begin Nx_state = S0; end endcase end

always@(posedge Rx_baud or posedge Rst)

begin if(Rst) begin count1 = 0; count2 = 0; count3 = 0; bit_num = 0; data_done = 0; Pr_state = S0; end else begin Pr_state = Nx_state; case(Nx_state)

S0: begin count1 = 0; count2 = 0; count3 = 0; bit_num = 0; data_done = 0; data_done = 0; Rx_data_out_done = 0; end

S1: begin count1 = 0; end

S2: begin count1 = count1 + 1; end

S3: begin count2 = count2 + 1; end

S4: begin data[bit_num] = Rx; bit_num = bit_num + 1; count2 = 0; end

S5: begin

count3 = count3 + 1; end

S6: begin data_done = 1; Rx_data_out = data; Rx_data_out_done = 1; end

default: begin data_done = 0; count1 = 0; count2 = 0; count3 = 0; bit_num = 0; end endcase end end endmodule

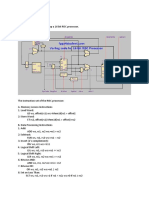

7: Result: 7:1. RTL Schematic View of receiver Top module:

7.2: RTL Schematic View of receiver Baud Rate Generator module

7.3: RTL Schematic View of receiver module

8: Simulated Behavioral Result: 8:1. Simulated Behavioral Result of Top module of Receiver:

8:2. Simulated Behavioral Result of Baud rate generator of Receiver:

8:2. Simulated Behavioral Result of UART Receiver:

You might also like

- MATLAB & Simulink For Digital CommunicationDocument115 pagesMATLAB & Simulink For Digital CommunicationKy Phan40% (5)

- Interfacing and Some Common Building Blocks: Coe 111: Advanced Digital DesignDocument35 pagesInterfacing and Some Common Building Blocks: Coe 111: Advanced Digital DesignFrancisNo ratings yet

- Design and Verification of AMBA APB ProtocolDocument8 pagesDesign and Verification of AMBA APB ProtocolsiruNo ratings yet

- Digital Design With SystemVerilogDocument58 pagesDigital Design With SystemVerilogStephen A. EdwardsNo ratings yet

- Uvm Cookbook CollectionDocument54 pagesUvm Cookbook CollectionQuý Trương QuangNo ratings yet

- Introduction To The Packet-Based ProtocolDocument50 pagesIntroduction To The Packet-Based ProtocolAbhishekNo ratings yet

- What Is Setup and Hold Time?Document12 pagesWhat Is Setup and Hold Time?Minu MathewNo ratings yet

- Verilog CodesDocument10 pagesVerilog CodesKrishna RamaNo ratings yet

- VCS QuickStartDocument66 pagesVCS QuickStartMarko NedicNo ratings yet

- Static Timing AnalysisDocument9 pagesStatic Timing AnalysisPradeepdarshan PradeepNo ratings yet

- AXI Interface Custom IP MicroBlazeDocument28 pagesAXI Interface Custom IP MicroBlazesujit24chavadaNo ratings yet

- Digital Verilog SV Interview QuestionsDocument10 pagesDigital Verilog SV Interview Questionsradhakodirekka8732No ratings yet

- How To Write FSM Is VerilogDocument8 pagesHow To Write FSM Is VerilogAyaz MohammedNo ratings yet

- Lab 5 DR Muslim (Latest)Document15 pagesLab 5 DR Muslim (Latest)a ThanhNo ratings yet

- System Verilog BasicsDocument82 pagesSystem Verilog BasicsTiger Gangappa AngadiNo ratings yet

- SANDISKDocument3 pagesSANDISKrAM100% (3)

- 32 SPD - eRAN12.1 - LTE FDD Network Design Technical Training-20170315-A-1.0Document112 pages32 SPD - eRAN12.1 - LTE FDD Network Design Technical Training-20170315-A-1.0Juan Ulises CapellanNo ratings yet

- Fpga Interview QuestionDocument35 pagesFpga Interview QuestionRAGUL RAJ S100% (1)

- ASIC LabDocument75 pagesASIC LabMayur AgarwalNo ratings yet

- Amba 3 Axi Protocol Checker: User GuideDocument58 pagesAmba 3 Axi Protocol Checker: User GuidepriyajeejoNo ratings yet

- Uart Receiver Verilog CodeDocument31 pagesUart Receiver Verilog CodeSannena Govinda80% (5)

- Spyglass CDCDocument2 pagesSpyglass CDCRahul SharmaNo ratings yet

- FPGA Interview QuestionsDocument12 pagesFPGA Interview QuestionsVirbhadra RathodNo ratings yet

- Vlsi Design of Amba Based Ahb2apb BridgeDocument12 pagesVlsi Design of Amba Based Ahb2apb BridgeAnonymous e4UpOQEPNo ratings yet

- System Verilog: Question 1. What Is Callback ?Document15 pagesSystem Verilog: Question 1. What Is Callback ?Shreyas S R100% (1)

- I 2 CDocument16 pagesI 2 CelumalaianithaNo ratings yet

- Clock Domain Crossing BasicsDocument9 pagesClock Domain Crossing BasicsRapolu SushmaNo ratings yet

- An CDC False PathDocument6 pagesAn CDC False PathMukeshPandaNo ratings yet

- Intro to SystemVerilog FeaturesDocument68 pagesIntro to SystemVerilog FeaturesHardik TrivediNo ratings yet

- Bridge Axi AhbDocument19 pagesBridge Axi Ahbsureshchandra100% (1)

- ASIC Design Interview Questions: Verilog Interview Questions ExplainedDocument18 pagesASIC Design Interview Questions: Verilog Interview Questions Explainedvasav1No ratings yet

- Ssvs Training: Huawei Technologies Co., LTDDocument14 pagesSsvs Training: Huawei Technologies Co., LTDEdwin Llugsha100% (2)

- Verilog interview questions and answers for FPGA & ASIC designDocument7 pagesVerilog interview questions and answers for FPGA & ASIC designradhakodirekka8732No ratings yet

- Design and verification of AXI-APB bridgeDocument9 pagesDesign and verification of AXI-APB bridgeKi KiNo ratings yet

- Cisco Packet TracerDocument33 pagesCisco Packet TracerMT RA0% (1)

- Arm Amba Ahb Split & RetryDocument2 pagesArm Amba Ahb Split & Retrynvenkatesh485No ratings yet

- Digital Design Concepts ExplainedDocument3 pagesDigital Design Concepts Explainedthatflamyguy2216No ratings yet

- MulticastDocument97 pagesMulticastAndres ChavessNo ratings yet

- Ahb Interview QuestionsDocument1 pageAhb Interview QuestionsRamachandranNo ratings yet

- Hillstone Security Management User Guide 3.0R2Document321 pagesHillstone Security Management User Guide 3.0R2MayNo ratings yet

- Max Clock Frequency D-FF Circuit Buffer Design Latchup Prevention State Machines 2's Complimenter/TITLEDocument27 pagesMax Clock Frequency D-FF Circuit Buffer Design Latchup Prevention State Machines 2's Complimenter/TITLERui ChenNo ratings yet

- Router 1X3 - RTL Design and VerificationDocument10 pagesRouter 1X3 - RTL Design and VerificationIJERDNo ratings yet

- Verilog Interview QuestionsDocument4 pagesVerilog Interview QuestionsKing KhanNo ratings yet

- Structural Data Types: Wire and RegDocument25 pagesStructural Data Types: Wire and RegRAGUL RAJ SNo ratings yet

- Ahb QuestionsDocument20 pagesAhb QuestionsMohammed Nawaz ShaikNo ratings yet

- On Verification Using Uvm SPI ProtocolDocument33 pagesOn Verification Using Uvm SPI ProtocolSuyog Chavan0% (1)

- SV Lab ManualDocument20 pagesSV Lab ManualShakeel ScetNo ratings yet

- Arm Amba AhbDocument18 pagesArm Amba AhbgeethaNo ratings yet

- System Verilog TrainingDocument2 pagesSystem Verilog TrainingVlsi GuruNo ratings yet

- AMBA APB UVM Testbench FrameworkDocument19 pagesAMBA APB UVM Testbench FrameworkDivya srivastavaNo ratings yet

- Setup and Hold ViolationsDocument9 pagesSetup and Hold Violationsrajurecd100% (1)

- Design and Implementation of UartDocument21 pagesDesign and Implementation of Uartbhanu455No ratings yet

- Synchronous FIFO VerilogDocument23 pagesSynchronous FIFO VerilogRoshan RajuNo ratings yet

- Ddr3-Emac40-Queue-Manager Test Bench: - C2sisDocument20 pagesDdr3-Emac40-Queue-Manager Test Bench: - C2sisAnkit Goel100% (1)

- Io MultiplexingDocument19 pagesIo Multiplexingsubramanyam62No ratings yet

- Timing AnalysysDocument15 pagesTiming AnalysysrrramananNo ratings yet

- Cadence Product Validation Engineer Interview QuestionsDocument3 pagesCadence Product Validation Engineer Interview QuestionsSanjay Sanju YadavNo ratings yet

- Apb Protocal: Presented By, Sulthana ShaikDocument26 pagesApb Protocal: Presented By, Sulthana ShaikJerin VargheseNo ratings yet

- Assertion AxiDocument42 pagesAssertion AxiSuvendra Sahoo0% (1)

- Spi Protocol Verilog Code ExplanationDocument15 pagesSpi Protocol Verilog Code Explanationgokul pNo ratings yet

- EGCP 446: Advanced Digital Design: Part One - Moore State Machine On FPGADocument16 pagesEGCP 446: Advanced Digital Design: Part One - Moore State Machine On FPGAShashwat PatelNo ratings yet

- A Division of Labor: B.1 Test Labkit.vDocument31 pagesA Division of Labor: B.1 Test Labkit.vraymar2kNo ratings yet

- Lab # 4Document15 pagesLab # 4inzamamNo ratings yet

- EE312 Experiment 07: Objective 1Document18 pagesEE312 Experiment 07: Objective 1SAURABH RAJNo ratings yet

- OG For WDM ASON Network Management - (V100R006C02 - 01)Document354 pagesOG For WDM ASON Network Management - (V100R006C02 - 01)Taha TounsiNo ratings yet

- ITT575 - Scheme of WorkDocument5 pagesITT575 - Scheme of WorkCalvin OhseyNo ratings yet

- Alcatel-Lucent in Iuh R9 PDFDocument2 pagesAlcatel-Lucent in Iuh R9 PDFRZNo ratings yet

- Binary Offset CarrierDocument20 pagesBinary Offset Carriernaitiknakrani1803No ratings yet

- Optical EthernetDocument29 pagesOptical EthernetNiharika Madgula100% (1)

- Distributed SystemsDocument1 pageDistributed SystemsTejas PanchalNo ratings yet

- Review of Network Technologies: Indian Institute of Technology KharagpurDocument19 pagesReview of Network Technologies: Indian Institute of Technology KharagpurKapasi TejasNo ratings yet

- Fortios v7.0.7 Release NotesDocument37 pagesFortios v7.0.7 Release Notesumbo202No ratings yet

- Communicating Lab FundamentalsDocument7 pagesCommunicating Lab FundamentalsEdward YaoNo ratings yet

- Accurate Modeling of Modbus/TCP For Intrusion Detection in SCADA SystemsDocument14 pagesAccurate Modeling of Modbus/TCP For Intrusion Detection in SCADA Systemsalibob78No ratings yet

- Group B Assignment: File Transfer Using UDP SocketsDocument5 pagesGroup B Assignment: File Transfer Using UDP Socketsvaibhav patilNo ratings yet

- WorkshopPLUS - Active Directory Federation Services Deployment, Administration and Troubleshooting 5.3.2019Document2 pagesWorkshopPLUS - Active Directory Federation Services Deployment, Administration and Troubleshooting 5.3.2019RaphaelCPNo ratings yet

- Huawei S2300 Configuration GuideDocument200 pagesHuawei S2300 Configuration GuideAndrés Espejo100% (1)

- Mohan ResumeDocument2 pagesMohan Resumeapi-3697677No ratings yet

- Well Known IP PortsDocument19 pagesWell Known IP PortsantonpgmNo ratings yet

- Encor Chap 8 OspfDocument35 pagesEncor Chap 8 OspfEric LambaNo ratings yet

- Huawei Video Phone ESpace 8850 Administrator Guide (V100R001C01 - 01)Document130 pagesHuawei Video Phone ESpace 8850 Administrator Guide (V100R001C01 - 01)minhNo ratings yet

- PL2303GT USB To RS232 Serial Bridge Controller With Built-In RS232 TransceiverDocument29 pagesPL2303GT USB To RS232 Serial Bridge Controller With Built-In RS232 TransceiverNabeel MohammedNo ratings yet

- User Guide: 300Mbps Wi-Fi Range Extender With AC Passthrough TL-WA860REDocument39 pagesUser Guide: 300Mbps Wi-Fi Range Extender With AC Passthrough TL-WA860REPedro MendozaNo ratings yet

- BRKCRS 2111Document76 pagesBRKCRS 2111garmahis79No ratings yet

- 1 0 SV9100 SIP Trunk Config Guide XCast LabsDocument38 pages1 0 SV9100 SIP Trunk Config Guide XCast Labsdynamic chartsNo ratings yet

- Simulation The Concentrated-NOC: CMesh-NOC and CTorus-NOCDocument5 pagesSimulation The Concentrated-NOC: CMesh-NOC and CTorus-NOCJournal of ComputingNo ratings yet

- Cluster SetupDocument4 pagesCluster SetupSuhaimi MieNo ratings yet

- KQ 330fDocument8 pagesKQ 330fservio2009No ratings yet