Professional Documents

Culture Documents

FPGA Design

Uploaded by

Dana HowellCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FPGA Design

Uploaded by

Dana HowellCopyright:

Available Formats

Course Title:

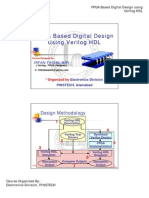

FPGA Based Digital Design using Verilog HDL

FPGA Based Digital Design Using Verilog HDL

Course Designed by:

IRFAN FAISAL MIR

( Verilog / FPGA Designer ) irfanfaisalmir@yahoo.com

* Organized by Electronics Division PINSTECH, Islamabad

Integrated Circuits

Uses for digital IC technology today:

Standard Microprocessors

Used in desktop PC and embedded applications

Memory Chips (RAMs) Application Specific ICs (ASICs)

Custom design to match particular applications Can be optimized for low power, low cost, high performance

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Field Programmable Logic Devices (FPGAs, CPLDs)

Customized to particular applications Reconfigure device Short time to market Xilinx FPGA

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

FPGA Basics

FPGA Basics FPGA stands for Field Programmable Gate Array. FPGA can be categorized as: Anti-fuse based (ex: Actel) SRAM Based (ex: Xilinx, Altera) SRAM Based FPGAs are most popular due to its reconfigurable feature

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

World Popular Xilinx FPGA is typically an SRAM-based device Number of System Gates, Speed Grade, Frequency, No of I/Os and Build in features etc are basic identity of any FPGA

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

FPGA is a Programmable Integrated Circuit consisting of: An internal array of Configurable Logic Blocks (CLBs). A ring of programmable input/output blocks. Connected together via programmable Basic FPGA Internal Architecture interconnection.

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Some Popular Xilinx FPGAs:

Spartan II/IIE/III, VirtexTM, Virtex-E and VirtexTM-II devices. Range of Xilinx FPGAs from Few 10K Gates to Multi-Million Gates with Embedded Cores.

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

Verilog HDL Basics

Verilog HDL Basics

Verilog HDL is a Hardware Description Language. It describes the hardware. It is not a programming & procedural language. Verilog HDL is a concurrent language It enables specification of a digital system at a range of levels of abstraction: Switches, Gates, RTL, and higher Open Verilog International (OVI) IEEE Course Organized By: Electronics Division, Introductory Class 1364 PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Why use an HDL ?

Describe complex designs (millions of gates) Input to synthesis tools (synthesizable subset) Design exploration with simulation

Why not use a general purpose language

Support for structure and instantiation Support for describing bit-level behavior Support for timing

Introductory Class

Support for concurrency Organized By: Electronics Division, Course

PINSTECH, Islamabad

Verilog vs. VHDL

Verilog is relatively simple and close to C VHDL is complex Verilog has 60% of the world digital design market (larger share in US)

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Why do we choose FPGA based solutions ?

We choose FPGA based solution due to two main reason :

Prefer FPGA design flow over ASIC design flow

Traditional ASIC Design Flow

Specifications Layout Entry Layout Extraction Layout Verification

Introductory Class

RTL Code +Synthesis Circuit Validation

Circuit Entry Implementation

ASICs Design Cycle

Concept to RTL RTL to Netlist Netlist to GDS II

ASICs Manufacturing Cycle

GDS II to a Mask

Course Organized By: Electronics Division, Mask to a wafer PINSTECH, Islamabad Wafer to a Packaged part

Why do we prefer FPGA over ASIC ? Customized to particular applications Reconfigure hardware Short time to market When product has hundreds or thousands components, FPGA is preferred. Mostly in Pakistan, FPGA based solution is preferred Setup cost of ASIC is too High. On the other hand min cost of FPGA is about $10 There are FPGA based training boards for Course Organized By: Electronics Division, Introductory Class rapid prototyping PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

FPGA Vs ASIC

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

FPGA Vs ASIC

In latest FPGAs, there are multi-million system gates FPGA has great resources having RAM Blocks, Arithmetic Operations, Signaling Compatibility and many more FPGAs are introduced as an alternative to custom ICs for implementing glue logic: improved density relative to discrete SSI/MSI components (within around 100x of custom ICs) Course Organized By: Electronics Division, Introductory Class

Design Optimization and Specific Chip Dependency Removal

PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

System Integration

FPGA

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

FPGA Technology

Moores Law: In 1965, Gordon Moore noted that the number of transistors on a chip doubled every 18 to 24 months. He made a prediction that semiconductor technology will double its effectiveness every 18 months.

System Gates

50M 10M 4M 2M 1M 500K

FPGAs with 2 million system gates were available in 1998 and ... . . . FPGAs with 50 million system gates will be available in 2004

1998 1999 2000 2001 2002 2003 2004 Course Organized By: Electronics Division, PINSTECH, Islamabad

Introductory Class

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

FPGA Based Design Steps

Design Steps:

Verilog HDL is used for Hardware Designing Synthesis tools typically accept only a subset of the full Verilog language constructs Synthesis tools convert the actual design (Verilog code) to gate level netlist Finally design is implemented into your target technology (Xilinx By: Electronics Division, FPGAs) Course Organized

PINSTECH, Islamabad

Introductory Class

Design Methodology

1

Verilog HDL Description

4

Verilog Test Drivers Synthesis Verilog Design FPGA Implementation Verilog HDL Simulator Simulation Output

2 3

Verilog HDL Simulator Simulation Output Introductory Class

6

Compare Outputs

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Design Example

Example of 4x1 MUX Design Flow

First make a design of system on paper and study its all aspects Write a Behavioral Model in Verilog HDL of design for check its functionality Write RTL in Verilog HDL of design Synthesis tools convert the RTL design (Verilog code) to gate level netlist Finally design is implemented into your target technology (Xilinx FPGAs) Course download in Division, Introductory Class Create a bit file of design that Organized By: Electronics FPGA PINSTECH, Islamabad

Software Required ModelSim PE/SE/XE Xilinx Foundation Series 3.1i/Xilinx ISE Series 4.1i or Above Hardware Required FPGA Boards (Xilinx Spartan/Virtex) Xilinx Parallel Cable

Course Organized By: Electronics Division, PINSTECH, Islamabad

Introductory Class

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

in_0 in_1 in_2 in_3

MUX 4X1

out_data

sel_1 sel_0 Block Diagram of 1-bit 4x1 MUX

First we define its input and outputs ports (in size, numbers) and assign a unique name of each port. Here

inputs: in_0, in_1, in_2, in_3 and sel_0, sel_1 output: out_data (*These are all single bit) Organized By: Course Introductory Class

Electronics Division, PINSTECH, Islamabad

Design 1-bit 4x1 MUX in Verilog HDL

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Test Bench for Design

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

ModelSim main Window

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

ModelSim main Window

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Waveform Viewer of ModelSim

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Synthesis and Implement Design using XILINX tool

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

FPGA Based Design Flow

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

FPGA in Real World

How to use in Real Environment

Xilinx FPGAs are volatile because they are based on SRAM technology. That is, the device loses its configuration if the power to the device is turned off. FPGAs typically utilize an external memory device, such as a PROM for production type environment to prevent the loss of configuration data in a power outage. Xilinx PROM are available in two different type One Time Programmable (OTP) [XC17x] Introductory Class In System Programmable Course Organized By: Electronics Division, [XC18x] PINSTECH, Islamabad

Xilinx XC4000 FPGA in Slave Serial Mode

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Xilinx FPGA use with PROM

PCB

P R O M

FPGA

JTAG Header

Select Mode

External Source

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

FPGA Development kit

Xilinx Virtex-E Development Kit

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Motivation

System On Chip (SoC) SoC means you put the entire system on a single chip Your Analog and Digital Design on a single chip Example of any complex design that have Micro controller, Memories, Analog portion, DSP processor and algorithm on FPGA Concept is that put all above in a single chip Course Organized By: Electronics Division,

PINSTECH, Islamabad

Introductory Class

New market of business in electronics For SoC you need the Core of every component i-e IP (Intellectual Property) of these core You can build your own IPA group of two or three engineers

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Course Strategy

Information Instructor

Irfan Faisal Mir (M.Sc Electronics)

irfanfaisalmir@yahoo.com

Prerequisite

Digital Logic Design Computer Architecture Concept Programming Basics

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Duration: Two Weeks (Five days per week) Total Lectures: Twenty (20) Total LABS: Twenty (20) (Time: (Time: 1.5 hrs per lecture) 1.5 hrs per lab)

Introductory Class

Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

Course Title:

FPGA Based Digital Design using Verilog HDL

Course Outlines

Course Summary:

Digital Design Methodology Verilog HDL Language with Designing Issues Behavioral and RTL Design Optimized State Machine based Design Testing and Verification Methodology Xilinx FPGA/CPLD architecture FPGA Design Flow

Introductory Class

Digital Circuits Designed Course Organized By: Electronics Division, for specificPINSTECH, Islamabad FPGA

Constraint Editor, Core Generator, Floorplanner, FPGA Editor, iMPACT Constraint Definitions, Timing Analysis Synthesis and implementation using Xilinx ISE 6.1i tools System On Chip (SoC) Xilinx FPGA on PCB in real systems Hardware Testing of FPGA Based Design on Xilinx Development board

Introductory Class Course Organized By: Electronics Division, PINSTECH, Islamabad

Course Organized By: Electronics Division, PINSTECH

You might also like

- UpsDocument40 pagesUpsManveer Singh Saluja100% (3)

- Verilog Imp...Document105 pagesVerilog Imp...Arun JyothiNo ratings yet

- FPGA System Design Course OverviewDocument30 pagesFPGA System Design Course OverviewKrishna Kumar100% (1)

- (Student Mathematical Library 050) Mike Mesterton-Gibbons-A Primer On The Calculus of Variations and Optimal Control Theory-American Mathematical Society (2009)Document274 pages(Student Mathematical Library 050) Mike Mesterton-Gibbons-A Primer On The Calculus of Variations and Optimal Control Theory-American Mathematical Society (2009)Dana Howell100% (1)

- FPGA ArchitectureDocument39 pagesFPGA ArchitectureeeshgargNo ratings yet

- ECE545 Lecture5 Dataflow 6Document15 pagesECE545 Lecture5 Dataflow 6Utpal DasNo ratings yet

- Experiment Sheet - FPGA Design ALLDocument38 pagesExperiment Sheet - FPGA Design ALLSidney O. EbotNo ratings yet

- 1.FPGA Design Flow Processes PropertiesDocument5 pages1.FPGA Design Flow Processes Propertiesmachnik1486624No ratings yet

- LN 14 Arithmetic ModulesDocument42 pagesLN 14 Arithmetic ModulesYermakov Vadim IvanovichNo ratings yet

- LN 10 Design OptionsDocument75 pagesLN 10 Design Optionschaitragowda213_4732No ratings yet

- Islam and Science BOOKDocument88 pagesIslam and Science BOOKDana Howell100% (1)

- Islam and Science BOOKDocument88 pagesIslam and Science BOOKDana Howell100% (1)

- LN 06 Hierarchical ModelingDocument37 pagesLN 06 Hierarchical ModelingChauHuynhNo ratings yet

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionFrom EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionNo ratings yet

- C28x WorkshopDocument400 pagesC28x WorkshopMarcio De Andrade VogtNo ratings yet

- Verilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation PrinciplesDocument3 pagesVerilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation PrinciplesSindhu RajanNo ratings yet

- 21CS43 - Module 1Document21 pages21CS43 - Module 1EMMANUEL RAJARATHNAMNo ratings yet

- Lessons Learnt from Project Report on Verilog Model CheckingDocument3 pagesLessons Learnt from Project Report on Verilog Model CheckingVinit PatelNo ratings yet

- Riscv Presentation PDFDocument71 pagesRiscv Presentation PDFkotresh tNo ratings yet

- 080-MV7000 User Manual Section6 - Maintenance - 4MKG0016 - Rev C PDFDocument38 pages080-MV7000 User Manual Section6 - Maintenance - 4MKG0016 - Rev C PDFForce MomentumNo ratings yet

- VLSI Lecture02 OpenIDEA (정무경)Document69 pagesVLSI Lecture02 OpenIDEA (정무경)Vinit PatelNo ratings yet

- IR Drop AnalysisDocument9 pagesIR Drop AnalysisRohith Raj100% (1)

- FPGA Structure and ApplicationsDocument11 pagesFPGA Structure and Applicationsanupnaskar naskar100% (1)

- Complex Programmable Logic DeviceDocument7 pagesComplex Programmable Logic DeviceShaik BasheeraNo ratings yet

- CPLDDocument30 pagesCPLDNanda Ganesh Kumar KingNo ratings yet

- Digital System Design by Dr. Shoaib Ahmed KhanDocument30 pagesDigital System Design by Dr. Shoaib Ahmed KhanZain NadeemNo ratings yet

- EE520 ASIC Design PDFDocument44 pagesEE520 ASIC Design PDFthiendoan_bkNo ratings yet

- Asic & Fpga Design QB For MeDocument24 pagesAsic & Fpga Design QB For MejebajohannahsamuelNo ratings yet

- Fpga Programming Using Verilog HDL LanguageDocument89 pagesFpga Programming Using Verilog HDL LanguageSidhartha Sankar Rout0% (1)

- Differences between 8-bit 8085 and 16-bit 8086 microprocessorsDocument3 pagesDifferences between 8-bit 8085 and 16-bit 8086 microprocessorsFaisal Al-Balushi100% (4)

- Dijsktra ThesisDocument65 pagesDijsktra ThesisGupta AakashNo ratings yet

- Fpga DSP WhitepaperDocument15 pagesFpga DSP Whitepaperzohair_r66No ratings yet

- ADPLL Design and Implementation On FPGADocument6 pagesADPLL Design and Implementation On FPGANavathej BangariNo ratings yet

- Altera Max and 7000Document23 pagesAltera Max and 7000Rathish RtsNo ratings yet

- Training Report On VerilogDocument25 pagesTraining Report On VerilogSohail AnsariNo ratings yet

- EE6403 DSP Hand Written NotesDocument282 pagesEE6403 DSP Hand Written Notessyed ibrahim100% (1)

- Chandra Resume VIT (M.tech-VLSI Design) Analog DesignDocument2 pagesChandra Resume VIT (M.tech-VLSI Design) Analog DesignAjay Kumar MattupalliNo ratings yet

- Bus StructureDocument160 pagesBus StructureRohit SaxenaNo ratings yet

- Ap9212 Advanced Digital System Design L T P c3 0 0 3Document1 pageAp9212 Advanced Digital System Design L T P c3 0 0 3Adam Wells100% (1)

- EC551-Fall-2011 Advanced Digital Design With Verilog & FPGAsDocument4 pagesEC551-Fall-2011 Advanced Digital Design With Verilog & FPGAsApoorva BhattNo ratings yet

- Introduction To PSpiceDocument15 pagesIntroduction To PSpiceUmera Anjum100% (1)

- Place & Route Tutorial #1: I. SetupDocument13 pagesPlace & Route Tutorial #1: I. SetupDurgaPrasadNo ratings yet

- Orcad PSpice DesignerDocument47 pagesOrcad PSpice DesignerAishwarya JS100% (1)

- VLSI Lab Manual V Sem July16Document65 pagesVLSI Lab Manual V Sem July16Aditya RanjanNo ratings yet

- Ec8562 DSP ManualDocument86 pagesEc8562 DSP ManualN.S.Priyanga 33No ratings yet

- VHDL PDFDocument112 pagesVHDL PDFvivek patelNo ratings yet

- Introduction To VLSI DesignDocument33 pagesIntroduction To VLSI DesignAnonymous P9xMOgEYt1No ratings yet

- Sequential Digital Circuits Flip Flops Latches Edge TriggeredDocument22 pagesSequential Digital Circuits Flip Flops Latches Edge Triggeredvikramkolanu100% (2)

- Vlsi Physical Design Automation: Theory and PracticeDocument15 pagesVlsi Physical Design Automation: Theory and PracticeMilind SharmaNo ratings yet

- CS8382 DS Lab Manual Cse PDFDocument65 pagesCS8382 DS Lab Manual Cse PDFvlsiprabhu0% (1)

- Chapter 8 - Cmos ComparatorsDocument39 pagesChapter 8 - Cmos Comparatorsfabio-delima8012100% (1)

- KSJ FPGA EtherCAT Master IntroductionDocument4 pagesKSJ FPGA EtherCAT Master IntroductionAndres LNo ratings yet

- 7.performance Analysis of Wallace Tree Multiplier With Kogge Stone Adder Using 15-4 CompressorDocument38 pages7.performance Analysis of Wallace Tree Multiplier With Kogge Stone Adder Using 15-4 Compressoranil kumarNo ratings yet

- Anti FuseDocument2 pagesAnti FuseRahmatullah JatoiNo ratings yet

- Digital Design Flow OverviewDocument68 pagesDigital Design Flow OverviewAbhiPanchalNo ratings yet

- Ap7202-Asic and FpgaDocument12 pagesAp7202-Asic and FpgaMOTHI.R MEC-AP/ECENo ratings yet

- DSDV MODULE 3 Implementation FabricsDocument17 pagesDSDV MODULE 3 Implementation Fabricssalman shariffNo ratings yet

- Summer Training Report On Vlsi and Fpga ImplementationDocument44 pagesSummer Training Report On Vlsi and Fpga ImplementationsaurabhNo ratings yet

- VLSI FDP Brochure - Phase3Document2 pagesVLSI FDP Brochure - Phase3Panku RangareeNo ratings yet

- Vlsi/Fpga Design and Test CAD Tool Flow in Mentor Graphics: Victor P. NelsonDocument44 pagesVlsi/Fpga Design and Test CAD Tool Flow in Mentor Graphics: Victor P. NelsonAvinash B RajNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument29 pagesDigital Integrated Circuits: A Design PerspectiveEMADNo ratings yet

- Application-Specific Integrated Circuit ASIC A Complete GuideFrom EverandApplication-Specific Integrated Circuit ASIC A Complete GuideNo ratings yet

- PMF 5.0 User GuideDocument136 pagesPMF 5.0 User GuideDana HowellNo ratings yet

- ZeitgeistDocument11 pagesZeitgeistDana HowellNo ratings yet

- Lecture#1-Introduction To AIDocument74 pagesLecture#1-Introduction To AIDana HowellNo ratings yet

- Understanding the HW/SW Interface <40Document8 pagesUnderstanding the HW/SW Interface <40Dana HowellNo ratings yet

- Preskill 2013 WeirdnessDocument2 pagesPreskill 2013 WeirdnessDana HowellNo ratings yet

- Book 2Document33 pagesBook 2Dana HowellNo ratings yet

- Sessional Two 2013Document3 pagesSessional Two 2013Dana HowellNo ratings yet

- Chapter 1 - Chapter 2 - Preskill "Quantum Computation"Document30 pagesChapter 1 - Chapter 2 - Preskill "Quantum Computation"_nimbleNo ratings yet

- Lecture#2Document21 pagesLecture#2Dana HowellNo ratings yet

- Indian Tex Users Group LaTex Tutorials - A Primer (Indian Tex User Grupo)Document155 pagesIndian Tex Users Group LaTex Tutorials - A Primer (Indian Tex User Grupo)Diego MorenoNo ratings yet

- VectorDocument4 pagesVectorDana HowellNo ratings yet

- ModuleDocument1 pageModuleDana HowellNo ratings yet

- Electron Beam LithographyDocument11 pagesElectron Beam LithographySaqib ZargarNo ratings yet

- B.Sc. Electronics Science syllabus (CBCSDocument58 pagesB.Sc. Electronics Science syllabus (CBCSmichaeledem_royalNo ratings yet

- Analysis and Design of Filament Power Supply With PDFDocument5 pagesAnalysis and Design of Filament Power Supply With PDFHoracio Dorantes ReyesNo ratings yet

- Sensitive Intruder Alarm CircuitDocument3 pagesSensitive Intruder Alarm CircuitChristopher OaresNo ratings yet

- Sikafume: Concrete AdditiveDocument3 pagesSikafume: Concrete AdditiveorgaNo ratings yet

- Corning Fused Silica 7980Document4 pagesCorning Fused Silica 7980Mandi IndarsNo ratings yet

- Garduino Geek GardeningDocument14 pagesGarduino Geek GardeningVLADAREANUCATALINDANIEL8726No ratings yet

- Design Rules-VlsiDocument9 pagesDesign Rules-VlsiPrabhat KumarNo ratings yet

- Ultra Compact High Voltage Power Supplies: SeriesDocument4 pagesUltra Compact High Voltage Power Supplies: SeriesHari NurcahyadiNo ratings yet

- Electronic CKT and Dig Lab ManualDocument55 pagesElectronic CKT and Dig Lab ManualSriramNo ratings yet

- Mr. S.C. Bansal: (Lecturer)Document96 pagesMr. S.C. Bansal: (Lecturer)Aizat RazakNo ratings yet

- LS800 eDocument124 pagesLS800 eVü PhämNo ratings yet

- 19-inch ASUS LCD Monitor with HDMI InputDocument82 pages19-inch ASUS LCD Monitor with HDMI InputAM76No ratings yet

- IGNOU - B.Sc. - PHE10: Electrical Circuits and ElectronicsDocument323 pagesIGNOU - B.Sc. - PHE10: Electrical Circuits and ElectronicsephuntNo ratings yet

- AN6780, AN6780S: General Purpose Long Interval TimersDocument4 pagesAN6780, AN6780S: General Purpose Long Interval TimersJuancaxp Pérez de AlejoNo ratings yet

- Ultra Fast Acting Electronic Circuit BreakerDocument6 pagesUltra Fast Acting Electronic Circuit BreakerHarish Kumar100% (1)

- CMOS Inverter Layout and Timing SimulationDocument5 pagesCMOS Inverter Layout and Timing SimulationAlif FirdausNo ratings yet

- Transistor HitachiDocument6 pagesTransistor HitachielgatolocoNo ratings yet

- CPUDocument8 pagesCPUUndefine HumanNo ratings yet

- Polin Multidrop Junior Fast Brochure (99999811680)Document2 pagesPolin Multidrop Junior Fast Brochure (99999811680)Ana Maria Marin100% (2)

- ISL9R860P2, ISL9R860S3ST: 8A, 600V Stealth™ DiodeDocument8 pagesISL9R860P2, ISL9R860S3ST: 8A, 600V Stealth™ DiodeManu MathewNo ratings yet

- CKTS 1: Experiment No. 1Document11 pagesCKTS 1: Experiment No. 1Andreana AmorNo ratings yet

- AC Voltmeter & OhmmeterDocument17 pagesAC Voltmeter & OhmmeterBatch 3No ratings yet

- Lanco 8.5 Mva GTP Rv.01Document14 pagesLanco 8.5 Mva GTP Rv.01Pankaj TiwariNo ratings yet

- Understanding Analog and Digital MultimetersDocument53 pagesUnderstanding Analog and Digital MultimetersUsman AhmadNo ratings yet

- Brother Compal Galaxie Sewing Machine Instruction ManualDocument81 pagesBrother Compal Galaxie Sewing Machine Instruction ManualiliiexpugnansNo ratings yet

- 0620 s05 QP 3Document30 pages0620 s05 QP 3G M Ali Kawsar100% (1)