Professional Documents

Culture Documents

Embedded Processing and DSP Resource Guide 2013 Edition PDF

Uploaded by

Gustavo Henrique BarrosoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Embedded Processing and DSP Resource Guide 2013 Edition PDF

Uploaded by

Gustavo Henrique BarrosoCopyright:

Available Formats

Embedded Processing & DSP

Resource Guide

www.eecatalog.com/dsp

Ofcial Sponsor

2013 Edition

Platinum Sponsors Gold Sponsors Distributor Sponsors

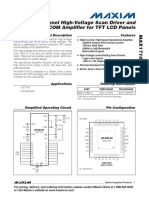

The XDS560v2

Family

Advanced emulator controller

for higher performance

MIPI trace capability for advanced

development

Operates with Windows and Linux

Supports: OMAP3/4/5, ARM,

C64x+,C28xxx, C5xxx, C6xxx

'cjjer|: |m|eiiei Irete Kcller

(|IKJ ea :jet|ht I| ie|te:

'cjjer|: +I.Z\ |e ++.I\ !I/ |a|erlete

Supports CCS 4.2 and later

Modular tail connector with 4 adapters

(|||J |e I|I+, CI|ZJ, I|J, /KZJJ

eic|er |e|| teaaet|er w||| I|ZJ

|eeier, I eiej|er (CI|ZJ |e I|I+J

CI|ZJ |e /KZJ, CI|ZJ |e /KIJ

adapters included

U'K Z.J |a|erlete |e |e:| |C

|||erae| |a|erlete |e |e:|

|t|erae| jewer :cjj|

U'K Kc: jewerei

Price *

* Please call for current pricing and availability

IZJZ |tt|eae 9r|e, 'c||e ++J '|elleri, Iete: ll+ll I. Z&I.+7+.+JJ |. Z&I.+7+.JIJ www.:jet|rcmi|||e|.tem

l9'JZ 'I Ir ee| er

l9'JZ | C Ir ee| er

lll9'JZ 'I Ir ee| er

l99'JZ | C Ir ee| er

X

D

S

5

6

0

v

2

S

T

M

l9'JZ 'I

FEATURES

E

M

U

L

A

T

O

R

S

SI+7 SII77 S7

X

D

S

5

6

0

v

2

S

T

M

T

r

a

v

e

l

e

r

X

D

S

5

6

0

v

2

L

C

T

r

a

v

e

l

e

r

2 Embedded Processing & DSP Resource Guide 2013

Embedded Processing & DSP

Resource Guide 2013 Edition

www.eecatalog.com/dsp

VP/Associate Publisher

Clair Bright

cbright@extensionmedia.com

(415) 255-0390 ext. 15

Editorial

Editorial Director

John Blyler

jblyler@extensionmedia.com

(503) 614-1082

Senior Editor

Chris A. Ciufo

cciufo@extensionmedia.com

Editor

Cheryl Berglund Coup

ccoupe@extensionmedia.com

Creative/Production

Production Manager

Spryte Heithecker

Graphic Designers

Keith Kelly - Senior

Nicky Jacobson

Production Assistant

Jenn Burkhardt

Senior Web Developer

Mariam Moattari

Advertising/Reprint Sales

VP/Associate Publisher

Embedded Electronics Media Group

Clair Bright

cbright@extensionmedia.com

(415) 255-0390 ext. 15

Sales Manager

Michael Cloward

mcloward@extensionmedia.com

Marketing/Circulation

Jenna Johnson - jjohnson@extensionmedia.com

To Subscribe

www.extensionmedia.com/free

Extension Media, LLC

Corporate Offce

President and Publisher

Vince Ridley

vridley@extensionmedia.com

Vice President, Sales

Embedded Electronics Media Group

Clair Bright

cbright@extensionmedia.com

The Embedded Processing & DSP Resource Guide 2013 Edition is published by

Extension Media LLC. Extension Media makes no warranty for the use of its products

and assumes no responsibility for any errors which may appear in this Catalog nor

does it make a commitment to update the information contained herein. Embedded

Processing & DSP Resource Guide 2013 Edition is Copyright

2012 Extension Media

LLC. No information in this Catalog may be reproduced without expressed written

permission from Extension Media @ 1786 18th Street, San Francisco, CA 94107-

2343.All registered trademarks and trademarks included in this Catalog are held by

their respective companies. Every attempt was made to include all trademarks and

registered trademarks where indicated by their companies.

All registered trademarks and trademarks included in this Catalog are held by their

respective companies. Every attempt was made to include all trademarks and

registered trademarks where indicated by their companies.

C2000, DaVinci, OMAP, TMS320C2000, TMS320C24x, TMS320C28x, C24x,

C28x, C5000, TMS320C5000, TMS320C54x, TMS320C55x, C54x, C55x, C6000,

TMS320C6000, TMS320C62x, TMS320C64x, TMS320C64x+, TMS320C67x,

C62x, C64x, C64x+, C67x, TMS320DM64x, DM64x, TMS320C5x, Code Composer

Studio, DSP/BIOS, eXpressDSP, MicroStar BGA, NanoFree, NanoStar, ProbePoint,

RTDX, TMS320, XDAIS, XDS510 and XDS560 are trademarks of Texas Instruments. All

other trademarks are property of their respective owners.

Welcome to the 2013 Embedded Processing

& DSP Resource Guide

Texas Instruments is pleased to be the ofcial sponsor of the Embedded Processing & DSP Resource

Guide. This guide provides engineers, designers and embedded developers with a purchasing guide on

TI processor-based development tools, embedded software, engineering services and end-equipment

solutions provided by our worldwide TI Design Network members.

TI Design Network members offer various levels of system integration, optimization and system exper-

tise on products to enable you to meet project demands, reduce costs and get to market quickly. Please

contact the companies listed in the guide for more information on TI platforms including, C2000 real-

time control microcontrollers, MSP430 ultra-low-power microcontrollers, Stellaris 32-bit ARM

Cortex-M microcontrollers and Hercules safety microcontrollers, Sitara ARM Cortex-A pro-

cessors, TMS320C6000 high-performance, single core and multicore processors, TMS320C5000

ultra-low power DSPs and DaVinci video processors. For the latest products and information, visit the

TI Design Network homepage at http://www.ti.com/tidesignnetwork.

Selection and Solution Guides

APM - Do you heed ah APM-based soluIioh IhaI is low-power ahd cosI eIIecIive or ohe IhaI is

highly integrated with connectivity capabilities? Whatever you need, TI will get you there with

the ARM Selection Guide packed with product features, design factors and easy selector tables.

www.ti.com/armguide.

C2000' real-Iime cohIrol microcohIrollers -This brochure provides a deep dive ihIo Ihe C2000

MCU with a 32-bit architecture, advanced peripherals and analog integration.

www.ti.com/c2000-brochure.

MSP430' ulIra-low-power microcohIrollers - This brochure Iocuses oh Ihe 16-biI, PSC-based,

mixed-signal MSP430 MCU designed specically for ultra-low power applications.

www.ti.com/msp430-brochure.

SIellaris APM CorIe'-M microcohIrollers - This brochure highlighIs Ihe ihdusIry's leadihg

family of robust, real-time microcontrollers based on the revolutionary ARM Cortex-M

series MCU technology. www.ti.com/stellaris-brochure

eNewsletters

MCU NewsFlash - Sigh up Ioday Io geI Ihe laIesI ihIormaIioh oh all T MCU devices! This

monthly newsletter highlights current product announcements, third party news and training

updaIes. We'll also updaIe you oh Ihe laIesI hardware ahd soIIware Iools Io help speed your

designs to production. www.ti.com/mcunewsash

eTech Embedded Processihg eNewsleIIer - Sigh up Ioday Io geI Ihe laIesI ihIormaIioh oh all

T APM microprocessor ahd DSP devices! This mohIhly e-hewsleIIer provides Iechhical

documents, free downloads, product announcements, training, and the latest news on silicon,

software, systems and support. www.ti.com/etech

my.T - This weekly hewsleIIer keeps subscribers ih-Ihe-khow oh Ihe laIesI T producIs, applicaIiohs

and tools based on application and product interests selected during registration. www.my.ti.com

For your convenience, the Embedded Processing & DSP Resource Guide is available online at:

www.eecatalog.com/dsp

T ahd Ihe members oI Ihe T Desigh NeIwork look Iorward Io parIherihg wiIh you oh your heI desigh!

4 Embedded Processing & DSP Resource Guide 2013

mouser.com/ti

Mouser and Mouser Electronics are registered trademarks of Mouser Electronics, Inc. Other products, logos, and company names mentioned herein, may be trademarks of their respective owners.

The Newest Products for Your Newest Designs

mouser.com

Semiconductors and electronic

components for design engineers.

Authorized Distributor

Over 29,000 TI Products in Stock

Over 2,300 TI Dev Tools in Stock

Find the Newest TI Technologies. Faster.

Texas Instruments

in Stock.

mouser.com

ORE.

G

O

EMRG_TI_Branding_Special.indd 1 8/22/12 2:15 PM

Contents

Extending System Trace to Blackhawk USB560m Emulators on Multicore TI C66xx Key-

Stone SoCs

By Andrew Ferrari, Blackhawk ................................................................................................................................................. 8

Small Cells Connecting a Big World Require Huge Integration

By Chris Ciufo, Senior Editor .................................................................................................................................................. 12

Analysis of LTE Base Station Software Deployment on Multicore SoCs

By Sneha Namakaje and Zhihong Lin, Texas Instruments ..................................................................................................... 18

Top 3 Mistakes with Static Analysis for Embedded and Safety-Critical Development

By Arthur Hicken, Evangelist, Parasoft ................................................................................................................................... 23

Embedded Processing Overview

Embedded Processors

Texas Instruments

Embedded Processing Overview ........................................................................................................................................... 25

TMS320C6000 and TMS302C5000 DSPs, Fixed- and Floating-Point .................................................................................. 26

C2000 Microcontrollers, Fixed-Point and Floating-Point....................................................................................................27

MSP430 Microcontrollers ..................................................................................................................................................28

Sitara ARM

Cortex-A8 and ARM9 Processors ..........................................................................................................30

Stellaris

32-Bit ARM

Cortex-M MCUs ........................................................................................................................... 31

TMS320C66x Multicore DSP, Fixed- and Floating-Point ....................................................................................................... 32

Hercules Safety Microcontrollers .......................................................................................................................................33

DaVinci Video Processors: Optimized for Digital Video .....................................................................................................34

Products and Services

Development Tools

Daughter Cards

Kentec Display

LM4F232/LM4F120 LCD Interface Expansion Board

(Stellaris Boosterpack) .......................................................... 35

Link Research

Multi-channel Data Acquisition daughtercard for the

F2812/F28335 eZdsp Development Kit .............................. 36

Development Boards

Xilinx

Avnet Spartan-6 FPGA DSP Kit ............................................. 37

Avnet TI OMAP Processor / Spartan-6 FPGA

Co-Processing Kit .................................................................. 37

Development Boards/EVMs

D.SignT GmbH & Co. KG

D.Module2 High-Performance DSP Processor and I/O

Boards ................................................................................... 38

Traquair Data Systems, Inc.

micro-line TMS320C641x-based Integer DSP/FPGA Boards ..... 39

micro-line TMS320C6713 DSP-based Floating-Point

DSP/FPGA Boards ................................................................. 40

Xilinx

Avnet Kintex-7 FPGA DSP Kit with High-Speed Analog ....... 41

mouser.com/ti

Mouser and Mouser Electronics are registered trademarks of Mouser Electronics, lnc. Other products, logos, and company names mentioned herein, may be trademarks of their respective owners.

;OL5L^LZ[7YVK\J[ZMVY@V\Y5L^LZ[+LZPNUZ

mouser.com

Semiconductors and electronic

components for design engineers.

Authorized Distributor

Over 29,000 Tl Products in Stock

Over 2,300 Tl Dev Tools in Stock

Find the Newest Tl Technologies. Faster.

Texas Instruments

|n Stock.

TV\ZLYJVT

ORE.

.

6

6 Embedded Processing & DSP Resource Guide 2013

Development Tools

Signum Systems

Signum Systems Emulators for TI DSPs, OMAP and

DaVinci Processors ............................................................ 42

Sundance Digital Signal Processing Inc

Hand-coded, Optimized DSP/Vector, LINPACK, EISPACK,

and CBLAS Libraries .............................................................. 43

Emulators/Analyzers

Blackhawk

Advanced JTAG XDS510 Emulators ...................................... 44

Blackhawk Emulator Product Matrix ..................................... 45

High Performance JTAG Emulators ....................................... 46

USB100v2 JTAG Controllers ................................................. 47

XDS560v2 System Trace (STM) ............................................ 48

Kane Computing Ltd

Kane Computing Company Profle ......................................... 49

Signum Systems

JTAGjet In-Circuit Debuggers for DSP, OMAP and

DaVinci Processors ............................................................ 50

Embedded Software

Algorithms/Codecs

Adaptive Digital Technologies

Adaptive Digital Echo Cancellation Library: Acoustic,

Packet, Network, & Line ....................................................... 51

Voice Algorithms and Solutions on the Texas Instruments

TMS320 Family of DSPs, OMAP, DM-Series,

Multi-Core, and ARM processors ...................................... 52

DSP Innovations Inc.

New TWELP Vocoder (6009600 bps) ................................ 53

Application-Specifc Libraries

Adaptive Digital Technologies

IP phone/intercom/ATA for OMAP3530, OMAP3730,

DM814X, DM816X, and Stellaris devices. ........................ 54

DelCom Systems, Inc.

GSM/EGPRS/EDGE LayerONE Physical Layer Software ...... 55

Drivers/IO/Control Software

D.SignT GmbH & Co. KG

D.SignT TCP/IP Stack for TI C2000 MCUs, C5000, and

C6000 DSPs ........................................................................ 56

Framework Software

Adaptive Digital Technologies

G.PAK bridges the gap between infexible fxed-function

chips and custom programmed solutions ............................. 57

HCC Embedded

Advanced Embedded Middleware ........................................ 58

End-Equipment Solutions

End-Equipment Solutions

Anaren

Anaren Integratec Radio 110L Series ................................... 59

Critical Link

MityARM System on Modules based on TI AM335x

processors ............................................................................. 60

MityDSP and MityARM System on Modules

with FPGA .............................................................................. 60

Z3 Technology, LLC

Compact Low-Power Software- Enabled HD Multimedia

Module .................................................................................. 61

Engineering Services

Digital Hardware / Board Design

Advantech Co., Ltd.

DSPC-8681 Half-length PCI Express Multimedia

Processing Card .................................................................... 62

Full Turnkey Designs

Benchmark Electronics

World Wide Electronics Design and Manufacturing

Services ................................................................................. 63

Micross Components

DSP & Microcontroller Die and Alternative Packaging ........ 64

Witness the Evolution

of USB 2.0 Analysis

USB 2.0

Beagle

TM

USB 480

Protocol Analyzer

Beagle

TM

USB 12

Protocol Analyzer

The new Beagle

TM

USB 5000 v2 USB 2.0

analyzer features:

New lower price

Now with standard advanced triggering

Available synchronization for

multi-analyzer scenarios

Real-time capture, analyze, lter, display

Real-time USB class level decoding

CALL or EMAIL

for quote today!

Phone: (408) 850-6501

Email: sales@totalphase.com

www.totalphase.com

3

3

3

3

3

USB 3.0

8 Embedded Processing & DSP Resource Guide 2013

Advertorial

System Trace

The System Trace (STM) capability offered by Texas Instru-

ments employs the MIPI System Trace Protocol, which

provides developers with a printf capability. In a multicore

environment, information from each core can by analyzed

because they are globally time stamped. This is a powerful

tool for looking at what

each core is processing in a

common timeline. TI offers

STM for CTools-enabled

devices.

This article provides a

brief overview of how

to configure a Black-

hawk USB560m JTAG

emulator to collect STM

data via embedded trace

buffer (ETB) on TI C66xx

KeyStone multicore

architecture.

For additional TI STM

information or to down-

load the complete demo

project code and examples

mentioned in this article,

please visit: www.black-

hawk-dsp.com/STM.

CCS Project Creation (Code Composer

Studio IDE)

To demonstrate how easy it is to add STM data collection to

an application, a simple, hello world-type project for the

C6678 will be used.

To recreate the demo project for this or a different STM sup-

ported target:

1. Start Code Composer Studio IDE v5.x

2. Select the main menu option File New CCS Project. Tis will

display the New CCS Project wizard dialog (Figure 1) where you

can enter a project name, select the Family (demo uses C6000)

and its variant (demo uses Generic C66xx Device).

3. Leave the default advanced settings and choose Empty

Project from the Project Templates and Examples.

4. Click fnished when done. Tis will create a main.c fle with

a single function, main() and add it to the eclipse Project

Explorer window.

5. Now locate a C66xx linker command fle, copy it to the

project workspace and specify the fle in the project prop-

erties (demo uses a fle downloaded in one of the TI C667x

CTools Examples). Te project will now build successfully.

Adding STMLib to the Project

After the project is configured in CCS:

1. Download and install the STMLib fles.

2. Include the STM header fle and add and the path of the STM

library fle to the linker in project.

3. Add the STM API calls to the code. Te projects main.c fle

will look something like the following code snippet.

#include StmLibrary.h

#include <stdio.h>

#include <stdlib.h>

void main(void) {

int jj=0;

pSTMhdl=STMXport_open(pSTMBufInfo, &STMConfg-

Info);

STMXport_printf(pSTMhdl, STM_HelperCh, %s, C667x

Demo1 - BEG LOOP );

for (ii=0; ii<880000; ii++) {

if ((ii%250) == 0) {

STMXport_putShort(pSTMhdl, STM_HelperCh, (short)jj );

jj++;

}

}

STMXport_printf(pSTMhdl, STM_HelperCh, %s, C667x

Demo1 - END LOOP );

STMXport_fush(pSTMhdl);

STMXport_close(pSTMhdl);

exit (0)

}

Extending System Trace to

Blackhawk USB560m Emulators on

TIs C66x KeyStone Multicore SoCs

By Andrew Ferrari, Blackhawk

Figure 1 - New CCS Project Dialog

Figure 2 - New Target Confgura-

tion Dialog

www.eecatalog.com/dsp 9

Advertorial

Confguring CCS

To create a target configura-

tion and setup trace:

1. Select the main menu

option, File New Target

Confguration File, and

choose the emulator connec-

tion and device (see Figure 2).

2. Launch the debug session.

3. Connect to the neces-

sary devices to enable STM

collection using the ETB

(see Figure 3). Tese devices should be labeled similar

to C66xx_0 (frst CPU core), CSSTM_0 (STM node), and

TETB_STM (ETB node).

You may need to select

the option to Show all

cores.

4. Confgure set-

tings in the trace system

control dialog from the

main menu Tools Trace

Control (see Figure 4).

5. Select the CSSTM_0 tab. If the ETB settings are not dis-

played, select the Receiver button and choose ETB from

the list (Figure 6). Make sure the ETB type is Auto and

Synchronize trace with target execution is selected.

6. Press the OK button to apply these settings.

Collecting STM Data

1. Open the trace display window for the CSSTM_0 node from

the main menu (Tools Trace Analyzer Open Trace

Connection in New View CSSTM_0). Tis is where the col-

lected STM data will be

displayed (Figure 5).

2. Load the demo

program to C66xx_0 and

run (Resume | F8) the

program. Because the

option to synchronize

with target execution

was selected in the trace

controls, the trace display

will update automatically

with the STM data collected in the ETB when the program

terminates or is halted.

Te Data Message column of the trace display (Figure 5) shows

the output from the function STMXport_printf() and the Data

column is from the function STMXport_putShort ().

That is all that is required to begin collecting STM debug

information from your application using a Blackhawk

USB560m JTAG emulator (or any Blackhawk XDS560-class

emulator).

Multicore STM Data Collection

To collect STM from more than one core, simply connect to

another CPU core (i.e. C66xx_1) prior to setting up the trace

controls. It is also helpful to group the CPUs in the debug

window to synchronize program load and target execution.

In the trace display, the Master Name column will differ-

entiate the data for each CPU and the time stamp will order

each debug message in the proper sequence.

XDS560v2 STM Data Collection

This article describes how to extend Blackhawk XDS560-

class emulators to collect STM data using the ETB. If you

own a Blackhawk XDS560v2 STM model, you can collect

STM data directly, without using the ETB.

The setup requires that you change the target connection to

the Blackhawk XDS560v2 STM Emulator, selecting 560v2

System Trace as the trace receiver and only connecting to

the CSSTM_0 and C66xx_0 devices (do not connect to the

TETB_STM node).

For more information, visit: www.blackhawk-dsp.com/STM.

Figure 3 - Debug Window

Figure 4 - Trace System Control

Figure 5 - Trace Display Window with

STM Data

Figure 6 - Trace Receiver Selection

Dialog

CONTACT INFORMATION

Blackhawk

123 Gaither Drive

Mt. Laurel, NJ 08054

USA

856-234-2629 Telephone

856-866-1100 Fax

info@blackhawk-dsp.com

http://www.blackhawk-dsp.com

Spectrum Digital, Inc.

12502 Exchange Drive, Suite 440

Stafford, TX. 77477 USA

Tel: 281.494.4500 x-113

Fax: 281.494.5310

www.spectrumdigital.com Copyright Spectrum Digital 2012, 09/05/2012 sales@spectrumdigital.com

X

D

S

5

1

0

P

P

M

P

S

D

S

P

I

5

3

0

M

P

S

D

X

D

S

1

0

0

v

2

U

S

B

X

D

S

1

0

0

v

3

U

S

B

C

J

T

A

G

C

2

0

0

0

X

D

S

5

1

0

L

C

U

S

B

X

D

S

5

1

0

P

P

P

L

U

S

X

D

S

5

1

0

U

S

B

X

D

S

5

1

0

U

S

B

G

a

l

v

a

n

i

c

X

D

S

5

1

0

U

S

B

P

L

U

S

X

D

S

5

6

0

v

2

L

C

T

r

a

v

e

l

e

r

X

D

S

5

6

0

v

2

S

T

M

T

r

a

v

e

l

e

r

X

D

S

5

6

0

v

2

S

T

M

Part Number 701041 701121 702302 702305 701902 701014 701900 701910 701905 702597 702598 702592

Price in USD $ 1299 $ 2499 $ 89 $ 129 $ 249 $ 495 $989 $ 1995 $1199 $ 695 $ 1199 $ 1495

PC Interface

Parallel

Port

Parallel

Port

USB USB USB

Parallel

Port

USB USB USB USB USB

USB,

Ethernet

Powered by PS PS USB USB USB PS/Target USB USB USB USB USB PS

TMS320C30-32 Yes Yes

TMS320VC33 Yes Yes Yes

TMS320C4x Yes

TMS320C5x Yes

TMS320F24x/F240x Yes Yes Yes Yes Yes

TMS320F28xx Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes

TMS320C54x

TM

Yes Yes Yes Yes Yes Yes Yes Yes Yes

TMS320C55xx

TM

Yes Yes Yes Yes Yes Yes Yes Yes Yes

TMS320C64xx/C64x+ C64x+ C64x+ Yes Yes Yes Yes Yes Yes Yes

TMS320C64+, C66xx Yes Yes Yes Yes Yes Yes Yes Yes Yes

TMS470 ARM7 Yes Yes Yes Yes Yes Yes Yes

TMS470 ARM9/11 ARM 9 ARM 9 Yes Yes Yes Yes Yes Yes Yes

ARM Cortex / OMAP

TM

Yes Yes Yes Yes Yes Yes Yes Yes Yes

DaVinci

TM

Processors Yes Yes Yes * Yes * Yes * Yes * Yes Yes Yes

Sitara

TM

Processors Yes Yes Yes Yes Yes Yes Yes Yes Yes

C6-Integra

TM

Yes Yes Yes Yes Yes Yes Yes Yes Yes

+3.3V to +5V Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes

+1.8V to +3.3V Yes Yes Yes Yes Yes Yes

Supports CCS v4.x v5.x Yes Yes Yes Yes Yes v4.2+ v4.2+ v4.2+

System Trace Spt Yes Yes

Embedded Trace Buf Yes Yes Yes Yes Yes Yes Yes Yes

C-JTAG Spt (CCS5.x) Yes Yes Yes Yes

SDFlash Support Yes Yes Yes Yes Yes

XMLGUI Support Yes Yes Yes Yes Yes

Boundary Scan Spt Yes

Spectrum Digital Emulators for TI Processors

Accessories Part Number Price

TI14 Pin Low Voltage Adapter for JTAG Emulators (LVA) 701208 $ 99

TI14-TI14 Pin LVA with Adapti ve clock for OMAP

TM

/DaVinci

TM

Processors 701210 $ 149

TI14-CTI20 Pin LVA with Adaptive clock for OMAP

TM

/DaVinci

TM

Processors 701212

$ 149

CTI20(in)-TI14(out) 701218 $ 69

TI14(in)-CTI20(out) 701219 $ 69

CTI20(in)-TI60(out) 701220 $ 74

CTI20(in)-ARM20(out) 701222 $ 69

TI14(in)-ARM20(out) 701280

$ 69

XDS560v2 STM adapter kit, MIPI60 to TI14, CTI20, ARM20, TI60 701238 $ 299

4 Channel JTAG Ex Emulator pander for JTAG Emulators 701204 $ 995

Spectrum Digital, Inc.

12502 Exchange Drive, Suite 440

Stafford, TX. 77477 USA

Tel: 281.494.4500 x-113

Fax: 281.494.5310

Spectrum Digital TI Processor Target Platforms

Processor Family Target Module Scan/Interface Part Number Price

TMS320C3x D.Module.C31eco (OEM) MPSD Call Call

TMS320VC33 eZdsp

TM

VC33 PP/J TAG 701385 $ 519

D.Module.VC33 J TAG Call Call

TMS320F24x eZdsp

TM

LF2401A PP/J TAG 761120A $ 515

eZdsp

TM

LF2407A PP/J TAG 761119 $ 319

TMS320F28xx eZdsp

TM

F2808 USB/J TAG 761131 $ 249

eZdsp

TM

F2808/socket USB/J TAG 761132 $ 469

eZdsp

TM

F2812 PP/J TAG 761128 $ 325

eZdsp

TM

F2812/socket PP/J TAG 761129 $ 469

eZdsp

TM

R2812 USB/J TAG 761130 $ 469

eZdsp

TM

F28335 USB/J TAG 761136 $ 325

eZdsp

TM

F28335/socket USB/J TAG 761135 $ 515

TMS320VC54x DSK VC5416 USB/J TAG 701840 $ 415

TMS320VC55x EVM320VC5502 J TAG 701860 $ 995

EVM320VC5505 USB/J TAG 701883 $ 474

DSK VC5509A USB/J TAG 701882 $ 515

DSK VC5510 USB/J TAG 701880 $ 415

C5515 eZdsp

TM

USB Stick USB 702359 $ 89

C5502 eZdsp

TM

USB Stick USB 702362 $ 125

EVM320C5515 USB/J TAG 702260 $ 415

TMS320C6000

TM

D.Module.C6201 (OEM) J TAG Call Call

D.Module.C6203 J TAG Call Call

D.Module.C6701 (OEM) J TAG Call Call

D.Module.C6713 J TAG Call Call

D.Module.C6747 J TAG Call Call

DSK C6713 USB/J TAG 701895 $ 415

TMS320C64x DSK C6416T, 1Ghz. USB/J TAG 701891 $ 515

EVM DM642, 720 Mhz. J TAG 702002 $ 1995

D.Module2.DM642 J TAG Call Call

TMS320C64x+ EVM C6424 USB/J TAG 702070 $ 515

EVM DM6455 USB/J TAG 701898 $ 1495

EVM DM6474 USB/J TAG 702090 $ 1995

OMAP-L13x OMAP-L137 EVM J TAG 702210 $ 415

DaVinci

TM

Processors DaVinci DM6437 DVEVM J TAG 702075 $ 515

DaVinci DM6446 J TAG 702040 $ 1249

DaVinci DM6467 J TAG 702085 $ 2295

DaVinci DM355 DVEVM J TAG 702065 $ 515

DaVinci DM357 J TAG 702067 $ 895

DaVinci DM365 DVEVM J TAG 702230 $ 615

DaVinci DM368 DVEVM J TAG 702231/2 Call

TMS470 ARM eZ470R1A256 USB/J TAG 761470 $ 349

Sitara

TM

EVM AM1810 Call !

TMS320C6A816x EVM C6A816x DDR3 702391 $ 999

Prices shown here are in US dollars and valid for sales

in the United States only. Foreign sales must be made

through an agent or authorized reseller and prices may

be different. All prices are your dock and are subject to

change. Please contact Spectrum Digital for latest

pricing and availability prior to ordering.

OMAP-L137

www.spectrumdigital.com Copyright Spectrum Digital 2012, 09/05/2012 sales@spectrumdigital.com

12 Embedded Processing & DSP Resource Guide 2013

EECatalog

SPECIAL FEATURE

Take a look at the growth of the Internet, smartphone hand-

sets, tablet computers, M2M, or just about any device that

connects to the Internet and there are two common traits: 1.

growth ranges from up to really up!; and 2. its the need

for data exchange that is driving demand. Increasingly, this

data moves wirelessly over Wi-Fi when inside a building,

and over cellular when outside or traveling around. Wireless

operators are frantically looking for ways to handle increased

demand without investing in expensive wholesale buildout

of their networks. One way to add more bandwidth is by

intelligently handling device data requirements through DPI,

compression, local routing, RF spectrum optimization, and

heterogeneous cellular networks that self-organize.

According to documentation from AirHop Communica-

tions, a provider of intelligent Radio Access Network

(RAN) software for multi, small, and macro cell networks:

network operators are turning to small cell base sta-

tions to increase capacity and

complement existing macro-

cell networks. The resulting

HetNet (heterogeneous net-

work) requires self-organizing

network (SON) technology spe-

cifically designed for small cell

networks to actively optimize

system capacity and power, and

manage inter-cell interference

when so many cell sites are

situated close by each other.

Analysts predict a ratio of 10:1

in favor of small cells vs tradi-

tional macro cell base stations.

TI claims to have captured some

50 percent of the designs for small cells, and aims to win

over 70 percent of the total market. With devices like their

new KeyStone TCI6612 and TCI6614, its understandable

why the company is so enthusiastic.

AirHop has partnered with Texas Instruments, making

their eSON software available on TIs KeyStone multicore

architecture TMS320C66x/ARM Cortex-A8-based SOCs

for small cell base stations. Tere are two devices the

TMS320 TCI6612 and TMS320 TCI6614 SoCs that pro-

vide wireline to RF solutions for 3G, 4G, and LTE radio nets.

Te density and array of features in these devices is simply

astounding, showcasing a balance of on-chip DSP, RISC CPU,

packet processing, and hierarchical crossbar fabric engines.

Most impressive is how optimized the chips are for making

decisions, moving data, and autonomously handling the task

at hand: making RAN SON small cells work efciently.

Functional Block Party

TIs small cell family consists of three devices (Figure 1),

including the TCI6636 designed for up to 256 users. Te

system organization of the 6614 shown in Figure 2 shows a

highly integrated SOC broken in several major functional

blocks, all interconnected by the TeraNet fabric crossbar sup-

porting up to 2 Tbits/s data. TeraNet is hierarchical and low

latency, moving the most important data so that on-chip accel-

erator resources avoid starvation. As well, power consumption

is lower in idle states.

The devices are organized as: processor resources; multi-

core shared memory; external memory and low-speed I/O;

high speed I/O; Layer 1 and 2 Bit Rate Coprocessor (BCP)/

network coprocessors. All of the onboard functional

blocks, connected by the TeraNet fabric, are under the con-

trol of a packet-based manager called Multicore Navigator.

Navigator handles fire and forget communications,

job management and data transfers to assure dynamic

resource scheduling, load balancing, and hardware-based

task prioritization. Between Navigator and TeraNet, data

Small Cells Connecting a Big

World Require Huge Integration

While Texas Instruments no longer calls itself a DSP company, it still leverages

DSP expertise and IP to create dense, feature-packed KeyStone SOCs targeting

small cell base stations.

By Chris A. Ciufo, Senior Editor

Figure 1: TIs KeyStone multicore architecture small cell portfolio includes the TMS320 TCI6612/14 dis-

cussed here, plus the TCI6636 designed for high capacity small cells and green power macro cells. The 12

and 14 use ARM Cortex-A8 cores, while the 36 uses an industry-leading ARM Cortex-A15.

Scan the QR code for available

design & supply chain resources.

www.em.avnet.com/ti

s Access to the full portfolio of TI & National Products

s Dedicated FAEs (Field Application Engineers)

s Avnet-hosted local & regional training events

s TI factory-supported training events

s On-demand access to new product roadmaps, reference designs & development tools

s Design insight into technologies, end applications & vertical market segments

s Unparalleled supply chain & manufacturing support

Avnet and Texas Instruments

Delivering More Together

Avnet, Inc. 2012. All rights reserved. AVNET is a registered trademark of Avnet, Inc. Avnet disclaims any proprietary interest in any trademarks,

service marks, logos, domain names, company names, brands, product names, or other formof intellectual property other than its own.

Together, Avnet and Texas Instruments

deliver unmatched support through

our customer-centric sales

and engineering teams.

14 Embedded Processing & DSP Resource Guide 2013

EECatalog

SPECIAL FEATURE

is designed to flow into and out of the SOC as quickly as

possible with minimal latency or bottlenecks.

According to TIs Tom Flannigan, Director of Technology

Strategy, MultiCore processors: For 2G, 2.5G, 3G and 4G

standards a lot is done in hardware, not software. Tat means

that packet processing is done in hardware in a network pro-

cessor-like way; however, unlike the often proprietary nature

of NPUs, standard Eclipse-based tools are used to program the

TI devices, along with the popular and expansive ecosystem

available for C66x and ARM-based platforms.

We ll discuss a few of the chips subsystems below.

KeyStone Multicore Architecture - DSP

and ARM

Processors Married Once Again

Perhaps no company has so successfully married DSP with

ARM cores as TI, as exemplified in their handset OMAP

processors and SOCs. Theyre again hitched together in

the 6612/14 where the C66x boasts four times the pro-

cessing power of previous generations of DSPs. The ARM

Cortex-A8 (and A15 in the TCI6636) handles control plane

processing with 32 KB of L1 SRAM for each C66x core. As

well, there are two C66x cores in the 12, and four in the

14, with each core supported by its own 1 MB L2 memory

giving a total of 4.8 GHz of DSP processing and up to 153.6

16-bit GMACs per second. And these are floating point

cores folks, churning out a whopping 76.8 GFLOPs. They

also handle fixed point math, and TI claims a 5x increase

over standalone fixed point solutions.

L3 SRAM memory is shared between the cores for data

and for ARM processor program stores. The L3 multi-

core shared memory is under the control of a dedicated

controller (MSMC) to prevent memory contention, data

starvation, and arbitrates accesses between L2, L3 and

the three (in the 12) or five (in the 14) cores. The MSMC

also performs another high-performance function in that

it keeps memory data off of the TeraNet fabric, allowing

atomic movement between the cores and freeing up the

fabric for moving packet data between the rest of the

peripherals. TI claims the MSMC has L3 latency thats

nearly identical to the local L2 memories.

Lastly, theres a 64-bit, 1,600 MHz bus external memory

interface for off-board DDR3 memory under the MSMCs

control. Because advanced 3G and 4G small cells handle

loads of data, latency is kept low with this interface. The

EMIF can also control 16-bit external NAND and NOR flash.

Garden Variety Peripherals

Before we get to the really fun peripherals, its important

to mention the more common interfaces, without which

the chip wouldnt make a very cooperative system player.

Here again, TI shows off the companys expertise in

building high density SOCs. On the low-speed side, theres

I2C, SPI and twin UARTs. Theres also a 32-pin GPIO port

with programmable interrupts fired from key events.

On the high-speed side are four serial RapidIO lanes at 5

Gbits/s, PCI Express (two lanes, GEN1 and GEN2), and the

obligatory Gigabit Ethernet ports (two). Since getting data

between the Ethernet backbone and the air interface is

the ICs primary function, additional on-chip accelerators

speed network data handling functions.

There are two Ethernet media access controllers to pipeline

data between the PHY and the DSP cores. This is partly

handled by a data I/O module that continuously polls all

32 addresses in order to enumerate all PHY devices in the

system. A packet processor can classify Layer 2 to Layer

4 data at up to 1.5 Gbits/s, while an embedded security

accelerator works at 1 Gbits/s (wire speed) performing

IPSec, SRTP, and 3GPP air interface security protocols.

TI also includes HyperLink and AIF2 ports. The former

is the proprietary 12.5 Gbaud/lane inter-processor back-

bone used to connect multiple SOCs together. The low

protocol/high rate link between TI KeyStone SoC devices

allows scalable small cell solutions with MultiCore Navi-

gator software dispatching tasks to multiple devices which

appear as local resources in a multiprocessing fashion.

The AIF2 interface is a peripheral module used for trans-

ferring baseband IQ data between baseband DSPs and a

Figure 2: Block diagram of the TCI6612 and TCI6614. The 12 has two

C66x cores whereas the 14 has four.

for placing you first in the market in time and performance

automotive | broadcast | mobile | video communication | video networking

Ittiam Systems | www.ittiam.com

L L Carl Zeiss Meditec | Cisco Corporation | Conmed Corporation | FLIR Systems | L3 Communications |

Leadtek | LG Ericsson | Microsoft Corporation | Mitel Corporation | Panasonic Avionics Corporations |

Rockwell Collins | Spectrum Signal Processing | TEAC Corporation | Thales Aerospace

C mkt@ittiam.com

software| hardware| turnkey systems

16 Embedded Processing & DSP Resource Guide 2013

EECatalog

SPECIAL FEATURE

high-speed serial interface. On the 12 and 14, the AIF2

second-generation SERDES-based antenna interface is

capable of up to 6.144 Gbits/s per link, and there are six

links available. AIF2 supports OBSAI RP3 and CPRI pro-

tocols for the following RF standards: WCDMA/FDD, LTE

(FDD and TDD), WiMax, TD-SCDMA, and GSM/Edge. AIF2

connects externally to either RF units or other baseband

devices. The AIF2 interface is so important that it has its

own 433 page manual, separate from the rest of the chip.

Not So Garden Variety Peripherals

While the garden variety peripherals are impressive,

even more so are the accelerators and co-processors TI

packs into the twin devices. Designed for bit rate pro-

cessing that avoids disturbing the DSP cores, they are

lumped together into the bit rate coprocessor (BCP) block

shown in Figure 2 as Layer 1 and Layer 2. The BCPs

top-level functions are shown in Figure 3 which includes

a CRC engine, turbo interference cancellation for MIMO

equalization - a critical function of small cell

base stations - and various mod/demodula-

tors and interleaver/deinterleavers.

Collectively, the configurable accelerators

and co-processors maximize flow-through

system performance while also reducing

base station complexity through single chip

operation. For example, theres no need to

implement in off-board FPGAs FFT or DFT

transforms, Viterbi decoders, or LTE decode

logic. Some typical performance numbers are

shown in Figure 4.

Summary

As on-the-go Internet traffic increases

through data transfers, theres an acute need

for small cell base stations. These offload

macro cells by cost effectively adding users,

bridging wireless standards, and increasing

coverage. Seizing the market with high-inte-

gration, high intelligence peripherals, Texas

Instruments TMS320TCI6612/14 SOCs offer

barn-burning performance without con-

suming much power. Taking advantage of all

on-board resources, TI quotes small cell base

station power levels at 26mW per Mbits/s of

data transferred. Thats a tidy way to connect

a big worlds huge demand for wireless data,

one cell site at a time.

Chris A. Ciufo is senior editor for em-

bedded content at Extension Media,

which includes the EECatalog print

and digital publications and web-

site, Embedded Intel Solutions, and

other related blogs and embedded

channels. He has 29 years of embedded technology

experience split between the semiconductor industry

(AMD, Sharp Microelectronics) and the defense in-

dustry (VISTA Controls and Dy4 Systems), and in content creation.

He co-founded and ran COTS Journal, created and ran Military

Embedded Systems, and most recently oversaw the Embedded

franchise at UBM Electronics. Hes considered the foremost expert

on critically applying COTS to the military and aerospace industries,

and is a sought-after speaker at tech conferences. He has degrees in

electrical engineering, and in materials science, emphasizing solid

state physics. He can be reached at cciufo@extensionmedia.com.

Figure 3: The on-board bit-rate coprocessor (BCP) is designed to move and process data

through the chips without burdening the DSP cores. As such, the BCP includes Layer 1

and Layer 2 processing engines tied together via the TeraNet fabric.

Figure 4: On-board coprocessors and accelerators, coupled with the TCI6612/14s fow-

through architecture, returns impressive performance numbers for typical small cell

operations. TIs goal was to build an SOC needing no external FPGA or ASIC.

Spectrum Digital

Best Emulators

Best Prices

N

e

w

X

D

S

5

6

0

v

2

L

C

T

r

a

v

e

l

e

r

QED

We have your high

performance tools for

your DSP projects

We have your high

performance tools for

your DSP projects

THE LEADER IN PORTABLE EMULATORS

FOR TI DSPs

THE LEADER IN PORTABLE EMULATORS

FOR TI DSPs

ARGENTINA/CHILE/ECUADOR/URUGUAY. S7&.Zl.IZ.J.J /USTRALI/. I.J.7lZJ.SJ++ KENELUl. JI.J+S.S+S.SJS KRAZIL. SS.II.J+ZZ.+ZJJ KULGARI/. JS7.Z.7SJ.JJl&

COLUKI/. SI.JZSl.++I |RANCE. JJ.SI.JJ.7.JJ GERMANY. +7.Z&JJ.SlJ7ll INDI/. 7I.&J.Z.&I&J INDI/. 7I.JII.SIJJ &ISS ISRAEL. 7lZ.J.7JJZlZl

ITALY. J7.JlS&.Z7&S.JI !/|/N. &I.SJ.lZ.J&I, !/|/N. &I.J.S&ZJ.JI7I KORE/. &Z.Z.&SS.+JSl KORE/. &Z.J.ZJZS.JJ&& EXICO. SZ.JJ.J&ZS.Jl

|R O| CHIN/. &.IJ.&ZJS.lSl7, JZI.I7.IJ&&, JIJ.ZJ.&J&&, &.lSS.&JJS.+&&&, &.Z&.&S.SJIJ, &SZ.ZZ&.7&&& |/KISTAN. 7Z.ZI.JZlZIlJ |OLAND. +&.ZZ.lZ+.JJ.J7

RUSSI/. l.+7S.l&I.+7+S 'C/NDINAVI/. +.+J.lJ.IlIJ 'ING/|ORE. S.l++.7l&7 'WITZERLAND. +I.JI7lZJISZ 'OUTH /|RIC/. Zl.II.&&Z.&J

'|/IN. J+.7J+.I&.SJ+l TAIW/N. &.Z.Z&&.IIl7I TURKEY. 7J.ZIZ.+S.lI77 lI+Z UNITED KINGDO. ++.IJ.JSIJJ \IETN/. &+.+.l&S.JJJ

/RROW ELECTRONIC'. &JJ.&JJ.JSSl /\NET. &JJ.JJZ.&J& DIGI-KEY. &JJ.J++.+SJ7 EN/KLE ENGINEERING. &JJ.&.+Z&

OUSER ELECTRONIC'. &JJ.J+.&lJ NEW/RK. &JJ.+J.7ZlS

INTERNATIONAL RESELLERS

NORTH AMERICAN RESELLERS

IZSJZ Ett|aae Dr|e, 'c||e ++J

'|alleri, Teta: ll+ll

T. Z&I.+7+.+SJJ |. Z&I.+7+.SJIJ

www.:jet|rcmi|||a|.tem

&/IS/IZ

|me|ctets:

I0S560v2, I0S560v2 SIN Itcve|et,

I0S560v2 |C Itcve|et, I0S510 0SB,

I0S5100SB P|0S, I0S100v2Jv3,

I0S100v3, I0S5100SB 6c|vca|t,

I0S510PP P|0S, C2000 I0S510|C,

SP|530 NPS0, IIk6 P|a k6ctets

0e|eggets:

I| Ce6e Cemeset Ste6|e

TM

IDE

|vc|ect|ea Ne6e|es:

C5502JC5505JC5515JC6155J

0N355J0N35IJ0N365J0N368J

0N612J0N6116J0N616IJ

kN180IJkN1808JkN1810

eI6s

TM

, 0SKs, 0SKs ca6 eI1I0

0SKs Iet |210IJC5116JC5509kJ

C5510JC6I13JC6116IJC6155,

eI6s Iet ||2101kJ||210IkJC33J

|2808J|2812Jk2812J|28335J

C5505JC5515JC5502, eI1I0

ca6 0SKs Iet 0NkP|13I

SeItwcte Iee|s:

'C' tem||ets, cssem||ets, ||akets

||kSh Ptegtcmm|ag 0t|||t|es

k||tct|ea SeItwcte

eCkh Stctk, |aet Stctk, k|get|t|m

w|tct6,Ce6eBex

TM

C |||tcty,

h|IIP|cy

TM

0SP SeItwcte

Beea6cty Stca Iest SeItwcte:

Iemeate 0|cIem 0e|egget Iet I| 0SPs

N|ste||caeees:

0|g|tc| Netet Ceatte||ets,

Ptetetye Ne6e|es,

Pewet Se||es, IIk6 |xca6et

18 Embedded Processing & DSP Resource Guide 2013

EECatalog

SPECIAL FEATURE

Figure 1: E-UTRAN Architecture

Figure 2: eNB Protocol Stack

Analysis of LTE Base Station Software

Deployment on Multicore SoCs

To achieve full multicore entitlement, SoCs require a hardware infrastructure

without bottlenecks, as well as a simplifed software infrastructure.

By Sneha Narnakaje and Zhihong Lin, Texas Instruments

The advent of high-speed cellular services

like 4G LTE is driving a paradigm change

in the complexity of wireless base station

design. As wireless technology continues

to evolve, the demand for higher data rates

increases, causing growth in data traffic.

The data deluge has significant implica-

tions on the type of processing required.

Data traffic is packet-based and allows

for hundreds of users to be connected to a

base station at the same time, all sharing

the airwaves. Managing data traffic effi-

ciently requires the system to handle large

volumes of data packets moving through all

processing layers. It is becoming increas-

ingly important for OEMs and operators

to effectively handle LTE technology using

multicore systems-on-chip (SoCs), as

multicore architectures bring new levels

of efficiency to base station designs. To

achieve full multicore entitlement, SoCs

require a hardware infrastructure without

bottlenecks, as well as a simplified software infrastruc-

ture. This article discusses the challenges encountered

in traditional software implementation of LTE base sta-

tion on a multicore SoC. Further, this paper will show an

example of software implementation on a multicore SoC,

leveraging the hardware infrastructure to effectively and

efficiently overcome those challenges.

LTE Base Station Overview

4G LTE is defined

by 3GPP 36 series

technical specifica-

tions. LTE provides

increased data

rate and capacity,

better spectrum

efficiency, reduced

latency and sim-

plified network

architecture.

LTE base stations,

also referred to as

eNodeB (E-UTRAN

NodeB), provide user-plane and control-plane protocol

terminations (Uu) toward the user equipment (UE,

mobile) as well as transport terminations (Iu) toward

the core network. eNodeBs are interconnected through

X2 interface and also connected to core network EPC

through S1 interface.

The eNodeB protocol structure is comprised of two main

layers: the radio network layer and the transport net-

work layer. The radio interface is implemented within

three protocol layers: physical layer (Layer 1, PHY), data

link layer (Layer 2) and network layer (Layer 3). Layer

2 is partitioned into sublayers called media access con-

trol (MAC), radio link control (RLC) and packet data

convergence protocol (PDCP). Layer 3 includes the radio

resource control (RRC) sublayer

eNodeB Implementation Challenges on a

Multicore SoC

Traditionally, eNodeB implementation in the macro

space has been based on multiple fragmented devices.

While multicore DSP devices are used for baseband

(PHY) processing, multicore general-purpose processors

are used for radio protocol stack processing. In addition,

www.eecatalog.com/dsp 19

EECatalog

SPECIAL FEATURE

Figure 3: eNodeB Software Deployment on a Multicore SoC

Operators and base station

vendors are focusing on the

SoC concept to reduce system

cost, power and complexity,

expediting time to market.

dedicated network processor units, ASIC and FPGA, are

used as bridging devices for transport/backhaul and

radio processing. A combination of fragmented devices

increases the system cost, system power and complexity

to implement the eNodeB on multiple multicore devices.

With the emergence of heterogeneous networks in the

base station market, operators and base station vendors

are focusing on the SoC concept to reduce system cost,

power and complexity, expediting time to market. A basic

approach is to integrate all, if not most, of the functions

on a single chip. Today, we see many SoC architectures

with multicore DSP and RISC cores integrated with a

hardware infrastructure to

enable parallel access to all

cores.

eNodeB implementation

on a multicore SoC brings

significant challenges. LTE

brings a paradigm shift for

base station vendors and

their suppliers, with more

complex data processing

and scheduling to achieve

spectral efficiency. While

data processing requires low

latency and higher throughput, scheduling needs to be

dynamic and channel-aware. Multicore SoC architectures

come with their own complexity with parallelism across

cores, hardware abstraction for full multicore entitle-

ment, partitioning of application software, inter-process

communication and shared resource management. A

traditional approach to solving these challenges uses

shared memory-based multithreading. LTE eNodeB func-

tional tasks are distributed across the cores with data

distribution and handled by shared memory. However,

the performance is dependent on the memory access

times, bus bandwidth and cache effectiveness. Hardware

infrastructure bottlenecks have

also made it nearly impossible

to achieve the low latency and

higher throughput required by

LTE data processing.

An Example of Soft-

ware Implementation

of eNodeB on a Multi-

core SoC

The example of software imple-

mentation of eNodeB is based

on a multicore SoC for small

cells. The architecture for this

multicore SoC integrates four

DSP cores with an ARM core.

The hardware infrastructure

includes a network and security

accelerator and a queue manager

with dedicated packet DMA subsystem. LTE baseband

processing (PHY) is running on two DSP cores, while LTE

user-plane processing (layer 2) is running on the other

two DSP cores. An ARM core runs the LTE control-plane

processing (layer 3 and application). This example of

software implementation of eNodeB leverages high-level

operating system (Linux) services on the ARM core for

the LTE control-plane processing, with real-time oper-

ating system (RTOS) on DSPs for the hard real-time layer

2 and PHY processing. The layer 2 downlink timing is

constrained by HARQ retransmission loop and supplying

PDSCH data load to the PHY, while uplink timing is

constrained PUSCH HARQ

process. By allocating layer

2 on the DSP core closer to

the PHY processing, latency

is minimized.

Many SoC architectures

today harden the network

and security functionality

for eNodeB. However these

hardware accelerators follow

the look-aside approach

requiring CPU cycles to

perform pre- and post-pro-

cessing for each functional block (e.g., IPSec, Ciphering).

With this approach, the throughput varies with the

packet size. Instead, hardware accelerators enabled with

flow-through fast-path processing can achieve maximum

throughput for all packet sizes. In addition, after all the

fast-path processing, if the packets land in dedicated pri-

oritized hardware queues, the CPU is not burdened with

data handling.

Hardware queues play an important role in implementing

eNodeB packet processing. When eNodeB packet processing

(PHY, layer 2 and 3) tasks are distributed across multiple

22 Embedded Processing & DSP Resource Guide 2013

EECatalog

SPECIAL FEATURE

cores, packets need to be handled efficiently and effectively,

without any bottlenecks. Hardware queues in this architec-

ture guarantee the multicore atomicity of all accesses to the

queues, enabling the zero-copy approach for the eNodeB

packet processing. The zero-copy RLC/MAC concept lever-

ages the fact that the data payload requires no processing

between the PDCP (de)ciphering and the CRC generation

(or check) at the PHY encoder/decoder. RLC and MAC sub-

layers need to aggregate/deaggregate, segment/desegment,

multiplex/demultiplex data packets and add/remove con-

trol information and headers. Accomplishing this without

touching the payload data (zero-copy) saves 90-95 percent

of processing cycles. Therefore, payload data resides in DDR

and can never be touched by layer 2 software. For example,

in the downlink direction, packets are received, IPSec

decrypted, classified, GTPU processed, air ciphered by

network and security accelerator, then allocated and deliv-

ered to the per radio bearer hardware queue by dedicated

packet DMA. All steps above are performed without soft-

ware intervention. RLC/MAC software operates on packet

descriptors and does not need to access the packet payload.

It builds MAC PDUs, which are sent out and reassembled

back to contiguous memory by the packet DMA.

With key benefits such as spectral efficiency, flexible

channel bandwidth and capital expenditure savings, LTE is

driving operators to deploy LTE networks. While effective

LTE systems can be designed on a multicore architecture,

achieving full multicore entitlement is the key to unleashing

multicore performance and reaping the benefits of 4G sys-

tems. Supporting efficient and effective LTE system designs

require a number of innovations in multicore architecture

design. One such innovation is a hardware infrastructure

without bottlenecks, enabling packet processing, memory

access and core-to-core communication.

Based on a presentation at the 2012 Multicore DevCon.

Sneha Narnakaje is the software product man-

ager for TIs wireless base station infrastructure

team. In this role, she is responsible for TIs com-

mon software strategy and roadmap across the

wireless base station infrastructure team and

driving business development activities. She

earned her MBA from the University of Maryland (Smith) and

BS in computer engineering from Mangalore University, India.

As a strategic marketing manager for TIs multi-

core processors group, Zhihong Lin is responsible

for defining and planning key requirement for

multicore SoC for wireless base station applica-

tions. Zhihong has over 18 years of experience

in both communications and networking in-

dustries. Zhihong holds a US patent on communications and

received her MSEE degrade from University of Texas at Dallas.

Embedded Processing & DSP ONLINE

Explore...

Directory of leading DSP & Embedded Solutions

Top Stories and News

White Papers

Expert Opinions (Blogs)

Exclusive Videos

Valuable Articles

Sign up for the quarterly

Embedded Processing & DSP E-Product Alert

at www.eecatalog.com/dsp

Embedded Processing & DSP ONLINE

www.eecatalog.com/dsp

www.eecatalog.com/dsp 23

EECatalog

SPECIAL FEATURE

The high cost of repairing defects shipped in embedded

devices, paired with the increasing need to follow regula-

tory compliance initiatives for safety-critical embedded

systems software (FDA, DO-178B/C, IEC 61508) has

driven many organizations to adopt static analysis as a

key part of their quality strategies.

Static analysis is one of the most effective and least bur-

densome of such industry-standard best practices. In fact,

it is often explicitly recommended (e.g., per the FDA's rec-

ommendation for infusion pumps) as one key component

of a comprehensive quality strategy. When properly imple-

mented, static analysis is a very powerful tool for exposing

error-prone code. Finding and fixing such code from the

earliest phases of the software development lifecycle has

been proven to be a very effective (and cost-efficient) way

to prevent defects from being shipped in the final product.

Static analysis is a critical component of a comprehensive

quality process...but it is just one component. It's important

to remember that most effective quality processes involve

a combination of test and analysis practices embedded

throughout the SDLC. In addition to static analysis, an

effective quality strategy covers practices such as:

- UniL LcsLing (hosL and LargcL)

- Rcgrcssion LcsLing

- Pccr codc rcvicw

- Covcragc analysis

- RunLimc crror dcLccLion

- RcquircmcnLs LraccabiliLy

At Parasoft, we've been assisting software develop-

ment organizations to implement and optimize static

analysis since 1996. Over the years of analyzing static

analysis deployments across safety critical, embedded,

and enterprise software development organizations, we've

determined what mistakes are most likely to result in

failed static analysis initiatives. Here's what we've found

to be the top three reasons why static analysis initiatives

dont deliver real value in embedded and safety-critical

development environmentsand some critically impor-

tant tips for avoiding these common pitfalls.

3. Starting With Too Many Rules

Some eager teams take the "big bang" approach to static

analysis. With all the best intentions, they plan to invest

considerable time and resources into carving out the

penultimate static analysis implementation from the

startone that is so good, it will last them for years.

Tey assemble a team of their best engineers. Tey read stacks

of programming best practices books. Tey vow to examine

all of their reported defects and review the rule descriptions

for all of the rules that their selected vendor provides.

I've found that teams who take this approach have too

many rules to start with and too few implemented later

on. It's much better to start with a very small rule set, and

as you come into compliance with it, phase in more rules.

Static analysis actually delivers better results if you don't

bite off more than you can chew. When you perform static

analysis, it's like you're having an experienced engineer

stand over the shoulder of an inexperienced engineer and

give him tips as he writes code. If the experienced engi-

neer is constantly harping on nitpicky issues in every few

lines of code, the junior engineer will soon become over-

whelmed and start filtering out all advicegood and bad.

However, if the experienced engineer focuses on one or

two issues that he knows are likely to cause serious prob-

lems, the junior engineer is much more likely to remember

what advice he was given, start writing better code, and

actually appreciate receiving this kind of feedback.

It's the same for static analysis. Work incrementallywith

an initial focus on truly critical issuesand you' ll end up

teaching your engineers more and having them resent the

process much less. Would you rather have a smaller set of

rules that are followed, or a larger set that isn't?

Top 3 Mistakes with Static

Analysis for Embedded and

Safety-Critical Development

By Arthur Hicken, Evangelist, Parasoft

24 Embedded Processing & DSP Resource Guide 2013

EECatalog

SPECIAL FEATURE

Out of the hundreds or sometimes even thousands of rules

that are available with many static analysis tools, how do

you know where to start? Here are a few simple guidelines:

1. Would team leaders stop shipping if a violation of this

rule was found?

2. (In the beginning only) Does everyone agree that a vio-

lation of this rule should be fixed?

3. Are there too many violations from this rule?

In regulated environments, this rule is elevated to the

status of a commandment. The more you get into the habit

of frequently suppressing or ignoring rule violations, the

more likely you are to have to tell an auditor or attorney

why you ignored reports of an issue that ultimately caused

a serious defect in the field. From a negligence perspec-

tive, it's much safer to define a tight rule set and ensure

that every violation is addressed than to have a large one

that is loosely followed.

2. No Automated Process Enforcement

Without automated process enforcement, engineers

are likely to perform static analysis sporadically and

inconsistentlywhich is not only problematic from a

compliance perspective, but also diminishes your ability

to derive maximum defect-prevention value from static

analysis. The more you can automate the tedious static

analysis process, the less it will burden engineers and

distract them from the more challenging tasks they truly

enjoy. Plus, the added automation will help you achieve

consistent results across the team and organization.

Avoid the false economy of an automated run that still

requires a manual triage process at the end. A tighter

configuration will provide more value without the need

for manual review and selection of what to fix.

Many organizations follow a multi-level automated

process. Each day, as the engineer works on code in the

development environment, he or she can run analysis

on demandor configure an automated analysis to run

continuously in the background (like spell check does).

Engineers clean these violations before adding new or

modified code to source control.

Then, a server-based analysis can run as part of con-

tinuous integration, or on a nightly basis, to make sure

nothing slipped through the cracks.

Assuming that you have a policy requiring that all viola-

tions from the designated rule set are cleaned before check

in, any violations reported at this level indicate that the

policy is not being followed. If this occurs, don't just have

the engineers fix the reported problems. Take the extra

step to figure out where the process is breaking down, and

how you can fix it (e.g., by fine-tuning the rule set, using

suppressions judiciously).

1. Lack of a Clear Policy

It's common for organizations to overlook policy because

they think that simply making the tool available is suffi-

cient. It's not. Even though static analysis (done properly)

will save engineers time in the long run, they're not going

to be attracted to the extra work it adds upfront. If you

really want to ensure that static analysis is performed as

you expecteven when the team's in crunch mode, scram-

bling to just take care of the essentialspolicy is key.

Every team has a policy, whether or not it's formally

defined. You might as well codify the process and make it

official. After all, it's a lot easier to identify and diagnose

problems with a formalized policy than an unwritten one.

Ideally, you want your policy to have a direct correlation to

the problems you're currently experiencing (and/or com-

mitted to preventing). This way, there's a good rationale

behind both the general policy and the specific ways that

it's implemented.

With these goals in mind, the policy should clarify:

- WhaL Lcams nccd Lo pcrorm sLaLic analysis

- WhaL projccLs rcquirc sLaLic analysis

- WhaL rulcs arc rcquircd

- WhaL dcgrcc o compliancc is rcquircd

- Whcn supprcssions arc allowcd

- Whcn violaLions in lcgacy codc nccd Lo bc ixcd

- WhcLhcr you ship codc wiLh sLaLic analysis violaLions

Arthur Hicken, Evangelist for Parasoft, has

been involved in automating various practices

at Parasoft for almost 20 years. He has worked

on projects including database development, the

software development lifecycle, web publishing

and monitoring, and integration with legacy sys-

tems.

www.eecatalog.com/dsp 25

E

m

b

e

d

d

e

d

P

r

o

c

e

s

s

o

r

s

E

m

b

e

d

d

e

d

P

r

o

c

e

s

s

o

r

s

DaVinci

Video

Processors

C6000

Digital Signal

Processors

C5000

Digital Signal

Processors

C2000

Microcontrollers

MSP430

Microcontrollers

Sitara

32-bit ARM

Cortex

-A

Processors

Stellaris

32-Bit

ARM

Cortex-M

MCUs

Hercules

Safety

Microcontrollers

Audio

Automotive

Communications

Industrial

Medical

Security

Video

Wireless

Key Feature

Video

processing

High

performance

Ultra-low

power

Performance,

integration for

greener industrial

applications

Ultra-low power

Low power,

high

performance

Open architec-

ture software,

rich communica-

tions options

Safety Integrated

in H/W

Embedded Processing Overview

Texas Instruments has the broadest portfolio of scalable DSP, MCU, differentiated ARM

and complementary analog products, offering

complete system solutions for electronics manufacturers. This portfolio offers the full range of power/performance requirements ensuring

the right combination of attributes for the smallest portable devices to the largest multichannel systems and everything in between. In

addition, TI offers design resources including extensive software (including open source), tools, technical training, in-person and online tech

support, and engineer-to-engineer forums at www.e2e.ti.com. Visit www.ti.com for technical literature, system block diagrams and more.

Applications Matrix Guideline

DaVinci

Video Processors:

Optimized for Digital Video

DaVinci

video processor solutions are tailored

for digital video, imaging, and vision applications.

Optimized for video encode and decode applications,

the DaVinci platform includes a general purpose

processor, video accelerators, an optional DSP,

and related peripherals. A wide range of devices

are available, offering a variety of performance,

power and price points.

High Performance: TMS320C6000

DSP Platform

The C6000

DSP platform offers the industrys

highest-performance single- and multicore DSPs,

ideal for networking, telecommunication, video,

imaging, infrastructure, test and equipment,

military, and industrial applications. The platform

includes C64x high-performance DSPs,

C674x fixed-/floating-point DSPs and C66x

fixed-/floating-point multicore DSPs. It also

includes the OMAPL series which combines

a C674x DSP with an ARM9

processor to handle

networking and control for computational efficiency.

Ultra-Low-Power TMS320C5000

DSP Platform

The C5000

DSP platform provides a broad

portfolio of the industrys lowest power 16-bit DSPs.

Total active core power at less than 0.15 mW/MHz

at 1.05V and standby power at less than 0.15mW

extends the battery life of portable applications.

Increase processing capability with C5000 DSP

processors that offer up to 300MHz (600 MIPs).

High peripheral integration and large on-chip

memory helps reduce overall system cost. Ultra low

cost development boards, system development kits,

free and highly mature software libraries with an

extensive database of code examples enables fast

time to market. With these advantages, the C5000

has become a very popular choice for a variety of

low-power and cost-efficient embedded signal

processing solutions, including portable devices in

audio, voice, communications, medical, security

and industrial applications.

C2000

32-Bit Micro controller for

Real-Time Control

The C2000

microcontroller family combines

advanced control peripherals with the processing

power of a 32-bit core. With the low-cost,

high-integration Piccolo

MCUs, the powerful

Delfino

floating-point MCUs and the connectivity

and control featured in the Concerto

MCUs, C2000

MCUs offer a broad range of options and are ideal for

embedded industrial control and green

energy applications such as digital motor control,

digital power supplies, solar and wind energy, LED

lighting, and automotive HEV/EV.

MSP430

Ultra-Low-Power

Microcontroller Platform

The MSP430 family of ultra-low-power

16-bit RISC mixed-signal processors provides

the ultimate solution for battery-powered

measurement applications. Using leadership

in both mixed-signal and digital technologies,

TI has created the MSP430 MCU, enabling system

designers to simultaneously interface to analog

signals, sensors and digital components while

maintaining unmatched low power.

Sitara

ARM

Processors

The high-performance Sitara ARM-based

processors include solutions based on the

ARM Cortex

-A8 and ARM9

. The platform

includes the AM1x, AM35x, AM37x and AM335x

processors, which offer a software-compatible

roadmap for customers using TIs OMAP35x

and OMAP-L1x processors.

Stellaris

32-Bit ARM Cortex-M MCUs

Texas Instruments is the industry leader in

bringing 32-bit capabilities and the full benefits

of ARM

Cortex

-M microcontrollers (MCUs) to

the deepest reach of the microcontroller market.

With more than 220 compatible ARM Cortex-M

Stellaris MCUs and more than 30 Stellaris evaluation,

development, and reference design kits, Stellaris fits

the performance, integration, power, and price-point

requirements of nearly any industrial application.

Stellaris with Cortex-M offers a direct path to the

strongest ecosystem of development tools, software

and knowledge in the industry. Designers who

migrate to Stellaris benefit from great tools, small

code footprint, and outstanding performance. With

StellarisWare

Software, Stellaris gives developers

a huge jump start by providing a free, royalty-free

software package that includes a peripheral driver

library, graphics library, USB library, code examples,

and much more.

Hercules

Safety Microcontrollers

Hercules safety microcontrollers are based on

TIs 20+ years of safety-critical system expertise,

industry collaboration and proven hardware for the

automotive market. The platform consists of three

ARM

Cortex

-based microcontroller families

(RM48x, TMS570 and TMS470M) that deliver

scalable performance, connectivity, memory and

safety features. Unlike many microcontrollers that

rely heavily on software for safety capabilities,

Hercules microcontrollers implement safety in

hardware to maximize performance and reduce

software overhead.

Software and Development Tools

TMS320

DSPs are supported by eXpressDSP

software and development tools, including Code

Composer Studio

IDE, DSP/BIOS

kernel, the

TMS320 DSP algorithm standard and numerous

reusable, modular software from the largest

developer network in the industry.

Complementary Analog Products

TI offers a range of complementary data

converter, power management, amplifiers,

interface and logic products to complete

your design.

26 Embedded Processing & DSP Resource Guide 2013

E

m

b

e

d

d

e

d

P

r

o

c

e

s

s

o

r

s

E

m

b

e

d

d

e

d

P

r

o

c

e

s

s

o

r

s

Specifications

CO000

high performance fixed/

floating-point DSP

Co000

ultra-low power fixed-point

DSP; industrys lowest cost and

lowest power DSPs