Professional Documents

Culture Documents

Part 6

Uploaded by

bmbsnpOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Part 6

Uploaded by

bmbsnpCopyright:

Available Formats

2.2 Sequential Circuit Design Example : The circuit under study will be a Counter.

We will design three counters, a synchronous one using JK Flip-Flops and counts from 0 up to 6 . 2.2.1 Counter using JK Flip-Flops 2.2.1.1 Excitation Tables and Karnaugh Maps

Karnaugh Maps: "J0" Map

"K0" Map

"J1" Map

"K1" Map

"J2" Map

"K2" Map

2.2.1.3 Boolean Expression

2.2.1.3 VHDL Behavioral Code of Inverter library ieee; use ieee.std_logic_1164.all; Entity invert is Port (a : in std_logic; b:out std_logic); end invert Architecture invbehave of invert is Begin b <= not (a); end invbehave;

2.2.1.4VHDL Behavioral Code of 2-input AND library ieee; use ieee.std_logic_1164.all; Entity and2i is Port (a,b : in std_logic; c:out std_logicl; end and2i Architecture andbehave of and2i is Begin c <= a and b; end andbehave; 2.2.1.5 VHDL Behavioral Code of 2-input OR library ieee; use ieee.std_logic_1164.all; Entity or2i is Port (a,b : in std_logic; c:out std_logic); end or2i Architecture orbehave of or2i is Begin c <= a or b; end orbehave; 2.2.1.6 VHDL Behavioral Code of JK Flip-Flop library ieee; use ieee.std_logic_1164.all: Entity jkff is Port (j,k,clk : in std_logic; q:out std_logic); end jkff Architecture behavelikethis of jkff is signal q_int : std jogic := '0'; Begin Process (clk) Begin If clk='1' and clk 'event then If j='1' and k='0' then q_int<='1'; elsif j='0' and k='1' then q_int<='0'; elsif j='1' and k='1' then q_int<=not (q_int); end if; end if;

end process; q<=q_int; end behavelikethis 2.2.1.7 VHDL Structural Code of the JK Flip-Flops Counter library ieee; use ieee.std_logic_1164.all; Entity jkcount is Port (clk: in std_logic; q0,q1,q2:out std_logic); end jkcount Architecture Structural of jkcount is signal q0int,q1int,q2int,q1i,q2i,j0,k0,j1,k1,j2,k2 : std_logic := '0'; Component invert is Port (a : in std_logic; b:out std_logic); end Component Component and2i is Port (a,b : in std_logic; c:out std_logic); end Component Component or2i is Port (a,b : in std_logic; c.out std_logic); end Component Component jkff is Port (j,k,clk : in std_logic; q:out std_logic); end Component begin inv0: invert port map (q1int,q1i) inv1 : invert port map(q2int,q2i) and0 : and2i port map(q0int,q1int,j2) or0: or2i port map(q1i,q2i,j0) or1 : or2i port map(q0int,q2int,k1) jk0 : jkff port map(j0,l,clk,q0int) jk1 : jkff port map(q0int,k1,clk,q1int) jk2 : jkff port map(j2,q1int,cIk,q2int) q0 <= q0int; q1 <= q1int;

q2 <= q2int; end Structural

You might also like

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Asynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterDocument20 pagesAsynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterKalagadda BikshaluNo ratings yet

- TP VHDL 3Document8 pagesTP VHDL 3KAWTAR EL AMRINo ratings yet

- Ecad Lab Manual PvpsitDocument53 pagesEcad Lab Manual PvpsitpriyankaveeramosuNo ratings yet

- Proiect - Structuri FPGADocument10 pagesProiect - Structuri FPGACrocoduluNo ratings yet

- E Cad Lab ManualDocument51 pagesE Cad Lab ManualRajesh DoradlaNo ratings yet

- VHDL SequentialDocument5 pagesVHDL SequentialSAKETSHOURAVNo ratings yet

- Dic File - 7 SemDocument22 pagesDic File - 7 SemShalini SharmaNo ratings yet

- Experiment No 3Document20 pagesExperiment No 3Ako C SeanNo ratings yet

- VHDL FileDocument25 pagesVHDL Filenitin_280890No ratings yet

- Decade CounterDocument3 pagesDecade Countergiridhar chikkaNo ratings yet

- Lab 7: VHDL 16-Bit ShifterDocument6 pagesLab 7: VHDL 16-Bit ShifterAvinash VikramNo ratings yet

- Experiment No. 2: Aim: A) D Flip-Flop: Synchronous VHDL CodeDocument6 pagesExperiment No. 2: Aim: A) D Flip-Flop: Synchronous VHDL CodeRahul MishraNo ratings yet

- VHDL ProgramDocument5 pagesVHDL ProgramJaswanth TejaNo ratings yet

- Date: 28 September, 2015: VHDL Assighment 2Document15 pagesDate: 28 September, 2015: VHDL Assighment 2Ishan DarwhekarNo ratings yet

- New Text DocumentDocument3 pagesNew Text DocumentNaveen NegiNo ratings yet

- Chandigarh University, GharuanDocument5 pagesChandigarh University, GharuanAnkit KumarNo ratings yet

- VHDL Code For Parallel in Parallel Out Shift RegisterDocument4 pagesVHDL Code For Parallel in Parallel Out Shift RegisterPRITY KUMARI 20BEC0773No ratings yet

- VHDL For FPGA Design - 4-Bit Binary Counter With Parallel Load - Wikibooks, Open Books For An Open World PDFDocument5 pagesVHDL For FPGA Design - 4-Bit Binary Counter With Parallel Load - Wikibooks, Open Books For An Open World PDFpavani kutalaNo ratings yet

- SCOE Vadgaon Pune: Unit Iii Algorithmic State MachineDocument11 pagesSCOE Vadgaon Pune: Unit Iii Algorithmic State MachineDeepakNo ratings yet

- Digital Lab Cs 6211 VHDL ProgramsDocument13 pagesDigital Lab Cs 6211 VHDL ProgramsMurugan GNo ratings yet

- Design Example 5.5Document10 pagesDesign Example 5.5MaheshNo ratings yet

- VHDLDocument13 pagesVHDLSrijeeta SenNo ratings yet

- Aplicaciones Spartan6 Ver1Document42 pagesAplicaciones Spartan6 Ver1juan mezaNo ratings yet

- Carrera de Ingeniería Electrónica Arquitectura de ComputadoresDocument25 pagesCarrera de Ingeniería Electrónica Arquitectura de ComputadoresNatalia PoloNo ratings yet

- 3 Bit Asynchronous Counter Using JK Flip Flop: Program VHDLDocument4 pages3 Bit Asynchronous Counter Using JK Flip Flop: Program VHDLsanthiniNo ratings yet

- N-Bit Shift Register PDFDocument232 pagesN-Bit Shift Register PDFAnuradha KhalkhoNo ratings yet

- Digital Circuits and Stystems: Lab FileDocument14 pagesDigital Circuits and Stystems: Lab FileAnurag AroraNo ratings yet

- Experiment No.1: A Binary To Gray ConverterDocument26 pagesExperiment No.1: A Binary To Gray ConverterVarun SharmaNo ratings yet

- Basic Gates ProgramDocument34 pagesBasic Gates ProgramJoychandra LoukrakpamNo ratings yet

- Ec-452 VHDL CadDocument39 pagesEc-452 VHDL Cadkishorereddy416No ratings yet

- Exercices VHDLDocument83 pagesExercices VHDLFadi Akoury50% (2)

- VHDL Code For D FF Using Behavior ModelDocument20 pagesVHDL Code For D FF Using Behavior ModelAdithya ChakilamNo ratings yet

- Using Case Statement VHDL Code:: Assignment 2Document15 pagesUsing Case Statement VHDL Code:: Assignment 2innovatorinnovatorNo ratings yet

- VHDL From BotrosDocument17 pagesVHDL From BotrossanjanaNo ratings yet

- Final LabDocument25 pagesFinal LabRAMYA VATHSALYA PNo ratings yet

- Document 1Document4 pagesDocument 1Puneeth Kumar ReddyNo ratings yet

- VHDL Programs LabDocument20 pagesVHDL Programs LabVasu SiriNo ratings yet

- Lab 6Document4 pagesLab 6marwa abdelrazikNo ratings yet

- ECAD LAB2 (Master Copy)Document57 pagesECAD LAB2 (Master Copy)B.n. Srinivasa RaoNo ratings yet

- Tugas8 - 2210191006 - Filosofi Dwibakti - LapsemDocument23 pagesTugas8 - 2210191006 - Filosofi Dwibakti - LapsemFD SyndromeNo ratings yet

- Bascule JKDocument9 pagesBascule JKOussema HamzaNo ratings yet

- VHDL Codes For A 4 Bit Parallel To Serial ConverterDocument9 pagesVHDL Codes For A 4 Bit Parallel To Serial ConverterAshutosh YadavNo ratings yet

- DLD LAB PROGRAMS Encoder, CountersDocument3 pagesDLD LAB PROGRAMS Encoder, Counters1GA22IS138Sanjay K. S.No ratings yet

- VHDL Project: Composite Color Generation Using RGB LedDocument15 pagesVHDL Project: Composite Color Generation Using RGB LedArun GoelNo ratings yet

- Digital Integrated Circuits Lab: Practical FILEDocument55 pagesDigital Integrated Circuits Lab: Practical FILELakshayNo ratings yet

- Cad of Electronics LabDocument4 pagesCad of Electronics LabVaibhav PandeyNo ratings yet

- Ieee Ieee STD - Logic - 1164 Ieee STD - Logic - ArithDocument2 pagesIeee Ieee STD - Logic - 1164 Ieee STD - Logic - ArithDharccana DeviNo ratings yet

- Decade CounterDocument3 pagesDecade CounterManohar thota100% (1)

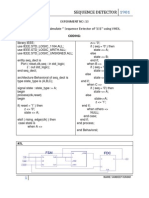

- Sequence Detector: Experiment No: 10 Activity: To Design and Simulate ' Sequence Detector of 101'' Using VHDLDocument2 pagesSequence Detector: Experiment No: 10 Activity: To Design and Simulate ' Sequence Detector of 101'' Using VHDLSaurabh KhandelwalNo ratings yet

- Modelado de Circuitos SecuencialesDocument10 pagesModelado de Circuitos SecuencialesNick CohechaNo ratings yet

- Sequential ExampleDocument11 pagesSequential ExampleAmit JadhavNo ratings yet

- Micro TPDocument7 pagesMicro TPsebastienNo ratings yet

- VHDL TutorialDocument14 pagesVHDL TutorialMohan Kumar SmkNo ratings yet

- Design and Simulation of Logic Gates Using VHDLDocument26 pagesDesign and Simulation of Logic Gates Using VHDLSushanth BabuNo ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- 2.1 Combinational Circuit Desion ExampleDocument2 pages2.1 Combinational Circuit Desion ExamplebmbsnpNo ratings yet

- Banking TerminologyDocument8 pagesBanking TerminologybmbsnpNo ratings yet

- Part 4Document5 pagesPart 4bmbsnpNo ratings yet

- 1.4.1.2 Concurrent StatementsDocument3 pages1.4.1.2 Concurrent StatementsbmbsnpNo ratings yet

- Part 2Document4 pagesPart 2bmbsnpNo ratings yet

- Binomial Formulas: Definition of Factorial NumbersDocument2 pagesBinomial Formulas: Definition of Factorial NumbersbmbsnpNo ratings yet

- Coordinate GeometryDocument78 pagesCoordinate Geometrybmbsnp100% (1)