Professional Documents

Culture Documents

QPSK基本原理与实现

Uploaded by

lingdong000Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

QPSK基本原理与实现

Uploaded by

lingdong000Copyright:

Available Formats

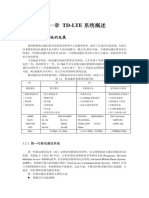

l 前言

随着电子技术的快速发展,对通信系统功能的要求不断提高。基于同样的硬件环境,由软件来完成不同的

通信功能的方式趋于成熟,通过改变程序可以很灵活地更改通信系统的功能和性能。于是,可编程高速器

件如 DSP,ARM 等成了现代数据通信系统的主要角色。数字调制是用载波信号的某些离散状态来表征所传送

的信息,然后在接收端对载波信号的离散调制参量进行检测。

四相相移键控(QPSK)方式已经在数字调制技术中占有越来越重要的地位,该调制方式广泛应用于卫星通信、

电缆调制解调、视频会议系统、蜂窝电话和其他数字通信等领域。它具有适中的频谱利用率,很低的比特

错误率。由于高速数字信号处理器(如 TI 公司 TMS320 系列)的广泛应用,为数字方式实现调制解调器提供

了有利的条件,同时省去了大量的硬件电路,如环型滤波器,VCO 等。在 DSP 技术的支持下很容易实现。

2 QPSK 的基本原理与算法

2.1 绝对正交相移键控(QPSK)

在绝对相移键控方式中,表达式为:

式中 I(t)是同相支路信号,Q(t)是正交支路信号。

图 1 给出实现 QPSK 调制的原理。输入的二进制数字信号经过串并转换电路分为两路速率减半的双极性信号:

同相信号 I(t)和正交信号 Q(t),经低通滤波成形后分别与相互正交的两路载波信号相乘,然后相加即可得

到 QPSK 信号,也可以采用相位选择法来实现 QPSK 信号,输入的二进制数字信号经串/并转换后,成为双

比特码元,而载波发生器产生 4 种不同相位的载波波形,根据双比特码元的不同组合.每个比特周期从 4

种不同相位的载波中选择一种输出,然后经带通滤波器滤除带外干扰信号,就得到 QPSK 信号,这种方式适

用于载波频率较高的场合。

设原始数据流为 dk(t)=d0d2d2…,取双极性脉冲序列。其值为+1 或一 1,分别代表 O 或 1,dk(t)经数据分

离器分成奇偶两路,dI(t)=d0d2d4…和 dQ(t)=d1d3d5…,每路的码元宽度扩展为 2T。其中,奇数路数据

d0(t)经过时延送入 O 信道,对载波 sinωct 进行二相调制;偶数路数据 dI(t)送入 I 信道,对载波 cosωct

进行二相调制。然后 2 个信号相加得到四相信号。码元转换时,QPSK 信号的相位可能产生 90°的跳变,也

可能产生 180°的跳变,前者发生在 2 个信道的一路数据改变极性时,后者发生在 2 个信道的数据同时改

变极性时。

2.2 偏移正交相移键控(OQPSK)

在绝对相移键控(QPSK)的调制中,输入的二进制信号经过串并转换后得到的 I,Q 两路数据是相互对齐的,

当输入的数据由 00 变为 11 或由 Ol 跳变为 10,即 I,Q 两路数据同时出现跳变时,输出调制信号的相位会

出现 π 的跳变,其相位变化关系由图 2(b)给出,信号在经过限带后有可能出现包络为 0 的现象,从而使

频谱扩展,会对相邻信号产生干扰。另外在传统的锁相环恢复电路中,可能造成本地载波的相位模糊,使

解调后的信号出现错误,还要采取措施消除相位模糊,所以实际应用中较少使用绝对相移键控。在第二代

的窄带 CDMA(IS 一 95)系统中,下行链路采用 QPSK 方式,上行链路采用 OQPSK 方式。

图 3 给出 0QPSK 的调制原理。在 OQPSK 调制中,输入的数据先做串/并转换,分成 I、Q 两路,然后对 Q 支

路的数据延时半个码元周期,后面和 QPSK 方式一样。这样每个码元周期内 I、Q 两路信号中只可能有一路

发生变化,调制后信号的相位跳变不会出现 π 相位跳变。

3 硬件系统设计

3.1 硬件组成

(1)核心板核心板主要由一块 DSP 组成,采用 TI 公司的 TMS320VC5416。该器件采用增强型哈佛结构,片内

共有 8 条总线(1 条程序总线、3 条数据总线和 4 条地址总线),具有功耗小,高度并行等优点;片内有 128

K 字节的 ROM,16 K 字节的 DARAM,3 个多通道缓冲串口(McBSPs),加强型的 8/16 位并行主机接口(HPI),

16 位可编程定时器,支持外部总线到内部存储器的 DMA 操作。该器件外围输入输出电平为 3.3 V,内核电

压为 1.8 V。

(2)电源部分 稳压电源电路采用 5 V 直流供电,通过 AMSll7 电源转换器分别转换成 3.3 V 和 1.8 V。因

存在模拟和数字 2 种信号,同时需要模拟和数字供电,系统中利用 2 个 10μH 的电感将这 2 种电源分离,

以免产生相互干扰。

(3)MCU 部分 MCU 采用 STC 公司的 89LE58RD,其供电电压为 3.3 V,具有 32 个 I/O 引脚,20 K 字节的片

内 ROM,256 字节片内 RAM。89LE58RD 通过异步串口与 PC 机相连,其输入输出电平为 TTL 标准,通信线路

上的数据信号采用 RS 一 232C 电平标准。系统采用 MAX202 进行电平标准转换。

(4)A/D,D/A 转换采用 D/A 和 A/D 转换器,该模块选用了 ADI 公司的 AD7303,它是一个 8 位双通道电压

输出 D/A 转换器,最高工作时钟为 30 MHz。AD7303 内部有 1 个 16 位的移位寄存器、2 个输入寄存器和 2

个 D/A 转换寄存器。16 位移位寄存器的低 8 位(DB0~DB7)用来存储待转换的数字量,高 8 位(DB8~DBl5)

是控制码,通过控制码选择通道和不同的数据装载方式,通过控制位 LDC、A/B、CRl 和 CR0 设置为两路输

出方式。AD7303 采用 SPI 方式与。DSP 的多路缓冲串口(McBSP)相接。

(5)SRAM 静态存储 SRAM 采用 IS6lLV25616,其速度为 10 ns,存储空间为 256 K 字节,供电电压为 3.3 V。

3.2 实现方案

图 4 给出调制实验系统总体设汁框图。PC 机为通信终端;单片机用来控制数据收发;DSP 运行 QPSK 等相关

算法;SRAM 用来存储算法及相关数据。当系统重新加电时,自动把程序及相关数据导入到 DSP 中。PC 机通

过异步串口连接单片机,利用串口调试软件如“串口调试助手”,即可与单片机交换数据。单片机一方面

与 PC 机交换数据,另一方面则直接通过 HPI 接口从 DSP 内存中读写数据。这样 DSP 与 PC 机通信不需花费

时间,大大节省了 DSP 的资源。DSP 利用多通道缓冲串行口 McBSP 发送数据给 D/A 转换器,以便在模拟线

路上进行传输。

4 QPSK 的设计与实现

QPSK 信号可看成是 2 个 BPSK 信号之和,它有 4 种不同的初始相位。首先在 DSP 中产生 1 个正弦波,然后

从已经存入存储器的数据中每次读出 2 位二进制信息,串并转换输入的二进制信息,把偶数位信息放人数

组 I(同相支路)中,奇数位信息放入数组 Q(正交支路)中,把产生的 I、Q 两路的一部分 PN 码片分别存储于

DSP 内部存储器,经过串/并转换后的二进制信息与存储器中的 I、Q 两路的。PN 码片分别进行模 2 加运算,

实现短码扩频,短码扩频后省去了低通滤波器,可直接正交调制,设计中采用了选相的方式,即根据扩频

后的 I、Q 两路的信息进行选相。选相时 I、Q 的组合采用格雷编码方式,当 I=0、Q=0 时选择初始相位 0;

当 I=0、Q=1 时选择初始相位 π/2;当 I=l、Q=1 时选择初始相位 π;当 I=1、Q=0 时选择初始相位 3π/2。

为保证每个码元都能有完整的波形输出,存储的正弦波为两个周期。1 个周期有 64 个点,初始相位为 0,

相当于从第 16 个点开始连续读 1 个周期正弦波。图 5 是 QPSK 调制流程图,图 6 是调制后的 QPSK 信号波形

图,是在 CCS 仿真软件中看到的波形图。图 6 中的纵坐标为幅度值,单位为 mV;横坐标为时间轴,单位为

μs。

5 结语

实验证明,基带数字调制算法 QPSK 系统达到了设计要求,且能提供较高性能。但因缺少射频模块及天线,

该平台不能在无线信道上调试和实验,这是下一步研究目标。

You might also like

- S7 1200样本Document48 pagesS7 1200样本hezhipingNo ratings yet

- 第2章 计算机控制系统的硬件设计技术Document99 pages第2章 计算机控制系统的硬件设计技术hj443729425No ratings yet

- 2009年下半年 网络工程师(上午+下午) 答案详解Document54 pages2009年下半年 网络工程师(上午+下午) 答案详解mangkong233No ratings yet

- 基于ADS1256和STM32的数据采集装置设计 郭玉霞Document5 pages基于ADS1256和STM32的数据采集装置设计 郭玉霞123No ratings yet

- 1012 - 1 TD-LTE eNodeB设备基础 (V2.0)Document44 pages1012 - 1 TD-LTE eNodeB设备基础 (V2.0)Chang JackNo ratings yet

- 第1章 现代互联网技术概述Document96 pages第1章 现代互联网技术概述flach062No ratings yet

- 计算机组成原理Document12 pages计算机组成原理Fulei SunNo ratings yet

- 用VB实现上位机与RFID控制器的串行通信Document3 pages用VB实现上位机与RFID控制器的串行通信李宏观No ratings yet

- 通信复试面试真题集锦部分问题Document19 pages通信复试面试真题集锦部分问题zzy3096822580No ratings yet

- 模拟会话 202003Document64 pages模拟会话 202003Xin LinNo ratings yet

- 6680数字声波操作维修手册Document30 pages6680数字声波操作维修手册majid aziziNo ratings yet

- GPRS&EDGE原理Document78 pagesGPRS&EDGE原理Yest windNo ratings yet

- (中文) 现场总线与HART协议的关系及应用 PDFDocument2 pages(中文) 现场总线与HART协议的关系及应用 PDFvirgil guimanNo ratings yet

- 基于FPGA的高速数据采集存储系统设计与实现 刘静Document4 pages基于FPGA的高速数据采集存储系统设计与实现 刘静kamutulafuNo ratings yet

- IDM7842 Modbus Gateway ManualDocument6 pagesIDM7842 Modbus Gateway ManualBOsy Ying LoNo ratings yet

- 马丁Document2 pages马丁袁明汇No ratings yet

- 可编程逻辑器件与应用专题 (清华)Document36 pages可编程逻辑器件与应用专题 (清华)lieshi2958100% (3)

- SCANET用户手册CN2016.07 1Document107 pagesSCANET用户手册CN2016.07 1Alvaro Jesus Ledo PelaezNo ratings yet

- W XJ y 201516010Document4 pagesW XJ y 201516010miusayNo ratings yet

- DA和AD转换电路图Document92 pagesDA和AD转换电路图大漠飞鱼No ratings yet

- 4D成像雷达拆解 2023 05 零部件Document21 pages4D成像雷达拆解 2023 05 零部件mong magnumNo ratings yet

- 1 1诺基亚2G基站基础知识介绍1 (NOKIADocument71 pages1 1诺基亚2G基站基础知识介绍1 (NOKIAJinzhe WangNo ratings yet

- SFP光模块及光接收器知识介绍 PPT课件Document76 pagesSFP光模块及光接收器知识介绍 PPT课件chifengNo ratings yet

- LGT8FX8x PDFDocument267 pagesLGT8FX8x PDFPol ErnNo ratings yet

- 光模块介绍 简介Document73 pages光模块介绍 简介ll1148733194No ratings yet

- 程控交换实习报告Document20 pages程控交换实习报告sandraNo ratings yet

- PZ DSP28335 L开发板入门教程Document17 pagesPZ DSP28335 L开发板入门教程Shwe Thin AungNo ratings yet

- Ge 智能平台网络及通讯用户手册Document119 pagesGe 智能平台网络及通讯用户手册meirangongNo ratings yet

- 串口通信Document47 pages串口通信maoyuhuiNo ratings yet

- GTM 382 Datenblatt enDocument2 pagesGTM 382 Datenblatt enJulius RachmanasNo ratings yet

- 基於opc Ua Tsn技術的工業通訊解決方案Document17 pages基於opc Ua Tsn技術的工業通訊解決方案YT LiuNo ratings yet

- 单片机的串行通信接口技术探讨Document4 pages单片机的串行通信接口技术探讨李宏观No ratings yet

- SIMOTION - XSEND - XRECEIVE 通信函数使用入门Document18 pagesSIMOTION - XSEND - XRECEIVE 通信函数使用入门李光明No ratings yet

- PXC系列控制器Document5 pagesPXC系列控制器Tim WongNo ratings yet

- The R2625 - R2670 APCO Project 25 - MR Test Equipment - en.zh-CNDocument4 pagesThe R2625 - R2670 APCO Project 25 - MR Test Equipment - en.zh-CN裴兆奇No ratings yet

- FlexRay 介绍Document11 pagesFlexRay 介绍Ryan WangNo ratings yet

- L2 考试试题Document45 pagesL2 考试试题vici archerNo ratings yet

- 北斗车载C1型终端技术规格书Document14 pages北斗车载C1型终端技术规格书jy00315189No ratings yet

- FBs PLCDocument28 pagesFBs PLC陳劍鋒No ratings yet

- Datasheet Cir2262Document3 pagesDatasheet Cir2262OVALLEPANo ratings yet

- HC-12 433Mhz SZH-CH069 PDFDocument13 pagesHC-12 433Mhz SZH-CH069 PDFMohamad RezazadeNo ratings yet

- Modbus高級通訊教程Document189 pagesModbus高級通訊教程alexwongks6118No ratings yet

- 第09章Document37 pages第09章张浩象No ratings yet

- 基于 CAN 的较高层协议和子协议-周立功Document25 pages基于 CAN 的较高层协议和子协议-周立功Kaede MatsushmaNo ratings yet

- 數據機Document1 page數據機bowos78400No ratings yet

- 第一章 TD-LTE概述Document10 pages第一章 TD-LTE概述grakiterNo ratings yet

- RS232,RS422,RS485的区别Document1 pageRS232,RS422,RS485的区别李宏观No ratings yet

- HRC 5000Document35 pagesHRC 5000INTERFONE SEM FIONo ratings yet

- Marconi Mstp Oms16xx 设备说明Document42 pagesMarconi Mstp Oms16xx 设备说明lf397426634No ratings yet

- 六.Global operationsDocument7 pages六.Global operationspaggyNo ratings yet

- Implementation and Test of The Embedded Ethernet Module of Microprocessor Protection PDFDocument4 pagesImplementation and Test of The Embedded Ethernet Module of Microprocessor Protection PDFshilps1234abcNo ratings yet

- $基于STM32的嵌入式测控系统设计 丁力Document6 pages$基于STM32的嵌入式测控系统设计 丁力huilin wuNo ratings yet

- DNP3 0规约Document203 pagesDNP3 0规约zhlNo ratings yet

- Modbus Manual CN20200715Document100 pagesModbus Manual CN20200715williamNo ratings yet

- ATBM8879 Product Brief (Chinese Lang)Document1 pageATBM8879 Product Brief (Chinese Lang)avrelecNo ratings yet

- Air720x (3229) 系列模块产品规格书 20191028Document2 pagesAir720x (3229) 系列模块产品规格书 20191028Thi KháchNo ratings yet

- 基于正弦波模型的Codec2语音解码器的设计和实现: 国际电子和通信工程研究杂志 工程 (Ijer Ece)Document7 pages基于正弦波模型的Codec2语音解码器的设计和实现: 国际电子和通信工程研究杂志 工程 (Ijer Ece)xiao zhanNo ratings yet

- CAN-bus 现场总线基础方案-通讯-周立功Document16 pagesCAN-bus 现场总线基础方案-通讯-周立功Kaede MatsushmaNo ratings yet