Professional Documents

Culture Documents

9D06106c Low Power VLSI Design

Uploaded by

raju.kprr8862Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

9D06106c Low Power VLSI Design

Uploaded by

raju.kprr8862Copyright:

Available Formats

Code: 9D06106c M.

Tech - I Semester Regular & Supplementary Examinations, April/May 2013 LOW POWER VLSI DESIGN

(Common to DSCE and DECS)

Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 (a) (b) 2 (a) (b) 3 (a) (b) 4 (a) (b) 5

Max Marks: 60

What are the low-voltage, low-power design considerations? Explain. What are the advantages and limitations of silicon-on-insulator technology? What are the BICMOS manufacturing and integration considerations? Explain. How graded drain structure can be produced? Mention the advantages. Give the device structure and describe the fabrication process of low-voltage/lowpower lateral BJT on SOI. With schematic diagrams explain about deep submicron processes. What are the features of HSPICE level 50 (Phillip MOS 69) model? Explain. Discuss in detail about limitations of MOSFET models. Draw the circuit for conventional BICMOS two-input NAND gate and describe its characteristics. Give the comparative evaluation of all the BICMOS circuits employing lateral parasitic PnP BJTs. What are the quality measures for latches and flip-flops? Explain. Explain about power reduction in clock networks. Explain in detail about low power techniques for SRAM. Write short note on the following: Sub-half micron MOS devices. Design perspectives of latches and flip-flops.

6 (a) (b) 7 (a) (b) 8 (a) (b)

*****

You might also like

- 9309 - CMOS Analog Design Chapter 8Document54 pages9309 - CMOS Analog Design Chapter 8raju.kprr8862No ratings yet

- Complete PCB Design Using OrCAD Capture and PCB EditorFrom EverandComplete PCB Design Using OrCAD Capture and PCB EditorRating: 5 out of 5 stars5/5 (1)

- 9D06106c Lower Power VLSI DesignDocument1 page9D06106c Lower Power VLSI Designjbsng123No ratings yet

- 9D06106c Low Power VLSI Design PDFDocument1 page9D06106c Low Power VLSI Design PDFVijay Kshatriya HRNo ratings yet

- Previous PapersDocument12 pagesPrevious PapersKaran SanaNo ratings yet

- Mar - 2010 - A7707-Low Power Vlsi DesignDocument1 pageMar - 2010 - A7707-Low Power Vlsi DesignvasuvlsiNo ratings yet

- A6508 - Low Power Vlsi DesignDocument2 pagesA6508 - Low Power Vlsi Designramanaidu1No ratings yet

- M.Tech I Semester Supplementary Examinations February/March 2018Document1 pageM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiNo ratings yet

- Intelligent Manufacturing SystemsDocument5 pagesIntelligent Manufacturing SystemsVenkata RamuduNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsContent for all CreatorNo ratings yet

- Roll No.: B. TechDocument3 pagesRoll No.: B. TechShivani VarshneyNo ratings yet

- SEPTEMBERDocument3 pagesSEPTEMBERRocky BobeeNo ratings yet

- VLSI DESIGN Question Bank: Unit 1Document12 pagesVLSI DESIGN Question Bank: Unit 1Babu GundlapallyNo ratings yet

- Previous Question PapersDocument4 pagesPrevious Question Papersshaker423No ratings yet

- MEDC-104 Vlsi Design Dec-2010Document2 pagesMEDC-104 Vlsi Design Dec-2010Prakash SinhaNo ratings yet

- LPVD 19-20 Mid SemDocument1 pageLPVD 19-20 Mid Semajay vermaNo ratings yet

- Time: 3 Hours Full Marks: 70Document3 pagesTime: 3 Hours Full Marks: 70pikluNo ratings yet

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDocument1 pageWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksNeil SamNo ratings yet

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANo ratings yet

- Mtech VLSI SyllabusDocument37 pagesMtech VLSI SyllabusRavindra vs100% (1)

- Jntu MDocument3 pagesJntu MVijay SagarNo ratings yet

- Vlsi Vlsi Design Dec 2020Document2 pagesVlsi Vlsi Design Dec 2020Margoob TanweerNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- Ec 1354Document5 pagesEc 1354kvnelavarasiNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document8 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsArchana TrivediNo ratings yet

- r7411001 Vlsi DesignDocument4 pagesr7411001 Vlsi DesignsivabharathamurthyNo ratings yet

- Vlsi Iae Question Paper PDFDocument1 pageVlsi Iae Question Paper PDFelakyaNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document2 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)venkiscribd444No ratings yet

- Low Power VLSI 2022-23Document1 pageLow Power VLSI 2022-23souranshusNo ratings yet

- Assignment 2 E5163 Sesi Jun 2011 Answer PDFDocument6 pagesAssignment 2 E5163 Sesi Jun 2011 Answer PDFsenyadnoireNo ratings yet

- BE - Semester-VI Examination B.E. (Ec) Semester Vi Subject Code: Subject Name: VLSI Technology and Design Date: Time: Total Marks: 70 InstructionsDocument1 pageBE - Semester-VI Examination B.E. (Ec) Semester Vi Subject Code: Subject Name: VLSI Technology and Design Date: Time: Total Marks: 70 Instructionshiren467_ecNo ratings yet

- VLSI DesignDocument5 pagesVLSI DesignqwertyuiopNo ratings yet

- Ec 1354 Vlsi DesignDocument5 pagesEc 1354 Vlsi Designdhasarathan_rajaNo ratings yet

- FPGA Based System DesignDocument2 pagesFPGA Based System Designammayi9845_930467904No ratings yet

- Sem1 EmbbededDocument9 pagesSem1 Embbededvishwanath cNo ratings yet

- Ec2354 Vlsi DesignDocument13 pagesEc2354 Vlsi Designjgssb85No ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- Question Bank For Mid-2 r13 (Vlsi) .Document6 pagesQuestion Bank For Mid-2 r13 (Vlsi) .rppvchNo ratings yet

- JNTUK2015Document1 pageJNTUK2015Sreekanth PagadapalliNo ratings yet

- Eprvd-102 Eprds-102a - 01.12 PDFDocument2 pagesEprvd-102 Eprds-102a - 01.12 PDFNaresh KumarNo ratings yet

- EM506 VLSI ArchitectureDocument5 pagesEM506 VLSI ArchitecturePrakash Velayudham VNo ratings yet

- Cmos AicdDocument22 pagesCmos AicdGurunath KanadeNo ratings yet

- Paper 1Document2 pagesPaper 1P KishoreNo ratings yet

- Rr320405 Vlsi DesignDocument6 pagesRr320405 Vlsi DesignSrinivasa Rao GNo ratings yet

- Set No: 1: Code No: V3219/R07Document4 pagesSet No: 1: Code No: V3219/R07Gopi Pavan JonnadulaNo ratings yet

- Chapter Wise QuestionsDocument2 pagesChapter Wise QuestionshjjhghgNo ratings yet

- VLSI DesignDocument7 pagesVLSI DesignVarun ThejNo ratings yet

- Time: 3 Hours Total Marks: 70: PD PLDocument1 pageTime: 3 Hours Total Marks: 70: PD PLDeepanshi RuhelaNo ratings yet

- Question BankDocument13 pagesQuestion BankRishi JhaNo ratings yet

- 9A05704 Advanced Computer ArchitectureDocument4 pages9A05704 Advanced Computer ArchitecturesivabharathamurthyNo ratings yet

- Code No: R05320402Document4 pagesCode No: R05320402chvsrsettiNo ratings yet

- VTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedDocument37 pagesVTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedAshik PadmanabhaNo ratings yet

- C H1074 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesC H1074 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDeepak KumarNo ratings yet

- Kang 1Document58 pagesKang 1123vidyaNo ratings yet

- S V University Exams Branch Enhancement of Rates For Various Examinations Fee With Effect From 01-07-2017 Communicated RegDocument12 pagesS V University Exams Branch Enhancement of Rates For Various Examinations Fee With Effect From 01-07-2017 Communicated Regraju.kprr8862No ratings yet

- Lesson Plan ADVD 2016-17Document5 pagesLesson Plan ADVD 2016-17raju.kprr8862No ratings yet

- Ch4 ISI and EqualizationDocument24 pagesCh4 ISI and Equalizationsuper_lativoNo ratings yet

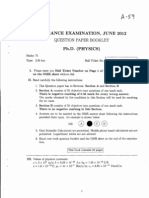

- PHD Physics EntranceDocument18 pagesPHD Physics Entrancekvanps_kumarNo ratings yet

- 02 WholeDocument160 pages02 Wholeraju.kprr8862No ratings yet

- 9D38104 Digital Communication TechniquesDocument1 page9D38104 Digital Communication Techniquesraju.kprr8862No ratings yet

- Analog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 3Document4 pagesAnalog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 3raju.kprr8862No ratings yet

- 9A02406 Network TheoryDocument8 pages9A02406 Network TheorysivabharathamurthyNo ratings yet

- CyberDocument2 pagesCyberraju.kprr8862No ratings yet

- 9A02406 Network TheoryDocument8 pages9A02406 Network TheorysivabharathamurthyNo ratings yet

- 4lab Moddemod PDFDocument9 pages4lab Moddemod PDFKhoirul Anam Al ImanNo ratings yet

- 9A04601 Digital CommunicationsDocument4 pages9A04601 Digital Communicationsraju.kprr8862No ratings yet

- 4lab Moddemod PDFDocument9 pages4lab Moddemod PDFKhoirul Anam Al ImanNo ratings yet

- Analog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013)Document4 pagesAnalog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013)raju.kprr8862No ratings yet

- Analog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 1Document4 pagesAnalog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 1raju.kprr8862No ratings yet

- 5 Linear Block CodesDocument29 pages5 Linear Block CodesSuprit PaulNo ratings yet

- ECE Test Series ScheduleDocument3 pagesECE Test Series Scheduleraju.kprr8862No ratings yet

- ELEN-610: Data Converters: Assignment #5Document1 pageELEN-610: Data Converters: Assignment #5raju.kprr8862No ratings yet

- AnalogDocument38 pagesAnalogecessecNo ratings yet

- 12D68101 Analog & Digital IC DesignDocument1 page12D68101 Analog & Digital IC Designraju.kprr8862No ratings yet

- 9311 - CMOS Analog Design Chapter 10Document23 pages9311 - CMOS Analog Design Chapter 10raju.kprr8862No ratings yet

- Sigdel PDFDocument22 pagesSigdel PDFraju.kprr8862No ratings yet

- RR310406 Digital CommunicationsDocument1 pageRR310406 Digital Communicationsraju.kprr8862No ratings yet

- Comparator SDocument57 pagesComparator Sraju.kprr8862No ratings yet

- Midterm1 PDFDocument8 pagesMidterm1 PDFraju.kprr8862No ratings yet

- Switched-Capacitor FundamentalsDocument20 pagesSwitched-Capacitor Fundamentalscleopatra2121No ratings yet

- Control Systems2Document4 pagesControl Systems2Peruru MuraliNo ratings yet