Professional Documents

Culture Documents

AD1 Introducao A Informatica 2007-1 Gabarito

Uploaded by

paulobrjOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

AD1 Introducao A Informatica 2007-1 Gabarito

Uploaded by

paulobrjCopyright:

Available Formats

Fundao CECIERJ - Vice Presidncia de Educao Superior a Distncia

Curso de Tecnologia em Sistemas de Computao UFF Disciplina INTRODUO INFORMTICA..... AD1 1 semestre de 2007. Data.......

AVALIAO DISTNCIA 1

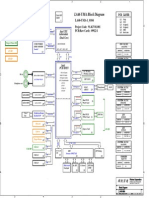

1. A figura a seguir mostra o painel traseiro de uma placa-me padro ATX. Procure identificar todos os tipos de conexo, citando o seu nome e pelo menos dois perifricos diferentes que podem ser conectados

2. Desde a primeira verso de computador pessoal baseado em chip-set Intel do tipo IBM-PC (atualmente conhecido apenas por PC), vrios tipos e padres de barramentos internos de expanso foram utilizados para conectar os mais diversos dispositivos, como por exemplo interface de rede, placa de vdeo, etc. Faa uma pesquisa e informe os seguintes dados para os diversos tipos de slots de expanso internos de PCs: a) b) c) d) Informe o que significa a sua sigla mostre o seu conector na placa-me (pode ser um desenho ou figura) a quantidade de bits de endereo a quantidade de bits de dados

e) f) g) h)

a capacidade de endereamento a largura da palavra, em bytes. o seu uso mais comum (tipo de perifrico para o qual foi desenvolvido) descreva a sua pinagem, informando o nome dos sinais. Procure na Internet

3. a) b) c) d) e)

Faa as mudanas de base abaixo mostrando todos os clculos efetuados: (1001.011)10 para a base 2 (3201678.23104)9 para a base 3 (540321)6 para a base 7 (CD65BA.C0BE)16 para a base 8 (30201.2331)8 para a base 4

4. Faa as operaes aritmticas abaixo indicando os resultados nas bases originais dos operandos: a) b) c) d) e) (CCAA)16 + (B9DC)16 (576765)8 + (757043)8 (300103)16 - (FDE0516 (100101101.1001)2 + (11101111.1111)2 (101100011.1001)2 - (11101101.1011)2

5. Sabendo que os nmeros fornecidos abaixo so representados internamente ao computador em registros de tamanho fixo de 8 bits; que destes, o bit mais significativo reservado para o sinal (0: positivo, 1: negativo), e que os negativos so representados em complemento a 2 , faa as operaes solicitadas no sistema binrio fornecendo os resultados nas notaes binria, hexadecimal e decimal e informando se estes so positivos ou negativos e ainda se a operao possvel ou gera erro. X = -(4D)16 a) X + Y b) X - Y c) Y - X Y = -(3E)16

Gabarito AD1 2007/1 2 pontos cada questo 1. 1 mouse PS2 (se a prova for P&B, aceitar tambm teclado) 2 impressora paralela 3 firewire 4 rede ethernet 5 entrada auxiliar 6 sada de som (auto-falante, caixa de som, etc.) 7 microfone 8 e 9 - usb 10 interface serial ou mouse (2 respostas aceitas) 11 SPDIF 12 teclado (se a prova for P&B, aceitar tambm mouse PS2)

2. EISA ou ISA a) Extended Industry Standard Architecture

b)

c) 24 bits de endereo d) 16 bits de dados e) 2^24 = 16 Mbytes f) 2 bytes g) uso geral h) ver item b PCI a) Peripheral Component Interconnect

b) c) 32 bits d) 32 bits ou 64 bits e) 2^32 = 4 Gbytes f) 4 ou 8 bytes g) uso geral h) Same with descriptions: Pin +5V +3.3V A1 TRST A2 +12V A3 TMS A4 TDI A5 +5V A6 INTA A7 INTC A8 +5V A9 RESV01 A10 +5V +3.3V A11 RESV03 A12 GND03 (OPEN) A13 GND05 (OPEN) A14 RESV05 A15 RESET A16 +5V +3.3V

Universal

Signal Rail (OPEN) (OPEN)

Signal Rail

Description Test Logic Reset +12 VDC Test Mde Select Test Data Input +5 VDC Interrupt A Interrupt C +5 VDC Reserved VDC +V I/O (+5 V or +3.3 V) Reserved VDC Ground or Open (Key) Ground or Open (Key) Reserved VDC Reset +V I/O (+5 V or +3.3 V)

A17 A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 A32 A33 A34 A35 A36 A37 A38 A39 A40 A41 A42 A43 A44 A45 A46 A47 A48 A49 A52 A53 A54 A55 A56 A57 A58 A59 A60

GNT GND08 RESV06 AD30 +3.3V01 AD28 AD26 GND10 AD24 IDSEL +3.3V03 AD22 AD20 GND12 AD18 AD16 +3.3V05 FRAME GND14 TRDY GND15 STOP +3.3V07 SDONE SBO GND17 PAR AD15 +3.3V10 AD13 AD11 GND19 AD9 C/BE0 +3.3V11 AD6 AD4 GND21 AD2 AD0 +5V REQ64

+3.3V

Signal Rail

Grant PCI use Ground Reserved VDC Address/Data 30 +3.3 VDC Address/Data 28 Address/Data 26 Ground Address/Data 24 Initialization Device Select +3.3 VDC Address/Data 22 Address/Data 20 Ground Address/Data 18 Address/Data 16 +3.3 VDC Address or Data phase Ground Target Ready Ground Stop Transfer Cycle +3.3 VDC Snoop Done Snoop Backoff Ground Parity Address/Data 15 +3.3 VDC Address/Data 13 Address/Data 11 Ground Address/Data 9 Command, Byte Enable 0 +3.3 VDC Address/Data 6 Address/Data 4 Ground Address/Data 2 Address/Data 0 +V I/O (+5 V or +3.3 V) Request 64 bit ???

A61 A62 A63 A64 A65 A66 A67 A68 A69 A70 A71 A72 A73 A74 A75 A76 A77 A78 A79 A80 A81 A82 A83 A84 A85 A86 A87 A88 A89 A90 A91 A92 A93 A94 B1 B2 B3 B4 B5 B6

VCC11 VCC13 GND C/BE[7]# C/BE[5]# +5V PAR64 AD62 GND AD60 AD58 GND AD56 AD54 +5V AD52 AD50 GND AD48 AD46 GND AD44 AD42 +5V AD40 AD38 GND AD36 AD34 GND AD32 RES GND RES -12V TCK GND TDO +5V +5V

+5 VDC +5 VDC Ground Command, Byte Enable 7 Command, Byte Enable 5 +V I/O (+5 V or +3.3 V) Parity 64 ??? Address/Data 62 Ground Address/Data 60 Address/Data 58 Ground Address/Data 56 Address/Data 54 +V I/O (+5 V or +3.3 V) Address/Data 52 Address/Data 50 Ground Address/Data 48 Address/Data 46 Ground Address/Data 44 Address/Data 42 +V I/O (+5 V or +3.3 V) Address/Data 40 Address/Data 38 Ground Address/Data 36 Address/Data 34 Ground Address/Data 32 Reserved Ground Reserved -12 VDC Test Clock Ground Test Data Output +5 VDC +5 VDC

+3.3V

Signal Rail

+3.3V

Signal Rail

+3.3V

Signal Rail

B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17 B18 B19 B20 B21 B22 B23 B24 B25 B26 B27 B28 B29 B30 B31 B32 B33 B34 B35 B36 B37 B38 B39 B40 B41 B42 B43 B44 B45 B46 B47 B48

INTB INTD PRSNT1 RES PRSNT2 GND GND RES GND CLK GND REQ +5V AD31 AD29 GND AD27 AD25 +3.3V C/BE3 AD23 GND AD21 AD19 +3.3V AD17 C/BE2 GND13 IRDY +3.3V06 DEVSEL GND16 LOCK PERR +3.3V08 SERR +3.3V09 C/BE1 AD14 GND18 AD12 AD10

(OPEN) (OPEN)

(OPEN) (OPEN)

+3.3V

Signal Rail

Interrupt B Interrupt D Reserved +V I/O (+5 V or +3.3 V) ?? Ground or Open (Key) Ground or Open (Key) Reserved VDC Reset Clock Ground Request +V I/O (+5 V or +3.3 V) Address/Data 31 Address/Data 29 Ground Address/Data 27 Address/Data 25 +3.3VDC Command, Byte Enable 3 Address/Data 23 Ground Address/Data 21 Address/Data 19 +3.3 VDC Address/Data 17 Command, Byte Enable 2 Ground Initiator Ready +3.3 VDC Device Select Ground Lock bus Parity Error +3.3 VDC System Error +3.3 VDC Command, Byte Enable 1 Address/Data 14 Ground Address/Data 12 Address/Data 10

B49 B50 B51 B52 B53 B54 B55 B56 B57 B58 B59 B60 B61 B62 B63 B64 B65 B66 B67 B68 B69 B70 B71 B72 B73 B74 B75 B76 B77 B78 B79 B80 B81 B82 B83 B84 B85 B86 B87 B88 B89

GND20 (OPEN) (OPEN) AD8 AD7 +3.3V12 AD5 AD3 GND22 AD1 VCC08 ACK64 VCC10 VCC12 RES GND C/BE[6]# C/BE[4]# GND AD63 AD61 +5V AD59 AD57 GND AD55 AD53 GND AD51 AD49 +5V AD47 AD45 GND AD43 AD41 GND AD39 AD37 +5V AD35

GND GND

(OPEN) (OPEN)

Ground Ground or Open (Key) Ground or Open (Key) Address/Data 8 Address/Data 7 +3.3 VDC Address/Data 5 Address/Data 3 Ground Address/Data 1 +5 VDC Acknowledge 64 bit ??? +5 VDC +5 VDC Reserved Ground Command, Byte Enable 6 Command, Byte Enable 4 Ground Address/Data 63 Address/Data 61 +V I/O (+5 V or +3.3 V) Address/Data 59 Address/Data 57 Ground Address/Data 55 Address/Data 53 Ground Address/Data 51 Address/Data 49 +V I/O (+5 V or +3.3 V) Address/Data 47 Address/Data 45 Ground Address/Data 43 Address/Data 41 Ground Address/Data 39 Address/Data 37 +V I/O (+5 V or +3.3 V) Address/Data 35

+3.3V

Signal Rail

+3.3V

Signal Rail

+3.3V

Signal Rail

B90 B91 B92 B93 B94

AD33 GND RES RES GND

Address/Data 33 Ground Reserved Reserved Ground

PCI-Express a) Peripheral Component Interconnect Express

b) c) d) e) f) g) h)

Serial Serial No se aplica No se aplica Substituio de PCI e AGP (principalmente interface de vdeo)

PCI-Express 1x Connector Pin-Out

Pi n # 1 2 3 4 5 6 7 Side B Connector Name +12v +12v Description +12 volt power +12 volt power Name Side A Connector Description

PRSNT Hot plug presence detect #1 +12v +12v GND +12 volt power +12 volt power Ground

RSVD Reserved GND Ground

SMCL SMBus clock K SMDA SMBus data T GND Ground

JTAG2 TCK JTAG3 TDI JTAG4 TDO

8 9 10 11

+3.3v

+3.3 volt power

JTAG5 TMS +3.3v +3.3v +3.3 volt power +3.3 volt power

JTAG1 +TRST# 3.3Vau 3.3v volt power x WAKE Link Reactivation #

PWRG Power Good D

Mechanical Key 12 RSVD Reserved 13 GND Ground GND Ground

REFCL K+ Reference Clock Differential pair HSOp( REFCL 14 0) Transmitter Lane 0, KDifferential pair HSOn( GND Ground 15 0) 16 GND 17 Ground HSIp(0 ) Receiver Lane 0, Differential pair HSIn(0 ) GND Ground

PRSNT Hotplug detect #2 Ground

18 GND

PCI-Express 4x Connector Pin-Out

Pi n # 1 2 3 4 5 Side B Connector Name +12v +12v Description +12 volt power +12 volt power Name Side A Connector Description

PRSNT Hot plug presence detect #1 +12v +12v GND +12 volt power +12 volt power Ground

RSVD Reserved GND Ground

SMCL SMBus clock

JTAG2 TCK

K 6 7 8 9 10 11 SMDA SMBus data T GND +3.3v Ground +3.3 volt power JTAG3 TDI JTAG4 TDO JTAG5 TMS +3.3v +3.3v +3.3 volt power +3.3 volt power

JTAG1 +TRST# 3.3Vau 3.3v volt power x WAKE Link Reactivation #

PWRG Power Good D

Mechanical Key 12 RSVD Reserved 13 GND Ground GND Ground

REFCL K+ Reference Clock Differential pair HSOp( REFCL 14 0) Transmitter Lane 0, KDifferential pair HSOn( GND Ground 15 0) 16 GND 17 Ground HSIp(0 ) Receiver Lane 0, Differential pair HSIn(0 ) GND Ground

PRSNT Hotplug detect #2 Ground

18 GND 19

HSOp( RSVD Reserved 1) Transmitter Lane 1, Differential pair HSOn( GND Ground 20 1) 21 GND Ground HSIp(1 Receiver Lane 1, ) Differential pair

22 GND 23

Ground

HSIn(1 ) Ground Ground

HSOp( GND 2) Transmitter Lane 2, Differential pair HSOn( GND 24 2) 25 GND 26 GND 27 Ground Ground

HSIp(2 ) Receiver Lane 2, Differential pair HSIn(2 ) Ground Ground

HSOp( GND 3) Transmitter Lane 3, Differential pair HSOn( GND 28 0) 29 GND Ground

30 RSVD Reserved 31 PRSNT Hot plug detect #2 Ground

HSIp(3 ) Receiver Lane 3, Differential pair HSIn(3 ) GND Ground

32 GND

RSVD Reserved

PCI-Express 8x Connector Pin-Out

Pi n # 1 2 3 4 Side B Connector Name +12v +12v Description +12 volt power +12 volt power Name Side A Connector Description

PRSNT Hot plug presence detect #1 +12v +12v GND +12 volt power +12 volt power Ground

RSVD Reserved GND Ground

5 6 7 8 9 10 11

SMCL SMBus clock K SMDA SMBus data T GND +3.3v Ground +3.3 volt power

JTAG2 TCK JTAG3 TDI JTAG4 TDO JTAG5 TMS +3.3v +3.3v +3.3 volt power +3.3 volt power

JTAG1 +TRST# 3.3Vau 3.3v volt power x WAKE Link Reactivation #

PWRG Power Good D

Mechanical Key 12 RSVD Reserved 13 GND Ground GND Ground

REFCL K+ Reference Clock Differential pair HSOp( REFCL 14 0) Transmitter Lane 0, KDifferential pair HSOn( GND Ground 15 0) 16 GND 17 Ground HSIp(0 ) Receiver Lane 0, Differential pair HSIn(0 ) GND Ground

PRSNT Hotplug detect #2 Ground

18 GND 19

HSOp( RSVD Reserved 1) Transmitter Lane 1, Differential pair HSOn( GND Ground 20 1) 21 GND Ground HSIp(1 Receiver Lane 1, ) Differential pair

22 GND 23

Ground

HSIn(1 ) Ground Ground

HSOp( GND 2) Transmitter Lane 2, Differential pair HSOn( GND 24 2) 25 GND 26 GND 27 Ground Ground

HSIp(2 ) Receiver Lane 2, Differential pair HSIn(2 ) Ground Ground

HSOp( GND 3) Transmitter Lane 3, Differential pair HSOn( GND 28 0) 29 GND Ground

30 RSVD Reserved 31 PRSNT Hot plug detect #2 Ground

HSIp(3 ) Receiver Lane 3, Differential pair HSIn(3 ) GND Ground

32 GND 33

RSVD Reserved

HSOp( RSVD Reserved 4) Transmitter Lane 4, Differential pair HSOn( GND Ground 34 4) 35 GND 36 GND 37 Ground Ground HSIp(4 ) Receiver Lane 4, Differential pair HSIn(4 ) Ground

HSOp( Transmitter Lane 5, GND 5) Differential pair

38

HSOn( 5) Ground Ground

GND

Ground

39 GND 40 GND 41

HSIp(5 ) Receiver Lane 5, Differential pair HSIn(5 ) Ground Ground

HSOp( GND 6) Transmitter Lane 6, Differential pair HSOn( GND 42 6) 43 GND 44 GND 45 Ground Ground

HSIp(6 ) Receiver Lane 6, Differential pair HSIn(6 ) Ground Ground

HSOp( GND 7) Transmitter Lane 7, Differential pair HSOn( GND 46 7) 47 GND 48 Ground

PRSNT Hot plug detect #2 Ground

HSIp(7 ) Receiver Lane 7, Differential pair HSIn(7 ) GND Ground

49 GND

PCI-Express 16x Connector Pin-Out

Pi n # 1 2 Side B Connector Name Description +12v +12v +12 volt power +12 volt power Side A Connector Name Description PRSN Hot plug presence T#1 detect +12v +12 volt power

3 4 5 6 7 8 9 10 11

RSVD Reserved GND Ground

+12v GND

+12 volt power Ground

SMCL SMBus clock K SMDA SMBus data T GND Ground

JTAG2 TCK JTAG3 TDI JTAG4 TDO JTAG5 TMS +3.3v +3.3 volt power +3.3v +3.3 volt power PWRG Power Good D

+3.3v +3.3 volt power JTAG1 +TRST# 3.3Vau 3.3v volt power x WAKE Link Reactivation #

Mechanical Key 12 RSVD Reserved 13 GND 14 Ground GND Ground

HSOp( 0) Transmitter Lane 0, Differential pair HSOn( 15 0) 16 GND 17 Ground

REFC LK+ Reference Clock Differential pair REFC LKGND Ground

PRSN Hotplug detect T#2 Ground

HSIp(0 ) Receiver Lane 0, Differential pair HSIn(0 ) GND Ground

18 GND 19

HSOp( 1) Transmitter Lane 1, Differential pair HSOn( 20 1)

RSVD Reserved GND Ground

21 GND 22 GND 23

Ground Ground

HSIp(1 ) Receiver Lane 1, Differential pair HSIn(1 ) GND GND Ground Ground

HSOp( 2) Transmitter Lane 2, Differential pair HSOn( 24 2) 25 GND 26 GND 27 Ground Ground

HSIp(2 ) Receiver Lane 2, Differential pair HSIn(2 ) GND GND Ground Ground

HSOp( 3) Transmitter Lane 3, Differential pair HSOn( 28 3) 29 GND Ground

30 RSVD Reserved 31 PRSN Hot plug detect T#2 Ground

HSIp(3 ) Receiver Lane 3, Differential pair HSIn(3 ) GND Ground

32 GND 33

RSVD Reserved RSVD Reserved GND Ground

HSOp( 4) Transmitter Lane 4, Differential pair HSOn( 34 4) 35 GND 36 GND Ground Ground

HSIp(4 ) Receiver Lane 4, Differential pair HSIn(4 )

HSOp( 5) Transmitter Lane 5, Differential pair HSOn( 38 5) 37 39 GND 40 GND 41 Ground Ground

GND GND

Ground Ground

HSIp(5 ) Receiver Lane 5, Differential pair HSIn(5 ) GND GND Ground Ground

HSOp( 6) Transmitter Lane 6, Differential pair HSOn( 42 6) 43 GND 44 GND 45 Ground Ground

HSIp(6 ) Receiver Lane 6, Differential pair HSIn(6 ) GND GND Ground Ground

HSOp( 7) Transmitter Lane 7, Differential pair HSOn( 46 7) 47 GND 48 Ground

PRSN Hot plug detect T#2 Ground

HSIp(7 ) Receiver Lane 7, Differential pair HSIn(7 ) GND Ground

49 GND 50

HSOp( 8) Transmitter Lane 8, Differential pair HSOn( 51 8) 52 GND Ground

RSVD Reserved GND Ground

HSIp(8 Receiver Lane 8, ) Differential pair

53 GND 54

Ground

HSIn(8 ) GND GND Ground Ground

HSOp( 9) Transmitter Lane 9, Differential pair HSOn( 55 9) 56 GND 57 GND 58 Ground Ground

HSIp(9 ) Receiver Lane 9, Differential pair HSIn(9 ) GND GND Ground Ground

HSOp( 10) Transmitter Lane 10, Differential pair HSOn( 59 10) 60 GND 61 GND 62 Ground Ground

HSIp(1 0) Receiver Lane 10, Differential pair HSIn(1 0) GND GND Ground Ground

HSOp( 11) Transmitter Lane 11, Differential pair HSOn( 63 11) 64 GND 65 GND 66 Ground Ground

HSIp(1 1) Receiver Lane 11, Differential pair HSIn(1 1) GND GND Ground Ground

HSOp( 12) Transmitter Lane 12, Differential pair HSOn( 67 12) 68 GND Ground

HSIp(1 Receiver Lane 12, 2) Differential pair

69 GND 70

Ground

HSIn(1 2) GND GND Ground Ground

HSOp( 13) Transmitter Lane 13, Differential pair HSOn( 71 13) 72 GND 73 GND 74 Ground Ground

HSIp(1 3) Receiver Lane 13, Differential pair HSIn(1 3) GND GND Ground Ground

HSOp( 14) Transmitter Lane 14, Differential pair HSOn( 75 14) 76 GND 77 GND 78 Ground Ground

HSIp(1 4) Receiver Lane 14, Differential pair HSIn(1 4) GND GND Ground Ground

HSOp( 15) Transmitter Lane 15, Differential pair HSOn( 79 15) 80 GND 81 82 Ground

PRSN Hot plug present T#2 detect RSVD Hot Plug Detect #2

HSIp(1 5) Receiver Lane 15, Differential pair HSIn(1 5) GND Ground

AGP a) Accelerated Graphics Port ou Advanced Graphics Port

b) c) d) e) f) g) h)

32 bits 32 bits 4 Gbytes 4 bytes Interfaces de video 3.3 Volt Boards Universal Boards Side A +12V Side B OVRCNT# 1.5 Volt Boards Side A +12V Side B OVRCNT#

Pin # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Side A +12V

Side B OVRCNT#

TYPEDET# +5.0V Reserved USBGround INTA# RST# GNT# VCC 3.3 ST1 Reserved PIPE# Ground Reserved SBA1 VCC 3.3 5.0V USB+ Ground INTB# CLK REQ# VCC 3.3 ST0 ST2 RBF# Ground Reserved SBA0 VCC 3.3

TYPEDET# +5.0V Reserved USBGround INTA# RST# GNT# VCC 3.3 ST1 Reserved PIPE# Ground WBF# SBA1 VCC 3.3 5.0V USB+ Ground INTB# CLK REQ# VCC 3.3 ST0 ST2 RBF# Ground Reserved SBA0 VCC 3.3

TYPEDET# +5.0V Reserved USBGround INTA# RST# GNT# VCC 3.3 ST1 Reserved PIPE# Ground WBF# SBA1 VCC 3.3 5.0V USB+ Ground INTB# CLK REQ# VCC 3.3 ST0 ST2 RBF# Ground Reserved SBA0 VCC 3.3

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

SBA3 Reserved Ground SBA5 SBA7 Key Key Key Key AD30 AD28 VCC 3.3 AD26 AD24 Ground Reserved C/BE3# Vddq 3.3 AD22 AD20 Ground AD18 AD16 Vddq 3.3

SBA2 SB_STB Ground SBA4 SBA6 Key Key Key Key AD31 AD29 VCC 3.3 AD27 AD25 Ground AD STB1 AD23 Vddq 3.3 AD21 AD19 Ground AD17 C/BE2# Vddq 3.3

SBA3 SB_STB# Ground SBA5 SBA7 Reserved GROUND Reserved Vcc 3.3 AD30 AD28 VCC 3.3 AD26 AD24 Ground AD STB1# C/BE3# Vddq AD22 AD20 Ground AD18 AD16 Vddq

SBA2 SB_STB Ground SBA4 SBA6 Reserved GROUND 3.3Vaux Vcc 3.3 AD31 AD29 VCC 3.3 AD27 AD25 Ground AD STB1 AD23 Vddq AD21 AD19 Ground AD17 C/BE2# Vddq

SBA3 SB_STB# Ground SBA5 SBA7 Reserved GROUND Reserved Vcc 3.3 AD30 AD28 VCC 3.3 AD26 AD24 Ground AD STB1# C/BE3# Vddq 1.5 AD22 AD20 Ground AD18 AD16 Vddq 1.5

SBA2 SB_STB Ground SBA4 SBA6 Reserved GROUND 3.3Vaux Vcc 3.3 AD31 AD29 VCC 3.3 AD27 AD25 Ground AD STB1 AD23 Vddq 1.5 AD21 AD19 Ground AD17 C/BE2# Vddq 1.5

41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 A62 63 64

FRAME# Reserved Ground Reserved VCC 3.3 TRDY# STOP# PME# Ground PAR AD15 Vddq 3.3 AD13 AD11 Ground AD9 C/BE0# Vddq 3.3 Reserved AD6 Ground AD4 AD2 Vddq 3.3

IRDY# 3.3Vaux Ground Reserved VCC 3.3 DEVSEL# Vddq 3.3 PERR# Ground SERR# C/BE1# Vddq 3.3 AD14 AD12 Ground AD10 AD8 Vddq 3.3 AD STB0 AD7 Ground AD5 AD3 Vddq 3.3

FRAME# Reserved Ground Reserved VCC 3.3 TRDY# STOP# PME# Ground PAR AD15 Vddq AD13 AD11 Ground AD9 C/BE0# Vddq Reserved AD6 Ground AD4 AD2 Vddq

IRDY# 3.3Vaux Ground Reserved VCC 3.3 DEVSEL# Vddq PERR# Ground SERR# C/BE1# Vddq AD14 AD12 Ground AD10 AD8 Vddq AD STB0# AD7 Ground AD5 AD3 Vddq

FRAME# KEY KEY KEY KEY TRDY# STOP# PME# Ground PAR AD15 Vddq 1.5 AD13 AD11 Ground AD9 C/BE0# Vddq 1.5 Reserved AD6 Ground AD4 AD2 Vddq 1.5

IRDY# KEY KEY KEY KEY DEVSEL# Vddq 1.5 PERR# Ground SERR# C/BE1# Vddq 1.5 AD14 AD12 Ground AD10 AD8 Vddq 1.5 AD STB0# AD7 Ground AD5 AD3 Vddq 1.5

65 66

AD0 Reserved

AD1 Reserved

AD0 Vrefcg

AD1 Vrefcg

AD0 Vrefcg

AD1 Vrefcg

3. a) b) c) d) e) 4. a) b) c) d) e) 5. a) X + Y A operao gera erro de overflow, pois o resultado negativo em complemento 2, (101110101)2 = -(139)10 = -(8B)16 no pode ser armazenado em 8 bits. b) X Y Resultado: (11110001)2 (em compl. 2) = -(15)10 = -(0F)16 c) Y X Resultado: (00001111)2 (em compl. 2) = +(15)10 = +(0F)16 (18686)16 (1556030)8 (2022FE)16 (1000011101.1)2 (1110101.111)2 (1111101001.000000101101...)2 (10020001202122.0210010011)3 (242551)7 (63262672.60137)8 (3002001.103121)4

You might also like

- Manual LCD TV BeryllusDocument50 pagesManual LCD TV BeryllusNascNet100% (5)

- Pinagen e Descrição DB 25 e db9Document9 pagesPinagen e Descrição DB 25 e db9vinyxxxNo ratings yet

- 4806 727 17392 PDFDocument73 pages4806 727 17392 PDFMarcio Antonio MachadoNo ratings yet

- Wistron Ds2 Uma - Amd - Dell 1526Document44 pagesWistron Ds2 Uma - Amd - Dell 1526Vinicius SoaresNo ratings yet

- Conexões e cabos seriais RS-232Document5 pagesConexões e cabos seriais RS-232Bruno BatistaNo ratings yet

- Conversão Protocolos USB RS232 RS485Document9 pagesConversão Protocolos USB RS232 RS485JOEL FARIA HAUKNo ratings yet

- Philips Ch. Lc9.2l LaDocument72 pagesPhilips Ch. Lc9.2l LaSeminarski RadoviNo ratings yet

- Guia técnico de chassis de televisão a coresDocument81 pagesGuia técnico de chassis de televisão a coresHector OviedoNo ratings yet

- TV LCD Philips 32plf5604 78 Chassis Tcm3 2L LA PortuguesDocument67 pagesTV LCD Philips 32plf5604 78 Chassis Tcm3 2L LA Portuguesgreenpis100% (1)

- 715G3214Document100 pages715G3214Vagner Augusto100% (1)

- Philips 32PFL3403Document80 pagesPhilips 32PFL3403Leonardo Reyes GonsalezNo ratings yet

- Philips 32PFL3403 Chasis LC8.1L-LADocument80 pagesPhilips 32PFL3403 Chasis LC8.1L-LALuis Juan CaldoNo ratings yet

- Philips Chassis l03.1l Aa 20pt4331-78 Schematic DiagramDocument13 pagesPhilips Chassis l03.1l Aa 20pt4331-78 Schematic DiagramИегҵ ГемасснеNo ratings yet

- Treinamento BDX PlusDocument54 pagesTreinamento BDX Pluslaurotvlar100% (1)

- WEG Controlador PFW e Multimedidor MMW 50025399 Catalogo Portugues BRDocument12 pagesWEG Controlador PFW e Multimedidor MMW 50025399 Catalogo Portugues BRFelipe Sales100% (1)

- Guia técnico de TV a cores com especificações, conexões e diagramasDocument73 pagesGuia técnico de TV a cores com especificações, conexões e diagramasHeron Cesar VieiraNo ratings yet

- Lenovo b460 v460 Wistron La46 Uma Rev 1Document48 pagesLenovo b460 v460 Wistron La46 Uma Rev 1Herman ToothrotNo ratings yet

- CABO COAXIAL E1 DB15Document17 pagesCABO COAXIAL E1 DB15Vitor Monteiro Pelarin0% (1)

- Aula 5 - Exercicios 8085Document16 pagesAula 5 - Exercicios 8085Paulo EduardoNo ratings yet

- Teste PCI 12 Derivações 2 PDFDocument15 pagesTeste PCI 12 Derivações 2 PDFMarcelo PriebeNo ratings yet

- Pamirs - Uma - 06228-SB R-1 0214Document41 pagesPamirs - Uma - 06228-SB R-1 0214nikola1660100% (1)

- TV Philips 26PF5321-manual de Serviço (Chassis LC4.3Uaa)Document89 pagesTV Philips 26PF5321-manual de Serviço (Chassis LC4.3Uaa)Alexandre Morgado67% (3)

- Manual Servico TV LCD Philips Chassis Tcm3 1L LaDocument71 pagesManual Servico TV LCD Philips Chassis Tcm3 1L LabrazlucasNo ratings yet

- Guia completo do Step Servo Kalatec KTC-DR34ECDocument26 pagesGuia completo do Step Servo Kalatec KTC-DR34ECFrancisco RodriguesNo ratings yet

- G31VS2 M ManualDocument11 pagesG31VS2 M ManualPriscila Poeta Darley67% (3)

- Manual Eletrico IAC-500 Rev 1 - A.15Document48 pagesManual Eletrico IAC-500 Rev 1 - A.15Grupo Mais Segurança & MonitoramentoNo ratings yet

- Acer Jm41 (Uma)Document40 pagesAcer Jm41 (Uma)rasrozi5170100% (1)

- Frequências Horizontais e Especificações Técnicas LCD 15 e 20Document45 pagesFrequências Horizontais e Especificações Técnicas LCD 15 e 20Juan Carlos PerdomoNo ratings yet

- Sony Vaio Vgn-Ar71mrDocument73 pagesSony Vaio Vgn-Ar71mrRommel LoayzaNo ratings yet

- Manutenção TV coloridaDocument61 pagesManutenção TV coloridaLuis Antonio Rivas RodriguezNo ratings yet

- TV a cores LC4.8LLA guia de serviçoDocument88 pagesTV a cores LC4.8LLA guia de serviçoJuan Palavecino0% (1)

- TV Colorida Chassis TCM3.1L ManualDocument71 pagesTV Colorida Chassis TCM3.1L ManualVicente MalvicaNo ratings yet

- Medindo O Valor De Pico Para Uma Medição De Co2 Com A Raspberry Pi Programada Em PythonFrom EverandMedindo O Valor De Pico Para Uma Medição De Co2 Com A Raspberry Pi Programada Em PythonNo ratings yet

- Projetos Com Stm8s103f3 Programado Em Arduino - Parte XxviiFrom EverandProjetos Com Stm8s103f3 Programado Em Arduino - Parte XxviiNo ratings yet

- Medindo O Valor De Pico Para Uma Medição De Barômetro Com A Raspberry Pi Programada Em PythonFrom EverandMedindo O Valor De Pico Para Uma Medição De Barômetro Com A Raspberry Pi Programada Em PythonNo ratings yet

- Medindo O Valor De Pico Para Uma Medição De Etanol Com A Raspberry Pi Programada Em PythonFrom EverandMedindo O Valor De Pico Para Uma Medição De Etanol Com A Raspberry Pi Programada Em PythonNo ratings yet

- Análise De Vibração Com Stm32f103 Com Dft Programado No Arduino E Visual BasicFrom EverandAnálise De Vibração Com Stm32f103 Com Dft Programado No Arduino E Visual BasicNo ratings yet

- Enviando A Medição De Gaussímetro Para Monitoramento No Vc# Com A Raspberry Pi Programada Em PythonFrom EverandEnviando A Medição De Gaussímetro Para Monitoramento No Vc# Com A Raspberry Pi Programada Em PythonNo ratings yet

- Medindo O Valor De Pico Para Uma Medição De Dinamômetro Com A Raspberry Pi Programada Em PythonFrom EverandMedindo O Valor De Pico Para Uma Medição De Dinamômetro Com A Raspberry Pi Programada Em PythonNo ratings yet

- Medindo O Valor De Pico Para Uma Medição De Ozônio Com A Raspberry Pi Programada Em PythonFrom EverandMedindo O Valor De Pico Para Uma Medição De Ozônio Com A Raspberry Pi Programada Em PythonNo ratings yet

- Enviando A Medição De Barômetro Para Monitoramento No Vb Com A Raspberry Pi Programada Em PythonFrom EverandEnviando A Medição De Barômetro Para Monitoramento No Vb Com A Raspberry Pi Programada Em PythonNo ratings yet

- Enviando A Medição De Álcool Para Monitoramento No Vb Com A Raspberry Pi Programada Em PythonFrom EverandEnviando A Medição De Álcool Para Monitoramento No Vb Com A Raspberry Pi Programada Em PythonNo ratings yet

- Análise De Vibração Com Stm32f103 Com Dft Programado No Arduino E Visual C#From EverandAnálise De Vibração Com Stm32f103 Com Dft Programado No Arduino E Visual C#No ratings yet

- Medindo O Valor De Pico Para Uma Medição De Gaussímetro Com A Raspberry Pi Programada Em PythonFrom EverandMedindo O Valor De Pico Para Uma Medição De Gaussímetro Com A Raspberry Pi Programada Em PythonNo ratings yet

- Medindo O Valor De Pico Para Uma Medição De Benzeno Com A Raspberry Pi Programada Em PythonFrom EverandMedindo O Valor De Pico Para Uma Medição De Benzeno Com A Raspberry Pi Programada Em PythonNo ratings yet

- Enviando A Medição De Barômetro Para Monitoramento No Vc# Com A Raspberry Pi Programada Em PythonFrom EverandEnviando A Medição De Barômetro Para Monitoramento No Vc# Com A Raspberry Pi Programada Em PythonNo ratings yet

- Enviando A Medição De Gaussímetro Para Monitoramento No Vb Com A Raspberry Pi Programada Em PythonFrom EverandEnviando A Medição De Gaussímetro Para Monitoramento No Vb Com A Raspberry Pi Programada Em PythonNo ratings yet

- Enviando A Medição De Decibelímetro Para Monitoramento No Vc# Com A Raspberry Pi Programada Em PythonFrom EverandEnviando A Medição De Decibelímetro Para Monitoramento No Vc# Com A Raspberry Pi Programada Em PythonNo ratings yet

- Projetos No Vb Para Raspberry Pi 3 Com Windows 10 Iot Core Parte XFrom EverandProjetos No Vb Para Raspberry Pi 3 Com Windows 10 Iot Core Parte XNo ratings yet

- Enviando A Medição De H2 Para Monitoramento No Vb Com A Raspberry Pi Programada Em PythonFrom EverandEnviando A Medição De H2 Para Monitoramento No Vb Com A Raspberry Pi Programada Em PythonNo ratings yet

- 43 PDFDocument1 page43 PDFpaulobrjNo ratings yet

- Manual 2fase 04 Anexo1 PDFDocument4 pagesManual 2fase 04 Anexo1 PDFGuilherme BotelhoNo ratings yet

- Recibos de Compra e Venda de Imóveis GrátisDocument1 pageRecibos de Compra e Venda de Imóveis Grátispaulobrj100% (3)

- Conter o Poder PunitivoDocument4 pagesConter o Poder PunitivopaulobrjNo ratings yet

- 9 Formas de Usar o Linux para Consertar o Seu Windows (Vídeo) - TecmundoDocument18 pages9 Formas de Usar o Linux para Consertar o Seu Windows (Vídeo) - TecmundopaulobrjNo ratings yet

- Governo Do Rio É Proibido de Conceder Novas Isenções FiscaisDocument2 pagesGoverno Do Rio É Proibido de Conceder Novas Isenções FiscaispaulobrjNo ratings yet

- Folha de Audiência - Única Com NomeDocument1 pageFolha de Audiência - Única Com NomepaulobrjNo ratings yet

- PROCESSOS GERENCIAIS - Guia Do Estudante PDFDocument2 pagesPROCESSOS GERENCIAIS - Guia Do Estudante PDFpaulobrjNo ratings yet

- Paj 2015 - 00241 - AndreiDocument6 pagesPaj 2015 - 00241 - AndreipaulobrjNo ratings yet

- Civil 6Document2 pagesCivil 6paulobrjNo ratings yet

- Existe Algum Curso Na Área Ambiental Que Não Use Muito Exatas - Guia Do EstudanteDocument2 pagesExiste Algum Curso Na Área Ambiental Que Não Use Muito Exatas - Guia Do EstudantepaulobrjNo ratings yet

- Os Estados de São Paulo eDocument8 pagesOs Estados de São Paulo epaulobrjNo ratings yet

- Introdução À Informática-CEDERJ - 03Document37 pagesIntrodução À Informática-CEDERJ - 03paulobrjNo ratings yet

- 20 Dicas para Estudantes de DireitoDocument5 pages20 Dicas para Estudantes de DireitopaulobrjNo ratings yet

- Recursos DidaticosDocument4 pagesRecursos DidaticospaulobrjNo ratings yet

- 3 - Filhos Do AfetoDocument2 pages3 - Filhos Do AfetopaulobrjNo ratings yet

- Cespe Sefaz EsDocument8 pagesCespe Sefaz EspaulobrjNo ratings yet

- Introdução À Informática-CEDERJ - 12Document49 pagesIntrodução À Informática-CEDERJ - 12paulobrjNo ratings yet

- Guia Certificacao Enem 2012Document11 pagesGuia Certificacao Enem 2012Bruna Karoline ZwirtesNo ratings yet

- Aula - 02 - Bit e ByteDocument27 pagesAula - 02 - Bit e ByteFormador VerissimoNo ratings yet

- As Palavras Mais Comuns Da Lingua Inglesa Rubens Queiroz de AlmeidaDocument137 pagesAs Palavras Mais Comuns Da Lingua Inglesa Rubens Queiroz de AlmeidaThalles Henrique100% (1)

- Introdução À Informática-CEDERJ - 01Document25 pagesIntrodução À Informática-CEDERJ - 01paulobrjNo ratings yet

- Inglês BBC em 30 CDsDocument5 pagesInglês BBC em 30 CDsCamila Garcia LopesNo ratings yet

- Apostila Aisipoa MapaDocument568 pagesApostila Aisipoa Mapaufrrj92% (12)

- Pasta 1Document2 pagesPasta 1paulobrjNo ratings yet

- Aprendendo A Programar - Programando Na Linguagem CDocument139 pagesAprendendo A Programar - Programando Na Linguagem CAllanDenis100% (5)

- Por que ir além da discussão sobre métodos de alfabetizaçãoDocument15 pagesPor que ir além da discussão sobre métodos de alfabetizaçãoraquel_krika100% (1)

- Hard Reset - Resete Total Samsung Galaxy Ace S5830 - Restaurar Parâmetros de Fábrica Portal - Phoneinfo - SolutionsDocument8 pagesHard Reset - Resete Total Samsung Galaxy Ace S5830 - Restaurar Parâmetros de Fábrica Portal - Phoneinfo - SolutionspaulobrjNo ratings yet

- Politica de CorreioDocument6 pagesPolitica de CorreiopaulobrjNo ratings yet

- Pret A PorterDocument41 pagesPret A PorterLuciana Raposo33% (3)

- Atualização firmware RG1200 corrige problemas PPPoE e IPv6Document3 pagesAtualização firmware RG1200 corrige problemas PPPoE e IPv6Josenilton CardealNo ratings yet

- Av 1Document5 pagesAv 1Diogernes Oliveira CarmoNo ratings yet

- Guia completo do Windows 10Document7 pagesGuia completo do Windows 10Yascara MendesNo ratings yet

- Install Asterisk 11Document3 pagesInstall Asterisk 11tecnologiaciaNo ratings yet

- Trabalho - VPNDocument58 pagesTrabalho - VPNPedro Correia100% (2)

- Tabela de Preços de Serviços de Infomatica - CB InfoDocument1 pageTabela de Preços de Serviços de Infomatica - CB InfoCleyton Barros100% (1)

- Fundamentos de Rede para Huawei Certified Network EngineerDocument35 pagesFundamentos de Rede para Huawei Certified Network EngineerAndreMesquitaNo ratings yet

- Skyhawk 3 5 hddDS1902 7 1711BR PT - BRDocument3 pagesSkyhawk 3 5 hddDS1902 7 1711BR PT - BReder munhozNo ratings yet

- Avaliação de Arquitetura de ComputadoresDocument1 pageAvaliação de Arquitetura de ComputadoresPatrícia EstevamNo ratings yet

- Manual IntegradorDimep R18Document41 pagesManual IntegradorDimep R18Wesley FerreiraNo ratings yet

- Apostila Modulo10 PreparatoriocomptiaDocument100 pagesApostila Modulo10 PreparatoriocomptiaMalkavyNo ratings yet

- 2 - SimuladoDocument2 pages2 - SimuladoGabriella HoraNo ratings yet

- Tutorial Rede Ponto A Ponto No XPDocument13 pagesTutorial Rede Ponto A Ponto No XPcabecudy0% (1)

- 14 4 Router e SwtchingDocument3 pages14 4 Router e Swtchingreinaldo cunhaNo ratings yet

- Manual Instalação MAC OSDocument10 pagesManual Instalação MAC OScaio de abreuNo ratings yet

- Configuração Padrão Da OLT 300XX para Novos Clientes PROVEDORES. - Login Https - Parks - Com.br - Cadastrosuporte - HTMLDocument6 pagesConfiguração Padrão Da OLT 300XX para Novos Clientes PROVEDORES. - Login Https - Parks - Com.br - Cadastrosuporte - HTMLSamuel JesusNo ratings yet

- Utilitários Unix - Wikipédia, A Enciclopédia LivreDocument3 pagesUtilitários Unix - Wikipédia, A Enciclopédia LivreMuryllo Siqueyros Lupus SanteNo ratings yet

- Porta Paralela (SPP)Document12 pagesPorta Paralela (SPP)Marilainny Martins da SilvaNo ratings yet

- Fundamentos de Redes: Protocolos da Camada de AplicaçãoDocument16 pagesFundamentos de Redes: Protocolos da Camada de AplicaçãoThaís RodriguesNo ratings yet

- Nada de Sync Ou BleachbitDocument27 pagesNada de Sync Ou BleachbitAfonso LucioNo ratings yet

- Configuração de redirecionamento de portas, modo bridge e IP fixo em terminais virtuaisDocument36 pagesConfiguração de redirecionamento de portas, modo bridge e IP fixo em terminais virtuaisHávila Correia100% (1)

- Principais comandos do CMDDocument16 pagesPrincipais comandos do CMDTFG News MusicsNo ratings yet

- Infra Magazine - Edição 01 - KaizukyDocument72 pagesInfra Magazine - Edição 01 - KaizukyEpitacio FonsecaNo ratings yet

- Sitrad Inbox ManualDocument22 pagesSitrad Inbox ManualGilson ChiozziNo ratings yet

- IACOM Introducao 2019 2 PDFDocument238 pagesIACOM Introducao 2019 2 PDFLeandro Costa Sobrinho MutucNo ratings yet

- 001 - IfBA - Redes de Computadores II - Introdução - Redes Locais - V07-02Document198 pages001 - IfBA - Redes de Computadores II - Introdução - Redes Locais - V07-02Douglas DóreaNo ratings yet

- Manual Do Usuário KZ Prog: (CPC-FR) Função Gravar FlashDocument7 pagesManual Do Usuário KZ Prog: (CPC-FR) Função Gravar FlashRoneiNo ratings yet

- Repetidor Access Point Wi Fi N - 300 Mbps WN9255Document7 pagesRepetidor Access Point Wi Fi N - 300 Mbps WN9255Gledson MarquesNo ratings yet

- Manual Ultra SystemDocument54 pagesManual Ultra SystemRafaelNo ratings yet

- Criar versões virtualizadas de programas com o CameyoDocument2 pagesCriar versões virtualizadas de programas com o CameyoHerik CostagomesNo ratings yet