Professional Documents

Culture Documents

The Altera Max 7000 Family of CPLDS: 1. Logic Array Blocks (Labs) 2. Macrocell Arrays Prefabricated Arrays of Higher

Uploaded by

Mohammad SalmanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

The Altera Max 7000 Family of CPLDS: 1. Logic Array Blocks (Labs) 2. Macrocell Arrays Prefabricated Arrays of Higher

Uploaded by

Mohammad SalmanCopyright:

Available Formats

The Altera MAX 7000 Family of CPLDs

The MAX 7000 architecture consists of the following elements: 1. Logic Array Blocks (LABs) 2. Macrocell Arrays Prefabricated arrays of higherlevel logic gates, flip flops, registers, and other ALU components to perform certain functions. They are manufactured on wafers which are normally called slices. 3. Expander product terms 4. Programmable Interconnect Array (PIA) 5. I/O control blocks. Figure 11.8 shows the basic architecture of Alteras MAX 7000 family of CPLDs As shown, it contains an array of blocks referred to as Logic Array Blocks (LABs), a Programmable Interconnect Array (PIA) that contains interconnect wires, and I/O control blocks. Each LAB contains 16 macrocells and the PIA can connect any LAB input or output to any other LAB. It also includes four dedicated inputs that can be used as general inputs or a high speed, global control signals (clock, clear), and two output enable signals.

You might also like

- Altera Max and 7000Document23 pagesAltera Max and 7000Rathish RtsNo ratings yet

- Spartan and Spartan-XL FPGA Families Data Sheet: Product SpecificationDocument83 pagesSpartan and Spartan-XL FPGA Families Data Sheet: Product SpecificationAkash ShejuleNo ratings yet

- Actel Device ArchitectureDocument8 pagesActel Device ArchitectureUday KumarNo ratings yet

- The Xilinx VirtexDocument9 pagesThe Xilinx VirtexShreyas MaheshNo ratings yet

- m10 HandbookDocument593 pagesm10 HandbookHChNo ratings yet

- Altera Epf8282alc84 4Document62 pagesAltera Epf8282alc84 4lim hyNo ratings yet

- EPM3064Document43 pagesEPM3064Duy LeNo ratings yet

- Max 5000 PDFDocument8 pagesMax 5000 PDFMahesh Kumar GubbalaNo ratings yet

- FPGADocument20 pagesFPGANanda Ganesh Kumar KingNo ratings yet

- Xilinx xc4000 & Altera'S Flex 8000/10000 FPGADocument17 pagesXilinx xc4000 & Altera'S Flex 8000/10000 FPGAkumarkankipati19No ratings yet

- PLD Architectures and TestingDocument37 pagesPLD Architectures and TestingParesh SawantNo ratings yet

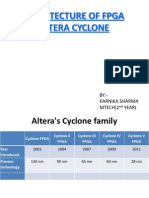

- Architecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)Document29 pagesArchitecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)karnika143100% (1)

- Altera FLEX 8000 Block Diagram (Review) Altera FLEX 10K Block Diagram (Review)Document4 pagesAltera FLEX 8000 Block Diagram (Review) Altera FLEX 10K Block Diagram (Review)Rohith RajNo ratings yet

- Examples of FPLD Families: Actel ACT, Xilinx LCA, Altera MAX 5000 & 7000Document9 pagesExamples of FPLD Families: Actel ACT, Xilinx LCA, Altera MAX 5000 & 7000karuppasamynagarajNo ratings yet

- Antifuse-Based Fpgas: Actel & QuicklogicDocument38 pagesAntifuse-Based Fpgas: Actel & QuicklogicSaurabh KukretiNo ratings yet

- Spartan II FPGADocument18 pagesSpartan II FPGAA B ShindeNo ratings yet

- XC9500XL High-Performance CPLD Family Data Sheet: Preliminary Product SpecificationDocument17 pagesXC9500XL High-Performance CPLD Family Data Sheet: Preliminary Product SpecificationArunkumar PatilNo ratings yet

- Features: ClassicDocument50 pagesFeatures: ClassicSamuel MarquezNo ratings yet

- Basic FPGA Architectures: Altera XilinxDocument8 pagesBasic FPGA Architectures: Altera XilinxkvinothscetNo ratings yet

- Altera ClassicDocument42 pagesAltera ClassicYeshmitha AnandNo ratings yet

- Xilinx XC4000Document24 pagesXilinx XC4000jeevitha100% (3)

- PLC Reviewer PDFDocument6 pagesPLC Reviewer PDFDhafnylynn MacasaetNo ratings yet

- Unit Ii: CPLD & Fpga Architecture & ApplicationsDocument18 pagesUnit Ii: CPLD & Fpga Architecture & ApplicationsGoutham DevisettyNo ratings yet

- Unit Ii: CPLD & Fpga Architecture & ApplicationsDocument20 pagesUnit Ii: CPLD & Fpga Architecture & ApplicationsNarasimha Murthy Yayavaram100% (1)

- Products 4936 MB 650 ML BrochureDocument2 pagesProducts 4936 MB 650 ML BrochureImran ShaukatNo ratings yet

- ch-2 Petruzella PDFDocument26 pagesch-2 Petruzella PDFozzaapriodede100% (2)

- M7000a (Epm7256ae)Document64 pagesM7000a (Epm7256ae)marcelgrandoNo ratings yet

- Avr Risc MicrocontrollerDocument11 pagesAvr Risc MicrocontrollerAmy OliverNo ratings yet

- FPGA Basics and Nios II Processor Intro: Week 2 Dr. Kimberly E. Newman Hybrid Embedded SystemsDocument22 pagesFPGA Basics and Nios II Processor Intro: Week 2 Dr. Kimberly E. Newman Hybrid Embedded Systemskanthi_thotaNo ratings yet

- Illiav 4Document34 pagesIlliav 4Tania HamidNo ratings yet

- XC9500XL High-Performance CPLD Family Data Sheet: Product SpecificationDocument18 pagesXC9500XL High-Performance CPLD Family Data Sheet: Product SpecificationonafetsNo ratings yet

- Core8051 DsDocument41 pagesCore8051 DsMinh Trí KnightNo ratings yet

- Introduction To Field Programmable Gate ArraysDocument44 pagesIntroduction To Field Programmable Gate ArraysBilal ShahidNo ratings yet

- FPGA TechnologyDocument26 pagesFPGA TechnologyvinaypantraNo ratings yet

- Manual WincuplDocument43 pagesManual WincuplRaul Alberto Lizarraga CuevasNo ratings yet

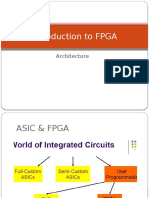

- Introduction To FPGA: ArchitectureDocument17 pagesIntroduction To FPGA: ArchitectureMuhammad AliNo ratings yet

- Mp3-8-Bit Microprocessor Architecture and OperationDocument17 pagesMp3-8-Bit Microprocessor Architecture and OperationserjaniNo ratings yet

- FPGA Arquitectura BasicaDocument7 pagesFPGA Arquitectura BasicaJesus LeyvaNo ratings yet

- I F P G A (Fpga) : Ntroduction To Ield Rogrammable ATE Rrays SDocument44 pagesI F P G A (Fpga) : Ntroduction To Ield Rogrammable ATE Rrays SHat HackersNo ratings yet

- CPLD and FpgaDocument28 pagesCPLD and FpgaUday KumarNo ratings yet

- Introduction To FPGA: ArchitectureDocument18 pagesIntroduction To FPGA: ArchitectureMuhammad AnasNo ratings yet

- BASCOM - Programming of Microcontrollers With EaseDocument236 pagesBASCOM - Programming of Microcontrollers With EasesaledjordjevicNo ratings yet

- Asics: I Will Miss You AlwaysDocument12 pagesAsics: I Will Miss You AlwaysSharif JamaliNo ratings yet

- XC9500 In-System Programmable CPLD Family: Product SpecificationDocument16 pagesXC9500 In-System Programmable CPLD Family: Product SpecificationMohamed MohNo ratings yet

- 02 - CH2. Introduction To PLC ArchetictureDocument43 pages02 - CH2. Introduction To PLC ArchetictureAhmed BashnainiNo ratings yet

- Intel 8051: From Wikipedia, The Free EncyclopediaDocument6 pagesIntel 8051: From Wikipedia, The Free Encyclopediasreekanth294No ratings yet

- Lec 2Document26 pagesLec 2sk2417No ratings yet

- AB CLX Standard 4 Day Module1 5CDocument58 pagesAB CLX Standard 4 Day Module1 5CHassan RashadNo ratings yet

- Field-Programmable Gate ArraysDocument14 pagesField-Programmable Gate Arraysநட்ராஜ் நாதன்No ratings yet

- Ds 099Document272 pagesDs 099Jit JagNo ratings yet

- PC Worx 6 OverviewDocument91 pagesPC Worx 6 OverviewĐỗ Thiện Phúc VinhNo ratings yet

- Microprocessor & Its ApplicationsDocument15 pagesMicroprocessor & Its ApplicationsSwamy Venkata UdayagiriNo ratings yet

- I F P G A (Fpga) : Ntroduction To Ield Rogrammable ATE Rrays SDocument13 pagesI F P G A (Fpga) : Ntroduction To Ield Rogrammable ATE Rrays Svidhya dsNo ratings yet

- Full Introduction of QuickLogic EclipsePlus FPGA FamilyDocument11 pagesFull Introduction of QuickLogic EclipsePlus FPGA FamilyjackNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- PLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsFrom EverandPLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsRating: 5 out of 5 stars5/5 (1)

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Shaadi Ke Baad Pehli RaatDocument2 pagesShaadi Ke Baad Pehli RaatMohammad Adil100% (3)

- ControlDocument4 pagesControlMohammad SalmanNo ratings yet

- Website Design Quote TemplateDocument1 pageWebsite Design Quote TemplateMohammad SalmanNo ratings yet

- 1-MS-Framework Introduction PDFDocument5 pages1-MS-Framework Introduction PDFMohammad SalmanNo ratings yet

- Thesis Format For MTECH - NIT 2014-15Document9 pagesThesis Format For MTECH - NIT 2014-15Mohammad SalmanNo ratings yet

- Currency Converter Using C#Document6 pagesCurrency Converter Using C#Mohammad SalmanNo ratings yet

- C1 FeasibilityDocument27 pagesC1 FeasibilityMohammad SalmanNo ratings yet

- Contents SeperatorDocument12 pagesContents SeperatorMohammad SalmanNo ratings yet

- Acid RainDocument10 pagesAcid RainMohammad SalmanNo ratings yet

- Unit 2 A) Techniques of Test Conduct and RapportDocument9 pagesUnit 2 A) Techniques of Test Conduct and RapportMohammad SalmanNo ratings yet

- FilteringDocument41 pagesFilteringAnil RayalaNo ratings yet

- Design of Novel Control Scheme For Four-Switch Three Phase Inverter Fed Permanent Magnet Brushless DC Motor DriveDocument6 pagesDesign of Novel Control Scheme For Four-Switch Three Phase Inverter Fed Permanent Magnet Brushless DC Motor DriveMohammad SalmanNo ratings yet

- Opamp IntegratorDocument6 pagesOpamp IntegratorMohammad SalmanNo ratings yet

- Feasibility StudyDocument2 pagesFeasibility StudyMohammad SalmanNo ratings yet

- Dice Game Controller Using SM ChartDocument43 pagesDice Game Controller Using SM ChartanjalisweNo ratings yet

- IEEE 802.11 Technical TutorialDocument18 pagesIEEE 802.11 Technical TutoriallamdxproNo ratings yet

- Edited PRCTDocument9 pagesEdited PRCTMohammad SalmanNo ratings yet

- Flynns ClassificationDocument2 pagesFlynns ClassificationMohammad SalmanNo ratings yet

- Internal RamDocument1 pageInternal RamMohammad SalmanNo ratings yet

- 68HC11Document5 pages68HC11Mohammad SalmanNo ratings yet

- MetastabilityDocument2 pagesMetastabilityMohammad SalmanNo ratings yet

- Finite State MachineDocument11 pagesFinite State MachineMohammad SalmanNo ratings yet

- Embedded Syllabus 2013Document23 pagesEmbedded Syllabus 2013Mohammad SalmanNo ratings yet

- Chapter 01 ACADocument5 pagesChapter 01 ACAMohammad SalmanNo ratings yet

- RISCvs CISCDocument3 pagesRISCvs CISCMohammad SalmanNo ratings yet

- Harshal RadarDocument22 pagesHarshal RadarMohammad SalmanNo ratings yet

- SSCDocument1 pageSSCMohammad SalmanNo ratings yet