Professional Documents

Culture Documents

EC6411 Circuit & Devices Lab Manual

Uploaded by

KALAIMATHICopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EC6411 Circuit & Devices Lab Manual

Uploaded by

KALAIMATHICopyright:

Available Formats

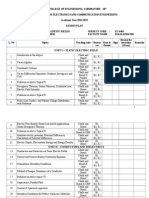

EC 6211

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUITS AND DEVICES LABORATORY

1. Characteristics of PN Junction Diode

2. Zener diode Characteristics & Regulator using Zener diode

3. Common Emitter input-output Characteristics

4. Common Base input-output Characteristics

5. FET Characteristics

6. SCR Characteristics

7. Clipper and Clamper & FWR

8. Verifications of Thevinin & Norton theorem

9. Verifications of KVL & KCL

10. Verifications of Super Position Theorem

11. verifications of maximum power transfer & reciprocity theorem

12. Determination of Resonance Frequency of Series & Parallel RLC Circuits

13. Transient analysis of RL and RC circuits

Content beyond the syllabus

14. Half wave rectifier

15.Bridge wave rectifier

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

FORWARD BIAS:

REVERSE BIAS:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

CHARACTERISTICS OF PN DIODE

Date:

AIM:

To study the PN junction diode characteristics under Forward & Reverse bias conditions.

APPARATUS REQUIRED:

S.No. Name of the Component

1

RPS

Range

Quantity Required

(0-30)V

(030)mA

(0100)A

(010)V

(01)V

Ammeter

Voltmeter

Resistor

Diode

1K , 10K

IN4007

Each 1

1

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

TABULAR COLUMN:

FORWARD BIAS:

S.No.

REVERSE BIAS:

VOLTAGE

CURRENT

(In Volts)

(In mA)

S..No.

VOLTAGE

CURRENT

(In Volts)

(In A)

MODEL GRAPH

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

PROCEDURE:

FORWARD BIAS:

1.

2.

3.

4.

Connect the circuit as per the diagram.

Vary the applied voltage V in steps of 0.1V.

Note down the corresponding Ammeter readings I.

Plot a graph between V & I

OBSERVATIONS

1. Find the d.c (static) resistance = V/I.

2. Find the a.c (dynamic) resistance r = V / I (r = V/ I) =

V2 V1

.

I 2 I1

3. Find the forward voltage drop = [Hint: it is equal to 0.7 for Si and 0.3 for Ge]

REVERSE BIAS:

1. Connect the circuit as per the diagram.

2. Vary the applied voltage V in steps of 1.0V.

3. Note down the corresponding Ammeter readings I.

4. Plot a graph between V & I

5. Find the dynamic resistance r = V / I.

Specification for 1N4001: Silicon Diode

Peak Inverse Voltage: 50V

Idc = 1A.

Maximum forward voltage drop at 1 Amp is 1.1 volts

The maximum reverse current @50 volts is 5 A

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Forward and Reverse bias characteristics of the PN junction diode was studied and

Dynamic Resistance = --------------------Static Resistance = -------------------------Cut in Voltage = ----------------------------

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

VIVA QESTIONS:1. Define depletion region of a diode?

2. What is meant by transition & space charge capacitance of a diode?

3. Is the V-I relationship of a diode Linear or Exponential?

4. Define cut-in voltage of a diode and specify the values for Si and Ge diodes?

5. What are the applications of a p-n diode?

6. Draw the ideal characteristics of P-N junction diode?

7. What is the diode equation?

8. What is PIV?

9. What is the break down voltage?

10. What is the effect of temperature on PN junction diodes?

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM (ZENER DIODE)

FORWARD BIAS:

REVERSE BIAS:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

CHARACTERISTICS OF ZENER DIODE

Date:

AIM:

To study the Zener diode characteristics under Forward & Reverse bias conditions.

APPARATUS REQUIRED:

S.No. Name of the Component

Range

Quantity Required

(0-30)V

RPS

Ammeter

(030) mA

Voltmeter

(030)V

Zener diode

FZ5.1

Resistor

1K

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

MODEL GRAPH

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

PROCEDURE:

FORWARD BIAS:

1. Connect the circuit as per the circuit diagram.

2. Vary the power supply in such a way that the readings are taken in steps of 0.1V in the

voltmeter till the needle of power supply shows 30V.

3. Note down the corresponding ammeter readings.

4. Plot the graph :V (vs) I.

5. Find the dynamic resistance r = V / I.

REVERSE BIAS:

1. Connect the circuit as per the diagram.

2. Vary the power supply in such a way that the readings are taken in steps of 0.1V in the

voltmeter till the needle of power supply shows 30V.

3. Note down the corresponding Ammeter readings I.

4. Plot a graph between V & I

5. Find the dynamic resistance r = V / I.

6. Find the reverse voltage Vr at Iz=20 mA.

RESULT:

Forward and Reverse bias characteristics of the Zener diode was studied and

Forward bias dynamic resistance = --------------------Zener breakdown voltage= -----------------------------

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

VIVAQUESTIONS:1. What type of temperature Coefficient does the zener diode have?

2. If the impurity concentration is increased, how the depletion width effected?

3. Does the dynamic impendence of a zener diode vary?

4. Explain briefly about avalanche and zener breakdowns?

5. Draw the zener equivalent circuit?

6. Differentiate between line regulation & load regulation?

7. In which region zener diode can be used as a regulator?

8. How the breakdown voltage of a particular diode can be controlled?

9. What type of temperature coefficient does the Avalanche breakdown has?

10. By what type of charge carriers the current flows in zener and avalanche breakdown

diodes?

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

TABULAR COLUMN:

Input characteristics: VCE constant

VCE =

VBE

(Volts)

IB

( A)

VCE =

VBE

(Volts)

IB

( A)

VCE =

VBE

(Volts)

IB

( A)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

CHARACTERISTICS OF CE CONFIGURATION OF BJT

Date:

AIM:

To plot the transistor characteristic of common-emitter configuration and to find the hparameters for the same.

EQUIPMENT REQUIRED:

S.No Name of the component

Range

Quantity

Power supply

(0-30)V

Ammeter

(0-10)mA,

Each 1

(0-1)mA

3

Voltmeter

(0-30)V,(0-2)V

Each 1

PROCEDURE:

i. Input characteristic:

1. Rig up the circuit as per the circuit diagram.

2. Set VCE = 5V (say), vary VBE insteps of 0.1V till the power supply VBB shows

20V and note down the corresponding IB. Repeat the above procedure for

10V, 15V etc.,

3. Plot the graph: VBE vs IB for a constant VCE.

4. Find the h-parameters: a. hrc : reverse voltage gain

b. hfc: input impedance

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

MODEL GRAPH:

Input Characteristics

TABULATION:

Output characteristics: IB constant

IB =

VCE

(Volts)

IC

(mA)

IB =

VCE

(Volts)

IC

(mA)

IB =

VCE

(Volts)

IC

(mA)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

ii. Output characteristic:

1. Rig up the circuit as per the circuit diagram.

2. Set IB = 20 A (say), vary VCE insteps of 1V and note down the corresponding

IC. Repeat the above procedure for 80 A, 200 A, 600 A etc.,

3. Plot the graph: VCE Vs IC for a constant IB.

4. Find the h-parameters: a. hoc : output admittance

b. hfc: forward current gain

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

MODEL GRAPH:

Output Characteristics

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

Result:

Thus the input and output characteristics of BJT under CE configuration are obtained.

Parameters

Practical readings

hfc

hic

hrc

hoc

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

VIVA QUESTIONS:

1.

What is the range of

for the transistor?

2.

What are the input and output impedances of CE configuration?

3.

Identify various regions in the output characteristics?

4.

what is the relation between

5.

Define current gain in CE configuration?

6.

Why CE configuration is preferred for amplification?

7.

What is the phase relation between input and output?

8.

Draw diagram of CE configuration for PNP transistor?

and

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

TABULAR COLUMN:

Input characteristics: VCB constant

VCB =

VEB

(Volts)

IE

(mA)

VCB =

VEB

(Volts)

IE

(mA)

VCB =

VEB

(Volts)

IE

(mA)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

CHARACTERISTICS OF CB CONFIGURATION

Date:

AIM:

To plot the transistor characteristic of common-base configuration and to find the hparameters for the same.

APPARATUS REQUIRED:

S.No

Name of the component

Range

Quantity

Power supply

(0-30) V

Ammeter

(0-20)mA,

Voltmeter

(0-20)V

PROCEDURE:

i. Input characteristic:

1. Rig up the circuit as per the circuit diagram.

2. Set VCB = 5V (say), vary VEB in a regular steps 0.1V till the power supply V EE

shows 20V and note down the corresponding IE. Repeat the above procedure

for 10V, 15V etc.,

3. Plot the graph: VEB Vs IE for a constant VCB.

4. Find the h-parameters: a. hrb : reverse voltage gain

b. hfb: input impedance

ii. Output characteristic:

5. Rig up the circuit as per the circuit diagram.

6. Set IE = 1mA (say), vary VCB insteps of 1V and note down the corresponding

IC. Repeat the above procedure for 3mA, 6mA, 10mA etc.,

7. Plot the graph: VCB Vs IC for a constant IE.

8. Find the h-parameters: a. hob : output admittance

b. hfb: forward current gain

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

MODEL GRAPH:

Input characteristics

Output characteristics: IE constant

IE =

VCB

(Volts)

IC

(mA)

IE =

VCB

(Volts)

IC

(mA)

IE =

VCB

(Volts)

IC

(mA)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

MODEL GRAPH:

Performance

Observation

Viva

Total

RESULT:

Thus the input and output characteristics of BJT under CB configuration are obtained.

Parameters

Practical readings

hfb

hib

hrb

hob

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

PIN DIAGRAM:

BOTTOM VIEW OF BFW10:

SPECIFICATION:

Voltage : 30V, IDSS > 8mA.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

CHARACTERISTICS OF JUNCTION FIELD EFFECT TRANSISTOR

Date:

AIM:

To Plot the characteristics of given FET & determine r d, gm, , IDSS,VP.

APPARATUS REQUIRED:

S.No.

Name of the component

Range

Quantity

RPS

(0-30)V

Ammeter

(030)mA

Voltmeter

(030)V

FET

BFW10

4

5

Resistor

Bread Board

1

One Each

1k ,68K

PROCEDURE:

DRAIN CHARACTERISTICS:

1. Connect the circuit as per the circuit diagram.

2. Set the gate voltage VGS = 0V.

3. Vary VDS in steps of 1 V & note down the corresponding I D.

4. Repeat the same procedure for VGS = -1V.

5. Plot the graph VDS Vs ID for constant VGS.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

MODEL GRAPH:

DRAIN CHARACTERISTICS:

TRANSFER CHARACTERISTICS:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

OBSERVATIONS

1. d.c (static) drain resistance, rD = VDS/ID.

2. a.c (dynamic) drain resistance, rd = VDS/ ID.

3. Open source impedance, YOS = 1/ rd.

TRANSFER CHARACTERISTICS:

1. Connect the circuit as per the circuit diagram.

2. Set the drain voltage VDS = 5 V.

3. Vary the gate voltage VGS in steps of 1V & note down the corresponding I D.

4. Repeat the same procedure for VDS = 10V.

5. Plot the graph VGS Vs ID for constant VDS.

FET PARAMETER CALCULATION:

Drain Resistancd rd =

VDS

VGS

ID

Transconductance gm =

ID

VDS

VGS

Amplification factor =rd . gm

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

TABULAR COLUMN:

DRAIN CHARACTERISTICS:

VGS = 0V

VDS (V)

ID(mA)

VGS = -1V

VDS (V)

ID(mA)

TRANSFER CHARACTERISTICS:

VDS =5volts

VGS (V)

ID(mA)

VDS = 10volts

VGS (V)

ID(mA)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Thus the Drain & Transfer characteristics of given FET is Plotted.

Rd =

gm =

=

IDSS =

Pinch off voltage VP =

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

VIVA QUESTIONS:

1. What are the advantages of FET?

2. Different between FET and BJT?

3. Explain different regions of V-I characteristics of FET?

4. What are the applications of FET?

5. What are the types of FET?

6. Draw the symbol of FET.

7. What are the disadvantages of FET?

8. What are the parameters of FET?

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

SCR CIRCUIT DIAGRAM:

MODEL GRAPH:

IA

(mA)

IL

Negative resistance region

IH

VBO

VAK (VOLTS)

TABULAR COLUMN:

VAK (volts)

IA (mA)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

CHARACTERISTICS OF SCR

Date:

AIM:

To find the latching and holding current for a given SCR.

APPARATUS REQUIRED:

S.No Name of the component

Range

Quantity

(0-30)V

1.

Power supply

2.

SCR

3.

Resistor

1K

4.

Ammeter

(0-30)mA

5.

Voltmeter

(0-30)V

6.

Bread Board

PROCEDURE FOR SCR:

1. Rig up the circuit as per the circuit diagram.

2. Set gate current IG equal to firing current, vary anode to cathode voltage V AK in steps

of 0.5V and note down the corresponding anode current IA.

3. VBO is the point where the SCR voltage (VAK) suddenly drops and sudden increase

anode current IA.

4. Note down the current at that point called latching current.

5. Increase the VAK insteps of 1V till its maximum.

6. Open the gate terminal and decrease the anode voltage VAK.

7. Holding current is the current below, which the deflection in both voltmeter (V AK)

and an ammeter (IA) suddenly reduces to zero.

8. Holding current is the minimum current that a SCR can maintain its condition.

Holding current always less than latching current.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Thus the characteristics of SCR verified and graph were drawn.

Parameters

Practical readings

Peak voltage

Valley voltage

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Clipper Circuit Diagram

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

CLIPPER AND CLAMPER

Date:

AIM:

To design and construct the clipper, clamper, integrator, differentiator circuits and draw

the waveforms.

APPARATUS REQUIRED:

S.No

APPARATUS REQUIRED

Resistors

RANGE

Diode

QUANTITY

1K

1N4007

Power supply

0-30V

Capacitors

0.1 F

CRO

(0 -30)MHz

Bread board

CRO Probes

8.

Signal generator

(0-2)MHz

9.

Bread Board

Procedure:

1.Ring up the circuit as per the circuit diagram.

2. Set input signal voltage (say 5V, 1 k Hz) using signal generator.

3. Observe the output waveform using CRO (DC mode).

4. Sketch the observed waveform on the graph sheet.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Clamper circuit diagram

Tabulation:

Amplitude (volts)

Time(sec)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Thus Clipper and Clamper circuits were constructed and their output was obtained.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Circuit diagram:

Without Filter:-

With Filter:-

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

FULL WAVE RECTIFIER

Date:

Aim:

To construct a full wave rectifier and to measure DC voltage under load and to calculate

the ripple factor.

Apparatus Required:

S.No.

Name of the Component / Apparatus

1

2

Transformer

Diode

Resistor

4

5

6

7

Capacitor

CRO

Bread Board

Connecting wires

Specification / Range Quantity

(9 0 9 ) V

1N4007

2

2

1k

47F

(0-30)MHz

-

1

1

1

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Model Graph:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Procedure:

Connections are given as per the circuit diagram without filter.

Note the amplitude and time period of the input signal at the secondary winding of the

transformer and rectified output.

Repeat the same steps with the filter and measure Vdc.

Calculate the ripple factor.

Draw the graph for voltage versus time.

as no such means is provided.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Tabulation:

Input Signal

S.No

Output Signal

Condition

Amplitude

Without Filter

With Filter

Time

Amplitude

Time

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Thus the full wave rectifier was constructed and its input and output waveforms are

drawn.

Theoretical

Practical

DC Voltage

Ripple Factor

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

VIVA QUESTIONS:1. Define regulation of the full wave rectifier?

2. Define peak inverse voltage (PIV)? And write its value for Full-wave rectifier?

3. If one of the diode is changed in its polarities what wave form would you get?

4. Does the process of rectification alter the frequency of the waveform?

5. What is ripple factor of the Full-wave rectifier?

6. What is the necessity of the transformer in the rectifier circuit?

7. What are the applications of a rectifier?

8. What is ment by ripple and define Ripple factor?

9. Explain how capacitor helps to improve the ripple factor?

10. Can a rectifier made in INDIA (V=230v, f=50Hz) be used in USA (V=110v, f=60Hz)?

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Circuit diagram:

Thevenins Voltage Experiment set up:

Thevenins Resistance Experiment set up:

Thevenins circuit:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Ex.No:

2015

VERIFICATION OF THEVENIN AND NORTON THEOREMS

Date:

AIM:

To verify the Thevenin and Norton theorem for the given circuit diagram

APPARATUS REQUIRED:

S.No

Name of the component

Range

Quantity

Voltmeter

(0-10)V

Ammeter

(0-10)V

Power supply

(0 30)V

Resister

1K

500,50

Each 1

PROCEDURE:

THEVENIN THEOREM

1. Connect the circuit as per the circuit diagram.

2. Measure the voltage across the load using voltmeter.

To find Thevenins voltage:

1. Connect the circuit as per the circuit diagram.

2. Remove the load resistance and measure the open circuited voltage across the output

terminal using voltmeter (Vth).

To find thevenins resistance:

1. Connect the circuit as per the circuit diagram.

2. Replace the supply by its internal resistance and open circuit the load.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

3. Using multimeter in resistance mode measure the resistance across the output

terminal (Rth).

TABULAR COLUMN: THEVENIN THEOREM

Voltage (volts)

Open circuit

Thevenins

Voltage (fig 2d)

voltage (volts)

resistance ( )

(volts)

Circuit Diagram:

Nortons Voltage Experiment Set up:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Thevenins circuit:

1. Connect the power supply (Vth) & resistance (Rth) in series.

2. Connect the load resistance (1K ).

3. Switch on the power supply & measure the voltage drop across load resistance using

voltmeter.

4. Voltage measured should be equal to the voltage measured.

NORTON THEOREM

1. Connect the circuit as per the circuit diagram.

2. Measure the voltage across the load using voltmeter.

To find Nortons voltage:

1. Connect the circuit as per the circuit diagram.

2. Short-circuit the load resistance and measure the short-circuited current using

ammeter (INO).

To find Nortons resistance:

1. Connect the circuit as per the circuit diagram.

2. Replace the supply by its internal resistance and open circuit the load.

3. Using multimeter in resistance mode measure the resistance across the output

terminal (Rth).

To find Nortons circuit:

1. Connect the current source (INOR) and Rth in parallel.

2. Connect the load resistance (1K ).

3. Switch on the current source & measure the voltage drop across load resistance using

voltmeter.

4. Voltage measured should be equal to the voltage measured.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Nortons Resistance Experiment Set up:

Nortons Circuit:

TABULAR COLUMN:

I1(mA)

I2(mA)

I1 + I2 (mA)

I (mA)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Thus the Thevenin and Notron theorem was verified.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

Circuit diagram for verification of KCL

Fig.1a Circuit diagram for verification of KCL

Circuit diagram for verification of KVL

Fig.1b Circuit diagram for verification of KVL

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

VERIFICATION OF KIRCHOFFS CURRENT AND VOLTAGE LAWS

Ex.No:

Date:

AIM:

To verify Kirchhoffs Current law (KCL) and Kirchhoffs Voltage law (KVL).

APPARATUS REQUIRED:

S.No

Name of the component

Range

Quantity

Required

Resistor

270, 330, 3560

1 each

Ammeter

(0-10)mA

Regulated power supply(RPS)

(0-30)V

Voltmeter

(0-30)V

Bread board

PROCEDURE (KCL):

1. Connect the circuit as shown in Fig (1).

2. Switch ON the Regulated Power Supply (RPS) and set the RPS to a particular value of

voltage say 5V.

3. Record the readings of three ammeters namely I 1,I2,I3 with proper sign by taking current

entering the node as positive and leaving the node as negative in the observation

Table(1).

4. Add I2 and I3 and verify whether the added value is equal to I1. (As per KCL, I1=I2+I3).

5. Increase the RPS settings in steps of 5V up to a maximum of 25V.

6. Repeat the steps 3 to 5 by incrementing the RPS settings in terms of 5V.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

TABULAR COLUMN (KCL)

SL.NO RPS VOLTAGE (Volts)

I1 (mA)

I2 (mA)

I3 (mA)

I1= I2+I3(mA)

1

2

3

4

5

TABULAR COLUMN (KVL)

SL.NO RPS Voltage (Volts)

V1(Volts) V2 (Volts)

V3

(Volts)

V=V1+ V2 + V3

(Volts)

1

2

3

4

5

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

PROCEDURE (KVL):

1. Connect the circuit as shown in Fig (2).

2. Switch ON the Regulated Power Supply (RPS) and set the RPS to a particular value of

voltage (V) say 5V.

3. Record the readings of two voltmeters namely V1, V2 and RPS Voltage in the observation

table (2).

4. Add V1 and V2 and verify whether the added value is equal to V. (as per KVL V =

V1+V2).

5. Increase the RPS settings in steps of 5V up to a maximum of 25V.

Repeat the steps 2 to 5 for each value of RPS setting.

Performance

Observation

Viva

Total

RESULT

Thus the verification of Kirchhoffs current law and Kirchhoffs voltage law is done.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

TABULAR COLUMN:

I1(m

A)

I2(m

A)

I1 + I2

(mA)

I

(mA

)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

VERIFICATION OF SUPERPOSITION THEOREM

Date:

AIM:

To verify the superposition theorem

APPARATUS REQUIRED:

S.No

Name of the component

Range

Quantity

Ammeter

(0-10)mA

Power supply

(0-30)V

Resister

10K, 50

3,1

Bread board

PROCEDURE:

1. Connect the circuit as per the circuit diagram [fig4a]

2. Switch on the DC power supplies (10V & 5V) and note down the corresponding

ammeter readings (say I A).

3. Replace the second power supply by its internal resistance [fig4b].

4. Switch on the power supply (10V) and note down the corresponding ammeter reading

(say I1).

5. Connect back the second power supply (5V) and replace the first power supply by its

internal resistance [fig4c].

6. Switch on the power supply (5V) and note down the corresponding ammeter reading

(say I2).

7. Verify the following condition:

I = I1 + I2

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Thus the superposition theorem was verified.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

MAXIMUM POWER TRANSFER CIRCUIT DIAGRAM:

TABULAR COLUMN:

S.No.

Resistance RL ()

Current IL (mA)

Power P=IL2 RL

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

VERIFICATION OF MAXIMUM POWER TRANSFER AND

RECIPROCITY THEOREM

Date:

AIM:

To verify the maximum power transfer theorem for the given circuit diagram

APPARATUS REQUIRED:

S.No

Name of the component

Range

Quantity

Signal generator

(0-1)MHz

Voltmeter

(0-10)V

Ammeter

(0-100)mA

PROCEDURE:

1. The circuit connections are given as per the circuit diagram.

2. Switch ON the power supply.

3. Initially set 5V as input voltage from RPS.

4. The ammeter reading is noted for various values of load resistance and the values are

tabulated.

5. The load resistance for the maximum power is obtained from the table

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Maximum Power Transfer Model Graph:

Reciprocity Theorem Circuit Diagram

Voltage & Current

Before interchanging

After interchanging

Voltage (Volts)

Current (mA)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Thus the maximum power transfer theorem and reciprocity theorem were verified.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

Series resonance

Calculation:

R = 600

L = 101.4mH

C = 0.01F

Tabulation:

S.No.

Frequency (KHz)

Output voltage (Volts) I = V / R (mA)

Ms B.KALAIMATHI AP/ECE

EC 6211

Ex.No:

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

FREQUENCY RESPONSES OF SERIES AND PARALLEL

Date:

RESONANCE CIRCUITS

AIM:

To design a RLC series and parallel resonance circuit and to obtain the frequency

response.

APPARATUS REQUIRED:

S.No

Name of the component

Range

Quantity

Signal generator

(0-1)MHz

Voltmeter

(0-10)V

Ammeter

(0-10)mA

Resistor

1K

Capacitor

1F

Inductor

1mH

Bread board

PROCEDURE (Series Resonance):

1. The circuit connections are given as per the circuit diagram.

2. Switch ON the power supply.

3. The input is given in the form of sin wave by function generator.

4. The amplitude of the response across the resistor is noted for various frequency ranges.

5. The current is calculated and tabulated

To measure the resonance frequency:

1. Plot the graph: Current Vs frequencies.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Model Graph :

Parallel Resonance:

Calculation:

R= 600

L = 101.4mH

C = 0.01F

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

1. Draw a horizontal line, which intersects the curve at

2015

1

times the maximum current

2

reading.

2. Lower intersected point and upper intersected point are respectively called lower cutoff frequency and upper cut-off frequency on frequency axis.

Bandwidth, BW = f2 f1

Selectivity = Bandwidth/f0 = (f2 f1)/ f0

PROCEDURE (Parallel Resonance):

1. Rig up the circuit as per the circuit diagram.

2. Set input voltage, VI = 5V using signal generator and vary the frequency from (0-1M)

Hz in a regular steps.

3. Note down the corresponding output voltage and current.

Z

4. Plot the graph: Normalized impedance

Vs frequencies

Z0

To measure the resonance frequency:

1. Plot the graph: Normalized impedance

Z

Vs frequencies

Z0

2. Draw a horizontal line, which intersects the curve at

1

times the maximum current

2

reading.

3. Lower intersected point and upper intersected point are respectively called lower cutoff frequency and upper cut-off frequency on frequency axis.

Quality factor:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Resistnace

C

R

=

=R

L

Reactance 0 L

Q0 =

MODEL GRAPH:

Tabulation:

S.No.

Frequency (KHz)

Output voltage (Volts) I = V / R (mA)

Bandwidth & selectivity:

In parallel resonance circuit, the specified points are the one at which normalized impedance

1

falls to

of its value at resonance.

2

Bandwidth, BW = f2 f1

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Selectivity = Bandwidth/f0 =(f2 f1)/ f0

Performance

Observation

Viva

Total

RESULT:

Thus the parallel and series RLC circuit was designed and the frequency response curves

were drawn.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

RC circuit diagram:

RL circuit diagram:

Ms B.KALAIMATHI AP/ECE

EC 6211

Ex.No:

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

TRANSIENT ANALYSIS OF RL AND RC CIRCUITS

Date:

AIM:

To design a RL and RC circuit and to obtain the Steady state response.

APPARATUS REQUIRED:

S.No

Name of the component

Range

Quantity

Power supply

(0-10)V

Voltmeter

(0-10)V

Ammeter

(0-10)mA

Resistor

12K

Capacitor

1000F

Inductor

1mH

Bread board

PROCEDURE (Series Resonance):

1. Connect the circuit as per the circuit diagram.

2. Switch over the contact to position 1.

3. Switch on the power supply and stopwatch simultaneously.

4. Take the ammeter and voltmeter reading in a regular time interval.

5. Switch over the contact to position 2 and simultaneously reverse the polarity of ammeter.

6. Note down the reading from the ammeter and voltmeter at regular time intervals.

7. Plot the graph: voltage vs time (charging and discharging)

Current vs time (charging and discharging)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

MODEL GRAPH:

Charging graph:

Tabulation: Charging

Voltage(volts)

Time( sec)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Discharging graph:

Tabulation: Discharging

Voltage(volts)

Time( sec)

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

Performance

Observation

Viva

Total

2015

RESULT:

Thus the RL & RC circuit was designed and the Steady state response curves were

drawn.

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

WITHOUT FILTER:

WITH FILTER:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

HALF WAVE RECTIFIER

Date:

Aim:

To construct a half wave rectifier and to measure DC voltage under load and to calculate

the ripple factor.

Apparatus Required:

S.No.

Name of the Component / Apparatus

1

2

Transformer

Diode

Resistor

4

5

6

7

Capacitor

CRO

Bread Board

Connecting wires

Specification / Range Quantity

(9 0 9 ) V

1N4007

2

1

1k

100F

(0-30)MHz

-

1

1

1

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Model Graph:

Tabulation:

Input Signal

S.No

Output Signal

Condition

Amplitude

Without Filter

With Filter

Frequency

Amplitude

Frequency

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Procedure:

Connections are given as per the circuit diagram without filter.

Note the amplitude and time period of the input signal at the secondary winding of the

transformer and rectified output.

Repeat the same steps with the filter and measure Vdc.

Calculate the ripple factor.

Draw the graph for voltage versus time.

as no such means is provided.

Performance

Observation

Viva

Total

RESULT:

Thus the half wave rectifier was constructed and its input and output waveforms are

drawn.

Theoretical

Practical

DC Voltage

Ripple Factor

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

2015

CIRCUITS AND DEVICES LABORATORY MANUAL

Viva Questions and answers:

1.

In

half-wave

rectifier,

the

load

current

flows

for

only

the

.. of the input signal.

2. A half-wave rectifier is equivalent to a circuit.

3. The output of a half-wave rectifier is suitable for running ........... motors.

4. The DC output polarity from a half-wave rectifier can be reversed by reversing the

.

5. In a half wave rectifier if a resistance equal to load resistance is connected in parallel with

the diode then the circuit will .

6. The efficiency and ripple factor of a half-wave rectifier is and

..

7. The main job of a voltage regulator is to provide a nearly . output voltage.

8. In a Zener diode voltage regulator, the diode regulates so long as it is kept in

.. bias condition.

9. In Zener diode regulator, the maximum load current which can be supplied to load resistor is

limited in between .. and .

10. The percentage voltage regulation of voltage supply providing 100 V unloaded and 95 V at

full load is

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

CIRCUIT DIAGRAM:

WITHOUT FILTER:

WITH FILTER:

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ex.No:

BRIDGE WAVE RECTIFIER

Date:

Aim:

To construct a bridge wave rectifier and to measure DC voltage under load and to

calculate the ripple factor.

Apparatus Required:

S.No.

Name of the Component / Apparatus

1

2

Transformer

Diode

Resistor

4

5

6

7

Capacitor

CRO

Bread Board

Connecting wires

Specification / Range Quantity

(9 0 9 ) V

1N4007

2

4

1k

100F

(0-30)MHz

-

1

1

1

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Model Graph:

Tabulation:

Input Signal

S.No

Output Signal

Condition

Amplitude

Without Filter

With Filter

Frequency

Amplitude

Frequency

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Procedure:

Connections are given as per the circuit diagram without filter.

Note the amplitude and time period of the input signal at the secondary winding of the

transformer and rectified output.

Repeat the same steps with the filter and measure Vdc.

Calculate the ripple factor.

Draw the graph for voltage versus time.

as no such means is provided.

Performance

Observation

Viva

Total

RESULT:

Thus the bridge wave rectifier was constructed and its input and output waveforms are

drawn.

Theoretical

Practical

DC Voltage

Ripple Factor

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

Ms B.KALAIMATHI AP/ECE

EC 6211

CIRCUITS AND DEVICES LABORATORY MANUAL

2015

VIVAQUESTIONS:1. What is the PIV of Bridge rectifier?

2. What is the efficiency of Bridge rectifier?

3. What are the advantages of Bridge rectifier?

4. What is the difference between the Bridge rectifier and fullwaverectifier?

5. What is the o/p frequency of Bridge Rectifier?

6. What is the disadvantage of Bridge Rectifier?

7. What is the maximum secondary voltage of a transformer?

8. What are the different types of the filters?

9. What is the difference between the Bridge rectifier and half wave Rectifier?

10. What is the maximum DC power delivered to the load?

Ms B.KALAIMATHI AP/ECE

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- EC3311-Electronic Devices and Circuits Lab - ManualDocument99 pagesEC3311-Electronic Devices and Circuits Lab - ManualJenifer niroshaNo ratings yet

- ITC 215: Data Structure and Algorithm Module ObjectivesDocument3 pagesITC 215: Data Structure and Algorithm Module Objectiveskarthikeyan50700HRNo ratings yet

- Crisis Management PlanDocument8 pagesCrisis Management PlanNfareeNo ratings yet

- Circuit & Devices Lab ManualDocument107 pagesCircuit & Devices Lab ManualKALAIMATHI100% (2)

- Signals-and-Systems - Basics & Formula HandbookDocument19 pagesSignals-and-Systems - Basics & Formula HandbookKALAIMATHI100% (15)

- Differential Amplifier Using BJTDocument11 pagesDifferential Amplifier Using BJTAssini HussainNo ratings yet

- ELECTRICAL CIRCUIT THEORY MCQs PDFDocument9 pagesELECTRICAL CIRCUIT THEORY MCQs PDFYashNo ratings yet

- Hospital Building Civil ProjectDocument128 pagesHospital Building Civil ProjectArun Ragu100% (6)

- Chapter 5pptDocument46 pagesChapter 5pptkalehiwotkoneNo ratings yet

- Lic Lab ManualDocument89 pagesLic Lab ManualKALAIMATHI100% (1)

- Astable Multivibrators Using 555 ICDocument6 pagesAstable Multivibrators Using 555 ICJaimin ShahNo ratings yet

- Experiment No.2: Colpitt OscillatorDocument3 pagesExperiment No.2: Colpitt OscillatorBhadresh Renuka50% (2)

- ADE Lab Manual - Analog Part PDFDocument21 pagesADE Lab Manual - Analog Part PDFJk RinkuNo ratings yet

- Network Analysis and Synthesis QBDocument11 pagesNetwork Analysis and Synthesis QBGowthamNo ratings yet

- BJTDocument6 pagesBJTengineerluvNo ratings yet

- Experiment 11: NPN BJT Common Emitter CharacteristicsDocument7 pagesExperiment 11: NPN BJT Common Emitter CharacteristicsMalikAlrahabiNo ratings yet

- EXP17 Class A Power AmplifierDocument3 pagesEXP17 Class A Power AmplifierMohammed Dyhia AliNo ratings yet

- Diode Clippers: 1. Positive Clipper and Negative ClipperDocument6 pagesDiode Clippers: 1. Positive Clipper and Negative ClipperBibek ThapaNo ratings yet

- UNIT 3-2marks-FET PDFDocument9 pagesUNIT 3-2marks-FET PDFpriyanka236No ratings yet

- Emf Two MarksDocument17 pagesEmf Two Marksnithyagovnd100% (2)

- Half Wave Rectification Experiment - 3: TheoryDocument10 pagesHalf Wave Rectification Experiment - 3: TheoryLakshayNo ratings yet

- Experiment 2 3-Phase MeasurementDocument10 pagesExperiment 2 3-Phase MeasurementSaraha AloNo ratings yet

- Analog Electronics Circuits (Semester V - EEE) : Important QuestionsDocument2 pagesAnalog Electronics Circuits (Semester V - EEE) : Important QuestionsHadush KingNo ratings yet

- Emitter FollowerDocument8 pagesEmitter FollowerjerlineprincyNo ratings yet

- Refresher Course: Experimental PhysicsDocument15 pagesRefresher Course: Experimental PhysicsNeelam KapoorNo ratings yet

- Oscillator PDFDocument4 pagesOscillator PDFJoshua DuffyNo ratings yet

- Experiment PE LABDocument5 pagesExperiment PE LABsureshfm1100% (1)

- Awp Unit Wise QuesDocument5 pagesAwp Unit Wise QuesNagireddy GujjulaNo ratings yet

- Generalized Method for Solving Clipper Circuit ProblemsDocument4 pagesGeneralized Method for Solving Clipper Circuit ProblemsAnshuman Vyas0% (2)

- Operational Amplifier GuideDocument56 pagesOperational Amplifier GuideVedang PavanjeNo ratings yet

- Transient of R.C. CircuitDocument9 pagesTransient of R.C. CircuitArinder SinghNo ratings yet

- Experiment Name-Study of Wein Bridge OscillatorDocument2 pagesExperiment Name-Study of Wein Bridge Oscillatormrana_56No ratings yet

- Op-Amp MCQDocument13 pagesOp-Amp MCQAbhisek Gautam BTNo ratings yet

- Single Tuned Amplifier: Experiment:5Document2 pagesSingle Tuned Amplifier: Experiment:5hari007kmrNo ratings yet

- Circuit Analysis -I Year ECE- Question BankDocument20 pagesCircuit Analysis -I Year ECE- Question BankPandyselvi Balasubramanian100% (1)

- Op-Amp Differentiator Circuit ExperimentDocument2 pagesOp-Amp Differentiator Circuit ExperimentBhadresh Renuka100% (1)

- Experiment - 05Document17 pagesExperiment - 05Sagar SharmaNo ratings yet

- Lab#2B: Half-Wave Rectifier Circuit Without and With FilterDocument5 pagesLab#2B: Half-Wave Rectifier Circuit Without and With FilterHemanth GedelaNo ratings yet

- Commutation SCRDocument4 pagesCommutation SCRAmit ParchakeNo ratings yet

- Experiment - 4 Half Wave Rectifier Pre - Lab QuestionsDocument8 pagesExperiment - 4 Half Wave Rectifier Pre - Lab Questionsgautam KrishnaNo ratings yet

- AE LAB - Experiment No.2-1Document4 pagesAE LAB - Experiment No.2-1Prajwal PatilNo ratings yet

- Lab # 11 Power Amplifier: Class-ADocument8 pagesLab # 11 Power Amplifier: Class-ARaja SaifNo ratings yet

- Experiment No. 6 Op-Amp As Comparator & Schmitt Trigger: Analog Circuits LAB ManualDocument14 pagesExperiment No. 6 Op-Amp As Comparator & Schmitt Trigger: Analog Circuits LAB ManualchaitanyaNo ratings yet

- Voltage Regulation of 3-Phase Alternator by ZPF and ASA MethodsDocument6 pagesVoltage Regulation of 3-Phase Alternator by ZPF and ASA Methods61EEPrabhat PalNo ratings yet

- Questions On The Operational AmplifierDocument12 pagesQuestions On The Operational Amplifierkibrom atsbha50% (2)

- Gate Question LICDocument46 pagesGate Question LICnaveeth11No ratings yet

- 15ecl48 VTU Raghudathesh RC Wein Bridge OscillatorsDocument7 pages15ecl48 VTU Raghudathesh RC Wein Bridge OscillatorsraghudatheshgpNo ratings yet

- Questions & Answers On Transistor Biasing and Thermal StabilizationDocument32 pagesQuestions & Answers On Transistor Biasing and Thermal Stabilizationkibrom atsbhaNo ratings yet

- Chapter 3: Ac Power AnalysisDocument40 pagesChapter 3: Ac Power AnalysisAtyia Javed100% (1)

- OP-AMP Lab - Summer & Subtractor CircuitsDocument4 pagesOP-AMP Lab - Summer & Subtractor CircuitsKidist kefelegnNo ratings yet

- 6.question Bank: Unit-I Part A QuestionsDocument10 pages6.question Bank: Unit-I Part A Questionsbashyam88No ratings yet

- Network Theory Question Bank PDFDocument14 pagesNetwork Theory Question Bank PDFmohammadmohisin134No ratings yet

- First Order Active Filters (LPF, HPF) : (A) Low Pass FilterDocument12 pagesFirst Order Active Filters (LPF, HPF) : (A) Low Pass FilterVRNo ratings yet

- Astable Multi Vibrator: Prior To The Lab SessionDocument5 pagesAstable Multi Vibrator: Prior To The Lab SessionRiya Saluja100% (1)

- MCQ-EC 304 Transmission Lines and WaveguidesDocument6 pagesMCQ-EC 304 Transmission Lines and WaveguidesSreejithNo ratings yet

- Ecet321l - E1 - Single Stage Ce AmplifierDocument9 pagesEcet321l - E1 - Single Stage Ce AmplifierKenneth DomingoNo ratings yet

- Aim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpDocument8 pagesAim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpAvinash Nandakumar100% (1)

- Speed Control of DC MotorDocument4 pagesSpeed Control of DC MotorjitbakNo ratings yet

- Electrical and Electronic MeasurementsDocument47 pagesElectrical and Electronic MeasurementsAkashGauravNo ratings yet

- Exp 11 Voltage Regulator Using IC 723Document5 pagesExp 11 Voltage Regulator Using IC 723Savio Pereira67% (3)

- EC Lab Manual (08.407)Document101 pagesEC Lab Manual (08.407)Assini HussainNo ratings yet

- Aero Lab Manual 2014-2015Document23 pagesAero Lab Manual 2014-2015Muthyala AkhilNo ratings yet

- ECAD2 Complete ManualDocument37 pagesECAD2 Complete ManualJeremy HensleyNo ratings yet

- ECCE4466: Power Electronics Student Lab Manual: Department of Electrical and Computer EngineeringDocument20 pagesECCE4466: Power Electronics Student Lab Manual: Department of Electrical and Computer Engineeringsenpai_mendozaNo ratings yet

- Emf Unit IIIDocument30 pagesEmf Unit IIIKALAIMATHINo ratings yet

- Signals and Systems (Ec2204) FormulaDocument9 pagesSignals and Systems (Ec2204) FormulaKALAIMATHI50% (2)

- Emf Unit IiDocument22 pagesEmf Unit IiKALAIMATHINo ratings yet

- Emf Unit IDocument42 pagesEmf Unit IKALAIMATHINo ratings yet

- EMF Lesson PlanDocument6 pagesEMF Lesson PlanKALAIMATHINo ratings yet

- Digital Lab ManualDocument87 pagesDigital Lab ManualKALAIMATHINo ratings yet

- EMF Lesson PlanDocument5 pagesEMF Lesson PlanKALAIMATHINo ratings yet

- EMF - 2 Mark & 16 MarksDocument26 pagesEMF - 2 Mark & 16 MarksKALAIMATHINo ratings yet

- Electronic System Design ManualDocument47 pagesElectronic System Design ManualKALAIMATHINo ratings yet

- EMF Lesson PlanDocument6 pagesEMF Lesson PlanKALAIMATHINo ratings yet

- Electronic Circuits - I: Lab ManualDocument85 pagesElectronic Circuits - I: Lab ManualKALAIMATHI80% (5)

- Lesson Plan - Signals & Systems 2012Document3 pagesLesson Plan - Signals & Systems 2012KALAIMATHINo ratings yet

- Diligence International Group Understands MexicoDocument2 pagesDiligence International Group Understands MexicoPR.comNo ratings yet

- EZSkin v3 User GuideDocument16 pagesEZSkin v3 User GuidePg1978No ratings yet

- Ln26r71bd Ln-s2652d Ln26r71b Ln32r71bd LN s3252d DiagramaDocument261 pagesLn26r71bd Ln-s2652d Ln26r71b Ln32r71bd LN s3252d DiagramaVictor Julio AlvarezNo ratings yet

- Citrix Xen Desktop Interview Questions and Answers - Citrix Xen Desktop FAQsDocument3 pagesCitrix Xen Desktop Interview Questions and Answers - Citrix Xen Desktop FAQsAnonymous rNmxZViYaNo ratings yet

- COMPREHENSIVE MUSIC AND ARTS EXAMDocument4 pagesCOMPREHENSIVE MUSIC AND ARTS EXAMChris Patlingrao100% (1)

- MARSIC300 trainingDocument31 pagesMARSIC300 trainingDenys Podlevskykh100% (1)

- Marketing Research of Pre-Start-UpDocument2 pagesMarketing Research of Pre-Start-UpafsalpkgroupNo ratings yet

- Jobber JR DetailsDocument2 pagesJobber JR DetailsUrvish PatelNo ratings yet

- Acronyms Used in Offshore ConstructionDocument32 pagesAcronyms Used in Offshore ConstructionDaniel De Assis ItaborahyNo ratings yet

- WELKIN - Price Reference - 2021-07-15Document1 pageWELKIN - Price Reference - 2021-07-15marcoaparrafNo ratings yet

- MTO Response Letter 0609Document3 pagesMTO Response Letter 0609hwy7and8No ratings yet

- Nested Group PowerShellDocument3 pagesNested Group PowerShellNeha SinghNo ratings yet

- OBJECTIVES QUESTIONS RESISTIVITYDocument3 pagesOBJECTIVES QUESTIONS RESISTIVITYPankaj Kumar SinghNo ratings yet

- Compressive Strength, Chloride Diffusivity and Pore Structure of High Performance Metakaolin and Silica Fume ConcreteDocument8 pagesCompressive Strength, Chloride Diffusivity and Pore Structure of High Performance Metakaolin and Silica Fume ConcreteAboalmaail AlaminNo ratings yet

- I2C Bus ManualDocument51 pagesI2C Bus Manualapi-26349602100% (6)

- Leadership Learnings From Chhatrapati SHDocument5 pagesLeadership Learnings From Chhatrapati SHSagar RautNo ratings yet

- 1100cc Engine Parts CatalogueDocument39 pages1100cc Engine Parts CatalogueSimon placenciaNo ratings yet

- Sound level meter covers noise applicationsDocument2 pagesSound level meter covers noise applicationsAbigail DextreNo ratings yet

- Aymeric Gogibus - ManagementDocument1 pageAymeric Gogibus - ManagementSoufanGroupNo ratings yet

- Julian Assange Why The World Needs Wikileaks: General InstructionsDocument1 pageJulian Assange Why The World Needs Wikileaks: General InstructionsChris CiervoNo ratings yet

- Kurzweil MicropianoDocument24 pagesKurzweil Micropianoestereo8No ratings yet

- MMDS Indoor/Outdoor Transmitter Manual: Chengdu Tengyue Electronics Co., LTDDocument6 pagesMMDS Indoor/Outdoor Transmitter Manual: Chengdu Tengyue Electronics Co., LTDHenry Jose OlavarrietaNo ratings yet

- Occupant Manikin Introduction: 95th Percentile Male Driver ModelDocument9 pagesOccupant Manikin Introduction: 95th Percentile Male Driver ModelarstjunkNo ratings yet

- WB4303EDocument1 pageWB4303EcwiksjNo ratings yet

- Online School Management System Integrated With Accounting Management SystemDocument24 pagesOnline School Management System Integrated With Accounting Management SystemKIRUTHIKA SNo ratings yet

- Operations and Service 69UG15: Diesel Generator SetDocument64 pagesOperations and Service 69UG15: Diesel Generator SetAnonymous NYymdHgyNo ratings yet

- Machine TimeDocument11 pagesMachine TimeFRANCIS THOMASNo ratings yet