Professional Documents

Culture Documents

Recognition: Vlsi Lab Experiments

Uploaded by

Pavan RevankarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Recognition: Vlsi Lab Experiments

Uploaded by

Pavan RevankarCopyright:

Available Formats

VLSI LAB EXPERIMENTS

INTRODUCTION

RECOGNITION

7TH SEMESTER 59 E&C

VLSI LAB EXPERIMENTS

GENERATING MOS AND WIDTH PARAMETERS

7TH SEMESTER 60 E&C

VLSI LAB EXPERIMENTS

CONTACTS RECOGNITION AND RESISTOR SELECTION

7TH SEMESTER 61 E&C

VLSI LAB EXPERIMENTS

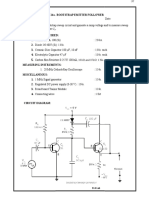

1. INVERTER

CIRCUIT LAYOUT

PHYSICAL LAYOUT

7TH SEMESTER 62 E&C

VLSI LAB EXPERIMENTS

VOLTAGE/TIME OR TRANSIENT ANALYSIS - POWER CONSUMPTION

INPUT VOLTAGE: VDD: 1.2 V

7TH SEMESTER 63 E&C

VLSI LAB EXPERIMENTS

DC ANALYSIS OR TRANSFER CHARACTERISTICS – BIASING POINT

7TH SEMESTER 64 E&C

VLSI LAB EXPERIMENTS

DC ANALYSIS OR TRANSFER CHARACTERISTICS – GAIN

7TH SEMESTER 65 E&C

VLSI LAB EXPERIMENTS

2. COMMON SOURCE AMPLIFIER

CIRCUIT LAYOUT

PHYSICAL LAYOUT

7TH SEMESTER 66 E&C

VLSI LAB EXPERIMENTS

INPUT PARAMETERS

VDD: 1.2 V

INPUT AMPLITUDE: Vin = 0.020 V

GAIN = - 1.4 V

THEORITICAL

Vout = - GAIN X Vin

= - (- 1.4 V) X 0.020 V

= 0.028 V

PRACTICAL

Vout = 0.030V

7TH SEMESTER 67 E&C

VLSI LAB EXPERIMENTS

VOLTAGE/TIME OR TRANSIENT ANALYSIS - POWER CONSUMPTION

7TH SEMESTER 68 E&C

VLSI LAB EXPERIMENTS

DC ANALYSIS OR TRANSFER CHARACTERISTICS – BIASING POINT

7TH SEMESTER 69 E&C

VLSI LAB EXPERIMENTS

DC ANALYSIS OR TRANSFER CHARACTERISTICS – GAIN

7TH SEMESTER 70 E&C

VLSI LAB EXPERIMENTS

3. COMMON DRAIN AMPLIFIER

CIRCUIT LAYOUT

PHYSICAL LAYOUT

7TH SEMESTER 71 E&C

VLSI LAB EXPERIMENTS

INPUT PARAMETERS

INPUT AMPLITUDE: Vin = 0.200 V

GAIN = 0.8 V

THEORITICAL

Vout = GAIN X Vin

= (0.8 V) X 0.200 V

= 0.16 V

PRACTICAL

Vout = 0.111 V

7TH SEMESTER 72 E&C

VLSI LAB EXPERIMENTS

VOLTAGE/TIME OR TRANSIENT ANALYSIS - POWER CONSUMPTION

7TH SEMESTER 73 E&C

VLSI LAB EXPERIMENTS

DC ANALYSIS OR TRANSFER CHARACTERISTICS – BIASING POINT

7TH SEMESTER 74 E&C

VLSI LAB EXPERIMENTS

DC ANALYSIS OR TRANSFER CHARACTERISTICS – GAIN

7TH SEMESTER 75 E&C

VLSI LAB EXPERIMENTS

4. SINGLE STAGE DIFFERENTIAL AMPLIFIER

CIRCUIT LAYOUT

7TH SEMESTER 76 E&C

VLSI LAB EXPERIMENTS

PHYSICAL LAYOUT

7TH SEMESTER 77 E&C

VLSI LAB EXPERIMENTS

INPUT PARAMETERS

7TH SEMESTER 78 E&C

VLSI LAB EXPERIMENTS

VOLTAGE/TIME OR TRANSIENT ANALYSIS

7TH SEMESTER 79 E&C

VLSI LAB EXPERIMENTS

DC ANALYSIS OR TRANSFER CHARACTERISTICS – GAIN

7TH SEMESTER 80 E&C

VLSI LAB EXPERIMENTS

FREQUENCY/TIME OR AC CHARACTERISTICS

7TH SEMESTER 81 E&C

VLSI LAB EXPERIMENTS

5. DIFFERENTIAL AMPLIFIER

CIRCUIT LAYOUT

7TH SEMESTER 82 E&C

VLSI LAB EXPERIMENTS

PHYSICAL LAYOUT

7TH SEMESTER 83 E&C

VLSI LAB EXPERIMENTS

INPUT PARAMETERS

Vin = 0.220

GAIN = 4.2V

THEORITICAL = 0.220 X 4.2 = 0.924 V

PRACTICAL = 1.009 V

7TH SEMESTER 84 E&C

VLSI LAB EXPERIMENTS

VOLTAGE/TIME OR TRANSIENT ANALYSIS

7TH SEMESTER 85 E&C

VLSI LAB EXPERIMENTS

DC ANALYSIS OR TRANSFER CHARACTERISTICS – GAIN

7TH SEMESTER 86 E&C

VLSI LAB EXPERIMENTS

FREQUENCY/TIME OR AC CHARACTERISTICS

7TH SEMESTER 87 E&C

VLSI LAB EXPERIMENTS

6. R-2R LADDER DIGITAL TO ANALOG CONVERTER (DAC)

CIRCUIT LAYOUT

PHYSICAL LAYOUT

7TH SEMESTER 88 E&C

VLSI LAB EXPERIMENTS

INPUT PARAMETERS

VDD: 1.2V

Sl. NO B0 B1 B2 B3

WEIGHTAGE 16 8 4 2

VALUE 0 0 1 1

CALCULATION 0 0 1.2/4 1.2/2

= 0.3 V = 0.6 V

B0 x Vdac/16 + B1 x Vdac/8 + B2 x Vdac/4 + B3 x Vdac/2

VDAC – WEIGHTED VALUE

THEORITICAL = 1.2 – (0.3+0.6) = 0.3 V

PRACTICAL = 0.279 V

VOLTAGE/TIME OR TRANSIENT ANALYSIS

7TH SEMESTER 89 E&C

VLSI LAB EXPERIMENTS

7TH SEMESTER 90 E&C

You might also like

- Citroen CX Workshop ManualDocument611 pagesCitroen CX Workshop ManualDiego Hernan Piñeiro100% (2)

- IEC 61000-4-2 ESD: Immunity To The Discharge of Electrostatic ElectricityDocument23 pagesIEC 61000-4-2 ESD: Immunity To The Discharge of Electrostatic ElectricityCORAL ALONSO100% (4)

- Commissioning Test Auto Reclosing Paper IPTS 2013 Buayaem ENU PDFDocument9 pagesCommissioning Test Auto Reclosing Paper IPTS 2013 Buayaem ENU PDFnassarkiNo ratings yet

- CSS - 9 - Written Assessment With Tos & BetaDocument8 pagesCSS - 9 - Written Assessment With Tos & BetaJevan Hope BaltazarNo ratings yet

- 03 CB - Routine Tests-NewDocument15 pages03 CB - Routine Tests-NewaaaygugNo ratings yet

- Pioneer CDJ-1000 MK3Document116 pagesPioneer CDJ-1000 MK3sw1hbj100% (1)

- Transformer WorkshopDocument44 pagesTransformer Workshopniyaz100% (3)

- HV Routine Test Fields For Extruded Power Cables: N N N NDocument4 pagesHV Routine Test Fields For Extruded Power Cables: N N N NJose Gregorio SanchezNo ratings yet

- EC8461 - EC II Lab ManualDocument90 pagesEC8461 - EC II Lab ManualKarm Pdk50% (2)

- BE8261 - Basic Elecrical, Electronics and Instrumentation Engineering LaboratoryDocument5 pagesBE8261 - Basic Elecrical, Electronics and Instrumentation Engineering LaboratoryKarthikeyan KrishnasamyNo ratings yet

- Lab Report 7 NaDocument4 pagesLab Report 7 Na4k dish infoNo ratings yet

- Exp-7 OC & SC TestDocument7 pagesExp-7 OC & SC TestVamsi RamNo ratings yet

- PTC Ci221350045 858462Document1 pagePTC Ci221350045 858462thangNo ratings yet

- Eca PDC Lab ManualDocument146 pagesEca PDC Lab Manualsoumya varanasiNo ratings yet

- Analog Circuits Lab manual18ECL48Document29 pagesAnalog Circuits Lab manual18ECL48Dintle PhofuNo ratings yet

- ABB 6inch Thyristor For UHVDC TransmissionDocument4 pagesABB 6inch Thyristor For UHVDC TransmissionFaisal WaseemNo ratings yet

- 700MW CSP + 250 MW PV Hybrid IPP - Dewa: Equipment ParametersDocument2 pages700MW CSP + 250 MW PV Hybrid IPP - Dewa: Equipment Parametersmuhammad bin aliNo ratings yet

- Comparação de SupercapacitoresDocument22 pagesComparação de Supercapacitorescarlosalberto.camargoNo ratings yet

- Ec 8261 - Circuits and Devices Laboratory: Second SemesterDocument5 pagesEc 8261 - Circuits and Devices Laboratory: Second SemesterSamraj JebasinghNo ratings yet

- Analog Electronics Laboratory Manual 10ESL37Document58 pagesAnalog Electronics Laboratory Manual 10ESL37Vaishnavi SrinathNo ratings yet

- Basic Electrical Laboratory EEL108A 19Document50 pagesBasic Electrical Laboratory EEL108A 19P SNo ratings yet

- Ec II Lab Manual (2013 2014)Document85 pagesEc II Lab Manual (2013 2014)surendhar1987No ratings yet

- ITEM No.: Bay No.: Drawing Ref.: Sheet: Contractor: Contract No.: Substation NoDocument7 pagesITEM No.: Bay No.: Drawing Ref.: Sheet: Contractor: Contract No.: Substation NosaiNo ratings yet

- Phys230-Ch5-Lect1-BJT BiasingDocument15 pagesPhys230-Ch5-Lect1-BJT BiasingAyeshaNo ratings yet

- ESS 2012 Peer Review - Life Cycle Testing and Evaluation of Energy Storage Devices - Summer Ferreira, SNLDocument16 pagesESS 2012 Peer Review - Life Cycle Testing and Evaluation of Energy Storage Devices - Summer Ferreira, SNLramukolakiNo ratings yet

- ECA Lab Manual-Sreedhar2Document119 pagesECA Lab Manual-Sreedhar2Veerendra KumarNo ratings yet

- Exp-9 Reg of Alternator - RemovedDocument6 pagesExp-9 Reg of Alternator - RemovedVamsi RamNo ratings yet

- Digital Electronics Lab ManualDocument18 pagesDigital Electronics Lab ManualUdayNo ratings yet

- CH 4Document28 pagesCH 4Nasser AlmofariNo ratings yet

- Ec8461 Cd&si LabDocument86 pagesEc8461 Cd&si LabReena RajNo ratings yet

- ECA LabDocument6 pagesECA LabECE DepartmentNo ratings yet

- Electrical and ElectronicsDocument63 pagesElectrical and ElectronicsMr. P. Muthuvel EIE-RESEARCH FACULTYNo ratings yet

- PE Lab ManualDocument95 pagesPE Lab ManualSureshNo ratings yet

- Closed Loop Fed DC DriveDocument103 pagesClosed Loop Fed DC DriveDhivagar NamakkalNo ratings yet

- Testing of Vlsi Circuits: Sequential Circuit Test GenerationDocument108 pagesTesting of Vlsi Circuits: Sequential Circuit Test GenerationSai Satya Krishna PathuriNo ratings yet

- Fat Report MV - 080324Document5 pagesFat Report MV - 080324The GunnersNo ratings yet

- Project: Layyah Combined Cycle Power Plant: Sub Station: Equipment: Panel Type Bay Ref: DateDocument2 pagesProject: Layyah Combined Cycle Power Plant: Sub Station: Equipment: Panel Type Bay Ref: DatesamlashNo ratings yet

- Why Does My Open Delta Connected Phasor Diagram Look WeirdDocument7 pagesWhy Does My Open Delta Connected Phasor Diagram Look WeirdMarcus SunNo ratings yet

- Ee8661 1Document2 pagesEe8661 1YokeshNo ratings yet

- HV Routine Test Fields For Extruded Power Cables Product Brochure 9.21 5 enDocument4 pagesHV Routine Test Fields For Extruded Power Cables Product Brochure 9.21 5 enkingyenzaNo ratings yet

- Exp-6 Load Test On DC Series GenDocument5 pagesExp-6 Load Test On DC Series GenVamsi RamNo ratings yet

- Peak Inrush Current From Capacitor Bank SwitchingDocument23 pagesPeak Inrush Current From Capacitor Bank SwitchingMochammad RizalNo ratings yet

- HCN Sla 00 Bac Ec 00 250-A GCB Factory Test ProcedureDocument13 pagesHCN Sla 00 Bac Ec 00 250-A GCB Factory Test ProcedureBuồnNgủNo ratings yet

- Sts Test FormDocument2 pagesSts Test FormsugiantobarusNo ratings yet

- Technical Data SheetDocument3 pagesTechnical Data Sheetfigv1975No ratings yet

- Spare 7Document5 pagesSpare 7daninadiryan08No ratings yet

- Practical Work Book LcaDocument93 pagesPractical Work Book LcaFaheem Raza100% (2)

- Ec6411 Circuits and Simulation Integrated Lab ManualDocument83 pagesEc6411 Circuits and Simulation Integrated Lab ManualNandhini MohanNo ratings yet

- Laboratory 6 Basic Op Amp CircuitsDocument10 pagesLaboratory 6 Basic Op Amp CircuitsKamran AliNo ratings yet

- Be8261 BeeieDocument82 pagesBe8261 BeeieMohammed OvaizNo ratings yet

- Exercise TemplateDocument13 pagesExercise TemplateKarunaNo ratings yet

- Book 1Document3 pagesBook 1Muhammad Abdul CharisNo ratings yet

- Vize 2015 PDFDocument1 pageVize 2015 PDFHasan ZehirNo ratings yet

- Ee8261 ManualDocument56 pagesEe8261 Manualpapayee lakshmananNo ratings yet

- EE-100 Introduction To Electrical Engineering: Lab 2: Verification of KVL and Voltage Division RuleDocument6 pagesEE-100 Introduction To Electrical Engineering: Lab 2: Verification of KVL and Voltage Division RuleSpoider YTNo ratings yet

- Exp-8 Sump TestDocument7 pagesExp-8 Sump TestVamsi RamNo ratings yet

- ENA - Lab - Manual (Update 17-4-2019) PDFDocument76 pagesENA - Lab - Manual (Update 17-4-2019) PDFMuhammad SaadNo ratings yet

- EC-2 Lab ManualDocument93 pagesEC-2 Lab ManualatchayaNo ratings yet

- Anna University Lab Manuals For Engineering Students Open Circuit & Short Circuit Test On A Single Phase TransformerDocument9 pagesAnna University Lab Manuals For Engineering Students Open Circuit & Short Circuit Test On A Single Phase TransformerLeonardoXanMNo ratings yet

- EEE F211 Orientation1 Cycle PDFDocument31 pagesEEE F211 Orientation1 Cycle PDFJAY JANAK MANEKNo ratings yet

- PR No.2 Superposition TheoremDocument4 pagesPR No.2 Superposition Theorembadgujar_bandhuNo ratings yet

- 3-Phase VoltDocument14 pages3-Phase VoltBibah GeeNo ratings yet

- ZK-201 Manufacturer Data Sheet enDocument1 pageZK-201 Manufacturer Data Sheet enAbdoul IsmailNo ratings yet

- Fdocuments - in - Ca650059en 600 A 25 KV Class T Op II Deadbreak Apparatus With Its Cooper PowerDocument8 pagesFdocuments - in - Ca650059en 600 A 25 KV Class T Op II Deadbreak Apparatus With Its Cooper PowerJalal AlbadriNo ratings yet

- EPack-2PH Data Sheet USADocument6 pagesEPack-2PH Data Sheet USARichard TroetschNo ratings yet

- Multiplexed Energy Metering AFEs Ease ASIC Integration and Provide Significant Cost ReductionDocument6 pagesMultiplexed Energy Metering AFEs Ease ASIC Integration and Provide Significant Cost ReductionEngr Muhammad Irfan ShahidNo ratings yet

- Logic Gates SAMDocument15 pagesLogic Gates SAMSatyam TripathiNo ratings yet

- Cambridge IGCSE Physics Block4 ElectricityDocument8 pagesCambridge IGCSE Physics Block4 ElectricityRattee SirirojtanadolNo ratings yet

- Raytheon R1206XXDocument70 pagesRaytheon R1206XXtyutyuNo ratings yet

- 9086 Cuadro AnacondaDocument19 pages9086 Cuadro Anacondaestefany camargoNo ratings yet

- 5V - 48V Small Footprint, Surface Mount Transient Voltage SuppressorsDocument5 pages5V - 48V Small Footprint, Surface Mount Transient Voltage SuppressorsNuc LeusNo ratings yet

- Science Class 8 Electrical CircuitsDocument7 pagesScience Class 8 Electrical CircuitsPramitaNo ratings yet

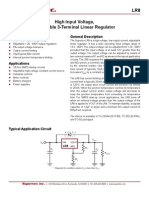

- Supertex Inc.: LR8 High Input Voltage, Adjustable 3-Terminal Linear RegulatorDocument10 pagesSupertex Inc.: LR8 High Input Voltage, Adjustable 3-Terminal Linear RegulatorristrettoNo ratings yet

- Fisher Fieldvue DVC6200 SIS Digital Valve Controller: Instruction ManualDocument116 pagesFisher Fieldvue DVC6200 SIS Digital Valve Controller: Instruction Manualanon_179203922No ratings yet

- Eee3091F: Energy Conversion Intro, Applications, Machine TypesDocument27 pagesEee3091F: Energy Conversion Intro, Applications, Machine TypesYousuf IsaacsNo ratings yet

- Westinghouse Lighting MFB-1000 General Purpose Mercury Floodlight Spec Sheet 3-72Document2 pagesWestinghouse Lighting MFB-1000 General Purpose Mercury Floodlight Spec Sheet 3-72Alan MastersNo ratings yet

- KW600 User ManualDocument31 pagesKW600 User ManualSantiago OviedoNo ratings yet

- Rulmeca Motorized Pulley Catalog12 PG 78-89Document12 pagesRulmeca Motorized Pulley Catalog12 PG 78-89zikezakosiNo ratings yet

- Excel Shortcuts CFIDocument19 pagesExcel Shortcuts CFIRAVICHANDRAN LNo ratings yet

- Eaton 134917 DS7 340SX055N0 N en - GBDocument5 pagesEaton 134917 DS7 340SX055N0 N en - GBasmoosa_scribdNo ratings yet

- Motor m42sp 6nkDocument2 pagesMotor m42sp 6nkWil WiltmarNo ratings yet

- TQI7002700 SJ02 V 01Document1 pageTQI7002700 SJ02 V 01Natalya DrugakovaNo ratings yet

- EKM Metering EKM-15E 120 Volt Meter Spec SheetDocument2 pagesEKM Metering EKM-15E 120 Volt Meter Spec SheetAdam BrouwerNo ratings yet

- NV3029C v0.2Document182 pagesNV3029C v0.2SpecShareNo ratings yet

- Biographical Recount TextDocument1 pageBiographical Recount TextRafi DaffaNo ratings yet

- Ac70 SeriesDocument147 pagesAc70 SeriesNguyễn Đức SơnNo ratings yet

- Past Papers Mcqs With solution-SUPARCO-NTS Past PapersDocument22 pagesPast Papers Mcqs With solution-SUPARCO-NTS Past PaperszunairaNo ratings yet

- Posco CrgoDocument35 pagesPosco CrgoRichard SyNo ratings yet