Professional Documents

Culture Documents

CS 162 Computer Architecture: Cs 152 l6 Multiply DAP Fa 97 © U.C.B

Uploaded by

Kabindra ShresthaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CS 162 Computer Architecture: Cs 152 l6 Multiply DAP Fa 97 © U.C.B

Uploaded by

Kabindra ShresthaCopyright:

Available Formats

CS 162

Computer Architecture

Lecture 10

L.N. Bhuyan

cs 152 l6 Multiply 1 DAP Fa 97 © U.C.B.

MIPS arithmetic

° instructions

Instruction Example Meaning Comments

° add add $1,$2,$3 $1 = $2 + $3 3 operands; exception possible

° subtract sub $1,$2,$3 $1 = $2 – $3 3 operands; exception possible

° add immediate addi $1,$2,100 $1 = $2 + 100 + constant; exception possible

° add unsigned addu $1,$2,$3 $1 = $2 + $3 3 operands; no exceptions

° subtract unsigned subu $1,$2,$3 $1 = $2 – $3 3 operands; no exceptions

° add imm. unsign. addiu $1,$2,100 $1 = $2 + 100 + constant; no exceptions

° multiply mult $2,$3 Hi, Lo = $2 x $3 64-bit signed product

° multiply unsigned multu$2,$3 Hi, Lo = $2 x $3 64-bit unsigned product

° divide div $2,$3 Lo = $2 ÷ $3, Lo = quotient, Hi = remainder

° Hi = $2 mod $3

° divide unsigned divu $2,$3 Lo = $2 ÷ $3, Unsigned quotient & remainder

° Hi = $2 mod $3

° Move from Hi mfhi $1 $1 = Hi Used to get copy of Hi

° Move from Lo mflo $1 $1 = Lo Used to get copy of Lo

cs 152 l6 Multiply 2 DAP Fa 97 © U.C.B.

MULTIPLY

(unsigned)

° Paper and pencil example (unsigned):

Multiplicand 1000

Multiplier 1001

1000

0000

0000

1000

Product 01001000

° m bits x n bits = m+n bit product

° Binary makes it easy:

•0 => place 0 ( 0 x multiplicand)

•1 => place a copy ( 1 x multiplicand)

° 4 versions of multiply hardware & algorithm:

•successive refinement

cs 152 l6 Multiply 3 DAP Fa 97 © U.C.B.

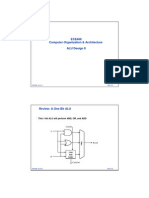

Unisigned shift-add multiplier (version

1)

° 64-bit Multiplicand reg, 64-bit ALU, 64-bit Product reg,

32-bit multiplier reg

Shift Left

Multiplicand

64 bits

Multiplier Shift Right

64-bit ALU

32 bits

Write

Product Control

64 bits

Multiplier = datapath + control

cs 152 l6 Multiply 4 DAP Fa 97 © U.C.B.

Multiply Algorithm Version Start

1

Multiplier0 = 1 1. Test Multiplier0 = 0

Multiplier0

1a. Add multiplicand to product &

place the result in Product register

° Product Multiplier Multiplicand

0000 0000 0011 0000 0010 2. Shift the Multiplicand register left 1 bit.

° 0000 0010 0001 0000 0100

3. Shift the Multiplier register right 1 bit.

° 0000 0110 0000 0000 1000

° 0000 0110 32nd No: < 32 repetitions

repetition?

Yes: 32 repetitions

Done

cs 152 l6 Multiply 5 DAP Fa 97 © U.C.B.

Observations on Multiply Version

1

° 1 clock per cycle => 100 clocks per multiply

• Ratio of multiply to add 5:1 to 100:1

° 1/2 bits in multiplicand always 0

=> 64-bit adder is wasted

° 0’s inserted in left of multiplicand as shifted

=> least significant bits of product never changed

once formed

° Instead of shifting multiplicand to left, shift product to

right?

cs 152 l6 Multiply 6 DAP Fa 97 © U.C.B.

MULTIPLY HARDWARE Version 2

° Half of the shifted multiplicand register contains 0.

Why not shift the product right?

° 32-bit Multiplicand reg, 32 -bit ALU, 64-bit Product reg,

32-bit Multiplier reg

Multiplican

d

32 bits

Multiplier Shift Right

32-bit ALU 32 bits

Shift Right

Product Control

64 bits Write

cs 152 l6 Multiply 7 DAP Fa 97 © U.C.B.

Multiply Algorithm Version Start

2

Multiplier Multiplicand Product

0011 0010 0000 0000

Multiplier0 = 1 1. Test Multiplier0 = 0

Multiplier0

1a. Add multiplicand to the left half of product &

place the result in the left half of Product register

° Product Multiplier Multiplicand

0000 0000 0011 0010

2. Shift the Product register right 1 bit.

3. Shift the Multiplier register right 1 bit.

32nd No: < 32 repetitions

repetition?

Yes: 32 repetitions

Done

cs 152 l6 Multiply 8 DAP Fa 97 © U.C.B.

MULTIPLY HARDWARE Version 3

° Product register wastes space that exactly matches

size of multiplier

=> combine Multiplier register and Product register

° 32-bit Multiplicand reg, 32 -bit ALU, 64-bit Product

reg, (0-bit Multiplier reg)

Multiplican

d

32 bits

32-bit ALU

Shift Right

Product (Multiplier) Control

64 bits Write

cs 152 l6 Multiply 10 DAP Fa 97 © U.C.B.

Multiply Algorithm Version Start

3

Multiplicand Product

0010 0000 0011

Product0 = 1 1. Test Product0 = 0

Product0

1a. Add multiplicand to the left half of product &

place the result in the left half of Product register

2. Shift the Product register right 1 bit.

32nd No: < 32 repetitions

repetition?

Yes: 32 repetitions

Done

cs 152 l6 Multiply 11 DAP Fa 97 © U.C.B.

Observations on Multiply Version

3

° 2 steps per bit because Multiplier & Product combined

° MIPS registers Hi and Lo are left and right half of Product

° Gives us MIPS instruction MultU

° How can you make it faster?

° What about signed multiplication?

• easiest solution is to make both positive & remember whether to

complement product when done (leave out the sign bit, run for 31

steps)

• apply definition of 2’s complement

- need to sign-extend partial products and subtract at the end

• Booth’s Algorithm is elegant way to multiply signed numbers using

same hardware as before and save cycles

- can handle multiple bits at a time

cs 152 l6 Multiply 12 DAP Fa 97 © U.C.B.

Motivation for Booth’s

Algorithm

° Example 2 x 6 = 0010 x 0110:

0010

x 0110

+ 0000 shift (0 in multiplier)

+ 0010 add (1 in multiplier)

+ 0100 add (1 in multiplier)

+ 0000 shift (0 in multiplier)

00001100

° ALU with add or subtract gets same result in more than one way:

6 = – 2 + 8

0110 = – 00010 + 01000 = 11110 + 01000

° For example

° 0010

x 0110

0000 shift (0 in multiplier)

– 0010 sub (first 1 in multpl.)

. 0000 shift (mid string of 1s)

. + 0010 add (prior step had last

1) 00001100

cs 152 l6 Multiply 13 DAP Fa 97 © U.C.B.

Booth’s

Algorithm

middle of run

end of run beginning of run

011110

Current Bit Bit to the Right Explanation Example Op

1 0 Begins run of 1s 0001111000 sub

1 1 Middle of run of 1s 0001111000 none

0 1 End of run of 1s 0001111000 add

0 0 Middle of run of 0s 0001111000 none

Originally for Speed (when shift was faster than add)

° Replace a string of 1s in multiplier with an initial subtract when we first

see a one and then later add for the bit after the last one –1

+ 10000

01111

cs 152 l6 Multiply 14 DAP Fa 97 © U.C.B.

Booths Example (2 x

7)

Operation Multiplicand Product next?

0. initial value 0010 0000 0111 0 10 -> sub

1a. P = P - m 1110 + 1110

1110 0111 0 shift P (sign ext)

1b. 0010 1111 0011 1 11 -> nop, shift

2. 0010 1111 1001 1 11 -> nop, shift

3. 0010 1111 1100 1 01 -> add

4a. 0010 + 0010

0001 1100 1 shift

4b. 0010 0000 1110 0 done

cs 152 l6 Multiply 15 DAP Fa 97 © U.C.B.

Booths Example (2 x

-3)

Operation Multiplicand Product next?

0. initial value 0010 0000 1101 0 10 -> sub

1a. P = P - m 1110 + 1110

1110 1101 0 shift P (sign ext)

1b. 0010 1111 0110 1 01 -> add

+ 0010

2a. 0001 0110 1 shift P

2b. 0010 0000 1011 0 10 -> sub

+ 1110

3a. 0010 1110 1011 0 shift

3b. 0010 1111 0101 1 11 -> nop

4a 1111 0101 1 shift

4b. 0010 1111 1010 1 done

cs 152 l6 Multiply 16 DAP Fa 97 © U.C.B.

You might also like

- Chapter3 Arithmetic For ComputersDocument51 pagesChapter3 Arithmetic For ComputersZhuan WuNo ratings yet

- Computer Architecture Chapter on ArithmeticDocument52 pagesComputer Architecture Chapter on ArithmeticHuyNo ratings yet

- 2.2 Multiplication & DivisionDocument28 pages2.2 Multiplication & DivisionGireesh DgNo ratings yet

- ECE232: Hardware Organization and Design: MULTIPLY (Unsigned)Document18 pagesECE232: Hardware Organization and Design: MULTIPLY (Unsigned)Srinivas CherukuNo ratings yet

- Ch4 Mult DivDocument41 pagesCh4 Mult DivAngga RiyandiNo ratings yet

- Ece552 08 Integer MultiplyDocument22 pagesEce552 08 Integer MultiplyMoin PashaNo ratings yet

- Ece552 08 Integer MultiplyDocument22 pagesEce552 08 Integer MultiplyAbinaya87No ratings yet

- 2.2 Multiplication & Division PDFDocument28 pages2.2 Multiplication & Division PDFGireesh DgNo ratings yet

- Review: A One Bit Alu: CarryinDocument6 pagesReview: A One Bit Alu: CarryinNarender KumarNo ratings yet

- CPE 335 CPE 335 Computer Organization MIPS Arithmetic - Part IIDocument28 pagesCPE 335 CPE 335 Computer Organization MIPS Arithmetic - Part IIِAbdul-Rahman Al-magidiNo ratings yet

- Designing A Divider: With Contributions From J. Kubiatowicz (CS152)Document12 pagesDesigning A Divider: With Contributions From J. Kubiatowicz (CS152)PahomijeNo ratings yet

- Computer Science 37 Lecture 9Document17 pagesComputer Science 37 Lecture 9Alexander TaylorNo ratings yet

- Design A Fast ALU For The MIPS ISA - Requirements ?Document71 pagesDesign A Fast ALU For The MIPS ISA - Requirements ?thanhvnptNo ratings yet

- Lecture 8: Binary Multiplication & DivisionDocument20 pagesLecture 8: Binary Multiplication & DivisionAfnanNo ratings yet

- Lecture 8: Binary Multiplication & DivisionDocument20 pagesLecture 8: Binary Multiplication & DivisionTahir KhanNo ratings yet

- ECE468 Computer Organization & Architecture ALU Design II: °this 1-Bit ALU Will Perform AND, OR, and ADDDocument16 pagesECE468 Computer Organization & Architecture ALU Design II: °this 1-Bit ALU Will Perform AND, OR, and ADDNarender KumarNo ratings yet

- Unit 2 PPT COCADocument58 pagesUnit 2 PPT COCAvenkat anjemetiNo ratings yet

- CS M151B / EE M116C: Computer Systems ArchitectureDocument29 pagesCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNo ratings yet

- Computer Architecture ECE 361 Lecture 6: ALU DesignDocument33 pagesComputer Architecture ECE 361 Lecture 6: ALU DesignRahul SinghNo ratings yet

- Multiplication: - Accomplished Via Shifting and AdditionDocument4 pagesMultiplication: - Accomplished Via Shifting and Additionanand_duraiswamyNo ratings yet

- D S A K: Igital EsignDocument63 pagesD S A K: Igital EsignBilal KhanNo ratings yet

- Review Multiple Hardware AlgorithmsDocument6 pagesReview Multiple Hardware AlgorithmsNarender KumarNo ratings yet

- Data Representation (V) for SMJE3093Document75 pagesData Representation (V) for SMJE3093Andre207No ratings yet

- 1 Number SystemDocument137 pages1 Number Systemfangkevin33No ratings yet

- ECE4680 Computer Organization & Architecture Divide, Floating Point, Pentium BugDocument17 pagesECE4680 Computer Organization & Architecture Divide, Floating Point, Pentium BugNarender KumarNo ratings yet

- CPSC 161: Prof. L.N. Bhuyan .HTMLDocument28 pagesCPSC 161: Prof. L.N. Bhuyan .HTMLShyamala RamachandranNo ratings yet

- Booth's Algorithm - Multiplication & DivisionDocument27 pagesBooth's Algorithm - Multiplication & Divisionnaveen86% (21)

- Review: MIPS Organization: Processor MemoryDocument13 pagesReview: MIPS Organization: Processor MemorytyfnpkrNo ratings yet

- Embedded C and The PIC Micro ControllerDocument12 pagesEmbedded C and The PIC Micro ControllermanasbiswalNo ratings yet

- ASIC Design for Signal Processing Using Booth RecodingDocument4 pagesASIC Design for Signal Processing Using Booth RecodingMichael SohanlallNo ratings yet

- Lecture 11 - CH 03Document19 pagesLecture 11 - CH 03Osama RousanNo ratings yet

- BOOTHDocument3 pagesBOOTHBharath VijaiNo ratings yet

- Lecture 4 Computer Arithmetic Part I IntegersDocument19 pagesLecture 4 Computer Arithmetic Part I IntegerstesfuNo ratings yet

- Chapter 3 Part 3 PDFDocument11 pagesChapter 3 Part 3 PDFHeba M AL SalmiNo ratings yet

- Expt No: 8086 Programming Date: Addition & SubtractionDocument63 pagesExpt No: 8086 Programming Date: Addition & SubtractionpinnamanenimounikaNo ratings yet

- Booth's Algorithm ExplainedDocument14 pagesBooth's Algorithm ExplainedFarhat VooDooNo ratings yet

- Computer Arithmetic Part I: IntegersDocument19 pagesComputer Arithmetic Part I: IntegerstesfuNo ratings yet

- Arithmetic: - Performance (Seconds, Cycles, Instructions) - AbstractionsDocument7 pagesArithmetic: - Performance (Seconds, Cycles, Instructions) - Abstractionsanand_duraiswamyNo ratings yet

- 2.1 Addtion&subtractionDocument42 pages2.1 Addtion&subtractionGireesh DgNo ratings yet

- This Unit: Arithmetic and ALU Design ShiftsDocument8 pagesThis Unit: Arithmetic and ALU Design ShiftsBhagya RajuNo ratings yet

- Bit Op Stanford PDFDocument14 pagesBit Op Stanford PDFnatitsionmamNo ratings yet

- Simple Shift-Add Multiplier: ELE 4550 ASIC Technologies Project TutorialDocument3 pagesSimple Shift-Add Multiplier: ELE 4550 ASIC Technologies Project TutorialramyarakiNo ratings yet

- SLHT Grade 7 CSS Week 4Document7 pagesSLHT Grade 7 CSS Week 4princeyahweNo ratings yet

- 9 Multiplication and DivisionDocument11 pages9 Multiplication and DivisionAkhilReddy SankatiNo ratings yet

- Presentation EE471 MultiplicationDocument20 pagesPresentation EE471 MultiplicationVõ Hoàng ChươngNo ratings yet

- Computer Arithmetic OperationsDocument71 pagesComputer Arithmetic OperationsRayan IslamNo ratings yet

- Efficient Multiplier TechniquesDocument3 pagesEfficient Multiplier Techniquesdeepakkr22781No ratings yet

- Introduction To CMOS VLSI Design (E158) Lecture 16: Datapath Functional UnitsDocument26 pagesIntroduction To CMOS VLSI Design (E158) Lecture 16: Datapath Functional UnitsAnil KumarNo ratings yet

- Microprocessor 8085 ManualDocument30 pagesMicroprocessor 8085 Manualrajji_kashish100% (2)

- C Programming Bitwise OperatorsDocument12 pagesC Programming Bitwise Operatorspawan vermaNo ratings yet

- CS205-Assignment1-solutionDocument7 pagesCS205-Assignment1-solutionjohnnybyzhangNo ratings yet

- Lecture5 CENG241 Fall2015Document22 pagesLecture5 CENG241 Fall2015Aurghya SahaNo ratings yet

- Chapter IV Computer ArithmeticDocument133 pagesChapter IV Computer Arithmeticsr23shubhiNo ratings yet

- Chapter 3Document47 pagesChapter 3Curacao JTRNo ratings yet

- Arithmetic Coprocessor Coprocessor BasicDocument83 pagesArithmetic Coprocessor Coprocessor Basicprachi pandey100% (6)

- Multipliers: Presented ByDocument13 pagesMultipliers: Presented ByNitin Suyan PanchalNo ratings yet

- Python Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibFrom EverandPython Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibNo ratings yet

- DevKitC - Getting - Started - Guide - EN ESP8266Document11 pagesDevKitC - Getting - Started - Guide - EN ESP8266BIT MechanicalNo ratings yet

- Midterm AnswersDocument9 pagesMidterm Answerspocho_gt500No ratings yet

- 1 - Advanced Network ArchitectureDocument10 pages1 - Advanced Network ArchitectureAbdouMohamedNo ratings yet

- IEC 61850 Server Interface: User ManualDocument33 pagesIEC 61850 Server Interface: User ManualThành CôngNo ratings yet

- Arquestra SystemDocument42 pagesArquestra SystemLuis AngelNo ratings yet

- Token Rings (802.5)Document26 pagesToken Rings (802.5)Naveen IdxNo ratings yet

- Practical MSX Machine Code Programming Steve Webb TextDocument105 pagesPractical MSX Machine Code Programming Steve Webb TextRebelliousXNo ratings yet

- MATLAB Functions for LabJack U12 CommunicationDocument18 pagesMATLAB Functions for LabJack U12 CommunicationgennarinomingNo ratings yet

- HBase Succinctly PDFDocument85 pagesHBase Succinctly PDFrisjakNo ratings yet

- Siemens RedundancyDocument30 pagesSiemens RedundancyWan EzzatNo ratings yet

- Appendix C - Ntmf01 Termination Unit Configuration: C-1 C-2 C-3 C-4 C-5Document6 pagesAppendix C - Ntmf01 Termination Unit Configuration: C-1 C-2 C-3 C-4 C-5ganistrumNo ratings yet

- TR-134 - Corrigendum-1 Broadband Policy Control PDFDocument110 pagesTR-134 - Corrigendum-1 Broadband Policy Control PDFDaniel ReyesNo ratings yet

- PCNSE7 - Pass Palo Alto Networks Certified Network Security Engineer ExamDocument37 pagesPCNSE7 - Pass Palo Alto Networks Certified Network Security Engineer ExamSaurabh Gupta100% (1)

- Centrala FC 2060Document18 pagesCentrala FC 2060Danijel PavićNo ratings yet

- Catalyst 6000 Family Software Configuration GuideDocument880 pagesCatalyst 6000 Family Software Configuration GuideMaximo ExilioNo ratings yet

- Intel Serial IO - Bring Up Guide and Release Note Rev1p0Document30 pagesIntel Serial IO - Bring Up Guide and Release Note Rev1p0gdfeiu dionwdnNo ratings yet

- Stockd DebuglogDocument2 pagesStockd DebuglogAabhasNo ratings yet

- Task 2 - Repair SMART TracksDocument10 pagesTask 2 - Repair SMART TracksCapacitacion CrodeNo ratings yet

- BEST PRACTICES IN JCL AGENDADocument36 pagesBEST PRACTICES IN JCL AGENDAshilpakhaireNo ratings yet

- Ask The Expert Udfs Part 4 Making Udfs Work in ParallelDocument36 pagesAsk The Expert Udfs Part 4 Making Udfs Work in ParallelAhmed Mohammed AwadNo ratings yet

- Introduction To MicroprocessorDocument264 pagesIntroduction To MicroprocessorUdit GuptaNo ratings yet

- Switchport Port Security Explained With ExamplesDocument10 pagesSwitchport Port Security Explained With ExamplesAyush UppalNo ratings yet

- How To Backup Oracle Database Using RMAN (With Examples)Document1 pageHow To Backup Oracle Database Using RMAN (With Examples)Marco Capac YupanquiNo ratings yet

- Operating Systems: User InterfaceDocument9 pagesOperating Systems: User InterfaceDmdhineshNo ratings yet

- Lab1 Build and Execute A Simple Message FlowDocument38 pagesLab1 Build and Execute A Simple Message Flow'SudarshanRaiNo ratings yet

- Enter The BIOS On Any PC Access Keys by ManufacturerDocument5 pagesEnter The BIOS On Any PC Access Keys by ManufacturerNimish MadananNo ratings yet

- TR17 ME11 StaticDocument51 pagesTR17 ME11 Staticemazitov-1No ratings yet

- Wireless and Mobile Computing: University of GujratDocument42 pagesWireless and Mobile Computing: University of GujratIqra HanifNo ratings yet

- Requirements: For OMICRON Test Universe 3.20Document5 pagesRequirements: For OMICRON Test Universe 3.20Khalfan AlhashmiNo ratings yet

- DHomesb Chapter 6 - CCNA DiscoveryDocument6 pagesDHomesb Chapter 6 - CCNA DiscoveryAbdullah Al HawajNo ratings yet