Professional Documents

Culture Documents

Aes Arch

Uploaded by

ibzz1982Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Aes Arch

Uploaded by

ibzz1982Copyright:

Available Formats

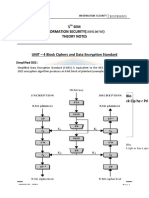

AES Implementation details

AES is implemented as defined in the FIPS-197 document.

The Algorithm is implemented in ECB mode.

ADD ROUND KEY

SUB SHIFT MIX

BYTES ROWS COLS

CIPHER TEXT

INPUT TEXT

[128 BITS]

KEY [128 BITS]

SUB ROT

WORD WORD

W[i-NK]

RCON

Figure 1-Error! No text of specified style in document.-1 Architectural block diagram

For details about each of the blocks refer the FIPS-197 document.

The decryption process follows virtually the same order as encryption except for another

round of mix columns on the generated keys before giving them to the add round key

step. This flow is clearly explained in the FIPS-197 document.

The encryption/decryption sequence

Input data and key is fed in two blocks of 64 bits in consequtive clock cycles with the

load signal. 64 bits of input and key are read in the posedge after the load signal goes

high and another block of 64 bits of input and key are read in the posedge after the load

signal goes low. Hence the complete data and key is loaded only when the load signal

makes a low-high-low transition(basically a pulse). The process starts once the start

signal is pulsed and the output is validated with 'done' signal 13 clock cycles after the

'start' signal goes low . 'done' remains high until the next start cycle.

clk

load

start

13 clock cycles after start goes low

done

input block input block

data_in [64-127]

[0-63]

key block key block

data_in [64-127]

[0-63]

data_out output valid

Figure -2 Process sequence for encryption/decryption

The arcitecture isnt pipelined and hence only able to perform multi encryption/decryption

serially one after the other. The output is registered and avialable after 'done' signal goes

high. Asserting the start signal during an encrytion/decryption process will lead to

erroneous output.

You might also like

- Cisco CCNA Command Guide: An Introductory Guide for CCNA & Computer Networking Beginners: Computer Networking, #3From EverandCisco CCNA Command Guide: An Introductory Guide for CCNA & Computer Networking Beginners: Computer Networking, #3No ratings yet

- Network with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationFrom EverandNetwork with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationNo ratings yet

- Current Transformers How To Specify Them PDFDocument36 pagesCurrent Transformers How To Specify Them PDFargari19No ratings yet

- Staad ExcelentsDocument159 pagesStaad ExcelentsCe Win100% (4)

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- Key Injection by Master POS Operation Manual - v1.00 - 20161228Document9 pagesKey Injection by Master POS Operation Manual - v1.00 - 20161228Bishal Panda100% (2)

- UVM and Formal Verification of AES ModuleDocument29 pagesUVM and Formal Verification of AES ModuleChristiensen ArandillaNo ratings yet

- Ipsec Ike PDFDocument26 pagesIpsec Ike PDFPushpendra KumarNo ratings yet

- Shadowsocks: A Secure SOCKS5 Proxy: 1 OverviewDocument9 pagesShadowsocks: A Secure SOCKS5 Proxy: 1 OverviewPhilemon SundayNo ratings yet

- SpeedControl V90 S7-1200 DOC enDocument23 pagesSpeedControl V90 S7-1200 DOC enDavid LucioNo ratings yet

- Aes Ip Design DocDocument12 pagesAes Ip Design DocPrajkta DumbreNo ratings yet

- Lecture 2B RTL Design Methodology Transition From Pseudocode & Interface To A Corresponding Block DiagramDocument44 pagesLecture 2B RTL Design Methodology Transition From Pseudocode & Interface To A Corresponding Block DiagramAli Mohamed EltemsahNo ratings yet

- VHDL Aes 128 Encryption/Decryption: Bradley University Department of Electrical and Computer EngineeringDocument34 pagesVHDL Aes 128 Encryption/Decryption: Bradley University Department of Electrical and Computer EngineeringROo GAaNo ratings yet

- FPGA Implementation of AES Encryption and DecryptionDocument16 pagesFPGA Implementation of AES Encryption and DecryptionSatya NarayanaNo ratings yet

- Is CH4Document13 pagesIs CH4Dhruv SojitraNo ratings yet

- 554 00055 0 CS5280Document8 pages554 00055 0 CS5280WERLAN SILVANo ratings yet

- A 2.29 Gbitshec, 56 MW Non-Pipelined Rijndael AES Encryption Ina TechnologyDocument4 pagesA 2.29 Gbitshec, 56 MW Non-Pipelined Rijndael AES Encryption Ina TechnologyDeep SahaniNo ratings yet

- CNS Unit 2Document119 pagesCNS Unit 2Mr.Ashok SNo ratings yet

- DIS Unit IIDocument25 pagesDIS Unit IIBhuvaneshwari MNo ratings yet

- Block CipherDocument31 pagesBlock Ciphersanthosh n prabhuNo ratings yet

- Module 2 - Symmetric and Asymmetric Key Cryptography and Key ManagementDocument37 pagesModule 2 - Symmetric and Asymmetric Key Cryptography and Key Management04 KHUSHBU BHATIA SE ANo ratings yet

- BADC Conf 20Document2 pagesBADC Conf 20WasimulHaq WaimulNo ratings yet

- 214 Naef AesDocument8 pages214 Naef AesMrunali BarapatreNo ratings yet

- K L Code Hopping Encoder: EE OQ®Document34 pagesK L Code Hopping Encoder: EE OQ®prophaithNo ratings yet

- Network Security 2Document57 pagesNetwork Security 2DarshanNo ratings yet

- 2.7.6 Packet Tracer - Implement Basic ConnectivityDocument4 pages2.7.6 Packet Tracer - Implement Basic ConnectivityMerveille AizannonNo ratings yet

- SPsymposium Paper24 PDFDocument2 pagesSPsymposium Paper24 PDFRheaNo ratings yet

- Circuito Integrado HCS201Document29 pagesCircuito Integrado HCS201AndrésCardozoNo ratings yet

- Configuracion SSH en Gns3Document8 pagesConfiguracion SSH en Gns3Beto PuertasNo ratings yet

- BH Asia Matrosov Modern Secure Boot Attacks PDFDocument72 pagesBH Asia Matrosov Modern Secure Boot Attacks PDFManuel LeaNo ratings yet

- AES Cipher Modes With EFM32: AN0033 - Application NoteDocument20 pagesAES Cipher Modes With EFM32: AN0033 - Application NoteJavier Dorado SánchezNo ratings yet

- RC4 PRS GeneratorDocument4 pagesRC4 PRS GeneratorghionoiucNo ratings yet

- CCENT Lab 3 1 Enhancing The Initial Security v1.0.1Document32 pagesCCENT Lab 3 1 Enhancing The Initial Security v1.0.1Bijay LamaNo ratings yet

- Data Encryption StandardDocument72 pagesData Encryption StandardAkil KumarNo ratings yet

- Unit 1 AnsDocument39 pagesUnit 1 AnsVikramadityaNo ratings yet

- 11 Workbook+Warm+Up+LineDocument10 pages11 Workbook+Warm+Up+LineSaïd MOUGAMADOUSSOULTANENo ratings yet

- CNS UNIT-2 NotesDocument30 pagesCNS UNIT-2 Notespravallika100% (1)

- 07-Block Cipher Operation+stream CipherDocument37 pages07-Block Cipher Operation+stream Cipher6alal UshNo ratings yet

- Ikev2: Mubeen Nevrekar July 2021Document23 pagesIkev2: Mubeen Nevrekar July 2021Arun MmohantyNo ratings yet

- 21137GDocument36 pages21137GLaurence MichaelNo ratings yet

- Aes Algorithm For Encryption: Radhika D.BajajDocument6 pagesAes Algorithm For Encryption: Radhika D.BajajamrinNo ratings yet

- Experiment 6 - DDCADocument4 pagesExperiment 6 - DDCAbonthugouthamNo ratings yet

- R&S-1 Lab ManualDocument31 pagesR&S-1 Lab Manualsivac7000No ratings yet

- CS6701 CNS Unit-Ii NotesDocument23 pagesCS6701 CNS Unit-Ii Notesgayathri baskarNo ratings yet

- Spanning Tree Lab: Step 1: Getting Familiar With Switch IOSDocument21 pagesSpanning Tree Lab: Step 1: Getting Familiar With Switch IOSNNo ratings yet

- FPGA Based Lightweight Encryption Algorithm For Cyber Security ApplicationsDocument13 pagesFPGA Based Lightweight Encryption Algorithm For Cyber Security Applicationsmarvel homesNo ratings yet

- Block Ciphers: Dr. Md. Mahbubur RahmnaDocument124 pagesBlock Ciphers: Dr. Md. Mahbubur RahmnaimtibdNo ratings yet

- HCS301Document20 pagesHCS301Anonymous iNxLvwNo ratings yet

- Ips BasicsDocument19 pagesIps BasicsaloneheartsNo ratings yet

- 140 SP 2007Document15 pages140 SP 2007wahyu.pangestu007No ratings yet

- Advanced Encryption Standard (AES) : DR Faisal BashirDocument32 pagesAdvanced Encryption Standard (AES) : DR Faisal BashirJaveria AbbasiNo ratings yet

- CCNA1 - H2/H6: Cheat SheetDocument7 pagesCCNA1 - H2/H6: Cheat SheetBart De ZaeytydtNo ratings yet

- SMS EncryptDocument26 pagesSMS Encryptshankar rNo ratings yet

- ps2 Mux PDFDocument27 pagesps2 Mux PDFAnonymous pcNdMpNENo ratings yet

- Stream Cipher: July 2011Document32 pagesStream Cipher: July 2011KeerthanasudarshanNo ratings yet

- Introduction and AssemblerDocument86 pagesIntroduction and Assemblerproject missionNo ratings yet

- 9.1 ConfigurazionerouterDocument3 pages9.1 Configurazioneroutermigliorelli.davidNo ratings yet

- Hardware Implementation of AES Encryption and Decryption System Based On FPGADocument5 pagesHardware Implementation of AES Encryption and Decryption System Based On FPGAاليزيد بن توهاميNo ratings yet

- Cryptography - Quick Guide-Pages-26-41,46-51,55-60Document28 pagesCryptography - Quick Guide-Pages-26-41,46-51,55-60My HackNo ratings yet

- Data Security: Block Ciphers and The Data Encryption StandardDocument12 pagesData Security: Block Ciphers and The Data Encryption Standardapi-19822376No ratings yet

- BSidesNairobi2022 MichaelKangetheDocument27 pagesBSidesNairobi2022 MichaelKangetheMarkus DempfleNo ratings yet

- Huawei HG630 QSGDocument18 pagesHuawei HG630 QSGAmer EzahirNo ratings yet

- Bank Global Access System (Java)Document47 pagesBank Global Access System (Java)Pranay KumarNo ratings yet

- HCIA-Cloud Service Lab Guide V1.0Document158 pagesHCIA-Cloud Service Lab Guide V1.0Pedro CamiloNo ratings yet

- Mecapion Servo Motors 2012Document68 pagesMecapion Servo Motors 2012GianLucaNo ratings yet

- Passwörter ForumDocument6 pagesPasswörter ForumAh MedNo ratings yet

- Interview Transcript - David DanksDocument11 pagesInterview Transcript - David DanksJoon JangNo ratings yet

- Andhra University 20.8.10Document6 pagesAndhra University 20.8.10Ramesh NutakkiNo ratings yet

- Auto Cad Civil 3 D ManualDocument23 pagesAuto Cad Civil 3 D ManualTofanKurniawanNo ratings yet

- Ebook - Allan Mckay - VFX Hardware Guide - Jan 2019 PDFDocument29 pagesEbook - Allan Mckay - VFX Hardware Guide - Jan 2019 PDFSundeep ParmarNo ratings yet

- DSE9474 DSE9484 Data Sheet PDFDocument2 pagesDSE9474 DSE9484 Data Sheet PDFAung MhNo ratings yet

- Spectra System PumpsDocument2 pagesSpectra System PumpsAna JurkeviciuteNo ratings yet

- Catalog Altivar Process ATV600 Variable Speed DrivesDocument133 pagesCatalog Altivar Process ATV600 Variable Speed Drivesrabia akramNo ratings yet

- Ecd Lab Report 3Document6 pagesEcd Lab Report 3Saqib AliNo ratings yet

- Converting To SAP S/4HANA: Custom Code MigrationDocument15 pagesConverting To SAP S/4HANA: Custom Code MigrationKevin AndersonNo ratings yet

- Upload - NMBDocument15 pagesUpload - NMBTHANIGAINATHAN.G.D 10A3No ratings yet

- Seminar On: Hadoop TechnologyDocument13 pagesSeminar On: Hadoop TechnologySAV SportsNo ratings yet

- Circle Office: Divisional Office:: Southern Lahore Circle Gulberg DivisionDocument1 pageCircle Office: Divisional Office:: Southern Lahore Circle Gulberg DivisionWilliam KentNo ratings yet

- 06-E-SAT Including Data Management and Use of ResultsDocument53 pages06-E-SAT Including Data Management and Use of ResultsRgen Al VillNo ratings yet

- EIS SM Booster Antim Prahar Charts 2022 23Document94 pagesEIS SM Booster Antim Prahar Charts 2022 23Vinamra GuptaNo ratings yet

- ONDULEUR APC Easy UPS 3S 1-10 KVADocument7 pagesONDULEUR APC Easy UPS 3S 1-10 KVAouattara yaya katiaNo ratings yet

- Form 2 March 2020 Break Computer Studies AssignmentDocument16 pagesForm 2 March 2020 Break Computer Studies AssignmentKarari WahogoNo ratings yet

- HMMERDocument5 pagesHMMERemma698No ratings yet

- Military Briefing W3S0005 Student HandoutDocument14 pagesMilitary Briefing W3S0005 Student HandoutorcaNo ratings yet

- Discussion Assignment 5Document5 pagesDiscussion Assignment 5Nothando MkhwanaziNo ratings yet

- FortiGate I Student Guide-Online V2Document556 pagesFortiGate I Student Guide-Online V2GuillermoNo ratings yet

- Test Class MethodsDocument7 pagesTest Class Methodsvarun.chintatiNo ratings yet

- TRADOC Pamphlet 525-92-1Document38 pagesTRADOC Pamphlet 525-92-1Ricardo Alfredo Martinez CambaNo ratings yet