Professional Documents

Culture Documents

Cse Co

Uploaded by

Sowmya KoneruOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cse Co

Uploaded by

Sowmya KoneruCopyright:

Available Formats

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY: KAKINADA M.

Tech I Semester Regular Examinations, February/March 2009 COMPUTER ORGANISATION (Computer Science & Engineering-Common to CSE & NN) Time: 3 Hours Answer any FIVE questions Max Marks: 60

1.

(a) Explain with an example how Gray code number is converted into Binary code equivalent. (b) Describe Booths algorithm for division of two signed binary numbers. (c) Show that the exclusive OR function X = A + B + C + D is an odd function.

2.

(a) Design a 4-bit combinational circuit decremented using four adder circuits. (b) A two word instructions is stored in memory at an address designated by the symbol W. The address field of the instruction, stored at W+1, is designated by Y. The operand used during the execution of the instructions is stored at an address symbolized by Z. An index register contains the value X. State how Z is calculated from the other addresses of the addressing mode of the instruction is (a) Direct (b) indirect (c) relative (d) indexed

3.

(a) Explain the difference between hardwired control and micro programmed control? Give their relative merits and demerits. (b) Describe the conditional branching capability in a micro programmed control unit.

4.

(a) Why should a user program be partitioned? Describe the advantages and disadvantages of Partitioning. (b) Describe some of the importance metrics and measures of performances evaluation of computers (c) Give two applications of parallel processing.

5.

(a) Describe SET associative mapping technique for cache memory (b) What is memory interleaving? Describe with suitable diagram, higher-Order and lower-order inter leaving.

6.

(a) Design parallel priority interrupt hardware for a system with 4 interrupt sources. (b) Describe asynchronous data transfer schemes using suitable diagrams

7.

(a) Derive the equation for speed up of a K stage linear pipeline for performing N task (b) How Branch instructions are handled in Pipeline system (c) Describe a RISC Pipeline

(a) Give the architecture of a multi processor system (b) Give SIMD Computer model. (c) Describe latency hiding Technique.

You might also like

- Exceptional HandlingDocument53 pagesExceptional HandlingSowmya KoneruNo ratings yet

- Java OOPs, Exception Handling, Collections, AWT & Swing QuestionsDocument12 pagesJava OOPs, Exception Handling, Collections, AWT & Swing QuestionsDebashis SarkarNo ratings yet

- Ee107 (Anu)Document2 pagesEe107 (Anu)Sowmya KoneruNo ratings yet

- Analysis of SortingDocument3 pagesAnalysis of SortingSowmya KoneruNo ratings yet

- Model Selection Using Correlation in Comparison With Qq-PlotDocument5 pagesModel Selection Using Correlation in Comparison With Qq-PlotSowmya KoneruNo ratings yet

- Write Pattern SpiralDocument1 pageWrite Pattern SpiralSowmya KoneruNo ratings yet

- Abbas Ali MohammadDocument2 pagesAbbas Ali MohammadSowmya KoneruNo ratings yet

- DAA Content Preparation FormatDocument2 pagesDAA Content Preparation FormatSowmya KoneruNo ratings yet

- Analysis of SortingDocument3 pagesAnalysis of SortingSowmya KoneruNo ratings yet

- Analysis of SortingDocument3 pagesAnalysis of SortingSowmya KoneruNo ratings yet

- Mastering The Industrial Internet of Things (Iiot)Document16 pagesMastering The Industrial Internet of Things (Iiot)Sowmya KoneruNo ratings yet

- Model Selection Using Correlation in Comparison With Qq-PlotDocument5 pagesModel Selection Using Correlation in Comparison With Qq-PlotSowmya KoneruNo ratings yet

- Infosys Interview QuestionsDocument77 pagesInfosys Interview QuestionsSowmya KoneruNo ratings yet

- CoDocument11 pagesCoSowmya KoneruNo ratings yet

- Cse & ItDocument192 pagesCse & ItPawan Kumar Pulivarthi100% (1)

- Model Selection Using Correlation in Comparison With Qq-PlotDocument5 pagesModel Selection Using Correlation in Comparison With Qq-PlotSowmya KoneruNo ratings yet

- Jntuk CN Unit ViDocument13 pagesJntuk CN Unit ViSowmya KoneruNo ratings yet

- Model Selection Using Correlation in Comparison With Qq-PlotDocument5 pagesModel Selection Using Correlation in Comparison With Qq-PlotSowmya KoneruNo ratings yet

- III CN Unit Wise QuestionsDocument3 pagesIII CN Unit Wise QuestionsSowmya KoneruNo ratings yet

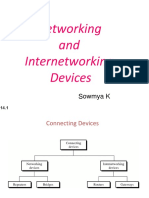

- Connecting Devices Backbone Networks Virtual Lans: Unit - 5Document38 pagesConnecting Devices Backbone Networks Virtual Lans: Unit - 5Sowmya KoneruNo ratings yet

- JNTUK R13 CN UNIT V Part ADocument51 pagesJNTUK R13 CN UNIT V Part ASowmya KoneruNo ratings yet

- Jntuk CN Unit ViDocument13 pagesJntuk CN Unit ViSowmya KoneruNo ratings yet

- JNTUK CN R13 UNIT V Notes (Extra)Document19 pagesJNTUK CN R13 UNIT V Notes (Extra)Sowmya KoneruNo ratings yet

- 8156859Document30 pages8156859Sowmya KoneruNo ratings yet

- CN&NP LAB Manual R13 RegulationDocument82 pagesCN&NP LAB Manual R13 RegulationSowmya KoneruNo ratings yet

- UNIT-2-part 1-Multiplexing PDFDocument45 pagesUNIT-2-part 1-Multiplexing PDFSowmya KoneruNo ratings yet

- States & CapitalsDocument1 pageStates & CapitalsSowmya KoneruNo ratings yet

- 08 VirtualMemoryDocument65 pages08 VirtualMemorySowmya KoneruNo ratings yet

- Information TechnologyDocument5 pagesInformation TechnologySowmya KoneruNo ratings yet

- JNTUK R16 II-I DLD UNIT I NotesDocument30 pagesJNTUK R16 II-I DLD UNIT I NotesSowmya Koneru100% (1)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)