Professional Documents

Culture Documents

GR 8284

Uploaded by

Jorge RodriguezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

GR 8284

Uploaded by

Jorge RodriguezCopyright:

Available Formats

AGPS-2006

8284A Generador de Reloj

El 8284 se encarga de proporcionarle al microprocesador los pulsos de reloj adecuados. Tambin enva la seal adecuada de inicializacin (RESET).

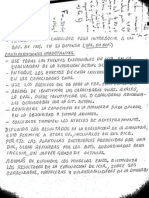

_________ _________ _| \__/ |_ |_|1 18|_| _| |_ |_|2 17|_| _| |_ |_|3 8284 A 16|_| _| |_ |_|4 15|_| _| |_ |_|5 14|_| _| |_ |_|6 13|_| _| |_ |_|7 12|_| _| |_ |_|8 11|_| _| |_ |_|9 10|_| |______________________|

CSYNC PCLK AEN1 RDY1 READY RDY2 AEN2 CLK GND

VCC X1 X2 ASYNC EFI F/C OSC RES RESET

Figura 1. Configuracin del 8284A

Descripcin de las terminales del 8284 para el modo mnimo del 8088.

X1 y X2 son las entradas del cristal, el cual no tiene polaridad. La frecuencia se divide entre 3, con la caracterstica que es de 33% en alto y 66% en bajo, la cual se obtiene en la salida CLK. La seal CLK es dividida entre 2 y se enva por la salida PCLK (reloj perifrico) EFI (external frecuency in) es la entrada de reloj si se usa oscilador u otra seal de frecuencia externa. La terminal F/C determina cul es la seal de origen, si sta est en 1, el origen es la seal EFI, si no, ser la obtenida en X1 y X2 (cristal). OSC es una seal de salida donde se obtiene la frecuencia del cristal en una sola terminal. RES es una lnea de entrada para el disparo de la seal de RESET. Aqu se conecta un arreglo de capacitor-resistencia con un botn de disparo normalmente abierto (push button).

1/2

AGPS-2006

RESET es la seal de inicializacin que se enva al microprocesador. READY se conecta directamente a la seal READY del 8088. AEN1 y AEN2 se utilizan para sistemas de varios procesadores, cuando se utiliza slo uno, estas entradas se colocan en tierra (GND). ASYNC sirve para sincronizar la salida READY y compensa los tiempos de respuesta de los dispositivos conectados al bus. En el modo mnimo esta seal se deja al aire. CSYNC se utiliza cuando existen mltiples 8284 conectados a un sistema y para esto se utiliza un reloj maestro. En el modo mnimo se conecta a GND.

2/2

You might also like

- Arduino. Guía práctica de fundamentos y simulación: RobóticaFrom EverandArduino. Guía práctica de fundamentos y simulación: RobóticaRating: 4.5 out of 5 stars4.5/5 (5)

- Comprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109From EverandComprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109No ratings yet

- Control neuronal y difuso para sistemas fotovoltaicosFrom EverandControl neuronal y difuso para sistemas fotovoltaicosNo ratings yet

- Compilador C CCS y Simulador Proteus para Microcontroladores PICFrom EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICRating: 2.5 out of 5 stars2.5/5 (5)

- Puesta en marcha de sistemas de automatización industrial. ELEM0311From EverandPuesta en marcha de sistemas de automatización industrial. ELEM0311Rating: 3 out of 5 stars3/5 (1)

- 06 ANEXO B - Estándar de Señales de SCADA Mínimas Requeridas Por CENACEDocument32 pages06 ANEXO B - Estándar de Señales de SCADA Mínimas Requeridas Por CENACERaul Montoya100% (3)

- Como Automatizar Timbre EscolarDocument8 pagesComo Automatizar Timbre EscolarEnya Andrea Ribba Hernandez0% (1)

- KNX. Domótica e Inmótica: Guía Práctica para el instaladorFrom EverandKNX. Domótica e Inmótica: Guía Práctica para el instaladorRating: 5 out of 5 stars5/5 (1)

- 8284 Clock GeneratorDocument4 pages8284 Clock GeneratorKennyi Aro ApazaNo ratings yet

- Medidor de VoltajeDocument15 pagesMedidor de VoltajeDAVID ALEJANDRO BURBANO USBANONo ratings yet

- Ejercicios Actividad 9 1 Arrays TolentinoMendozaDocument8 pagesEjercicios Actividad 9 1 Arrays TolentinoMendozaTole MendozaNo ratings yet

- Atsam4s AdcDocument6 pagesAtsam4s AdcBlack SwanNo ratings yet

- Ejercicios Dispositivos de ControlDocument7 pagesEjercicios Dispositivos de ControlArmando BalcheNo ratings yet

- Ejercicios Dispositivos 1Document7 pagesEjercicios Dispositivos 1Armando BalcheNo ratings yet

- PIC16F87XDocument11 pagesPIC16F87XfelitaNo ratings yet

- Sensor de TemperaturaDocument17 pagesSensor de TemperaturaJorge ArreguinNo ratings yet

- ArrutiSanchez 3CM14 P13Document7 pagesArrutiSanchez 3CM14 P13Miranda Pardo AngelNo ratings yet

- Laboratorio 3Document8 pagesLaboratorio 3Carlos MoreNo ratings yet

- Micro PIC16F87Document13 pagesMicro PIC16F87android x xxxNo ratings yet

- Tutorial Sensor de Humedad y Temperatura en LCD Con Atmega32Document16 pagesTutorial Sensor de Humedad y Temperatura en LCD Con Atmega32Medina Adame Denis0% (1)

- Conversor AD Del dsPIC30F4013 PDFDocument13 pagesConversor AD Del dsPIC30F4013 PDFdaviquito1No ratings yet

- Programación C ADCDocument3 pagesProgramación C ADCAl Bajad MamadNo ratings yet

- Reloj Digital Visualizaado Con DisplayDocument14 pagesReloj Digital Visualizaado Con DisplayIruy MartinezNo ratings yet

- Prac 6Document15 pagesPrac 6Jose Guillermo RodilesNo ratings yet

- Proyectos ElectronicosDocument15 pagesProyectos ElectronicosEdwin RegisNo ratings yet

- Unidad IiiDocument7 pagesUnidad IiiJuli CastilloNo ratings yet

- Tutorial Pickit2 v2.6Document19 pagesTutorial Pickit2 v2.6Daɳɳy ElSamNo ratings yet

- Contador de Revoluciones Digital Antiguo para DieselDocument3 pagesContador de Revoluciones Digital Antiguo para Dieseldarkking00No ratings yet

- Compus FinalDocument8 pagesCompus FinalPedro JerexNo ratings yet

- Bosmediano Carlos Ciercom Digitales Memoria Rom DiodosDocument12 pagesBosmediano Carlos Ciercom Digitales Memoria Rom DiodosLito' BosmedianoNo ratings yet

- 4-001contador ProgramableDocument11 pages4-001contador ProgramableDiego LaviniNo ratings yet

- Informe Sumador y RestadorDocument5 pagesInforme Sumador y RestadorWalter Ernest Muñoz MedinaNo ratings yet

- 11N LABEP2014-II Info PDFDocument26 pages11N LABEP2014-II Info PDFRubenPerezNo ratings yet

- LCD Mas Pic16f877Document17 pagesLCD Mas Pic16f877freimarNo ratings yet

- Timer 555 DisplayDocument9 pagesTimer 555 DisplayMar SusoNo ratings yet

- Taco MetroDocument25 pagesTaco MetrofernndaNo ratings yet

- Lab Nº8 MicrocontroladoresDocument17 pagesLab Nº8 MicrocontroladoresJoseph Segura CarvalloNo ratings yet

- LPCOpen LPC13xx ADCDocument5 pagesLPCOpen LPC13xx ADCyenhy angelNo ratings yet

- Convertidor Analógico Digital DSP TMS320F28335Document2 pagesConvertidor Analógico Digital DSP TMS320F28335David Fernández VillanuevaNo ratings yet

- Laboratorio 5 MicroDocument14 pagesLaboratorio 5 MicrohhenrirNo ratings yet

- Introducción Al NODE MCUDocument14 pagesIntroducción Al NODE MCUArturo72No ratings yet

- Manejo Del LCDDocument4 pagesManejo Del LCDfer6669993No ratings yet

- Labview y PicDocument0 pagesLabview y Picgjimenezt077292No ratings yet

- Examen No3 (Práctico)Document8 pagesExamen No3 (Práctico)Jaime JdNo ratings yet

- Ejemplo Termostato ARDUINODocument6 pagesEjemplo Termostato ARDUINOfabrizzioNo ratings yet

- PID AnalogicoDocument47 pagesPID AnalogicoEfra Efra ParraNo ratings yet

- Paper1 - Manejo Del ADCON2Document5 pagesPaper1 - Manejo Del ADCON2Juan Camilo QuicenoNo ratings yet

- RTC DS1307 Con PBPDocument8 pagesRTC DS1307 Con PBPalvaldez035981100% (1)

- Solis Aneliz Lab3Document6 pagesSolis Aneliz Lab3Adalberto MoralesNo ratings yet

- Cardio CidDocument57 pagesCardio Cidmaurojas100% (1)

- Cardiocid BBDocument57 pagesCardiocid BBmaurojas100% (7)

- Comparativo de Circuitos DigitalesDocument15 pagesComparativo de Circuitos DigitalesJose Ignacio Gonzalez LopezNo ratings yet

- Practica 2 - ADCDocument6 pagesPractica 2 - ADCDanielNo ratings yet

- PDF Control de Velocidad de Un Motor DC Con Pic - CompressDocument15 pagesPDF Control de Velocidad de Un Motor DC Con Pic - CompressJonathan Jimenez JardonNo ratings yet

- Informe Electronica ProgrambleDocument14 pagesInforme Electronica ProgrambleJorge RecabalNo ratings yet

- 4-002-Temporizador Program Able Horas-Minutos y SegundosDocument6 pages4-002-Temporizador Program Able Horas-Minutos y SegundosNelson Munoz PadillaNo ratings yet

- Librería UART de MikroC PRO para El Módulo USARTDocument4 pagesLibrería UART de MikroC PRO para El Módulo USARTYuki Rito100% (1)

- Arquitectura At89c52Document53 pagesArquitectura At89c52ernesto100% (3)