Professional Documents

Culture Documents

Usando El Puerto Paralelo de Una PC

Uploaded by

Johanny PérezCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Usando El Puerto Paralelo de Una PC

Uploaded by

Johanny PérezCopyright:

Available Formats

Usando el puerto paralelo de una PC

Proyecto: Interfaz para el Puerto Paralelo Fecha: 3 de Setiembre de 2000 Introduccin: El puerto paralelo de una PC es ideal para ser usado como herramienta de control de motores, rels, LED's, etc. El mismo posee un bus de datos de 8 bits (Pin 2 a 9) y muchas seales de control, algunas de salida y otras de entrada que tambin pueden ser usadas fcilmente. Las PC's generalmente poseen solo uno de estos puertos (LPT1) pero con muy poco dinero se le puede adicionar una tarjeta con un segundo puerto paralelo (LPT2). En reglas generales la direccin hexadecimal del puerto LPT1 es igual a 0x378 (888 en decimal) y 0x278 (632 en decimal) para el LPT2. Esto se puede verificar fcilmente en el setup de la PC o bien en el cartel que generalmente la PC muestra en el momento del booteo. Puede darse el caso que el LPT1 asuma la direccin 0x3BC (956 en decimal) y el LPT2 0x378, en ese caso habr que tratar de corregir el setup y/o los jumper de las tarjetas en caso que sea posible. De lo contrario se puede modificar el software que veremos mas adelante para aceptar esas direcciones.

Breve descripcin del puerto paralelo: El puerto paralelo de un PC posee un conector de salida del tipo DB25 hembra cuyo diagrama y seales utilizadas podemos ver en la siguiente figura:

Si deseamos escribir un dato en el bus de salida de datos (pin 2 a 9) solo debemos escribir el byte correspondiente en la direccin hexadecimal 0X378 (888 en decimal) cuando trabajamos con el LPT1 y 0x278 (632 en decimal) cuando trabajamos con el LPT2. Los distintos pins (bits) de salida correspondientes al bus de datos no pueden ser escritos en forma independiente, por lo que siempre que se desee modificar uno se debern escribir los ocho bits nuevamente. Para leer el estado de los pins de entrada (10, 12, 13 y 15) se debe realizar una lectura a la direccin hexadecimal 0x379 (889 en decimal) si trabajamos con el LPT1 o bien leer la direccin

0x279 (633 en decimal) si trabajamos con el LPT2. La lectura ser devuelta en un byte en donde el bit 6 corresponde al pin 10, el bit 5 corresponde al pin 12, el bit 4 corresponde al pin 13 y el bit 3 corresponde al pin 15. En la siguiente tabla se puede ver lo antedicho en una forma ms grfica: Escritura: Salida de Datos Escritura en direccin 0x378 (LPT1) o 0x278 (LPT2) DATO DB25 CN5 CN4 BIT 7 Pin 9 TTL 7 No usar BIT 6 Pin 8 TTL 6 HP 6 BIT 5 Pin 7 TTL 5 HP 5 BIT 4 Pin 6 TTL 4 HP 4 BIT 3 Pin 5 TTL 3 HP 3 BIT 2 Pin 4 TTL 2 HP 2 BIT 1 Pin 3 TTL 1 HP 1 BIT 0 Pin2 TTL 0 HP 0

Lectura: Entrada de Datos Lectura en direccin 0x379 (LPT1) o 0x279 (LPT2) DATO DB 25 CN6 BIT 7 No usar No usar BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 No usar No usar BIT 1 No usar No usar BIT 0 No usar No usar

Pin 10 Pin 12 Pin 13 Pin 15 Input 3 Input 2 Input 1 Input 0

Interfaz: En la archivo IPP01-CIRCUIT.PDF podemos apreciar el circuito correspondiente a la interfaz para el puerto paralelo. La interfaz nos provee 8 salidas TTL, 7 salidas de potencia (500ma) y cuatro entradas TTL. Es importante tener en cuenta que las salidas TTL entregan una tensin de 5v y solo se les puede exigir un mnimo de corriente, apenas suficiente para activar un transistor o bien un par de compuertas TTL. As mismo las entradas TTL deben ser alimentadas con una tensin mxima de 5v o de lo contrario el chip resultar daado. Esta tensin se obtiene desde VDD a travs del regulador U1 (7805). Las 7 salidas de potencia no son mas que la amplificacin mediante un array de transistores Darlington (ULN2003) de las salidas TTL 0 a 6 (la salida 7 no es usada). Este chip puede drenar una corriente mxima de 500ma, lo que es suficiente para activar un LED, un rel y hasta un motor DC de bajo consumo (tipo motor de grabador). La teora de funcionamiento es muy simple, solo se usan unas compuertas del tipo Buffer (74HC245) para poder conectarnos con seguridad al puerto paralelo, y un array de transistores Darlington (ULN2003) para brindar una salida de mayor potencia. Cabe aclarar que los dos integrados 74HC245 se alimentan del regulador de voltaje 7805, el cual se encarga de reducir la tensin de entrada (VDD) a 5v (Vcc). La tensin VDD debe estar comprendida entre 9 y 12v.

La tensin de entrada VHH alimenta directamente al ULN2003 para obtener mayor voltaje en caso de querer manejar un rel o bien un pequeo motor. La tensin VHH debe estar comprendida entre 3 y 15v. VHH podr conectarse directamente a VDD (y de esa forma usar solo un fuente de alimentacin) siempre que esto no provoque problemas de ruido. En los siguientes diagramas se pueden apreciar un ejemplo de conexionado de un LED y un Rel a las salidas de potencia. En forma anloga podramos conectar tambin un pequeo motor DC.

para interfaz:

Programa manejo de la

El siguiente es un programa hecho en Qbasic en donde se puede apreciar como se debe trabajar con el puerto paralelo y como se puede sacar provecho de la interfaz. Para visualizarlo o bajarlo a la PC haga click aqu. Tambin puede bajar el ejecutable (.exe) directamente si as lo desea haciendo click aqu. El funcionamiento de este software es muy simple y bsico. Primero le solicitar que elija el puerto a usar (LPT1 o LPT2). Luego puede elegir "Leer Port" para recuperar el estado de los pins de entrada (0 a 3) o bien "Escribir Port" para cambiar el estado de los pins de salida (0 a 7). Recuerde que si cambiamos el pin de salida 0 , tambin se altera el mismo pin en la salida de potencia (solo pins 0 a 6, el 7 no tiene salida de potencia). Mediante el anlisis de este programa Basic se puede intentar hacer programas mas elaborados en lenguajes ms modernos.

Introduccin Hace aos, IBM dise el puerto paralelo para manejar impresoras desde su gama de microcomputadores PC/XT/AT. Un conector estndar macho de 25 pines apareca en la parte trasera del PC con el solo propsito de servir de interfaz con la impresora. El sistema operativo DOS cargado en dichos PC soporta hasta tres puertos paralelos asignados a los identificadores LPT1, LPT2 y LPT3, y cada puerto requiere tres direcciones consecutivas del espacio de E/S (entrada-salida) del procesador para seleccionar todas sus posibilidades. Desde el punto de vista del hardware, el puerto consta de un conector hembra DB25 con doce salidas latch (poseen memoria/buffer intermedio) y cinco entradas, con ocho lneas de tierra. Desde el punto de vista del software, el puerto paralelo consta de tres registros (datos, estado y control) de 8 bits cada uno, que ocupan tres direcciones de E/S (I/O) consecutivas de la arquitectura x86.

La funcin normal del puerto consiste en transferir datos a una impresora mediante 8 lneas de salida de datos, usando las seales restantes como control de flujo. Sin embrago, puede ser usado como un puerto E/S de propsito general por cualquier dispositivo o aplicacin que se ajuste a sus posibilidades de entrada/salida.

Descripcin del conector fsico La conexin del puerto paralelo al mundo exterior se realiza mediante un conector hembra DB25. Observando el conector de frente y con la parte que tiene mayor nmero de pines hacia arriba, se numera de derecha a izquierda y de arriba a abajo, del 1 al 13 (arriba) y del 14 al 25 (abajo).

En este conector: 8 lneas (pines) son para salida de datos (bits de DATOS). Sus valores son nicamente modificables a travs de software, y van del pin 2 (dato 0, D0) al pin 9 (dato 7, D7). 5 lneas son de entrada de datos (bits de ESTADO), nicamente modificables a travs del hardware externo. Estos pines son: 11, 10, 12, 13 y 15, del ms al menos significativo. 4 lneas son de control (bits de CONTROL), numerados del ms significativo al menos: 17, 16, 14 y 1. Habitualmente son salidas, aunque se pueden utilizar tambin como entradas y, por tanto, se pueden modificar tanto por software como por hardware. las lneas de la 18 a la 25 son la tierra.

En la siguiente tabla se detallan la nomenclatura y descripcin de cada lnea. La columna "Centronics pin" se refiere a las lneas del conector tipo Centronics usado en las impresoras. La columna E/S se refiere al dato visto desde el lado del PC. DB25 Centronics Tipo pin pin (E/S) 1 2 3 4 5 6 1 2 3 4 5 6 S S S S S S Seal Strobe D0 D1 D2 D3 D4 Descripcin Si est bajo ms de 0.5 s, habilita a la impresora para que reciba los datos enviados. Bit 0 de datos, bit menos significativo (LSB) Bit 1 de datos Bit 2 de datos Bit 3 de datos Bit 4 de datos

7 8 9 10 11 12 13 14 15 16 17 18-25 18-25 18-25

7 8 9 10 11 12 13 14 32 31 36 19-30,33 16 17

S S S E E E E S E S S

D5 D6 D7 Ack Busy

Bit 5 de datos Bit 6 de datos Bit 7 de datos, bit ms significativo (MSB) Un pulso bajo de ~11s indica que se han recibido datos en la impresora y que la misma est preparada para recibir ms datos. En alto indica que la impresora est ocupada.

PaperEnd En alto indica que no hay papel. SelectIn En alto para impresora seleccionada. AutoFeed Error Init Select GND Si est bajo, el papel se mueve una lnea tras la impresin. En bajo indica error (no hay papel, est fuera de lnea, error no det.). Si se enva un pulso en bajo > 50 s la impresora se reinicia. En bajo selecciona impresora (en gral. no se usa, ya que SelectIn se fija a alto). Masa retorno del par trenzado. Masa lgica Masa chasis

El nombre de cada seal corresponde a la misin que cumple cada lnea con relacin a la impresora, el perifrico para el que fue diseado el puerto paralelo. Las seales activas a nivel bajo aparecen con la barra de negacin (por ejemplo, Strobe). Cuando se indica alto o bajo se refiere a la tensin en el pin del conector. Alto equivale a ~5V en TTL y bajo a ~0V en TTL.

Acceso al puerto

El puerto paralelo se identifica por su direccin de E/S (entrada/salida, I/O) base y se reconoce en sistemas MS-DOS por el nmero LPT (lp en Unix/Linux). Cuando arranca la mquina, la BIOS (Basic Input Output System) chequea direcciones especficas de E/S en busca de puertos paralelos y construye una tabla de las direcciones halladas en la posicin de memoria 40h:8h (o 0h:0408h) (vase direccionamiento segmentado). Esta tabla contiene hasta tres palabras de 16 bits, cada palabra con el byte bajo primero seguido por el byte alto. Cada palabra es la direccin de E/S base del puerto paralelo (que denominaremos LPT_BASE en lo sucesivo). La primera corresponde a LPT1, la segunda a LPT2 y la tercera a LPT3. Hay que agregar que, en MS-DOS tenemos el dispositivo PRN que es un alias a uno de los dispositivos LPT (generalmente es LPT1, pero se puede cambiar con la orden MODE). Las direcciones base estndar para los puertos paralelos son: 03BCh 0378h 0278h

chequeadas en este orden. La siguiente tabla muestra, como ejemplo, la memoria en un PC con dos puertos paralelo instalados en las direcciones hexadecimales 378 y 278.

Identificador DOS LPT1 LPT2 LPT3 (no instalado) Registros

Direccin 0000:0408/9 0000:040A/B 0000:040C/D

Byte bajo 78 78 00

Byte Hexadecimal Decimal alto 03 02 00 378 278 0 888 632 0

El puerto paralelo estndar (SPP) consta, como se mencion antes, de tres registros de 8 bits localizados en direcciones adyacentes del espacio de E/S del PC. Los registros se definen relativos a la direccin de E/S base (LPT_BASE) y son: LPT_BASE + 0: registro de DATOS LPT_BASE + 1: registro de ESTADO LPT_BASE + 2: registro de CONTROL

REGISTROS DATOS ESTADO Puerto DIRECCIN E/S Puerto Puerto 378h 278h 3BCh 379h 279h 3BDh CONTROL 37Ah 27Ah 3BEh

Nombre habitual LPT1 LPT2 MDA con p. paralelo

Se har referencia a cada bit de los registros como una inicial que identifica el registro seguido de un nmero que identifica el nmero de bit, siendo 0 el LSB (bit menos significativo) y 7 el MSB (bit ms significativo). Por ejemplo, D0 es el bit 0 del reg. de datos, S7 es el bit 7 del reg. de estado y C2 es el bit 2 del reg. de control. Se indican con una barra de negacin los bits que utilizan lgica negativa. En lgica positiva un 1 lgico equivale a alto (~5 V TTL) y un 0 lgico a bajo (~0 V TTL). En lgica negativa 1 equivale a bajo (~0 V) y 0 equivale a alto (~5 V).

Es preciso no confundir la lgica que sigue el puerto con la lgica que mantiene la impresora. Por ejemplo, la impresora pone a alto Busy (pin 11) para indicar que est ocupada. Pero en realidad, al leer el registro de estado, Busy la interpretamos como 0 (puesto que el pin 11 se corresponde con S7). Es decir, es como si fuera activa en bajo (Busy).

Registro de datos (D)

El registro de estado se halla en LPT_BASE. Se puede leer y escribir. Escribir un dato en el registro causa que dicho dato aparezca en los pines 2 a 9 del conector del puerto. Al leer el registro, se lee el ltimo dato escrito (NO lee el estado de los pines; para ello hay que usar un puerto bidireccional).

El estndar es que las salidas sean LS TTL (low schottky TTL), aunque las hay que son de tipo OC (colector abierto). La corriente que pueden entregar (modo source) es de 2,6 mA mximo y pueden absorber (modo sink) un mximo de 24 mA. n el puerto original de IBM hay condensadores de 2,2 nF a masa. Las tensiones para el nivel bajo son entre 0 y 0,8V y el nivel alto entre 2,4V y 5V. El registro de estado est en LPT_BASE+1. Es de slo lectura (las escrituras sern ignoradas). La lectura da el estado de los cinco pines de entrada al momento de la lectura. En la tabla siguiente los nombres de los pines se dejaron en ingls porque es como generalmente se identifican.

La lnea Busy tiene, generalmente, una resistencia de pull-up interna. El estndar es que sean entradas tipo LS TTL.

El registro de control se encuentra en LPT_BASE+2. Es de lectura/escritura.

Los cuatro bits inferiores son salidas. La lectura devuelve lo ltimo que se escribi a dichos bits. Son TTL a colector abierto con resistencias de pull-up de 4.7 k por lo que un dispositivo , externo puede forzar el estado de los pines sin daar el driver. Esto permite utilizar estas cuatro lneas como entradas. Para ello, se ponen en alto las cuatro salidas (escribiendo 0100b, es decir, 4h, en LPT_BASE+2) lo que hace que las salidas "floten". Ahora, un dispositivo externo puede forzar a bajo alguna de las salidas con lo que, leyendo el puerto, sabemos si esto sucedi o no. Es posible realizar esta tcnica en salidas totem-pole (como D0-D7) pero no se recomienda su uso porque habra que tener un conocimiento preciso de la corriente, ya que se puede sobrecargar los transistores de salida y daar el driver (especialmente en puertos integrados LSI). Bit de puerto bidireccional (compatible PS/2) El bit C5, est disponible slo si se trata de un puerto bidireccional; en los puertos comunes no se utiliza, al igual que los bits C6 y C7. Si C5=1, el buffer de los datos de salida se pone en alta impedancia, "desconectando" dicho buffer de los pines 2 a 9 del conector del puerto (D0 a D7). Si se escribe al registro de datos, se escribe al buffer pero no a la salida. Esto permite que al leer el puerto, se lea el estado de las entradas y no lo que hay en buffer. Cuando C5=0 el puerto retorna al modo salida, su estado por defecto. En las computadoras IBM PS/2, para habilitar el puerto paralelo bidireccional, adems de lo antes descrito, se debe poner a 1 el bit 7 del registro del puerto 102h (opciones de configuracin). En computadoras que no tengan puerto paralelo bidireccional compatible PS/2 hay que modificar uno o ms bits de algn puerto especfico correspondiente al chipset de la placa. A veces se habilita por el Setup o por jumper en la placa del puerto. Bit de interrupcin En trabajos normales de impresin ni el BIOS ni el DOS hacen uso de la interrupcin. El hecho de poseer una lnea de interrupcin que est conectada directamente al PIC (Programmable Interrupt Controller), lo hace muy til para experimentacin en data-loggers por ejemplo. El bit de interrupcin est conectado al control de un buffer de tres estados. Cuando C4=1, se activa el buffer y su entrada, S6, se conecta a la lnea IRQ (en general es IRQ7 o IRQ5). La lectura del bit, nos devuelve el estado del mismo (es decir si el buffer est en alta impedancia o no). Se producir una interrupcin, cuando haya un flanco descendente en el pin correspondiente a S6. A continuacin, se describen los pasos para poder utilizar interrupciones. Finalmente, se muestra una tabla que rene las caractersticas hardware y software del puerto paralelo.

DB25 Centronics Tipo Registro bit Activo pin pin (E/S) 1 1 Control C0 0 DO Dato 0 D1 Dato 1 D2 Dato 2 D3 Dato 3 D4 Dato 4 D5 Dato 5 D6 Dato 6 D7 Dato 7 S bajo

Seal

Descripcin Si est bajo ms de 0.5 s, habilita a la impresora para que reciba los datos enviados. Bit 0 de datos, bit menos significativo (LSB) Bit 1 de datos Bit 2 de datos Bit 3 de datos Bit 4 de datos Bit 5 de datos Bit 6 de datos Bit 7 de datos, bit ms significativo (MSB) Un pulso bajo de ~11s indica que se han recibido datos en la impresora y que la misma est preparada para recibir ms datos. En alto indica que la impresora est ocupada. En alto indica que no hay papel. En alto para impresora seleccionada.

Strobe

2 3 4 5 6 7 8 9

2 3 4 5 6 7 8 9

S S S S S S S S

alto alto alto alto alto alto alto alto

D0 D1 D2 D3 D4 D5 D6 D7

10

10

S6 Estado IRQ 6 Estado 7 Estado 5 Estado 4 Control 1 Estado 3 Control 2

alto

Ack

11 12 13 14

11 12 13 14

S7 S5 S4 C1

E E E S

bajo alto alto bajo

Busy PaperEnd SelectIn

Si est bajo, el papel se AutoFeed mueve una lnea tras la impresin. Error En bajo indica error (no hay papel, est fuera de lnea, error no det.). Si se enva un pulso en bajo > 50 s la impresora se reinicia. En bajo selecciona impresora (en gral. no se usa, ya que SelectIn se fija a alto). Masa retorno del par trenzado. Masa lgica Masa chasis

15

32

S3

alto

16

31

C2

alto

Init

17

36

Control C3 3

bajo

Select

18-25 18-25 18-25

19-30,33 16 17

GND

Miscelnea

El handshaking ("apretn de manos" o protocolo) es un conjunto de reglas que ambos extremos de un sistema de comunicacin tienen que seguir para que la comunicacin sea correcta. El puerto paralelo, usado con una impresora, transmite datos y transmite/recibe las seales de protocolo. Las principales son Strobe, Ack y Busy. La secuencia a seguir para enviar datos sera: 1. 2. 3. 4. Colocar el byte a enviar en el registro de datos. Verificar que la impresora no est ocupada (Busy = bajo, S7 = 1). Indicarle a la impresora que acepte los datos (Strobe = bajo , C0 = 1, pulso >5us). En ese instante la impresora indica que est ocupada recibiendo los datos (Busy = alto, S7 = 0). Finalmente, la impresora enva un pulso de aceptacin indicando que se recibieron los datos y que se puede volver al paso 1 (Ack = bajo, S6 = 0, pulso de entre 5 y 15 s s segn impresora).

5.

Las otras seales sirven para verificar el estado de la impresora (Error, PaperEnd), para reiniciarla (Init) y para configurarla (AutoFeed, Select). En los nuevos puertos, estas seales adquieren otra funcin, a veces parecida y otras totalmente distintas.

Interrupciones con el puerto paralelo En primer lugar, se debe habilitar el buffer que conecta la lnea ACK con la lnea IRQ. Esto lo hacemos poniendo a 1 el bit 4 del registro de control (LPT_BASE+2). Luego se debe preparar una ISR (Interrupt Service Routine) que atienda la interrupcin recordando enviar la seal EOI (20h) al registro de control del PIC (puerto 20h) al salir de la rutina. La interrupcin software corresponde a la nmero 0Dh para IRQ5 y 0Fh para IRQ7. Finalmente se habilita con 0 la interrupcin IRQ5 (o IRQ7) escribiendo al bit 5 (o 7) del registro de interrupciones del PIC (puerto 21h). Para desinstalar la ISR, se deshabilita la IRQ5 (o IRQ7) escribiendo un 1 al bit 5 (o 7) del registro de interrupciones del PIC (puerto 21h). Luego se hace que C4=0. Velocidad Un puerto paralelo ISA normal toma un ciclo-ISA para leer o escribir. En un sistema cuya velocidad de bus sea 1,3 Mhz, se puede decir que la lectura se puede hacer cada 1 s (idealmente, ya que siempre existen otras instrucciones software, etc; En la prctica pueden ser desde 1.2 s a 2 s). Algunos puertos soportan un modo "turbo" que elimina los 3 estados de espera de la CPU, con lo que la velocidad de lectura/escritura del puerto se duplica (2,7 MHz).

Envio y lectura de datos del puerto

Envo de datos al puerto El puerto paralelo puede ser usado como una comunicacin directa con el PC, de este modo es posible desarrollar aplicaciones en tiempo-real que necesiten un rpido tiempo de respuesta. El acceso se realiza escribiendo un byte (8 bits) en registro determinado. Este byte debe referirse a cada uno de los bits del registro. Esto significa que se debe definir el byte a escribir en sistema binario. Por ejemplo si queremos escribir en el registro de datos el bit D0 y el bit D2 entonces el byte es:

0 D7

0 D6

0 D5

0 D4

0 D3

1 D2

0 D1

1 D0

= 5 En decimal Registro de datos

Luego, se debe escribir 5 en el registro de datos (direccin base): Notas: dir_base y dir_estado es de tipo word, y dato es de tipo byte. En Turbo Pascal Port[dir_base]:=5; En C Outportb(dir_base, 5); En ensamblador mov dx, dir_base {Direccionar en dx la direccin base} mov al, 5 {Colocar en al el nmero 5} out dx, al {Enviar al puerto}

Lectura de datos del puerto La lectura de datos se realiza accesando un byte del registro determinado. Al hacer la lectura se debe convertir el byte a binario para determinar l o los bits que interesen. Note que slo se debe leer el registro de estado, o sea, la direccin base+1. En Turbo Pascal Var dato: byte; dato:=Port[dir_estado];

En C unsigned int dato; dato=inportb(dir_estado); En ensamblador mov dx, dir_estado {Direccionar dx con el registro de estado del puerto} in al, dx {Leer del puerto. En el registro al est el dato ledo}

Por ejemplo, si el dato ledo es igual a 96, significa que los bits S5 y S6 estn activos(tienen un nivel alto, un 1). 0 S7 1 S6 1 S5 0 S4 0 S3 0 S2 0 S1 0 S0 = 96 En decimal Registro de estado

Enmascaramiento Tanto en el envo como recepcin de datos binarios, se realizan operaciones a nivel de bits. Estas operaciones permiten aislar uno ms bits. Este proceso se denomina enmascaramiento. Por ejemplo, para saber si determinado bit que se ha ledo del registro de estado est en un nivel alto (1 lgico) se puede hacer la operacin "Y" lgica (AND) de la lectura con un valor que resulta de elevar 2 a la posicin que ocupa ese bit en el byte, y luego realizar la comparacin. Si el bit que se desea conocer es el bit 5, entonces la operacin es: Masc:=2^5=32 (Byte_leido AND masc) En el caso que el bit 5 est en un nivel alto: Byte_leido 0 S7 1 S6 1 S5 0 S4 0 S3 0 S2 AND 0 0 1 0 0 0 0 0 Mscara = 32 0 S1 0 S0 96 Posicin

Resulta

32= mscara

En el caso que el bit 5 no est en un nivel alto: Byte_leido 0 S7 1 S6 0 S5 1 S4 0 S3 0 S2 AND 0 0 1 0 0 0 0 0 Mscara = 32 0 S1 0 S0 80 Posicin

Resulta 0 0 0 0 0 0 0 0 0 <> mscara

Si el bit 5 es 1, entonces el resultado es 16, o igual a masc. Haciendo la comparacin: Si (Byte_leido AND masc) = masc entonces Inicio /* las acciones a realizar cuando el 4to bit es 1 */ Fin Si el bit 5 es 0, entonces el resultado siempre es 0, lo cual es diferente a masc. En caso que se desee realizar el enmascaramiento de ms de un bit, se realiza la suma los valores. Ej. Mscara para el bit 5 y el 7 Masc= 2^5+2^7=160

Expansin a 8 entradas digitales para el puerto paralelo

Como ya es sabido, el puerto paralelo estndar slo tiene 4 entradas digitales. Algunas aplicaciones pueden necesitar ms de las 4 entradas. En este caso es posible expandir las entradas mediante un sencillo circuito basado en un componente electrnico como el buffer 74LS157 para alimentar los datos en forma de dos nibbles (medio byte, 4 bits) mediante las entradas del registro de estado (4 o 5 lneas) hacia el puerto paralelo. Se puede usar el registro de datos o el registro de control para seleccionar el nibble.

Descripcin del buffer 74LS157

Fig. El buffer 74LS157

Referencias Entradas Salidas

I0a Entrada 0a Qa Salida Qa I0b Entrada 0b Qb Salida Qb I0c Entrada 0c Qc Salida Qc I0d Entrada 0d Qd Salida Qd I1a Entrada 1a I1b Entrada 1b I1c Entrada 1c I1d Entrada 1d

Alimentacin y operacin

S Seleccin de nibble. (Bajo selecciona I0. Alto selecciona I1) -Enable Habilitacin del componente (mantener seal en bajo)

Vcc 5 voltios Gnd Tierra La fuente de 5 voltios para alimentar este circuito se puede obtener directamente de la fuente de poder del PC, o del puerto de juegos (ver fuente de alimentacin).

Modo de operacin

Con el 74LS157 la seleccin se realiza a travs del registro de control o de datos. En la figura que est a continuacin se muestra en caso de que la seleccin sea a travs del registro de control.

Fig. Conexin sugerida del 74LS157

Programacin

El siguiente algoritmo permite leer los ocho bits de la entrada del 74LS157 /* Inicio */ /* Seleccin del primer nibble */ Colocar 0 en el bit C3- para seleccionar el nibble N1 Leer el registro de estado en una variable, por ejemplo d_leido Realizar la operacin d_leido XOR con 128, para corregir el signo de S7Este resultado operar con AND 240, para descargar bits no deseados Desplazar a la derecha 4 bits para colocarlo en el nibble de abajo

Almacenar el resultado de un lado /* Seleccin del segundo nibble */ colocar 1 en el bit C3-, para seleccionar el nibble N2 Leer el registro de estado en una variable, por ejemplo d_leido Realizar la operacin d_leido XOR con 128, para corregir el signo de S7Este resultado operar con AND 240, para descargar bits no deseados Realizar la operacin OR del resultado con el nibble almacenado previamente En el resultado final estn los 8 bits ledos.

Funcionamiento

Explicacin del funcionamiento mediante el BIOS y el MS-DOS

IBM especific direcciones base para el puerto paralelo estndar (dentro del espacio de direccionamiento de Entrada/Salida del 80x86). El adaptador de impresora podra usar la direccin base 3BCh, o ms tarde 378h o 278h. El BIOS (Basic Input Output System) de IBM crea en el momento de arranque o POST (Power On Seft Test) una tabla en el espacio de la memoria principal (RAM) para 4 direcciones base de puerto paralelo de impresora, estos se almacenan como 4 bytes empezando con la direccin de memoria 408h. Durante el arranque, el BIOS comprueba si hay puertos paralelos en las direcciones base 3BCh, 378h, y 278h, en ese orden, y almacena la direccin base de cualesquiera que hayan sido encontrados en posiciones consecutivas de la tabla. Las posiciones que no son usadas pueden estar en 0, o como algunos BIOS lo hacen, le colocan la direccin del primer puerto encontrado. Algunos programas pueden ignorar esta tabla, pero esta es usada por lo menos por el propio BIOS (mediante la INT 17 de E/S de impresora) y por el MS-DOS. El BIOS detecta estos puertos escribiendo AAh al registro de datos (en la direccin de E/S Base + 0), y luego si en el registro de datos se lee AAh. Significa que hay un puerto. Normalmente la asignacin de direcciones es como sigue:

Direccin 3BCh 378h Nombre LPT1 LPT2 Ubicacin Adaptador de impresin primario Adaptador de impresin secundario

Las referencias a cada registro del puerto se realizan de la siguiente forma:

o o o

Base (datos)=base+0 Estado=base+1 Control=base+2

Por ejemplo, si encontramos que la direccin base es 378h, entonces las direcciones del registro de datos, estado y control sern:

o o o

Base (datos)=378h Estado=379h Control=37Ah

Cada una de ellas permite accesar a los siguientes bits (descritos en la tabla general):

o o o

Base (datos)=D0, D1, D2, D3, D4, D5, D6, D7 Estado=S3, S4, S5, S6, S7 Control=C0, C1, C2, C3

******************************************

El Conversor Analgico Digital ADC0804CN y el puerto Paralelo

Si se desea capturar seales analgicas en el orden de los 0 a 5 voltios, es posible utilizar el conversor Analgico / Digital ADC0804CN Para ello se propone el esquema elctrico de un conversor analgico-digital bsico como el de la siguiente figura:

Esquema del interfaz de control de entradas analgicas mediante p. paralelo Dicho circuito se alimenta a +5v y convierte seales analgicas en el intervalo entre 0 y 5v. Como ncleo se utiliza el circuito integrado ADC0804CN, un conversor A/D de 8 bit, barato y habitualmente disponible. Por defecto, el intervalo de entrada est entre 0 y +5V pero, usando una referencia externa y/o elevando la seal Vin- respecto a GND, se puede conseguir un amplio intervalo de niveles de entrada. Trabaja con una frecuencia mxima de 8 kHz, de modo que se puede utilizar incluso con seales de audio de baja calidad. A efectos de prueba, la seal analgica a convertir proviene del potencimetro R2; variando ste se modifica la seal entre 0 y 5 voltios. Dicha seal se introduce en el conversor ADC0804. Una vez convertida, el valor digital es presentado en las lneas D0 a D7 y deber ser ledo a travs del puerto paralelo segn el protocolo explicado a continuacin. Para el correcto funcionamiento de la conversin se debe respetar un protocolo entre el PC y el conversor. Bsicamente es el siguiente:

Peticin de comienzo de conversin: el PC debe enviar esta peticin al ADC. Para ello se activa la seal CS (a nivel bajo) y, dentro del perodo de activacin, se activa la seal WR durante un mnimo de 100 ns. El conversor activar la lnea INTR (la seal es activa a nivel bajo) para indicar que ha terminado la conversin (ver figura siguiente). A partir de ese momento el PC puede leer el dato.

Diagrama de tiempos para el inicio de la conversin

Proceso de lectura: se selecciona el conversor a travs de la lnea CS y se enva un pulso negativo por la lnea RD. Tras unos 200 ns (tACC: tiempo de acceso) el dato est disponible para lectura y se desactiva la seal de lectura.

Diagrama de tiempos para la lectura del dato Los ciclos anteriores se repetirn tantas veces como datos se quieran capturar. Con objeto de simplificar la circuitera y, puesto que se cuenta con un solo ADC, se puede mantener permanentemente la seal CS a nivel bajo conectndola directamente a tierra

You might also like

- Usando El Puerto Paralelo de Una PCDocument5 pagesUsando El Puerto Paralelo de Una PCJuan De RiveraNo ratings yet

- db25Document24 pagesdb25goyoelenNo ratings yet

- El Puerto Paralelo Del PC PDFDocument9 pagesEl Puerto Paralelo Del PC PDFPa SolNo ratings yet

- Usando El Port Paralelo de Una PC Como Medio de ControlDocument4 pagesUsando El Port Paralelo de Una PC Como Medio de Controlmacks_ecNo ratings yet

- Lab 7Document53 pagesLab 7Ern SantosNo ratings yet

- El Puerto ParaleloDocument3 pagesEl Puerto ParaleloRichard MeloNo ratings yet

- Interfaz para Puerto Paralelo LPTDocument8 pagesInterfaz para Puerto Paralelo LPTeduard_perdomo_1No ratings yet

- Usando El Puerto Paralelo de Una PCDocument33 pagesUsando El Puerto Paralelo de Una PCaugustrush2291No ratings yet

- Diseño de sistemas de control por puerto paraleloDocument10 pagesDiseño de sistemas de control por puerto paraleloAntonio MoyaNo ratings yet

- Motor - Paso A Paso LPT1Document27 pagesMotor - Paso A Paso LPT1Saul Perez PerezNo ratings yet

- Electrónica DigitalDocument3 pagesElectrónica DigitalDanny SeaNo ratings yet

- Amplia 8 entradas de línea a placa de sonidoDocument79 pagesAmplia 8 entradas de línea a placa de sonidoFelix RuizNo ratings yet

- Computadoras PablinDocument27 pagesComputadoras PablinJaime Orozco QuiramaNo ratings yet

- Puertos ParalelosDocument10 pagesPuertos ParalelosCésar David HernándezNo ratings yet

- Informen 3 MicroDocument25 pagesInformen 3 MicroMarc Arellano SiancasNo ratings yet

- Manual IRAPC ADCM V2Document92 pagesManual IRAPC ADCM V2Alvaro Jose Mosquera S.No ratings yet

- Puerto ParaleloDocument41 pagesPuerto Paraleloedith02_18No ratings yet

- Descripción Del CircuitoDocument7 pagesDescripción Del CircuitoJavier SarangoNo ratings yet

- El Puerto LPTDocument11 pagesEl Puerto LPTJose Marpartida CaceresNo ratings yet

- Tema 06 - Puerto ParaleloDocument18 pagesTema 06 - Puerto ParaleloOmar Milton Condori PeñaNo ratings yet

- Uso de Puertos para Control ExternoDocument56 pagesUso de Puertos para Control ExternoMarcelo VilcaNo ratings yet

- 2 Instrumentacion Mecatronica Puerto ParaleloDocument8 pages2 Instrumentacion Mecatronica Puerto Paralelosusys_666No ratings yet

- Programar LPTDocument5 pagesProgramar LPTAlfredo CausaNo ratings yet

- Microcomputador Controlado Por Microprocesador 8085Document8 pagesMicrocomputador Controlado Por Microprocesador 8085Felix Menendez AliagaNo ratings yet

- Semaforo Con El Software Netbeans Usando El Puerto ParaleloDocument20 pagesSemaforo Con El Software Netbeans Usando El Puerto ParaleloLuis EnriqueNo ratings yet

- Puerto ParaleloDocument12 pagesPuerto ParaleloSanchez T. MarioNo ratings yet

- Puerto ParaleloDocument6 pagesPuerto ParaleloAndrés A. PavónNo ratings yet

- Tema 4.4 Programación Del Puerto ParaleloDocument6 pagesTema 4.4 Programación Del Puerto ParaleloLuuizPossible IndianaNo ratings yet

- TareaDocument7 pagesTareaHenrySolórzanoMartelNo ratings yet

- In MicrocomputadoraDocument7 pagesIn MicrocomputadoraDiego MeraNo ratings yet

- Proyecto de Programables Control de TemperaturaDocument49 pagesProyecto de Programables Control de TemperaturaCarlos ArriazaNo ratings yet

- LPTWebDocument52 pagesLPTWebAlmonacidNo ratings yet

- Control Del Puerto Paralelo Con Visual Basic 6.0Document7 pagesControl Del Puerto Paralelo Con Visual Basic 6.0Pedro SánchezNo ratings yet

- Manejo de PerifericosDocument135 pagesManejo de PerifericosGabby Michelle OrtizNo ratings yet

- Cajero expendedor de monedasDocument10 pagesCajero expendedor de monedasRocksoft-Toy RamirezNo ratings yet

- Programacion de Entradas y Salidas de Un MicrocontroladorDocument6 pagesProgramacion de Entradas y Salidas de Un MicrocontroladorMiguel Angel AburtoNo ratings yet

- Como Usar Un Puerto de OrdenadorDocument4 pagesComo Usar Un Puerto de OrdenadorDaniel CastroNo ratings yet

- C4 PuertosESParalelos PDFDocument66 pagesC4 PuertosESParalelos PDFMi KelNo ratings yet

- Circuitos DigitalesDocument40 pagesCircuitos DigitalestadekotardeNo ratings yet

- Registros PORT ArduinoDocument4 pagesRegistros PORT ArduinoIvan Andres MuñozNo ratings yet

- Secuencia de LedsDocument23 pagesSecuencia de LedsGUADALUPE GOMEZ HERNANDEZNo ratings yet

- Componentes Del ArduinoDocument13 pagesComponentes Del ArduinoErick Martinez GámezNo ratings yet

- GuialedsDocument10 pagesGuialedsel-elegidoNo ratings yet

- CONFIGURACIÓN PUERTO SERIE Y MAX232Document6 pagesCONFIGURACIÓN PUERTO SERIE Y MAX232ricardoraemNo ratings yet

- Introducción al funcionamiento y arquitectura interna del microcontrolador ATmega328PDocument11 pagesIntroducción al funcionamiento y arquitectura interna del microcontrolador ATmega328PJeremy Ruben Quiroz RamosNo ratings yet

- ArduinoplatformiovscodeDocument28 pagesArduinoplatformiovscodeLucas FiordelisiNo ratings yet

- Ensayo - Manuel Elias Berzunza PerezDocument15 pagesEnsayo - Manuel Elias Berzunza Perezmanuel eliasNo ratings yet

- Interfaces de E/S básicas y sus instruccionesDocument72 pagesInterfaces de E/S básicas y sus instruccionesJorge Gianotti HidalgoNo ratings yet

- Manejo de TablasDocument5 pagesManejo de TablasPabloNo ratings yet

- 232 HDocument67 pages232 HidianvidalNo ratings yet

- Significado de Paralelo y La Sigla LPTDocument3 pagesSignificado de Paralelo y La Sigla LPTBetsie GuerreroNo ratings yet

- DebugDocument8 pagesDebugMaito DíazNo ratings yet

- Practica Nro 9 Display 7 Segmentos Catodo ComunDocument16 pagesPractica Nro 9 Display 7 Segmentos Catodo ComunMarcoNo ratings yet

- Anexo - Practica 4 - Descripción Del Puerto ParaleloDocument11 pagesAnexo - Practica 4 - Descripción Del Puerto ParaleloAlan Garrido ValenciaNo ratings yet

- Manual de Prácticas Programacion AvanzadaDocument61 pagesManual de Prácticas Programacion AvanzadaCabezon TatengueNo ratings yet

- Practica 15 RelojDocument12 pagesPractica 15 RelojEmmanuel GonzalezNo ratings yet

- Manejo de Puertos de PCDocument11 pagesManejo de Puertos de PCAbel JmcNo ratings yet

- Mapeo puertos ArduinoDocument15 pagesMapeo puertos ArduinoJuan Luis Merlo100% (1)

- Prácticas de redes de datos e industrialesFrom EverandPrácticas de redes de datos e industrialesRating: 4 out of 5 stars4/5 (5)

- Práctica I Lab Controles IDocument2 pagesPráctica I Lab Controles IJohanny PérezNo ratings yet

- Práctica I Lab Controles IDocument2 pagesPráctica I Lab Controles IJohanny PérezNo ratings yet

- Práctica I Lab Controles IDocument2 pagesPráctica I Lab Controles IJohanny PérezNo ratings yet

- Clase Virtual - Micro - TelecomDocument2 pagesClase Virtual - Micro - TelecomJohanny PérezNo ratings yet

- Ejercicios de Micro - Primer CorteDocument1 pageEjercicios de Micro - Primer CorteJohanny PérezNo ratings yet

- Cómo Lograr Su Misión PersonalDocument3 pagesCómo Lograr Su Misión PersonalJohanny PérezNo ratings yet

- Micro Tele Reparacion 2009Document2 pagesMicro Tele Reparacion 2009Johanny PérezNo ratings yet

- Clase Virtual - Micro - TelecomDocument2 pagesClase Virtual - Micro - TelecomJohanny PérezNo ratings yet

- Micro Tele Reparacion 2010 - Feb 2014Document1 pageMicro Tele Reparacion 2010 - Feb 2014Johanny PérezNo ratings yet

- Clase Virtual - Micro - TelecomDocument2 pagesClase Virtual - Micro - TelecomJohanny PérezNo ratings yet

- LABORATORIO ELECTRÓNICA II - PRÁCTICA No 3Document2 pagesLABORATORIO ELECTRÓNICA II - PRÁCTICA No 3Johanny PérezNo ratings yet

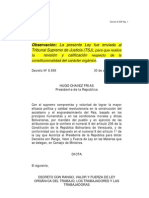

- Ley Orgánica Del Trabajo, Los Trabajadores y Las TrabajadorasDocument234 pagesLey Orgánica Del Trabajo, Los Trabajadores y Las TrabajadorasTareck El Aissami100% (4)

- Ejercicios Sistemas Digitales I - UnefaDocument2 pagesEjercicios Sistemas Digitales I - UnefaJohanny PérezNo ratings yet

- Electrónica Ii - Une - Abril - Agosto - 2012Document4 pagesElectrónica Ii - Une - Abril - Agosto - 2012Johanny PérezNo ratings yet

- Solución A La Prueba Corta - Une - Electrónica IiDocument3 pagesSolución A La Prueba Corta - Une - Electrónica IiJohanny PérezNo ratings yet

- Ejercicios de AssemblerDocument1 pageEjercicios de AssemblerJohanny PérezNo ratings yet

- Electrónica Ii - Une - Abril - Agosto - 2012Document4 pagesElectrónica Ii - Une - Abril - Agosto - 2012Johanny PérezNo ratings yet

- Ejercicios de DecibelesDocument1 pageEjercicios de DecibelesJohanny PérezNo ratings yet

- CLADocument3 pagesCLAJohanny PérezNo ratings yet

- Ejercicios Electrónica Ii - Une - TransistoresDocument2 pagesEjercicios Electrónica Ii - Une - TransistoresJohanny PérezNo ratings yet

- Mantenimiento de La PCDocument19 pagesMantenimiento de La PCJuan GarzaNo ratings yet

- Teorias de Mantenimiento de PCDocument7 pagesTeorias de Mantenimiento de PChanniahazelNo ratings yet

- Programación lógicaDocument4 pagesProgramación lógicaAldo CamPzNo ratings yet

- Programas de Edición de ImágenesDocument6 pagesProgramas de Edición de ImágenesreynaldoNo ratings yet

- Arquitectura de Oracle Database 11gDocument25 pagesArquitectura de Oracle Database 11gCarlos CruzNo ratings yet

- Debian Seguridad PDFDocument135 pagesDebian Seguridad PDFJorge Andres Cultid MejiaNo ratings yet

- Insertar Datos Sin Recargar PaginaDocument6 pagesInsertar Datos Sin Recargar PaginaHector TrianaNo ratings yet

- Que Son Los AntivirusDocument5 pagesQue Son Los AntivirusJosé EscamillaNo ratings yet

- Aplicaciones en El Plano de Viviendas: SketchupDocument110 pagesAplicaciones en El Plano de Viviendas: Sketchupgianella alfaro leonNo ratings yet

- PHP Basico Tema 13 Mysql y PHPDocument30 pagesPHP Basico Tema 13 Mysql y PHPEduardo LoyoNo ratings yet

- Crear Una Plantilla de SeguridadDocument3 pagesCrear Una Plantilla de SeguridadEnrique Williams JosephNo ratings yet

- Importar y Exportar Datos en MysqlDocument5 pagesImportar y Exportar Datos en MysqlzzzuzzzyNo ratings yet

- UNIDAD 1 Implantación de SistemasDocument11 pagesUNIDAD 1 Implantación de Sistemasjoinerjs2021100% (2)

- Analisis y Diseno de Sistemas Capitulo 10Document3 pagesAnalisis y Diseno de Sistemas Capitulo 10Randy Berks67% (6)

- 01) Prieto, A. V. y Pan, C. T. (2007)Document41 pages01) Prieto, A. V. y Pan, C. T. (2007)Jonathan GeexboxNo ratings yet

- Automatas y Lenguajes FormalesDocument157 pagesAutomatas y Lenguajes FormalesYeison UribeNo ratings yet

- Mejores Practicas CobolDocument9 pagesMejores Practicas CobolRichardBeltran0% (1)

- Evidencia 1Document3 pagesEvidencia 1Víctor HuertaNo ratings yet

- Panel de control y sus funciones principalesDocument27 pagesPanel de control y sus funciones principalesLuis AguirreNo ratings yet

- Lenguajes y Automatas Unidad 1Document18 pagesLenguajes y Automatas Unidad 1Yooekz Mencz CbdNo ratings yet

- Tutorial Informatica FrikisDocument310 pagesTutorial Informatica FrikisManu PGNo ratings yet

- Draft de Sistemas Electrónicos CooperantesDocument8 pagesDraft de Sistemas Electrónicos CooperantesomNo ratings yet

- Trabajo Final EstadisticaDocument5 pagesTrabajo Final EstadisticaAlandmrNo ratings yet

- TC2Document17 pagesTC2Jesus Antonio Duran AcevedoNo ratings yet

- TFTP InformDocument9 pagesTFTP InformEdgar FabianNo ratings yet

- Anexo 2 Manual de Usuario AlfrescoDocument12 pagesAnexo 2 Manual de Usuario AlfrescoAlex Fer B CNo ratings yet

- Macrocomputadoras Equipo 1Document7 pagesMacrocomputadoras Equipo 1héctor_cortés_8No ratings yet

- Manual de comunicaciones ZivercomDocument61 pagesManual de comunicaciones ZivercomPacoNo ratings yet

- Divisor de FrecuenciaDocument7 pagesDivisor de FrecuenciaGus RosellóNo ratings yet

- Ejercicios TEMA6 SsooDocument4 pagesEjercicios TEMA6 SsooDaniel GallegoNo ratings yet