Professional Documents

Culture Documents

dv4 LA-4117P

Uploaded by

Wade DyerCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

dv4 LA-4117P

Uploaded by

Wade DyerCopyright:

Available Formats

A

Compal confidential

Schematics Document

Mobile AMD S1G3 CPU with ATI

RS880M(NB) & SB710(SB) core logic

3

2009-03-15

REV:0.3

Compal Secret Data

Security Classification

2007/08/02

Issued Date

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Compal Electronics, Inc.

Cover Sheet

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Monday, March 16, 2009

Sheet

E

of

56

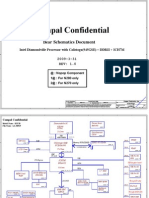

Compal Confidential

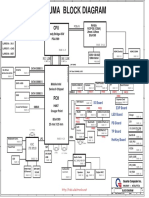

Consumer AMD 14" UMA - Ripley 2.0 (NBW20)

Accelerometer

ST LIS302DLTR

Thermal Sensor

ADM1032ARMZ

AMD S1G3 CPU

Page 6

Page 30

Fan conn

BANK 0, 1, 2, 3

Clock Generator

SLG8SP626VTR

Page 8, 9

Dual Channel

638-PIN uFCPGA 638

Page 4

72QFN

DDR2-SO-DIMM X2

DDR2 800MHz 1.8V

Page 15

Page 4, 5, 6, 7

Side-Port DDR2 SDRAM

1024Mbits(64Mbx16)

Page 12

Hyper Transport Link

16X16

USB conn x2

LVDS Panel

Interface Page

ATI RS880M

17

CRT

BT Conn

Page 10, 11, 12, 13, 14

Page 16

DDR2 400MHz

HDMI

USB conn x1

PCI-E BUS*5

Azalia (HDA I/F)

ATI SB710

Realtek

Mini-Card*2

8102E(10/100M) WLAN & WWAN

Page 27

Page 25

CardReader Socket

New Module

2

26

Page 17

SATA Master-2

SATA Slave

Express Card

FingerPrinter AES1610

page 35

USBx1

SATA Slave

Page 26

Page 31

USB WebCam

SATA Master-1

Page 19, 20, 21, 22, 23

Module

Module

Page 26

MDC V1.5

3

Page 31

USB2.0 X12

4X PCI-E

CardReader

JMicron

JMB385-LGEZ0A

daughter board

Mini-Card WWAN

Page

A-Link Express II

Page 18

Page 31

LPC BUS

RJ45/11 CONN

daughter board

Page 34

Audio CKT

Page 25

Page 27

TPA6017A2

Page 28

KBC

ENE KB926-C0

AMP & Audio Jack

Codec_IDT9271B7

Page 29

SATA HDD Connector

Page 24

Page 33

Docking CONN.

*RJ-45(LED*2)

*RJ-11(Pass Through)

*CRT

*COMPOSITE Video Out

*S-VIDEO OUT

*SPDIF

*Headphone/Line Out L/R

*Stereo Mic L/R

*Volume Control

*Consumer IR

*USB x1

*DC JACK

SATA ODD Connector

LED

Page 24

Touch Pad CONN.

Page 34

P41

Int.KBD

Page 33

Multi-Bay HDD/ODD Option Connector

Page 24

RTC CKT.

Page 19

SPI SPI ROM

MX25L1605

AM2C-12G

Page 32

Consumer IR

Page 34

Power OK CKT.

Power On/Off CKT.

P35

Compal Secret Data

2007/08/02

Issued Date

DC/DC Interface CKT.

A

Page 31

P35

Security Classification

Page 35

e-SATA Connector

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Page 36

B

Title

Compal Electronics, Inc.

Block Diagram

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Monday, March 16, 2009

Sheet

E

of

56

1.0/1.0a

Symbol Note :

For Riply PA-> PA@, RP@

For Riply PR-> PR@, RP@, PRM@

For Rachman UMA-> RM@, PRM@

: means Digital Ground

O MEANS ON

Voltage Rails

X MEANS OFF

RP10@

Z ZZ

: means Analog Ground

Layout Notes

PCB-Ripley MB

Please see VGA@ as no install. No support RX780M.

+5VS

RM10@

Z ZZ

PCB for 1.0/1.0a

PCB-Rachman UMA MB

DAZ=DAZ03Y00201

DAZ=DAZ03Y00101

+3VS

+1.5VS

power

plane

: Question Area Mark.(Wait check)

+0.9V

+VCCP

+5VALW

+CPU_CORE

+1.8V

+B

+3VALW

+VGA_CORE

+2.5VS

State

+1.8VS

+1.2VS

+0.9VGA

S1

S3

U3

RS780

RS780 R1

RS780R1@

RP11@

Z ZZ

S5 S4/AC & Battery

don't exist

RP@

Z ZZ

For Riply PA-> PA@/RP@/RPZ@

SMB_EC_CK2

DEVICE

HEX

ADDRESS

SMB_EC_DA2

DDR SO-DIMM 0

A0

10100000

I2C_CLK

DDR SO-DIMM 1

A4

10100100

I2C_DATA

CL OCK GENERATOR (EXT.)

D2

11010010

DDC_CLK0

DDC_DATA0

DDC_CLK1

EC SM Bus1 address

Device

HEX

Address

Smart Battery

16H

0001 011X b

24C16

A0H

1010 000X b

EC SM Bus2 address

Device

CPU

ADI1032-2 CPU

DDC_DATA1

SCL0

HEX

Address

98H

1001 100X b

SCL1

9AH

1001 101X b

SDA1

KB926

KB926

RS780M

RS780M

RS780M

SB700

SDA0

SB700

SCL2

SB700

SDA2

4

PCB-Ripley MB

SMBUS Control Table

SMB_EC_DA1

SCL3

SB700

SDA3

2007/08/02

Issued Date

X

X

X

X

X

X

X

X

X

BATT

V

X

X

X

X

X

X

X

X

SERIAL

EEPROM

V

X

X

X

X

X

X

X

X

THERMAL

SENSOR

CPU &

ADM1032

SODIMM

I / II

VCPU

V

ADM1032

X

X

X

X

X

X

X

X

X

X

X

X

V

X

X

X

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

CLK CHIP

X

X

X

X

X

V

X

X

X

Compal Secret Data

Security Classification

RM@

Z ZZ

DAZ=DAZ09000102

INVERTER

PCB-Rachman UMA MB

DAZ=DAZ03Y00102

X76

PCB for 2.0

For Rachman UMA-> RM@/PRM@/RMZ@

SMB_EC_CK1

I2C / SMBUS ADDRESSING

PCB-Ripley MB

DAZ=DAZ03Y00203

2.0

SOURCE

3

RM11@

Z ZZ

PCB for 1.1

For Riply PA-> PA@, RP@,RPZ@

For Riply PR-> PR@, RP@, PRM@,RPZ@

For Rachman UMA-> RM@, PRM@,RMZ@

S5 S4/ Battery only

SB700 R1

SBR1@

1.1

S5 S4/AC

U15

SB700

R3 NB and SB: RS780R3@,SBR3@

R1 NB and SB: RS780R1@,SBR1@

S0

RP11@,RM11@:For 1.A PCB

RP10@,RM10@:For 1.0 PCB.

"*" as default BOM setting

*PA@ : means install when Ripley PA.

PR@ : means install when Ripley PR.

RM@ : means install when Rachman.

*RP@ : means install when Ripley.

SIDE@ : means install when SidePort support.

@ : means just reserve , no build

45@ : Install when 45 level Assy

Title

MINI CARD

Slot 2

X

X

X

X

X

X

V

X

X

X76

PCB-Rachman UMA MB

DAZ=DAZ09100102

LCD

HDMI

X

X

V

X

X

X

X

X

X

X

X

X

V

X

X

X

X

X

G-Sensor

3

X

X

X

X

X

X

X

V

X

Compal Electronics, Inc.

Notes List

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Monday, March 16, 2009

Sheet

E

of

56

VLDT CAP.

+1.2V_HT

250 mil

1

<10> H_CADIP[0..15]

<10> H_CADIN[0..15]

H_CADIP[0..15]

H_CADOP[0..15]

H_CADIN[0..15]

H_CADON[0..15]

H_CADOP[0..15] <10>

C1

4.7U_0805_10V4Z

H_CADON[0..15] <10>

C2

4.7U_0805_10V4Z

C3

0.22U_0603_16V4Z

C4

0.22U_0603_16V4Z

C5

180P_0402_50V8J

C6

180P_0402_50V8J

Near CPU Socket

+1.2V_HT

JCPUA

<10>

<10>

<10>

<10>

3

<10>

<10>

<10>

<10>

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

H_CLKIP0

H_CLKIN0

H_CLKIP1

H_CLKIN1

J3

J2

J5

K5

H_CTLIP0

H_CTLIN0

H_CTLIP1

H_CTLIN1

N1

P1

P3

P4

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

HT LINK

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

AE2 +VLDT_B 1

C7

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

2

4.7U_0805_10V4Z

If VLDT is connected only on one side, one

4.7uF cap should be added to the island

side.

H_CADOP0

H_CADON0

H_CADOP1

H_CADON1

H_CADOP2

H_CADON2

H_CADOP3

H_CADON3

H_CADOP4

H_CADON4

H_CADOP5

H_CADON5

H_CADOP6

H_CADON6

H_CADOP7

H_CADON7

H_CADOP8

H_CADON8

H_CADOP9

H_CADON9

H_CADOP10

H_CADON10

H_CADOP11

H_CADON11

H_CADOP12

H_CADON12

H_CADOP13

H_CADON13

H_CADOP14

H_CADON14

H_CADOP15

H_CADON15

+5VS

H_CLKOP0

H_CLKON0

H_CLKOP1

H_CLKON1

H_CTLOP0

H_CTLON0

H_CTLOP1

H_CTLON1

PWM Fan Control circuit

<10>

<10>

<10>

<10>

JP2

H_CADIP0

H _CADIN0

H_CADIP1

H _CADIN1

H_CADIP2

H _CADIN2

H_CADIP3

H _CADIN3

H_CADIP4

H _CADIN4

H_CADIP5

H _CADIN5

H_CADIP6

H _CADIN6

H_CADIP7

H _CADIN7

H_CADIP8

H _CADIN8

H_CADIP9

H _CADIN9

H_CADIP10

H_CADIN10

H_CADIP11

H_CADIN11

H_CADIP12

H_CADIN12

H_CADIP13

H_CADIN13

H_CADIP14

H_CADIN14

H_CADIP15

H_CADIN15

D1

D2

D3

D4

1

D1

CH751H-40PT_SOD323-2

<10>

<10>

<10>

<10>

VLDT=500mA

C8

4.7U_0805_10V4Z

C9

0.1U_0402_16V4Z

3

4

GND

GND

1

2

5

6

Athlon 64 S1

Processor Socket

1

2

ACES_88231-02001

CONN@

+VCC_FAN

FOX_PZ6382A-284S-41F_GRIFFIN

CONN@

1

2

D Q1

@ D2

G

FAN_PWM

RLZ5.1B_LL34

SI3456BDV-T1-E3_TSOP6

<33>

9/20 SP07000DM00/SP07000EQ00

Compal Secret Data

Security Classification

2007/08/02

Issued Date

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Compal Electronics, Inc.

AMD CPU S1G2 HT I/F

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Monday, March 16, 2009

Sheet

E

of

56

Processor DDR2 Memory Interface

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

DDR_A_CLK#0

C10

1.5P_0402_50V9C

DDR_A_CLK1

1

DDR_A_CLK#1

C11

1.5P_0402_50V9C

+1.8V

2

DDR_B_CLK0

1

R1

C14

1.5P_0402_50V9C

1K_0402_1%

1

DDR_B_CLK#0

R2

C15

1.5P_0402_50V9C

C12

1K_0402_1%

1

DDR_B_CLK#1

+MCH_REF

DDR_B_CLK1

+0.9V

C13

2

2

1000P_0402_25V8J

0.1U_0402_16V4Z

+0.9V

JCPUB

Place them close to CPU within 1"

+1.8V

R4

1

1

R3

39.2_0402_1%

2

2

39.2_0402_1%

T2

<8> DDR_A_ODT0

<8> DDR_A_ODT1

<8> DDR_CS0_DIMMA#

<8> DDR_CS1_DIMMA#

<8> DDR_CKE0_DIMMA

<8> DDR_CKE1_DIMMA

<8> DDR_A_CLK0

<8> DDR_A_CLK#0

<8> DDR_A_CLK1

<8> DDR_A_CLK#1

<8> DDR_A_MA[15..0]

<8> DDR_A_BS#0

<8> DDR_A_BS#1

<8> DDR_A_BS#2

<8> DDR_A_RAS#

<8> DDR_A_CAS#

<8> DDR_A_WE#

PAD

DDR_A_ODT0

DDR_A_ODT1

D10

C10

B10

AD10

VTT1

VTT2

VTT3

VTT4

AF10

AE10

MEMZP

MEMZN

H16

T19

V22

U21

V19

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

T20

U19

U20

V20

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

J22

J20

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK1

DDR_A_CLK#1

N19

N20

E16

F16

Y16

AA16

P19

P20

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

N21

M20

N22

M19

M22

L20

M24

L21

L19

K22

R21

L22

K20

V24

K24

K19

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

R20

R23

J21

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

R19

T22

T24

MEM:CMD/CTRL/CLK VTT5

VTT6

VTT7

VTT8

VTT9

VTT_SENSE

RSVD_M1

MEMVREF

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_CKE0

MA_CKE1

RSVD_M2

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MA_CLK_H5

MA_CLK_L5

MA_CLK_H1

MA_CLK_L1

MA_CLK_H7

MA_CLK_L7

MA_CLK_H4

MA_CLK_L4

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MB_BANK0

MB_BANK1

MB_BANK2

MA_RAS_L

MA_CAS_L

MA_WE_L

MB_RAS_L

MB_CAS_L

MB_WE_L

W10

AC10

AB10

AA10

A10

Y10

W17

VTT_SENSE

PAD

T1

PAD

T3

+MCH_REF

B18

W26

W23

Y26

DDR_B_ODT0

DDR_B_ODT1

V26

W25

U22

DDR_CS0_DIMMB#

DDR_CS1_DIMMB#

J25

H26

DDR_CKE0_DIMMB

DDR_CKE1_DIMMB

P22

R22

A17

A18

AF18

AF17

R26

R25

DDR_B_CLK0

DDR_B_CLK#0

DDR_B_CLK1

DDR_B_CLK#1

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

R24

U26

J26

DDR_B_BS#0

DDR_B_BS#1

DDR_B_BS#2

U25

U24

U23

DDR_B_RAS#

DDR_B_CAS#

DDR_B_WE#

DDR_B_ODT0 <9>

DDR_B_ODT1 <9>

DDR_CS0_DIMMB# <9>

DDR_CS1_DIMMB# <9>

DDR_CKE0_DIMMB <9>

DDR_CKE1_DIMMB <9>

DDR_B_CLK0 <9>

DDR_B_CLK#0 <9>

DDR_B_CLK1 <9>

DDR_B_CLK#1 <9>

<9> DDR_B_DM[7..0]

DDR_B_MA[15..0] <9>

DDR_B_BS#0 <9>

DDR_B_BS#1 <9>

DDR_B_BS#2 <9>

DDR_B_RAS# <9>

DDR_B_CAS# <9>

DDR_B_WE# <9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

MEM:DATA

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

Y11

AE14

AF14

AF11

AD11

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

A12

B16

A22

E25

AB26

AE22

AC16

AD12

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

C12

B12

D16

C16

A24

A23

F26

E26

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

DDR_A_D[63..0] <8>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

E12

C15

E19

F24

AC24

Y19

AB16

Y13

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_DM[7..0] <8>

DDR_A_DQS0 <8>

DDR_A_DQS#0 <8>

DDR_A_DQS1 <8>

DDR_A_DQS#1 <8>

DDR_A_DQS2 <8>

DDR_A_DQS#2 <8>

DDR_A_DQS3 <8>

DDR_A_DQS#3 <8>

DDR_A_DQS4 <8>

DDR_A_DQS#4 <8>

DDR_A_DQS5 <8>

DDR_A_DQS#5 <8>

DDR_A_DQS6 <8>

DDR_A_DQS#6 <8>

DDR_A_DQS7 <8>

DDR_A_DQS#7 <8>

FOX_PZ6382A-284S-41F_GRIFFIN

FOX_PZ6382A-284S-41F_GRIFFIN

Athlon 64 S1

Processor

Socket

JCPUC

<9> DDR_B_D[63..0]

DDR_A_CLK0

Athlon 64 S1

Processor Socket

CONN@

CONN@

Compal Secret Data

Security Classification

2007/08/02

Issued Date

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Compal Electronics, Inc.

AMD CPU S1G2 DDRII I/F

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Monday, March 16, 2009

Sheet

E

of

56

@ C16

100U_D2_10VM

+1.8V

1

R5

02/27 Change net name to EN0.

2

10K_0402_5%

R10

2

300_0402_5%

Q3

C

CPU_THERMTRIP#_R

@ R6

1

+2.5VDDA VDDA=300mA

L1

3300P_0402_50V7K

1

2

FBM_L11_201209_300L_0805

1

1

1

1

+

4.7U_0805_10V4Z

C17

C18

C19

0.22U_0603_16V4Z

2

2

2

2

+2.5VS

3

1

PMBT3904_SOT23

1

R16

1

R7

0_0402_5%

2

EN0

2

0_0402_5%

2

0_0402_5%

<37,39>

H_THERMTRIP#_EC <33>

H_THERMTRIP# <20>

JCPUD

1

2

LDT_RST#

H_PWRGD_CPU

LDT_STOP#

CPU_LDT_REQ#

B7

A7

F10

C6

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

CPU_SIC

CPU_SID

AF4

AF5

AE6

SIC

SID

ALERT_L

0718 Silego -- 216 ohm

R8

169_0402_1%

<15> CLK_CPU_BCLK#

2

3900P_0402_50V7K

C21

Address:100_1100

R13

R14

+1.2V_HT

1

1

2 44.2_0402_1% CPU_HTREF0

2 44.2_0402_1% CPU_HTREF1

<43> CPU_VDD0_FB_H

<43> CPU_VDD0_FB_L

CPU_VDD0_FB_H

CPU_VDD0_FB_L

CLKIN_H

CLKIN_L

R6

P6

+1.8VS

Close to CPU

LDT_RST#

C22

0.01U_0402_25V4Z

@

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST27_SINGLECHAIN

+CPU_CORE_0

@ R489 10_0402_5%

1

2 CPU_VDD1_FB_H

1

2 CPU_VDD1_FB_L

@R488 10_0402_5%

R25

2 0_0402_5%

Reserve the R488 and R489 for S1G3 CPU

F6

E6

1

2

@

C939 0.1U_0402_16V4Z

2

1

R21

300_0402_5%

<19> H_PWRGD_CPU

@

R175

@ R814

2

CPU_SID

SMB_EC_DA1

3

1

R18

@

Q127

2

1

2.2K_0402_5% FDV301N_NL_SOT23-3

R19

2

1

FDV301N_NL_SOT23-3

2.2K_0402_5%

TEST23

H10

G9

TEST18

TEST19

E9

E8

TDO

TEST9

TEST6

E10

CPU_DBREQ#

AE9

CPU_TDO

+CPU_CORE_NB

VDD_NB_FB_H <43>

VDD_NB_FB_L <43>

CPU_TEST28_H_PLLCHRZ_P

CPU_TEST28_L_PLLCHRZ_N

TEST17

TEST16

TEST15

TEST14

D7

E7

F7

C7

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

TEST7

TEST10

C3

K8

TEST8

C4

TEST29_H

TEST29_L

C9

C8

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

VDD_NB_FB_H

VDD_NB_FB_L

R484 10_0402_5%

1

2

1

2

R485 10_0402_5%

Close to CPU

J7

H8

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

C2

AA6

VDD_NB_FB_H

VDD_NB_FB_L

TEST28_H

TEST28_L

TEST25_H

TEST25_L

AB8

AF7

AE7

AE8

AC8

AF8

PAD

PAD

PAD

PAD

PAD

PAD

T5

T6

route as differential

as short as possible

testpoint under package

T7

T8

T10

T12

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

PAD

PAD

T13

T14

H18

H19

AA7

D5

C5

2

CPU_LDT_REQ# <11,19>

02/15 Follow Trinity design.

02/15 Change R18 and R19

<32,33,34,37>

from 390 to 2.2K ohm.

03/04 Reserve R175, R814, C939, Q127 and Q129.

+1.8V

FDV301N, the Vgs is:

min = 0.65V

Typ = 0.85V

Max = 1.5V

+1.8V

1

C26

2

U2

1

THERMDA_CPU 2

C27

C24

0.01U_0402_25V4Z

@

AD7

DBREQ_L

H6

G6

+1.8V sense no support

T42

T43

0.1U_0402_16V4Z

+3VS

2

1

VDDNB_FB_H

VDDNB_FB_L

PAD

PAD

SMB_EC_CK1 <32,33,34,37>

C25

0.01U_0402_25V4Z

@

+1.8VS

VDD1_FB_H

VDD1_FB_L

W9

Y9

EC is PU to 5VALW

LDT_STOP#

R30

300_0402_5%

1 SMB_EC_CK1

@ Q129 3

S

CPU_SIC

0718 AMD , need check with AMD

CPU_LDT_REQ#

THERMDC_CPU

THERMDA_CPU

1K_0402_5%

2

2

1K_0402_5%

+1.8V

R36

300_0402_5%

SMB_EC_DA1

+1.8V

W7

W8

R22

1

1

R23

FOX_PZ6382A-284S-41F_GRIFFIN

CONN@

0.1U_0402_16V7K

+1.8VS

CPU_SVC

CPU_SVD

C23

<11,19> LDT_STOP#

+1.8V

2.09V for Gate

0718 AMD --> 1K ohm

VDDIO_FB_H

VDDIO_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

34.8K_0402_1%~N

20K_0402_5%

1

+3VS

H_PWRGD_CPU

THERMDC

THERMDA

2

0_0402_5%

+1.8V

@ 300_0402_5%

VDD0_FB_H

VDD0_FB_L

G10

AA9

AC9

AD9

AF9

A3

A5

B3

B5

C1

+1.8VS

1

@ R59

THERMDC_CPU 3

100P_0402_25V8K

4

2200p change to

100p

VDD

SCLK

D+

SDATA

D-

ALERT#

THERM#

GND

SMB_EC_CK2 <33>

SMB_EC_DA2 <33>

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

6

5

ADM1032ARMZ-2REEL_MSOP8

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

HDT Connector

JP3

1

3

5

7

9

11

13

15

17

19

21

23

2

4

6

8

10

12

14

16

18

20

22

24

26

CPU_TEST27_SINGLECHAIN

R24

2 @ 300_0402_5%

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

R26

R27

R28

R29

R31

R32

R33

R34

R35

1

2

2

2

2

2

2

2

2

2

1

1

1

1

1

1

1

1

300_0402_5%

@ 300_0402_5%

300_0402_5%

@ 300_0402_5%

@ 300_0402_5%

@ 300_0402_5%

@ 300_0402_5%

@ 300_0402_5%

@ 300_0402_5%

+3VS

5

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

T9 PAD

T11 PAD

@ MMBT3904_NL_SOT23-3

Q2

1

H_PROCHOT# <19>

R17

U1

HDT_RST# 4

LDT_RST#

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_THERMTRIP#_R

CPU_PROCHOT#_1.8

CPU_MEMHOT#_1.8V

<19>

CPU_TEST23_TSTUPD

PAD

AF6

AC7

AA8

Y

3

R15

300_0402_5%

T4

+CPU_CORE_0

R487 10_0402_5%

1

2 CPU_VDD0_FB_H

1

2 CPU_VDD0_FB_L

R486 10_0402_5%

THERMTRIP_L

PROCHOT_L

MEMHOT_L

CPU_PRO CHOT#_1.8

02/12 Remove R59.

2

1

@ 220_0402_5% R37

2

1

@ 220_0402_5% R38

2

1

@ 220_0402_5% R39

2

1

@ 220_0402_5% R40

2

1

300_0402_5% R41

CPU_SVC <43>

CPU_SVD <43>

1

@ 10K_0402_5%

2

300_0402_5%

HT_REF0

HT_REF1

CPU_VDD1_FB_H Y6

CPU_VDD1_FB_L AB6

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

SVC

SVD

CPU_SVC

CPU_SVD

A6

A4

2

R11

1

R9

+1.8V

M11

W18

C20

A9

A8

KEY1

KEY2

<15> CLK_CPU_BCLK

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

2 3900P_0402_50V7K

VDDA1

VDDA2

F8

F9

Place close to CPU wihtin 1.5"

CONN@ SAMTEC_ASP-68200-07

LDT_RST#

SB_PWRGD <20,33,43>

@ NC7SZ08P5X_NL_SC70-5

9/20 SP020016900

Address:100_1101

Compal Secret Data

Security Classification

2007/08/02

Issued Date

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Compal Electronics, Inc.

AMD CPU S1G2 CTRL

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Monday, March 16, 2009

Sheet

E

of

56

01/18 Change the net name from +CPU_CORE_1 to

VDD(+CPU_CORE) decoupling.

01/18 Change the net name from +CPU_CORE_1 to

+CPU_CORE_0

C30

330U_X_2VM_R6M

+CPU_CORE_0

+CPU_CORE_0

C31

330U_X_2VM_R6M

C29

330U_X_2VM_R6M

Near CPU Socket

Tigris platform will be 4A

+CPU_CORE_0

C32

22U_0805_6.3V6M

+CPU_CORE_0

C33

22U_0805_6.3V6M

C34

22U_0805_6.3V6M

C35

22U_0805_6.3V6M

L

1

C36

22U_0805_6.3V6M

2

+CPU_CORE_0

C38

22U_0805_6.3V6M

+CPU_CORE_NB

C41

0.01U_0402_25V4Z

C42

180P_0402_50V8J

C43

0.22U_0603_16V4Z

C44

0.01U_0402_25V4Z

+1.8V

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

3A/120mil/6vias

C45

180P_0402_50V8J

VDD0_1

VDD0_2

VDD0_3

VDD0_4

VDD0_5

VDD0_6

VDD0_7

VDD0_8

VDD0_9

VDD0_10

VDD0_11

VDD0_12

VDD0_13

VDD0_14

VDD0_15

VDD0_16

VDD0_17

VDD0_18

VDD0_19

VDD0_20

VDD0_21

VDD0_22

VDD0_23

K16

M16

P16

T16

V16

C39

22U_0805_6.3V6M

+CPU_CORE_0

C40

0.22U_0603_16V4Z

C37

22U_0805_6.3V6M

4A/160mil/8vias

Under CPU Socket

2

+CPU_CORE_0

JCPUE

G4

H2

J9

J11

J13

J15

K6

K10

K12

K14

L4

L7

L9

L11

L13

L15

M2

M6

M8

M10

N7

N9

N11

C28

330U_X_2VM_R6M

JCPUF

18A/720mil/36vias

+CPU_CORE_0

1

1

+CPU_CORE_0

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

+1.8V

FOX_PZ6382A-284S-41F_GRIFFIN

Athlon 64 S1

Processor Socket

CONN@

+CPU_CORE_NB

VDDIO decoupling.

+CPU_CORE_NB

+1.8V

C52

22U_0805_6.3V6M

2

1

C46

22U_0805_6.3V6M

C47

22U_0805_6.3V6M

C48

C49

C50

C53

22U_0805_6.3V6M

1 @

C54

22U_0805_6.3V6M

2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

FOX_PZ6382A-284S-41F_GRIFFIN

Athlon 64 S1

Processor Socket

C51

CONN@

0.22U_0603_16V4Z 0.22U_0603_16V4Z 180P_0402_50V8J 180P_0402_50V8J

2

2

2

2

+0.9V

Under CPU Socket

decoupling.

AA4

AA11

AA13

AA15

AA17

AA19

AB2

AB7

AB9

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

B4

B6

B8

B9

B11

B13

B15

B17

B19

B21

B23

B25

D6

D8

D9

D11

D13

D15

D17

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

Near Power Supply

VTT decoupling.

C: Change to NBO CAP

+ C59

220U_Y_4VM

2

Between CPU Socket and DIMM

+1.8V

+0.9V

1

C55

0.22U_0603_16V4Z

C56

0.22U_0603_16V4Z

C57

0.22U_0603_16V4Z

+1.8V

C61

0.01U_0402_25V4Z

C58

0.22U_0603_16V4Z

1

+1.8V

C60

0.01U_0402_25V4Z

180PF Qt'y follow the distance between

CPU socket and DIMM0. <2.5inch>

1

C62

180P_0402_50V8J

C63

180P_0402_50V8J

C64

180P_0402_50V8J

C67

4.7U_0805_10V4Z

C68

0.22U_0603_16V4Z

C69

0.22U_0603_16V4Z

C70

1000P_0402_25V8J

C71

1000P_0402_25V8J

C72

180P_0402_50V8J

C73

180P_0402_50V8J

Near CPU Socket Right side.

C65

180P_0402_50V8J

+0.9V

A: Add C165 and C176

to follow AMD Layout

review recommand for

EMI

+1.8V

C66

4.7U_0805_10V4Z

C79

4.7U_0805_10V4Z

C80

4.7U_0805_10V4Z

C81

0.22U_0603_16V4Z

C82

0.22U_0603_16V4Z

C83

1000P_0402_25V8J

C84

1000P_0402_25V8J

C85

180P_0402_50V8J

C86

180P_0402_50V8J

1

1

1

C74

4.7U_0805_10V4Z

1

C75

4.7U_0805_10V4Z

1

C76

4.7U_0805_10V4Z

C77

4.7U_0805_10V4Z

C: Change to NBO CAP

+ C78

220U_Y_4VM

@

Near CPU Socket Left side.

Compal Secret Data

Security Classification

2007/08/02

Issued Date

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Compal Electronics, Inc.

AMD CPU S1G2 PWR & GND

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Sheet

Monday, March 16, 2009

E

of

56

+V_DDR_MCH_REF

+1.8V

DDR_A_D0

DDR_A_D1

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

VREF

VSS

DQ0

DQ1

VSS

DQS0#

DQS0

VSS

DQ2

DQ3

VSS

DQ8

DQ9

VSS

DQS1#

DQS1

VSS

DQ10

DQ11

VSS

VSS

DQ4

DQ5

VSS

DM0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

VSS

CK0

CK0#

VSS

DQ14

DQ15

VSS

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

DDR_A_DM[0..7]

DDR_A_DM[0..7] <5>

DDR_A_DM0

D DR_A_DQS[0..7]

DDR_A_D6

DDR_A_D7

DDR_A_DQS#[0..7]

8

7

6

5

DDR_A_DQS[0..7] <5>

DDR_A_MA[0..15]

DDR_A_D12

DDR_A_D13

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6

DDR_A_D[0..63] <5>

DDR_A_MA[0..15] <5>

DDR_CKE0_DIMMA

DDR_A_BS#2

DDR_CKE1_DIMMA

DDR_A_MA15

DDR_A_DQS#[0..7] <5>

DDR_A_DM1

DDR_A_CLK0 <5>

DDR_A_CLK#0 <5>

DDR_A_D14

DDR_A_D15

+1.8V

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

2

DDR_A_D26

DDR_A_D27

<5> DDR_CKE0_DIMMA

<5> DDR_A_BS#2

DDR_CKE0_DIMMA

DDR_A_BS#2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

<5> DDR_A_BS#0

<5> DDR_A_WE#

<5> DDR_A_CAS#

<5> DDR_CS1_DIMMA#

<5> DDR_A_ODT1

DDR_A_MA10

DDR_A_BS#0

DDR_A_WE#

DDR_A_CAS#

DDR_CS1_DIMMA#

DDR_A_ODT1

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

<9,15,20,30> SMB_CK_DAT0

<9,15,20,30> SMB_CK_CLK0

+3VS

1

C103

0.1U_0402_16V4Z

VSS

DQ20

DQ21

VSS

NC

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

NC/CKE1

VDD

NC/A15

NC/A14

VDD

A11

A7

A6

VDD

A4

A2

A0

VDD

BA1

RAS#

S0#

VDD

ODT0

NC/A13

VDD

NC

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

CK1

CK1#

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

SA0

SA1

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

+V_DDR_MCH_REF

+V_DDR_MCH_REF <9>

DDR_A_DM2

DDR_A_D22

DDR_A_D23

C95

C96

2

1000P_0402_25V8J

DDR_A_D28

DDR_A_D29

DDR_A_DQS#3

DDR_A_DQS3

R44

1K_0402_1%

DDR_A_BS#0

DDR_A_MA10

DDR_A_MA1

DDR_A_MA3

47_0804_8P4R_5%

RP5

8

1

7

2

6

3

5

4

DDR_A_ODT1

DDR_CS1_DIMMA#

DDR_A_WE#

DDR_A_CAS#

DDR_CKE1_DIMMA

DDR_CKE1_DIMMA <5>

DDR_A_MA15

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6

1

C88

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

1

1

C90

1

C89

1

C91

1

C92

1

C93

1

C94

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

47_0804_8P4R_5%

RP6

8

1

7

2

6

3

5

4

1

C100

1

C99

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

47_0804_8P4R_5%

RP7

DDR_CS0_DIMMA#

8

1

DDR_A_RAS#

7

2

DDR_A_MA13

6

3

DDR_A_ODT0

5

4

1

C102

1

C101

2

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

C98

1

47_0804_8P4R_5%

Cross between +1.8V and +0.9V power plan

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

DDR_A_BS#1

DDR_A_RAS#

DDR_CS0_DIMMA#

DDR_A_ODT0

DDR_A_MA13

DDR_A_BS#1 <5>

DDR_A_RAS# <5>

DDR_CS0_DIMMA# <5>

DDR_A_ODT0 <5>

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

3

DDR_A_D44

DDR_A_D45

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_CLK1 <5>

DDR_A_CLK#1 <5>

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_D62

DDR_A_D63

FOX_AS0A426-N8RN-7F

CONN@

9/20 SP07000BZ00/SP07000EU00

DDR2 SOCKET H9.2 (REV)

Compal Secret Data

Security Classification

2007/08/02

Issued Date

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

1

C87

C97

0.1U_0402_16V4Z

DDR_A_D30

DDR_A_D31

47_0804_8P4R_5%

RP2

8

1

7

2

6

3

5

4

47_0804_8P4R_5%

RP4

8

1

7

2

6

3

5

4

DDR_A_MA5

DDR_A_MA8

DDR_A_MA9

DDR_A_MA12

R43

1K_0402_1%

DDR_A_D20

DDR_A_D21

1

VSS

DQ16

DQ17

VSS

DQS2#

DQS2

VSS

DQ18

DQ19

VSS

DQ24

DQ25

VSS

DM3

NC

VSS

DQ26

DQ27

VSS

CKE0

VDD

NC

BA2

VDD

A12

A9

A8

VDD

A5

A3

A1

VDD

A10/AP

BA0

WE#

VDD

CAS#

NC/S1#

VDD

NC/ODT1

VSS

DQ32

DQ33

VSS

DQS4#

DQS4

VSS

DQ34

DQ35

VSS

DQ40

DQ41

VSS

DM5

VSS

DQ42

DQ43

VSS

DQ48

DQ49

VSS

NC,TEST

VSS

DQS6#

DQS6

VSS

DQ50

DQ51

VSS

DQ56

DQ57

VSS

DM7

VSS

DQ58

DQ59

VSS

SDA

SCL

VDDSPD

DDR_A_DQS#2

DDR_A_DQS2

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

1

2

3

4

47_0804_8P4R_5%

RP3

8

1

7

2

6

3

5

4

DDR_A_MA4

DDR_A_MA2

DDR_A_BS#1

DDR_A_MA0

DDR_A_D16

DDR_A_D17

+1.8V

+0.9V

RP1

D DR_A_D[0..63]

DDR_A_D4

DDR_A_D5

DDR_A_D10

DDR_A_D11

+1.8V

JP4

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

Title

Compal Electronics, Inc.

DDRII SO-DIMM 0

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Monday, March 16, 2009

Sheet

E

of

56

+1.8V

DDR_B_D0

DDR_B_D1

1

2

1000P_0402_25V8J

+1.8V

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_D2

DDR_B_D3

DDR_B_D8

DDR_B_D13

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_D10

DDR_B_D11

VREF

VSS

DQ0

DQ1

VSS

DQS0#

DQS0

VSS

DQ2

DQ3

VSS

DQ8

DQ9

VSS

DQS1#

DQS1

VSS

DQ10

DQ11

VSS

VSS

DQ4

DQ5

VSS

DM0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

VSS

CK0

CK0#

VSS

DQ14

DQ15

VSS

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

+1.8V

+0.9V

JP5

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

<8> +V_DDR_MCH_REF

C104

D DR_B_D[0..63]

DDR_B_D4

DDR_B_D5

DDR_B_DM[0..7]

DDR_B_DM0

D DR_B_DQS[0..7]

DDR_B_D6

DDR_B_D7

DDR_B_MA[0..15]

DDR_B_DQS#[0..7]

DDR_B_D12

DDR_B_D9

RP8

DDR_B_MA6

DDR_B_MA2

DDR_B_MA0

DDR_CS0_DIMMB#

DDR_B_D[0..63] <5>

DDR_B_DM[0..7] <5>

DDR_B_DQS[0..7] <5>

8

7

6

5

1

2

3

4

2

C105

1

C106

1

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

C108

1

C107

1

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

C109

1

C110

1

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

C111

1

C112

1

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

C114

1

C113

1

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

C116

1

C115

1

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

2

C118

1

C117

1

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

47_0804_8P4R_5%

DDR_B_MA[0..15] <5>

RP9

DDR_B_MA14

DDR_B_MA11

DDR_B_MA7

DDR_B_MA4

DDR_B_DQS#[0..7] <5>

8

7

6

5

DDR_B_DM1

1

2

3

4

47_0804_8P4R_5%

DDR_B_CLK0 <5>

DDR_B_CLK#0 <5>

RP10

DDR_CKE1_DIMMB

DDR_B_MA15

DDR_CKE0_DIMMB

DDR_B_BS#2

DDR_B_D14

DDR_B_D15

8

7

6

5

1

2

3

4

47_0804_8P4R_5%

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

DDR_B_D21

DDR_B_D17

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_D18

DDR_B_D19

DDR_B_D24

DDR_B_D25

DDR_B_DM3

DDR_B_D26

DDR_B_D27

2

<5> DDR_CKE0_DIMMB

<5> DDR_B_BS#2

DDR_CKE0_DIMMB

DDR_B_BS#2

DDR_B_MA12

DDR_B_MA9

DDR_B_MA8

DDR_B_MA5

DDR_B_MA3

DDR_B_MA1

<5> DDR_B_BS#0

<5> DDR_B_WE#

<5> DDR_B_CAS#

<5> DDR_CS1_DIMMB#

<5> DDR_B_ODT1

DDR_B_MA10

DDR_B_BS#0

DDR_B_WE#

DDR_B_CAS#

DDR_CS1_DIMMB#

DDR_B_ODT1

DDR_B_D32

DDR_B_D33

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_D34

DDR_B_D35

DDR_B_D40

DDR_B_D41

DDR_B_DM5

DDR_B_D42

DDR_B_D43

DDR_B_D48

DDR_B_D49

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_D50

DDR_B_D51

DDR_B_D56

DDR_B_D57

DDR_B_DM7

DDR_B_D58

DDR_B_D59

<8,15,20,30> SMB_CK_DAT0

<8,15,20,30> SMB_CK_CLK0

+3VS

4

C119

0.1U_0402_16V4Z

VSS

DQ16

DQ17

VSS

DQS2#

DQS2

VSS

DQ18

DQ19

VSS

DQ24

DQ25

VSS

DM3

NC

VSS

DQ26

DQ27

VSS

CKE0

VDD

NC

BA2

VDD

A12

A9

A8

VDD

A5

A3

A1

VDD

A10/AP

BA0

WE#

VDD

CAS#

NC/S1#

VDD

NC/ODT1

VSS

DQ32

DQ33

VSS

DQS4#

DQS4

VSS

DQ34

DQ35

VSS

DQ40

DQ41

VSS

DM5

VSS

DQ42

DQ43

VSS

DQ48

DQ49

VSS

NC,TEST

VSS

DQS6#

DQS6

VSS

DQ50

DQ51

VSS

DQ56

DQ57

VSS

DM7

VSS

DQ58

DQ59

VSS

SDA

SCL

VDDSPD

GND

VSS

DQ20

DQ21

VSS

NC

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

NC/CKE1

VDD

NC/A15

NC/A14

VDD

A11

A7

A6

VDD

A4

A2

A0

VDD

BA1

RAS#

S0#

VDD

ODT0

NC/A13

VDD

NC

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

CK1

CK1#

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

SAO

SA1

GND

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

DDR_B_D20

DDR_B_D16

RP11

DDR_B_MA5

DDR_B_MA8

DDR_B_MA9

DDR_B_MA12

DDR_B_DM2

DDR_B_D22

DDR_B_D23

8

7

6

5

1

2

3

4

47_0804_8P4R_5%

RP12

DDR_B_D28

DDR_B_D29

DDR_B_MA10

DDR_B_BS#0

DDR_B_MA1

DDR_B_MA3

DDR_B_DQS#3

DDR_B_DQS3

8

7

6

5

1

2

3

4

47_0804_8P4R_5%

DDR_B_D30

DDR_B_D31

RP13

DDR_CKE1_DIMMB

DDR_B_ODT1

DDR_CS1_DIMMB#

DDR_B_CAS#

DDR_B_WE#

DDR_CKE1_DIMMB <5>

DDR_B_MA15

DDR_B_MA14

8

7

6

5

1

2

3

4

47_0804_8P4R_5%

DDR_B_MA11

DDR_B_MA7

DDR_B_MA6

RP14

DDR_B_RAS#

DDR_B_BS#1

DDR_B_ODT0

DDR_B_MA13

DDR_B_MA4

DDR_B_MA2

DDR_B_MA0

8

7

6

5

1

2

3

4

47_0804_8P4R_5%

DDR_B_BS#1

DDR_B_RAS#

DDR_CS0_DIMMB#

DDR_B_ODT0

DDR_B_MA13

Cross between +1.8V and +0.9V power plan

DDR_B_BS#1 <5>

DDR_B_RAS# <5>

DDR_CS0_DIMMB# <5>

DDR_B_ODT0 <5>

DDR_B_D36

DDR_B_D37

DDR_B_DM4

DDR_B_D38

DDR_B_D39

DDR_B_D44

DDR_B_D45

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_D46

DDR_B_D47

DDR_B_D52

DDR_B_D53

DDR_B_CLK1 <5>

DDR_B_CLK#1 <5>

DDR_B_DM6

DDR_B_D54

DDR_B_D55

DDR_B_D60

DDR_B_D61

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_D62

DDR_B_D63

+3VS

TYCO_292527-4

CONN@

9/20 SP07000ET00/SP07000GN00

Compal Secret Data

Security Classification

2007/08/02

Issued Date

2008/08/02

Deciphered Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Compal Electronics, Inc.

DDRII SO-DIMM 1

Size Document Number

Custom

LA-4117P

Date:

R ev

0.3

Monday, March 16, 2009

Sheet

E

of

56

U3B

PCIE_PTX_C_IRX_P0

PCIE_PTX_C_IRX_N0

PCIE_PTX_C_IRX_P1

PCIE_PTX_C_IRX_N1

PCIE_PTX_C_IRX_P2

PCIE_PTX_C_IRX_N2

PCIE_PTX_C_IRX_P3

PCIE_PTX_C_IRX_N3

<26> PCIE_PTX_C_IRX_P5

<26> PCIE_PTX_C_IRX_N5

<19>

<19>

<19>

<19>

<19>

<19>

<19>

<19>

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

AE3

AD4

AE2

AD3

AD1

AD2

V5

W6

U5

U6

U8

U7

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

GPP_RX4P

GPP_RX4N

GPP_RX5P

GPP_RX5N

AA8

Y8

AA7

Y7

AA5

AA6

W5

Y5

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

PART 2 OF 6

PCIE I/F

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

A5

B5

A4

B4

C3

B2

D1

D2

E2

E1

F4

F3

F1

F2

H4

H3

H1

H2

J2

J1

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

AC1

AC2

AB4

AB3

AA2

AA1

Y1

Y2

Y4

Y3

V1

V2

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

AD7

AE7

AE6

AD6

AB6

AC6

AD5

AE5

PCIE I/F SB

PCE_CALRP(PCE_BCALRP)

PCE_CALRN(PCE_BCALRN)

AC8

AB8

TMDS_B_DATA2 <18>

TMDS_B_DATA2# <18>

TMDS_B_DATA1 <18>

TMDS_B_DATA1# <18>

TMDS_B_DATA0 <18>

TMDS_B_DATA0# <18>

TMDS_B_CLK <18>

TMDS_B_CLK# <18>

1

PCIE_ITX_PRX_P0

PCIE_ITX_PRX_N0

PCIE_ITX_PRX_P1

PCIE_ITX_PRX_N1

PCIE_ITX_PRX_P2

PCIE_ITX_PRX_N2

PCIE_ITX_PRX_P3

PCIE_ITX_PRX_N3

C152

C153

C154

C155

C156

C157

C158

C159

PCIE_ITX_PRX_P5

PCIE_ITX_PRX_N5

C160 1

C161

1

SB_TX0P_C

SB_TX0N_C

SB_TX1P_C

SB_TX1N_C

SB_TX2P_C

SB_TX2N_C

SB_TX3P_C

SB_TX3N_C

R55

R56

C162

C163

C164

C165

C166

C168

C169

C167

1

1

1

1

1

1

1

1

1

1

2

2

0.1U_0402_16V7K

2 0.1U_0402_16V7K

0.1U_0402_16V7K

2 0.1U_0402_16V7K

0.1U_0402_16V7K

2

2 0.1U_0402_16V7K

0.1U_0402_16V7K

2

2 0.1U_0402_16V7K

2

1

1

PCIE_ITX_C_PRX_P0

PCIE_ITX_C_PRX_N0

PCIE_ITX_C_PRX_P1

PCIE_ITX_C_PRX_N1

PCIE_ITX_C_PRX_P2

PCIE_ITX_C_PRX_N2

PCIE_ITX_C_PRX_P3

PCIE_ITX_C_PRX_N3

2

1

1

1

1

1

2

2

2

2

2

2

2

2

1.27K_0402_1%

2K_0402_1%

CardReader

WLAN

LAN10/100

<4> H_CADOP[0..15]

0.1U_0402_16V7K

2 0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

New Card

<26>

<26>

<27>

<27>

<26>

<26>

<25>

<25>

PCIE_ITX_C_PRX_P5 <26>

PCIE_ITX_C_PRX_N5 <26>

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

TV Tuner<4>

<19>

<19>

<19>

<19>

<19>

<19>

<19>

<19>

H_CADOP[0..15]

H_CADIP[0..15]

H_CADON[0..15]

H_CADIN[0..15]

H_CADIP[0..15] <4>

H_CADIN[0..15] <4>

U3A

+1.1VS

RS880M_FCBGA528

RS780M Display Port Support (muxed on GFX)

GFX_TX0,TX1,TX2 and TX3

DP0

AUX0 and HPD0

GFX_TX4,TX5,TX6 and TX7

DP1

AUX1 and HPD1

9/20 SA00001ZG00(A11) S IC 216-0674001-00/RS780M FCBGA528P 0FH

H_CADON[0..15]

<4>

<4>

<4>

<4>

H_CLKOP0

H_CLKON0

H_CLKOP1

H_CLKON1

<4>

<4>

<4>

<4>

H_CTLOP0

H_CTLON0

H_CTLOP1

H_CTLON1

1 R57

H_CADOP0

H_CADON0

H_CADOP1

H_CADON1

H_CADOP2

H_CADON2

H_CADOP3

H_CADON3

H_CADOP4

H_CADON4

H_CADOP5

H_CADON5

H_CADOP6

H_CADON6

H_CADOP7

H_CADON7

Y25

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

H_CADOP8

H_CADON8

H_CADOP9

H_CADON9

H_CADOP10

H_CADON10

H_CADOP11

H_CADON11

H_CADOP12

H_CADON12

H_CADOP13

H_CADON13

H_CADOP14

H_CADON14

H_CADOP15

H_CADON15

AC24

AC25

AB25

AB24

AA24

AA25

Y22

Y23

W21

W20

V21

V20

U20

U21

U19

U18

T22

T23

AB23

AA22

H_CTLOP0

H_CTLON0

H_CTLOP1

H_CTLON1

M22

M23

R21

R20

2 301_0402_1% C23

A24

0718 Place within 1"

layout 1:2

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

PART 1 OF 6

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HYPER TRANSPORT CPU I/F

<26>

<26>

<27>

<27>

<26>

<26>

<25>

<25>

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

PCIE I/F GFX

D4

C4

A3

B3

C2

C1

E5

F5

G5

G6

H5

H6

J6

J5

J7

J8

L5

L6

M8

L8

P7

M7

P5

M5

R8

P8

R6

R5

P4

P3

T4

T3

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_RXCALP

HT_RXCALN

HT_TXCALP

HT_TXCALN

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

H_CADIP0

H _CADIN0

H_CADIP1

H _CADIN1

H_CADIP2

H _CADIN2

H_CADIP3

H _CADIN3

H_CADIP4

H _CADIN4

H_CADIP5

H _CADIN5

H_CADIP6

H _CADIN6

H_CADIP7

H _CADIN7

F21