Professional Documents

Culture Documents

Synchronous Sequential L I Logic: Providence University

Uploaded by

Albert TreblaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Synchronous Sequential L I Logic: Providence University

Uploaded by

Albert TreblaCopyright:

Available Formats

Providence University

Synchronous Sequential Logic L i

2010.10.13

Dept. of Computer Science and Information Engineering

1/12

Providence University

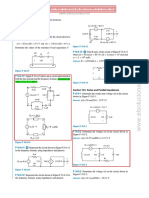

SR Latch

The SR latch is a circuit with two cross-coupled NOR gates or two cross-coupled NAND gates.

RS Flip-Flops characteristic equation is Q(t+1) = S + RQ(t)

Dept. of Computer Science and Information Engineering

2/12

Providence University

SR Latch with Control Input p

Graphic Symbols

RS

RS

Dept. of Computer Science and Information Engineering

3/12

Providence University

D Latch

One way to eliminate the undesirable condition of the indeterminate state in the RS latch is to ensure that inputs R and S are never equal time. to 1 at the same time

Graphic Symbols

D Flip-Flops characteristic equation is Q(t+1) = D

Dept. of Computer Science and Information Engineering

4/12

Providence University

D Latch

Verilog Design: D Latch

Dept. of Computer Science and Information Engineering

5/12

Providence University

Edge-Triggered D Flip-Flop g gg p p

It is similar to the symbol used for the D latch except for the arrowhead-like symbol in front of the letter C designating a dynamic input. input

Positive-edge

Negative-edge

Verilog Design: edge-triggered D Flip-Flop edge triggered Flip Flop

Dept. of Computer Science and Information Engineering

6/12

Providence University

D Flip-Flop with Asynchronous Reset p p y

Flip Flop Verilog Design: D Flip-Flop with Asynchronous Reset

Dept. of Computer Science and Information Engineering

7/12

Providence University

JK Flip-Flop p p

There are three operations that can be performed with a flip-flop: set it to 1, reset it to 0, or complement its output. The JK flip-flop operations. performs all three operations

Graphic Symbols

JK Flip-Flops characteristic equation is Q(t+1) = J Q(t) + KQ(t)

Dept. of Computer Science and Information Engineering

8/12

Providence University

JK Flip-Flop p p

Flip Flop Flip Flop Verilog Design: JK Flip-Flop from D Flip-Flop and gates

Dept. of Computer Science and Information Engineering

9/12

Providence University

T Flip-Flop p p

The T flip-flop is a complementing flip-flop and can be obtained from a JK flip-flop when inputs J and K are tied together.

The T flip-flop can be constructed with a D flip-flop and an exclusive-OR gate.

Graphic Symbols

T Flip-Flops characteristic equation is Q(t+1) = T Q(t)

Dept. of Computer Science and Information Engineering

10/12

Providence University

T Flip-Flop p p

Verilog Design: T Flip-Flop from D Flip-Flop and gates

Dept. of Computer Science and Information Engineering

11/12

Providence University

JK Flip-Flop p p

Verilog Design: JK Flip-Flop for Behavioral Modeling

Dept. of Computer Science and Information Engineering

12/12

You might also like

- Sequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos TatasDocument22 pagesSequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos Tatasvikramkolanu100% (2)

- Experiment No 13Document9 pagesExperiment No 13Amir AkhtarNo ratings yet

- Exp 4Document14 pagesExp 4Cherry Charan TejNo ratings yet

- Lab 5 - FlipflopDocument34 pagesLab 5 - Flipflopgokul sNo ratings yet

- Digital Fundamentals: With PLD ProgrammingDocument25 pagesDigital Fundamentals: With PLD ProgrammingDu PhongNo ratings yet

- Computer Organization-Flip FlopsDocument19 pagesComputer Organization-Flip Flopskamatamsandeepkumar20001305No ratings yet

- Lec # 06 - DLDDocument30 pagesLec # 06 - DLDSunny 17No ratings yet

- Unit 9 Latches and Flip-Flops: Dept. of Electrical and Computer Eng., NCTUDocument33 pagesUnit 9 Latches and Flip-Flops: Dept. of Electrical and Computer Eng., NCTUGevorg PetrosyanNo ratings yet

- COE211 CH5 Part1Document30 pagesCOE211 CH5 Part1hm100hm100hm100No ratings yet

- Expt 12Document5 pagesExpt 12Dhrrishith VikalNo ratings yet

- Practical: 13 To Study D Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Document4 pagesPractical: 13 To Study D Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Sohil VohraNo ratings yet

- TTTTT Eeee AsDocument20 pagesTTTTT Eeee AsEric GongNo ratings yet

- Flip Flop Mealy and Moore ModelDocument25 pagesFlip Flop Mealy and Moore Modelsurajpb1989100% (1)

- 5th Lecture Flip-FlopsDocument13 pages5th Lecture Flip-Flopsarshpreetmundra14No ratings yet

- Sequential Digital Circuits: Flip FlopsDocument27 pagesSequential Digital Circuits: Flip FlopsSubrahmanyam GuduruNo ratings yet

- Digital Fundamentals: FloydDocument42 pagesDigital Fundamentals: FloydlvsaruNo ratings yet

- chp7 PDFDocument14 pageschp7 PDFEugene VermeulenNo ratings yet

- Flip-Flops & Latches: Digital ElectronicsDocument20 pagesFlip-Flops & Latches: Digital ElectronicsGowtham PalanirajanNo ratings yet

- L4: Sequential Building Blocks (Flip - Flops, Latches and Registers)Document24 pagesL4: Sequential Building Blocks (Flip - Flops, Latches and Registers)ggk87No ratings yet

- Basic Flip Flops-SR Flip Flop, JK Flip Flop, D Flip Flop, T Flip Flop, CircuitsDocument11 pagesBasic Flip Flops-SR Flip Flop, JK Flip Flop, D Flip Flop, T Flip Flop, Circuitssagbhi100% (1)

- CA 452 MUX Sequential CKTDocument44 pagesCA 452 MUX Sequential CKTanamNo ratings yet

- VCLASS-2 M5 Perc Sintetik-28102020Document10 pagesVCLASS-2 M5 Perc Sintetik-28102020Fatah Nur HidayatNo ratings yet

- Chapter5 Synchronous Sequential LogicDocument24 pagesChapter5 Synchronous Sequential Logicz45eNo ratings yet

- pp07 FloydDocument42 pagespp07 Floydsss0% (1)

- cs302 Short Notes and Subjetive Paper For MidtermDocument52 pagescs302 Short Notes and Subjetive Paper For MidtermchashmanmuneerNo ratings yet

- DLD Exp 8 Student ManualDocument8 pagesDLD Exp 8 Student ManualS M AkashNo ratings yet

- Flip FlopsDocument60 pagesFlip FlopsA10-14Rajat KumarNo ratings yet

- Experiment No 11Document7 pagesExperiment No 11Ramiz IqbalNo ratings yet

- Experiment9 DE SH22Document3 pagesExperiment9 DE SH22UNCLE STATIONARYNo ratings yet

- American International University-Bangladesh: Title: Study of Different Flip-FlopsDocument7 pagesAmerican International University-Bangladesh: Title: Study of Different Flip-FlopsAbid ChowdhuryNo ratings yet

- Latches and Flip Flops CharacteristicsDocument13 pagesLatches and Flip Flops CharacteristicsWeaam RaedNo ratings yet

- Flip-Flops: S R Q Q' 1 0 1 0 Set 0 0 1 0 Previous Condition 0 1 0 1 Reset 0 0 0 1 Previous Condition 1 1 0 0 JammedDocument5 pagesFlip-Flops: S R Q Q' 1 0 1 0 Set 0 0 1 0 Previous Condition 0 1 0 1 Reset 0 0 0 1 Previous Condition 1 1 0 0 JammedMatt PrestonNo ratings yet

- Group 8 Adc Experiment 5-1Document17 pagesGroup 8 Adc Experiment 5-1ROHAN NAGRUTNo ratings yet

- D and JK FFDocument22 pagesD and JK FFRawan AyyoubNo ratings yet

- Computer Architecture 1Document39 pagesComputer Architecture 1ARAFAT GaamanNo ratings yet

- Flip FlopsDocument11 pagesFlip FlopsZakaria JubarnNo ratings yet

- 2012 - MC9211 (2) - Sequential CircuitDocument69 pages2012 - MC9211 (2) - Sequential CircuitAbhishek RaoNo ratings yet

- Flip FlopDocument34 pagesFlip Flopqwrr rewqNo ratings yet

- Solution of Homework#07: Xyq/Q 0 0 1 0 0 1 1 0 1 0 Last Q Last /Q 1 1 1 0Document4 pagesSolution of Homework#07: Xyq/Q 0 0 1 0 0 1 1 0 1 0 Last Q Last /Q 1 1 1 0Apoorva KaradiNo ratings yet

- FF and LDocument30 pagesFF and LRaja BenitaNo ratings yet

- Octal Latch - IC 74LS373 - It Has 8 D Latches With Tri State Buffers - It Has Two I/p Controle SignalsDocument1 pageOctal Latch - IC 74LS373 - It Has 8 D Latches With Tri State Buffers - It Has Two I/p Controle SignalsNeelam KapoorNo ratings yet

- Review of VHDL For Sequential CircuitsDocument11 pagesReview of VHDL For Sequential CircuitsJohn Joshua MontañezNo ratings yet

- Digital & Logic Design (DLD) : Lab Assignment Report On Implementation of D Flip Flop Ic On BreadboardDocument5 pagesDigital & Logic Design (DLD) : Lab Assignment Report On Implementation of D Flip Flop Ic On BreadboardHaris AmanNo ratings yet

- Topic 4Document55 pagesTopic 4tanay.s1No ratings yet

- Project ReportDocument11 pagesProject Reportamiethurgat100% (2)

- 6 111 l4 Seqntl BlocksDocument24 pages6 111 l4 Seqntl BlocksysakeunNo ratings yet

- Flip Flops and Registers: Bca 5 SemesterDocument19 pagesFlip Flops and Registers: Bca 5 SemesterDevi Sharan PrajapatiNo ratings yet

- Mod 5 - FLIPFLOPS and Its TypesDocument28 pagesMod 5 - FLIPFLOPS and Its TypesRavi CharanNo ratings yet

- Theory of Automata and Computation: Awot D. Defence University, College of EngineeringDocument26 pagesTheory of Automata and Computation: Awot D. Defence University, College of Engineeringkndnew guadeNo ratings yet

- CH 7Document69 pagesCH 7katral-jamerson-9379No ratings yet

- Sequential Circuits: Presented By: Group 3Document30 pagesSequential Circuits: Presented By: Group 3Jalaj SrivastavaNo ratings yet

- 10 - Sequential CircuitDocument32 pages10 - Sequential CircuitJose Mari Emmanuel MedinaNo ratings yet

- Cal - Digital Logic: Unis 2002 - 2003Document2 pagesCal - Digital Logic: Unis 2002 - 2003Anil KumarNo ratings yet

- Coeng3059:: Digital Logic DesignDocument25 pagesCoeng3059:: Digital Logic DesignALEMU DEMIRACHEWNo ratings yet

- L7 - Flip-Flops and Sequential Circuit DesignDocument41 pagesL7 - Flip-Flops and Sequential Circuit DesignSuresh ThallapelliNo ratings yet

- Study of Flip Flops Using ICsDocument5 pagesStudy of Flip Flops Using ICssaravanan_12aNo ratings yet

- VLSI ManDocument70 pagesVLSI Manrahulmohan3777No ratings yet

- The Spectral Theory of Toeplitz Operators. (AM-99), Volume 99From EverandThe Spectral Theory of Toeplitz Operators. (AM-99), Volume 99No ratings yet

- Screenshot 2024-01-22 at 6.12.43 PMDocument20 pagesScreenshot 2024-01-22 at 6.12.43 PMgj7cpz4fzyNo ratings yet

- Infineon IGCM04G60HA DataSheet v03 00 enDocument21 pagesInfineon IGCM04G60HA DataSheet v03 00 enRemy MendozaNo ratings yet

- Nullor Norator Model (Refer For Pspice Model of NullorDocument8 pagesNullor Norator Model (Refer For Pspice Model of NullorMurali SriramNo ratings yet

- Chapter 10 Differential AmplifiersDocument90 pagesChapter 10 Differential AmplifiersAbdulrahman behiry100% (1)

- Integrados 6 TerminalesDocument9 pagesIntegrados 6 TerminalesTitán SotoNo ratings yet

- Question PaperDocument2 pagesQuestion PapertrsureshNo ratings yet

- DC ChoppersDocument56 pagesDC Chopperssaikarthick023No ratings yet

- 6.BJT 6 (CH 8 Electronic Devices and Circuit Theory Robert Boylestad Louis Nashelsky 7th Edition)Document46 pages6.BJT 6 (CH 8 Electronic Devices and Circuit Theory Robert Boylestad Louis Nashelsky 7th Edition)shilaNo ratings yet

- BECE101L Basic-Electronics (Theory) NewDocument2 pagesBECE101L Basic-Electronics (Theory) NewNicky nirmalNo ratings yet

- Skanti P6001 Repair NotesDocument5 pagesSkanti P6001 Repair NotesEric PskdNo ratings yet

- Applied Electronics (Mid-Term Presentation) K-18EL101Document9 pagesApplied Electronics (Mid-Term Presentation) K-18EL101Noor SabaNo ratings yet

- Karaokay Microphone Amplifier: With Adjustable Tone Control, Usb Power and Loudspeaker OutputDocument3 pagesKaraokay Microphone Amplifier: With Adjustable Tone Control, Usb Power and Loudspeaker OutputKichiro CarvajalNo ratings yet

- Answers: (A) (B) (C) P 10.4-9: 486 10. Sinusoidal Steady-State AnalysisDocument5 pagesAnswers: (A) (B) (C) P 10.4-9: 486 10. Sinusoidal Steady-State Analysis147yourAsDeNo ratings yet

- 74VHC123A Dual Retriggerable Monostable Multivibrator: General DescriptionDocument10 pages74VHC123A Dual Retriggerable Monostable Multivibrator: General DescriptionKuni KazeNo ratings yet

- 555 Timer CircuitDocument5 pages555 Timer CircuitMack San MiguelNo ratings yet

- Lm6152/Lm6154 Dual and Quad High Speed/Low Power 75 MHZ GBW Rail-To-Rail I/O Operational AmplifiersDocument11 pagesLm6152/Lm6154 Dual and Quad High Speed/Low Power 75 MHZ GBW Rail-To-Rail I/O Operational AmplifiersahmedNo ratings yet

- Collector: Transistors Are One of The Most Important Electronic ComponentsDocument6 pagesCollector: Transistors Are One of The Most Important Electronic ComponentsimmanemmNo ratings yet

- Transistor Curve Tracer 001Document2 pagesTransistor Curve Tracer 001pecceriniNo ratings yet

- EE311 Analog Electronics Midterm I Q1) (25 PTS.) For The Following AmplifierDocument2 pagesEE311 Analog Electronics Midterm I Q1) (25 PTS.) For The Following AmplifierburakNo ratings yet

- Circuito de FuenteDocument8 pagesCircuito de FuenteEmer nelsonNo ratings yet

- Syllabus Electronics2 Spring2021Document1 pageSyllabus Electronics2 Spring2021Muhammed Bekir AdamNo ratings yet

- Game Theory ModelDocument5 pagesGame Theory ModelMaliki ChannelNo ratings yet

- Unit 3Document6 pagesUnit 3ShanilDayalanNo ratings yet

- EC6401 Electronics Circuits II - Notes - AnnaunivupdatesDocument96 pagesEC6401 Electronics Circuits II - Notes - Annaunivupdatesmanimangai100% (2)

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument5 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDjalma MotaNo ratings yet

- Adc DcaDocument6 pagesAdc DcaDr.R.RAMANNo ratings yet

- Bipolar Amplifier PDFDocument27 pagesBipolar Amplifier PDFAsta EfiNo ratings yet

- Unit 1: Transistors and Circuits: MOSFET Device MetricsDocument30 pagesUnit 1: Transistors and Circuits: MOSFET Device MetricsJeff HoNo ratings yet

- N-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesN-Channel Enhancement Mode MOSFET: Product SummaryMotorola E5 PlusNo ratings yet

- Lecture13 BJT Transistor Circuit AnalysisDocument24 pagesLecture13 BJT Transistor Circuit AnalysisAbdulGhaffarNo ratings yet