Professional Documents

Culture Documents

BIT401

Uploaded by

Afshan KaleemCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BIT401

Uploaded by

Afshan KaleemCopyright:

Available Formats

BIT 401 - VLSI Design

UNIT-I An overview of VLSI, Moores law, Electrical Conduction in Silicon, Electrical Characteristics of MOSFETs Theshold voltage, nFET Current-Voltage equations, square law and linear model of a FET, MOS capacitances, gate-source and gate drain capacitances, junction capacitances in a MOSFET, RC model of a FET, modeling small MOSFET, scaling. MOSFET as switches, pass characteristics, logic gates using CMOS, Bubble pushing, XOR and XNOR gates, AOI and OAI logic gates, transmission gates. TG based 2-to-1 MUX, XOR, XNOR, OR circuits. UNIT-II Physical structure of CMOS ICs, IC layers, layers used to create a MOSFET, Top and side view of MOSFETs, Silicon patterning or layouts for series and parallel connected FETs. Layouts of NOT gate, transmission gate, noninverting buffer, NAND2, NOR2, Complex logic gate, 4 input AOI gate. Stick diagram representations. Layouts of Basic Structure: nwells, active area definition, design of n+, p+ regions, masks for the nFET, active contact cross section and mask set, metal1 line with active contact, poly contact: cross section and layout, vias and higher level metals. Latchup prevention. UNIT-III Fabrication of CMOS ICs, CMOS process flow, Design rules: minimum space width, minimum spacing, surround, extension, cell concepts and cell based design, logic gates as basic cells, creation of new cell using basic gates. DC characteristics of the CMOS inverter symmetrical inverter, layouts, Inverter switching characteristics, RC switch model equivalent for the CMOS inverter, fanout, input capacitance and load effects, rise time and fall time calculation, propagation delay, driving large capacitive loads, delay minimization in an inverter cascade. UNIT-IV Pseudo nMOS, tristate inverter circuits, chocked CMOS, charge leakage, Dynamic CMOS logic circuits, precharge and evaluation charge sharing, Domino logic, Dual rail logic networks, differential Cascade Voltage Switch Logic (CVSL) AND/NAND, OR/NOR gates, Complementary Pars Transister Logic (CPL). The SRAM, 6T SRAM cell design parameters, writing to an SRAM, resistor model, SRAM cell layout, multi port SRAM, SRAM arrays, Dynamic RAMs: 1T RAM cell, charge leakage and refresh in a DRAM cell, physical design of DRAM cells. NOR based ROM, ROM array using pseudo nMOS circuitry, floating gate MOSFET, effect of charge storage on the floating gate, A E2PROM word using floating gate nFETs, logic gate diagram of the PLA, NOR based design, CMOS PLA, Gate arrays, gate array base. UNIT-V VLSI Design flow, structural gate level modeling, gate primitives, gate delays, switch level modeling, behavioral and RTL operators, timing controls, blocking and non blocking assignments, conditional statements, Data flow modeling and RTL, Comparator and priority encoder barrel shifter, D latch Master slave D type flip-flop, Arithmetic circuits; half adder, full adder, AOI based, TG based, ripple carry adders, carry look ahead adders, High speed adders, multipliers. Interconnect modeling; Interconnect resistance and capacitance sheet resistance Rs, time delay, single and multiple rung ladder circuits, simple RC inter connect model, modeling inter connect lines with a series pass FET, cross talk, floor planning and routing, clocking, Testing of VLSI circuits.

Suggested Reading: 1. John P. Uyemura, Introduction to VLSI circuits and Systems, John Wiley & Sons, 2002 References: 1. John P. Uyemura, Chip design for submicron VLSI: CMOS layout and simulation IE (a part of cengage learning) 2006. 2. Douglas A. Pucknell, Kamran Eshraghian, Basic VLSI Design 3 rd Edition, PHI, 2000. 3. Jan M. Rabey and others Digital Integrated Circuits A design perspective, Pearson Education

You might also like

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsFrom EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsRating: 4 out of 5 stars4/5 (3)

- Chapter 2Document37 pagesChapter 2Afshan KaleemNo ratings yet

- GeSemiconductorDataHandbook1977 Text PDFDocument1,378 pagesGeSemiconductorDataHandbook1977 Text PDFAnonymous xAqiGcQdDL100% (5)

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Diode AnimationDocument87 pagesDiode Animationaksaltaf913767% (3)

- PVsyst Training Part IDocument96 pagesPVsyst Training Part IBarun BiswasNo ratings yet

- Cmos Vlsi Design ContentDocument1 pageCmos Vlsi Design ContentdileepanmeNo ratings yet

- Review For Final Examination: ECE 4420 - Spring 2004Document3 pagesReview For Final Examination: ECE 4420 - Spring 2004Pay RentNo ratings yet

- VLSI Design SyllabusDocument2 pagesVLSI Design SyllabusJyoti RanjanNo ratings yet

- VLSI Design Course OverviewDocument4 pagesVLSI Design Course OverviewDr.P. RAJASEKARNo ratings yet

- EC8095 VLSI Design Regulation 2017 SyllabusDocument2 pagesEC8095 VLSI Design Regulation 2017 Syllabusjames RNo ratings yet

- ME - Detailed Syllabus - 2016-17 OnwardsDocument24 pagesME - Detailed Syllabus - 2016-17 OnwardsfilmfilmfNo ratings yet

- Syllabus - Vlsi and Chip DesignDocument2 pagesSyllabus - Vlsi and Chip Designjana kNo ratings yet

- (13ec604) Vlsi Design S: Ds Ds M DsDocument1 page(13ec604) Vlsi Design S: Ds Ds M DsSai Jaswanth SinghNo ratings yet

- CMOS VLSI Design Introduction Overview Methodologies Flow Hierarchy ConceptsDocument1 pageCMOS VLSI Design Introduction Overview Methodologies Flow Hierarchy ConceptsArun KumarNo ratings yet

- Syllabus For VLSI and Embedded SystemDocument1 pageSyllabus For VLSI and Embedded SystemAditya KumarNo ratings yet

- EP CoursesDocument6 pagesEP CoursesAditya BhowmikNo ratings yet

- EceDocument2 pagesEceDivya SeepanaNo ratings yet

- VLSI SYllabus With CODocument1 pageVLSI SYllabus With COchandranv76No ratings yet

- VLSI Systems Design FundamentalsDocument4 pagesVLSI Systems Design FundamentalsMuhammad Kamran AkramNo ratings yet

- Ganpat University Syllabus For Entrance Test M. Tech. (EC) VLSI & Embedded SystemsDocument2 pagesGanpat University Syllabus For Entrance Test M. Tech. (EC) VLSI & Embedded SystemsKaushik ChauhanNo ratings yet

- 9f55d1 - Introduction To Vlsi DesignDocument4 pages9f55d1 - Introduction To Vlsi DesignAman ShivachhNo ratings yet

- Revised Syllabus MicroelectronicsDocument19 pagesRevised Syllabus MicroelectronicsBaluvu JagadishNo ratings yet

- 73 Electronic ScineceDocument3 pages73 Electronic ScineceVeerabhadra rao BNo ratings yet

- 4-1 SyllabusDocument2 pages4-1 SyllabusNivvi NivethaNo ratings yet

- Sem 4 ECE SyllabusDocument5 pagesSem 4 ECE SyllabusPanthukalathil RamNo ratings yet

- VLSI Design Syllabus Covers MOS Technologies, Circuit Design ProcessesDocument1 pageVLSI Design Syllabus Covers MOS Technologies, Circuit Design ProcessesShoukath AliNo ratings yet

- VLSI Design SyllubusDocument1 pageVLSI Design SyllubusHarold WilsonNo ratings yet

- Ds Ds M DsDocument1 pageDs Ds M DsarunaNo ratings yet

- EE-225: Digital Logic DesignDocument2 pagesEE-225: Digital Logic DesignEzaz SyedNo ratings yet

- Subject: Electronic Science Code No.: (88) Unit-IDocument3 pagesSubject: Electronic Science Code No.: (88) Unit-Ianjumay19thNo ratings yet

- Vl9213 Solid State Device Modeling and Simulation LT P CDocument1 pageVl9213 Solid State Device Modeling and Simulation LT P CSoma SundarNo ratings yet

- EE Sem 4 SyllabusDocument10 pagesEE Sem 4 SyllabusTakudzwa MNo ratings yet

- Vlsi DesignDocument1 pageVlsi DesignlakshmipoNo ratings yet

- 6 Asst Prof Electronics & Communication - 1 - 230328 - 183218 PDFDocument6 pages6 Asst Prof Electronics & Communication - 1 - 230328 - 183218 PDFSujith kumarNo ratings yet

- MTech VLSI Design 1st Sem SyllabusDocument5 pagesMTech VLSI Design 1st Sem SyllabusPrakash Sinha100% (1)

- Electronics Science NET SyllabusDocument3 pagesElectronics Science NET SyllabusSivaKumarNo ratings yet

- GOVERNMENT ENGINEERING COLLEGE VLSI TECHNOLOGY LESSION PLANDocument1 pageGOVERNMENT ENGINEERING COLLEGE VLSI TECHNOLOGY LESSION PLANHarish Kumar ReddyNo ratings yet

- EC8095 VLSI Design SyllabusDocument1 pageEC8095 VLSI Design SyllabusBaskar KNo ratings yet

- Ec3352 Vlsi and Chip DesignDocument15 pagesEc3352 Vlsi and Chip DesignParanthaman GNo ratings yet

- R20-Vlsi SYLLABUSDocument2 pagesR20-Vlsi SYLLABUSdrkhamuruddeenNo ratings yet

- Electronics Science - English Only Nnet 88 PDFDocument3 pagesElectronics Science - English Only Nnet 88 PDFSexysam KamalNo ratings yet

- Vlsi TechnologyDocument1 pageVlsi TechnologyNagarjuna MalladhiNo ratings yet

- VLSI Design Fundamentals and Digital CircuitsDocument2 pagesVLSI Design Fundamentals and Digital Circuitsjames RNo ratings yet

- Department of Electrical EngineeringDocument14 pagesDepartment of Electrical EngineeringeserjeeNo ratings yet

- 13 Ec 558Document1 page13 Ec 558Siva KumarNo ratings yet

- Ec6111 - Vlsi DesignDocument9 pagesEc6111 - Vlsi DesignMegha SrivastavaNo ratings yet

- UGC NET Electronic Science SyllabusDocument3 pagesUGC NET Electronic Science Syllabuskumar HarshNo ratings yet

- GTU PHD Core Syllabus CMOS Analog Circuit DesignDocument1 pageGTU PHD Core Syllabus CMOS Analog Circuit Designsubhash_tuhhNo ratings yet

- VLSI Design (404201) : Teaching Scheme: Examination SchemeDocument2 pagesVLSI Design (404201) : Teaching Scheme: Examination SchemeSaurabhMoharirNo ratings yet

- GTU VLSI Technology and Design Course OverviewDocument3 pagesGTU VLSI Technology and Design Course OverviewSachin JoshiNo ratings yet

- (No. of Hours: 11) Unit IIDocument2 pages(No. of Hours: 11) Unit IIarupNo ratings yet

- VTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedDocument37 pagesVTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedAshik PadmanabhaNo ratings yet

- Principles of VLSI System DesignDocument1 pagePrinciples of VLSI System DesignMani BharathiNo ratings yet

- Department of Electronics and Communication Engineering DR B R Ambedkar National Institute of Technology Jalandhar-144011 Syllabus For Admission To PHD Program 2012-2013Document2 pagesDepartment of Electronics and Communication Engineering DR B R Ambedkar National Institute of Technology Jalandhar-144011 Syllabus For Admission To PHD Program 2012-2013Karan RathoreNo ratings yet

- EKTDocument54 pagesEKTAkash AdhvaryuNo ratings yet

- M.tech Advanced Digital Signal ProcessingDocument2 pagesM.tech Advanced Digital Signal ProcessingsrinivasNo ratings yet

- M.tech Advanced Digital Signal ProcessingDocument1 pageM.tech Advanced Digital Signal ProcessingsrinivasNo ratings yet

- Embedded Systems Course HandoutDocument3 pagesEmbedded Systems Course HandoutAfshan KaleemNo ratings yet

- Syllabus Pre PHDDocument3 pagesSyllabus Pre PHDAfshan KaleemNo ratings yet

- 3bis MultiplexingDocument42 pages3bis MultiplexingAmjad AfridiNo ratings yet

- Funlettertracing ODocument1 pageFunlettertracing OAfshan KaleemNo ratings yet

- RegistrationDocument5 pagesRegistrationAfshan KaleemNo ratings yet

- Unit - I: Instruction 4 Periods Per Week 3 Hours Univ. Exam 75 Marks Sessionals 25 MarksDocument2 pagesUnit - I: Instruction 4 Periods Per Week 3 Hours Univ. Exam 75 Marks Sessionals 25 MarksAfshan KaleemNo ratings yet

- Handwriting Alphabet JDocument1 pageHandwriting Alphabet JAfshan KaleemNo ratings yet

- B.E Reval2014-15 PDFDocument87 pagesB.E Reval2014-15 PDFAfshan KaleemNo ratings yet

- Course File Index: Muffakham Jah College of Engineering and Technology Information Technology DepartmentDocument1 pageCourse File Index: Muffakham Jah College of Engineering and Technology Information Technology DepartmentAfshan KaleemNo ratings yet

- Handwriting Alphabet GDocument1 pageHandwriting Alphabet GAfshan KaleemNo ratings yet

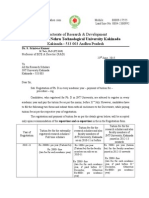

- Credit Course ApplicationDocument7 pagesCredit Course ApplicationAfshan KaleemNo ratings yet

- Multiple Access Techniques ExplainedDocument45 pagesMultiple Access Techniques ExplainedAfshan KaleemNo ratings yet

- Credit Course Exam Notification May 2015Document5 pagesCredit Course Exam Notification May 2015Afshan KaleemNo ratings yet

- VLSI Question Bank PDFDocument23 pagesVLSI Question Bank PDFAfshan KaleemNo ratings yet

- Multiple Access Techniques ExplainedDocument45 pagesMultiple Access Techniques ExplainedAfshan KaleemNo ratings yet

- ECE Pre-PhD Credit Course for Comm & Signal ProcessingDocument1 pageECE Pre-PhD Credit Course for Comm & Signal ProcessingAfshan KaleemNo ratings yet

- 4/4 Be (It) Ii-Semester BIT 451 Embedded Systems: Suggested ReadingDocument1 page4/4 Be (It) Ii-Semester BIT 451 Embedded Systems: Suggested ReadingAfshan KaleemNo ratings yet

- DS ManualDocument119 pagesDS ManualAfshan KaleemNo ratings yet

- Prosody-Preserving Voice Transformation To Evaluate Brain Representations of Speech SoundsDocument13 pagesProsody-Preserving Voice Transformation To Evaluate Brain Representations of Speech SoundsAfshan KaleemNo ratings yet

- VLSI NotesDocument130 pagesVLSI NotesOrcus DantalianNo ratings yet

- Ece Credit Course Pre PH.DDocument1 pageEce Credit Course Pre PH.DAfshan KaleemNo ratings yet

- ECE Pre-PhD Credit Course for Comm & Signal ProcessingDocument1 pageECE Pre-PhD Credit Course for Comm & Signal ProcessingAfshan KaleemNo ratings yet

- ECE Pre-PhD Credit Course for Comm & Signal ProcessingDocument1 pageECE Pre-PhD Credit Course for Comm & Signal ProcessingAfshan KaleemNo ratings yet

- ECE Pre-PhD Credit Course for Comm & Signal ProcessingDocument1 pageECE Pre-PhD Credit Course for Comm & Signal ProcessingAfshan KaleemNo ratings yet

- I/O Devices and Interfacing GuideDocument32 pagesI/O Devices and Interfacing GuideAfshan KaleemNo ratings yet

- 8051Document28 pages8051MadhuSquareNo ratings yet

- Unit VI-8051Document61 pagesUnit VI-8051Afshan KaleemNo ratings yet

- PV T-Max 1Document9 pagesPV T-Max 1akkNo ratings yet

- Introduction to VLSI Design and Bio-SensorsDocument60 pagesIntroduction to VLSI Design and Bio-Sensorssadia santaNo ratings yet

- BJT ProblemsDocument11 pagesBJT ProblemsRajesh PerlaNo ratings yet

- ECE3040 Homework6 SolutionDocument4 pagesECE3040 Homework6 Solutionmehtajay1993No ratings yet

- EC302Document23 pagesEC302api-3853441No ratings yet

- Elkadig SlideDocument98 pagesElkadig SlideMbah TekkomNo ratings yet

- 05 Internal MemoryDocument33 pages05 Internal MemoryfikaduNo ratings yet

- Final Review ProblemsDocument9 pagesFinal Review ProblemsthomasNo ratings yet

- ContinueDocument2 pagesContinueAsad AhmedNo ratings yet

- List BibliographyDocument3 pagesList BibliographyAyumuNo ratings yet

- Bipolar Transistors: Fabrizio BonaniDocument64 pagesBipolar Transistors: Fabrizio BonaniBilal Haider TanoliNo ratings yet

- Lec - 15 DICDDocument48 pagesLec - 15 DICDmd siddNo ratings yet

- 1H Transistor PNP 10a 80V Darlington To 220 1579892328Document2 pages1H Transistor PNP 10a 80V Darlington To 220 1579892328Fuerza AereaNo ratings yet

- ADA071857, HDBK of Modelling Incl Rad EffectsDocument718 pagesADA071857, HDBK of Modelling Incl Rad EffectsRGK77No ratings yet

- Darlington TransistorDocument6 pagesDarlington TransistorBilly JonesNo ratings yet

- VLSI Design - Lecture Notes, Study Material and Important Questions, AnswersDocument9 pagesVLSI Design - Lecture Notes, Study Material and Important Questions, AnswersM.V. TVNo ratings yet

- LTspice IV Library API Components GuideDocument85 pagesLTspice IV Library API Components GuidekalimbaloNo ratings yet

- Introduction To Logic Gates and Circuit Design: Hernandez, John Patrick A. EE-3104 Intended Learning OutcomesDocument17 pagesIntroduction To Logic Gates and Circuit Design: Hernandez, John Patrick A. EE-3104 Intended Learning OutcomesJohn Patrick HernandezNo ratings yet

- Optimization of Copper Indium Gallium Diselenide Thin Film Solar Cell (CIGS)Document7 pagesOptimization of Copper Indium Gallium Diselenide Thin Film Solar Cell (CIGS)Ouarda TerghiniNo ratings yet

- VTH Instability of MOSFETs With Advanced Gate Dielectrics (PHD Thesis)Document150 pagesVTH Instability of MOSFETs With Advanced Gate Dielectrics (PHD Thesis)shenchen100% (2)

- Power TransistorDocument37 pagesPower Transistorsaikarthick023No ratings yet

- Nanosheet Self Heating 08344800Document7 pagesNanosheet Self Heating 08344800ck maitiNo ratings yet

- U15Document17 pagesU15Kapildev KumarNo ratings yet

- Automotive Power Selection Guide 2019: Ultimate Power - Perfect ControlDocument146 pagesAutomotive Power Selection Guide 2019: Ultimate Power - Perfect ControlJohn Kevin ToralNo ratings yet

- THYRISTORDocument67 pagesTHYRISTORAko si GianNo ratings yet

- Regras de Projeto AMS CMOS 0.35Document32 pagesRegras de Projeto AMS CMOS 0.35Bárbara BrittoNo ratings yet

- Bss 145Document7 pagesBss 145Miloud ChouguiNo ratings yet