Professional Documents

Culture Documents

Tarea1 Sol

Uploaded by

Elvis ShahuanoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tarea1 Sol

Uploaded by

Elvis ShahuanoCopyright:

Available Formats

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

SEGUNDA TAREA DEL CURSO DE SISTEMAS DIGITALES

2010-B

PREGUNTA N1 Disear de desplazamiento bidireccional, que permita ingresar datos en modo paralelo de 4 bits, asimismo efecte desplazamiento hacia la derecha hacia la izquierda, dependiendo de una seal de control. SOLUCION

Figura N 1

Para mi diseo, utilizar flip-flops tipo D y muchas compuertas lgicas. Por lo general, cuando se realiza la carga en paralelo, se hace uso de las entradas asncronas de puesta en cero (Clear) y de puesta en uno (Preset). Para ello me val de compuertas NAND, ocurriendo lo siguiente: cuando por alguna entrada de datos ingresa un nivel bajo, se activa la entrada Clear y llega un nivel alto a la entrada Preset, poniendo en 0 al flip-flop. Esto lo repetimos en cada biestable, de este modo hemos ingresado los datos en forma asncrona. Para efectuar el desplazamiento, utilizaremos dos compuertas AND y una compuerta OR, sucediendo lo siguiente: La primera puerta AND es controlada por la entrada 1R/0L, cuando por ella ingresa un nivel alto, habilita la primera puerta AND dejando pasar la salida de este flip-flop al siguiente, as, para la

1 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

siguiente seal de reloj, la salida se desplazar hacia la derecha, de a para el primer ciclo de reloj, de a para el segundo flanco de cambio, para finalmente de a . Adicionalmente le agregu al circuito una entrada de datos cuando el desplazamiento es hacia la derecha. Cuando por la entrada 1R/0L ingresa un nivel bajo, ahora el desplazamiento es hacia la izquierda. Es debido a que ahora la primera puerta se inhibe mientras que la segunda es habilitada ingresando a la entrada de un biestable la salida del flip-flop anterior. De este modo hemos generado el registro de entrada de datos en paralelo y con desplazamiento bidireccional. PREGUNTA N2 Utilizando IC 74193 y dispositivos de soporte se pide disear el circuito digital que permita generar los estados siguientes:

Y se repite secuencia peridicamente SOLUCION PREGUNTA N3 Se tiene un ADC de aproximaciones sucesivas, de bits; siendo el tamao de salto de 10mV; el circuito dispone de un generador de reloj, cuya frecuencia de salida es . Determinar a) El tiempo de conversin, considerando una entrada analgica (muestra de amplitud 8,35 voltios) b) En relacin a la pregunta anterior determinar el valor digital obtenido despus de la conversin. c) Si la salida digital es 0101101011 calcular el valor de la seal de entrada analgica y el tiempo de conversin empleado. SOLUCION Sabemos que el tiempo de conversin en un ADC de aproximaciones sucesivas es fijo para cualquier valor de la entrada analgica. Bsicamente este convertidor consta del siguiente diagrama de bloques bsico.

2 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Figura N 2

Donde: DAC: Convertidor digital-analgicol. SAR: Registro de aproximaciones sucesivas. COM: Comparador Considerando el tamao de salto de 10 mV con un nmero de bits igual a 10, construimos una tabla para calcular el voltaje de salida en el DAC cuando se activa alguna de las 10 entradas los valores sern: N Bit Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Ahora, analizando tenemos Valor de voltaje ) ) ) ) ) ) ) ) ) )

( ( ( ( ( ( ( ( ( (

Figura N 3

3 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

La figura N3 muestra el primer paso del ciclo de conversin con el . La salida del DAC es 10.28 V. Puesto que es mayor que la entrada de 8.35 V, la salida del comparador est a nivel BAJO, lo que hace que el MSB del SAR se ponga a 0.

Figura N 4

La figura N4 muestra el segundo paso del ciclo de conversin con el bit 28 igual a 1. La salida del DAC es 5.11 V. Puesto que es menor que la entrada de 8.35 V, la salida del comparador est a nivel ALTO, lo que hace que este bit se mantenga en el SAR.

Figura N 5

La figura N5 muestra el tercer paso del ciclo de conversin con el bit 27 igual a 1. La salida del DAC es 7.66 V, ya que los bits de entrada 28 y 27 estn a 1; (5.11 V+2.55 V). Puesto que es menor que la entrada de 8.35 V, la salida del comparador est a nivel ALTO, lo que hace que este bit se mantenga en el SAR.

4 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Figura N 6

La figura N6 muestra el cuarto paso del ciclo de conversin con el bit 26 igual a 1. La salida del DAC es 8.93 V, ya que los bits de entrada 28, 27 y 26 estn a 1; (5.11 V+2.55 V+1.27 V). Puesto que es mayor que la entrada de 8.35 V, la salida del comparador est a nivel BAJO, lo que hace que este bit se ponga a cero en el SAR.

Figura N 7

La figura N7 muestra el quinto paso del ciclo de conversin con el bit 25 igual a 1. La salida del DAC es 8.29 V, ya que los bits de entrada 28, 27, 26 y 25 estn a 1; (5.11 V+2.55 V+0.63 V). Puesto que es menor que la entrada de 8.35 V, la salida del comparador est a nivel ALTO, lo que hace que este bit se mantenga en el SAR.

Figura N 8

5 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

La figura N8 muestra el sexto paso del ciclo de conversin con el bit 24 igual a 1. La salida del DAC es 8.6 V, ya que los bits de entrada 28, 27, 26, 25 y 24 estn a 1; (5.11 V+2.55 V+0.63 V+0.31 V). Puesto que es mayor que la entrada de 8.35 V, la salida del comparador est a nivel BAJO, lo que hace que este bit se ponga a 0 en el SAR.

Figura N 9

La figura N9 muestra el sptimo paso del ciclo de conversin con el bit 23 igual a 1. La salida del DAC es 8.44 V, ya que los bits de entrada 28, 27, 26, 25 y 23 estn a 1; (5.11 V+2.55 V+0.63 V+0.15 V). Puesto que es mayor que la entrada de 8.35 V, la salida del comparador est a nivel BAJO, lo que hace que este bit se ponga a 0 en el SAR.

Figura N 10

La figura N10 muestra el octavo paso del ciclo de conversin con el bit 22 igual a 1. La salida del DAC es 8.36 V, ya que los bits de entrada 28, 27, 26, 25 y 22 estn a 1; (5.11 V+2.55 V+0.63 V+0.07 V). Puesto que es mayor que la entrada de 8.35 V, la salida del comparador est a nivel BAJO, lo que hace que este bit se ponga a 0 en el SAR.

6 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Figura N 11

La figura N11 muestra el noveno paso del ciclo de conversin con el bit 21 igual a 1. La salida del DAC es 8.32 V, ya que los bits de entrada 28, 27, 26, 25 y 21 estn a 1; (5.11 V+2.55 V+0.63 V+0.03 V). Puesto que es menor que la entrada de 8.35 V, la salida del comparador est a nivel ALTO, lo que hace que este bit se mantenga en el SAR.

Figura N 12

La figura N12 muestra el dcimo (ltimo) paso del ciclo de conversin con el bit 20 igual a 1. La salida del DAC es 8.33 V, ya que los bits de entrada 28, 27, 26, 25, 21 y 20 estn a 1; (5.11 V+2.55 V+0.63 V+0.03 V+0.01 V). Puesto que es menor que la entrada de 8.35 V, la salida del comparador est a nivel ALTO, lo que hace que este bit se mantenga en el SAR. De este modo, nuestro ADC por aproximaciones sucesivas ha cuantificado este valor analgico con el siguiente cdigo: 0110100011 que equivale a 8.33 V, muy cercano al valor real. Como tambin podemos ver, se ha utilizado 10 ciclos de reloj (para nuestro caso de 1MHz), por ello el tiempo de conversin ser de 10 s. Podemos ver tambin que este ADC emplear el mismo tiempo de conversin ser el mismo para cualquier valor de entada analgica. Si la salida digital es 0101101011, el valor se la seal de entrada analgica cuantizada por el ADC ser:

7 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Entonces: a) El tiempo de conversin es 10 s, para cualquier valor de entrada se seal analgico. b) Nuestro ADC por aproximaciones sucesivas ha cuantificado este valor analgico (8.35 V) con el siguiente cdigo digital: 0110100011. c) El valor de la seal de entrada analgica es de 7.2 V, y el tiempo de conversin es el mismo que en la pregunta a, es decir 10 s. PREGUNRA N4 En el diseo de un contador sncrono se han obtenido las ecuaciones de estado de los Flip-Flops. ( ) ( ) (

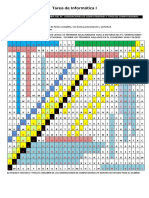

a) Graficar en funcin al tiempo los estados b) Determinar los estados binarios generados por el contador. SOLUCION 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 0 1 1 0 0 1 1 1 0 1 1 0 0 1 1 1 1 1 1 0 0 1 1 1 1 1 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 0 0 1 1 1 0 1 1 0 0 1 1 1 0 1 1 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 0 0 0 0 0 0 1 1 1 1 0 1 0 1 0 0 0 1 1 1 0 1 0 0

1 0 1 1 1 0 0 1 1 0 0 1 0 0 0 1

1 0 0 1 1 1 1 0 1 0 1 0 0 0 0 0

8 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Los estados binarios generados por el contador son: 15 0 12 10 5 13 6 4

1 11

PREGUNTA N5 Un sistema digital presenta las caractersticas siguientes:

Disear un circuito digital para ejecutar las funciones siguientes:

9 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

a) Escritura de datos a un banco de memorias usando IC 2114 en todas las direcciones del banco de memorias. b) Lectura de datos en el banco de memorias indicadas en el tem anterior. Comparando los datos ledos con los datos escritos; si son diferentes mostrar en un led rojoque existe error en la memoria. c) Repetir el diseo indicado en a) y b) considerando datos . SOLUCION

/16

Sistema de Memorias

A15-A0 MEMORIA DE 2kB 2114 (4)

7FFh

/8

D7-D0

a) Para escribir los datos:

/10

Sistema de Memorias

A9-A0 2x2114 1kB D7-D0

BUS DE DIRECCIONES

A9-A0 2x2114 1kB D7-D0

/8

Realizamos la tabla de estados:

BUS DE DATOS

HEX

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 1 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

h FFh FFh FFh

Vemos que solo cambia el bit del bus de direcciones, por ello colocamos un inversor a esta entrada.de ese modo durante la primera etapa de carga del dato 00000000 en la primera memoria de1kB. Cuando pasa a 1, el inversor invierte este 1 a 0, activando la segunda memoria de 1kB. De este modo hemos escrito en los 4 214 el dato 00000000. b) Para leer los datos, colocamos a nuestra memoria en modo lectura para luego verificar si hay error en la memoria, haremos uso del comparadores de 4 bits (4 7485), de la siguiente manera, ya que en total disponemos de 16 pares de entradas

10 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

en los comparadores, utilizaremos las cuatro primeras para ingresar 4 bits de la memoria, a las otras cuatro entradas del mismo comparador se ingresan valores bajos. Lo mismo haremos con los otros 3 comparadores (7485). Utilizaremos compuertas OR para detectar si hay o si no hay error, a las puertas OR se ingresan las salidas de desigualdad de cada comparador, as cuando al menos un comparador (7485) indique alguna desigualdad este activar un led de color rojo que nos indicar que el dato almacenado no es igual al dato 00000000.

BUS DE DATOS DE 1kB 2x2114

BUS DE DATOS DE 1kB 2x2114

c) Ser igual que en el caso anterior:

/16

Sistema de Memorias

A15-A0 MEMORIA DE 2kB 2114 (4)

7FFh

/8

D7-D0

/10

Sistema de Memorias

A9-A0 2x2114 1kB D7-D0

BUS DE DIRECCIONES

A9-A0 2x2114 1kB D7-D0

11 Flores Pacheco Alonso Mario

/8

BUS DE DATOS

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Realizamos la tabla de estados:

HEX

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 1 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

0 1 0 1

h FFh FFh FFh

Al igual que el caso anterior solo cambia , por ello a esta salida del sistema de memorias ser quien controle a los chips de las memorias 2114. Ahora para verificar si el dato almacenado (11111111) es correcto, como en el caso anterior utilizaremos los comparadores. La disposicin de la conexin es la misma que en el caso anterior, salvo que ahora en la otra entrada de cada comparador ingresaremos el valor 11111111.

BUS DE DATOS DE 1kB 2x2114

BUS DE DATOS DE 1kB 2x2114

PREGUNTA N7 Realizar la investigacin de: a) PLD (Dispositivos lgicos programables). b) Tipos de PLD (PLA, PAL, CPLD, FPGA, etc). c) Tecnologas de Fabricacin. d) Progrmacin VHDL. Ventajas, desventajas.

12 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

SOLUCION

2010-B

(Programmable Logic Device - Dispositivo Lgico Programable). Un PLD es un componente electrnico empleado para la fabricacin de circuitos digitales reconfigurables. A diferencia de las puertas lgicas, que tienen una funcin fija, un PLD tiene una funcin indefinida al momento de fabricarse. Antes de que un PLD pueda ser usado en un circuito, este puede ser programado, esto es, reconfigurado. Los PLD actuales emplean diferentes formas de almacenar datos: antifusibles de silicio, SRAM, celdas EPROM o EEPROM y memorias Flash. Antes de los PLD Antes de que los dispositivos PLD fueran inventados, los chips de memorias ROM (PROM, EPROM, EEPROM) eran usados para crear funciones lgicas combinacionales arbitrarias de M entradas con N salidas, siendo este el mejor dispositivo lgico combinacional de propsito general disponible en la poca. De todas maneras son circuitos ms lentos que los circuitos lgicos dedicados, pueden no funcionar bien en transiciones lgicas asncronas, consumen mucha energa, son ms caros, etc. Tampoco disponen de registros de entrada o salida, as que no pueden ser usados de forma independiente para lgica secuencial (a menudo se empleaban registros TTL externos). En cuanto a los lenguajes de programacin usados, PALASM y ABEL para los dispositivos de baja complejidad, mientras que Verilog y VHDL son lenguajes populares para dispositivos complejos. Se emplean dispositivos programadores (Ver programador (hardware)) para transferir los patrones de lgica booleana dentro de un dispositivo programable. Actualmente se emplean programadores universales que soportan diversas familias de dispositivos lgicos de diferentes fabricantes. Algunos formatos tpicos usados para almacenar patrones de lgica booleana son JEDEC, Altera POF (Programmable Object File) o Xilinx BITstream. Los primeros PLD Los primeros dispositivos lgicos programables fueron presentados por Motorola (el XC157 en 1969), Texas Instruments (el TMS2000 en 1970, basado en las memorias ROAM de solo lectura de IBM, poda ser programado alterando la capa de metal durante la produccin del circuito integrado). Justamente esta empresa comenz a llamarlos "dispositivos lgicos programables" (Programmable Logic Array). En 1973 National Semiconductor introdujo el DM7575, con 14 entradas y 8 salidas sin registros de memoria; este dispositivo fue la base del 82S100, producido por Signetics en 1975. La compaa General Electric fue la primera en crear un dispositivo PLD que poda ser

13 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

borrado: lanz en 1974, junto con Monolithic Memories, el PALA (Programmable Associative Logic Array).

Dispositivos PLD destacados * PAL (Programmable array logic) * GAL (Generic array logic) * CPLD * FPGA ASIC ASIC significa Circuitos Integrados de Aplicacin Especfica y son dispositivos definibles por el usuario. Los ASICs, al contrario que otros dispositivos, pueden contener funciones analgicas, digitales, y combinaciones de ambas. En general, son programables mediante mscara y no programables por el usuario. Esto significa que los fabricantes configurarn el dispositivo segn las especificaciones del usuario. Se usan para combinar una gran cantidad de funciones lgicas en un dispositivo. Sin embargo, estos dispositivos tienen un costo inicial alto, por lo tanto se usan principalmente cuando es necesario una gran cantidad. Estructura bsica de un PLD Un dispositivo programable por el usuario es aquel que contiene una arquitectura general pre-definida en la que el usuario puede programar el diseo final del dispositivo empleando un conjunto de herramientas de desarrollo. Las arquitecturas generales pueden variar pero normalmente consisten en una o ms matrices de puertas AND y OR para implementar funciones lgicas. Muchos dispositivos tambin contienen combinaciones de flip-flops y latches que pueden usarse como elementos de almacenaje para entrada y salida de un dispositivo. Los dispositivos ms complejos contienen macroclulas. Las macroclulas permite al usuario configurar el tipo de entradas y salidas necesarias en el diseo PROM

14 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Las PROM son memorias programables de slo lectura. Aunque el nombre no implica la lgica programable, las PROM, son de hecho lgicas. La arquitectura de la mayora de las PROM consiste generalmente en un nmero fijo de trminos AND que alimenta una matriz programable OR. Se usan principalmente para decodificar las combinaciones de entrada en funciones de salida. PAL

Las PAL son dispositivos de matriz programable. La arquitectura interna consiste en trminos AND programables que alimentan trminos OR fijos. Todas las entradas a la matriz pueden ser combinadas mediante AND entre si, pero los trminos AND especficos se dedican a trminos OR especficos. Las PAL tienen una arquitectura muy popular y son probablemente el tipo de dispositivo programable por usuario ms empleado. Si un dispositivo contiene macroclulas, comnmente tendr una arquitectura PAL. Las macroclulas tpicas pueden programarse como entradas,

15 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

salidas, o entrada/salida (e/s) usando una habilitacin tri-estado. Normalmente tienen registros de salida que pueden usarse o no conjuntamente con el pin de e/s asociado. Otras macroclulas tiene ms de un registro, varios tipos de retroalimentacin en las matrices, y ocasionalmente realimentacin entre macroclulas. GAL Las GAL son dispositivos de matriz lgica genrica. Estn diseados para emular muchas PAL pensadas para el uso de macroclulas. Si un usuario tiene un diseo que se implementa usando varias PAL comunes, puede configurar varias de las mismas GAL para emular cada de uno de los otros dispositivos. Esto reducir el nmero de dispositivos diferentes en existencia y aumenta la cantidad comprada. Comnmente, una cantidad grande del mismo dispositivo debera rebajar el costo individual del dispositivo. Estos dispositivos tambin son elctricamente borrables, lo que los hace muy tiles para los ingenieros de diseo.

PLA

Las PLA son matrices lgicas programables. Estos dispositivos contienen ambos trminos AND y OR programables lo que permite a cualquier trmino AND alimentar cualquier trmino OR. Las PLA probablemente tienen la mayor flexibilidad frente a otros dispositivos con respecto a la lgica funcional. Normalmente poseen realimentacin desde la matriz OR hacia la matriz AND que puede usarse para implementar mquinas de estado asncronas. La mayora de las mquinas de estado, sin embargo, se implementan como mquinas sincrnas. Con esta perspectiva, los fabricantes crearon un tipo de PLA denominado Secuencial (Sequencer) que posee registros de realimentacin desde la salida de la matriz OR hacia la matriz AND. PLDs complejos Los PLDs complejos son lo que el nombre implica, Dispositivos Complejos de Lgica Programable. Se consideran PAL muy grandes que tienen algunas caractersticas de las PLA. La arquitectura bsica es muy parecida a la PAL con la capacidad para aumentar la cantidad de trminos AND para cualquier trmino OR fijo. Esto se puede realizar quitando trminos AND adyacentes o empleando trminos AND desde una matriz expandida. Esto permite que cualquier diseo pueda ser implementado dentro de estos dispositivos.

16 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

FPGA

2010-B

Las FPGA son Campos de Matrices de Puertas Programables. Simplemente son matrices de puertas elctricamente programables que contienen mltiples niveles de lgica. Las FPGA se caracterizan por altas densidades de puerta, alto rendimiento, un nmero grande de entradas y salidas definibles por el usuario, un esquema de interconexin flexible, y un entorno de diseo similar al de matriz de puertas. No estn limitadas a la tpica matriz AND-OR. Por contra, contienen una matriz interna configurable de relojes lgicos (CLBs) y un anillo de circunvalacin de bloques de e/s (IOBs). Cada CLB contiene lgica programable combinacional y registros de almacenamiento. La seccin de lgica combinacional es capaz de implementar cualquier funcin booleana de sus variables de entrada. Cada IOB puede programarse independientemente para ser una entrada, y salida con control tri-estado o un pin bidireccional. Tambin contiene flip-flops que pueden usarse como buffers de entrada y salida. Los recursos de interconexin son una red de lneas que corren horizontalmente y verticalmente las filas y columnas entre el CLBS. Los interruptores programables conectan las entradas y salidas de IOBS y CLBS a lneas cercanas. Las lneas largas recorren la anchura o longitud entera del dispositivo, estableciendo intercambios para proporcionar una distribucin de seales crticas con la mnima demora o distorsin. Los diseadores que usan FPGAs pueden definir funciones lgicas en un circuito y revisar estas funciones como sea necesario. As, las FPGAs pueden disearse y verificarse en unos das, a diferencia de las varias semanas necesarias para las matrices de puerta programables. PREGUNTA 8 Realizar la programacin VHDL de los siguientes dispositivos. a) MUX 4/1. b) DEMUX 1/4. c) DECODER DECIMAL 3/8. d) SUMADOR TOTAL. e) COMPARADOR BINARIO.

17 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

f) FLIP FLOP JK, D. g) REGISTRO DE 4 BITS. h) CONTADOR ASINCRONO MODULO 16. SOLUCION Para nuestra solucin utilizaremos el mtodo estructural en todos los casos:

2010-B

a) Un MUX de 4 a 1 tiene lo siguiente:

Programa para el MUX de 4 a 1. HAREMOS LOS SIGUIENTES CAMBIOS: D1=IN1, D2=IN2, D3=IN3, D4=IN4, C1=IN5, C0=IN6, Y=OUT Library ieee; Use ieee.std_logic.1164.all; entity MUX_4_a_1 is port (IN1,IN2,IN3,IN4,IN5,IN6: in bit; OUT: out bit); end entity MUX_4_a_1; architecture LogicOperation of MUX_4_a_1 is //declaracin de componentes para una puerta AND de 3 entradas// component AND_gate3 is port (A,B,C: in bit X: out bit); end component AND_gate3; //declaracin de componentes para una puerta OR de 2 entradas// component OR_gate is port (A,B: in bit; X: out bit);

18 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

end component OR_gate: //declaracin de componentes para una entrada inversora// component Inverter is port (A: in bit; X: out bit); end component Inverter; signal G1OUT,G2OUT,G3OUT,G4OUT,G5OUT,G6OUT,G7OUT,G8OUT,G9OUT: bit; begin G1: Inverter port map (A=>IN5, X=>G1OUT); G2: Interver port map (B=>IN6, X=>G2OUT); G3: AND_gate3 port map (A=>IN1, B=>G1OUT, C=>G2OUT, X=>G3OUT); G4: AND_gate3 port map (A=>IN2, B=>G1OUT, C=>IN6, X=>G4OUT); G5: AND_gate3 port map (A=>IN3, B=>IN5, C=>G2OUT, X=>G5OUT); G6: AND_gate3 port map (A=>IN4, B=>IN5, C=>IN6, X=>G6OUT); G7: OR_gate port map (A=>G3OUT, B=>G4OUT, X=>G7OUT); G8 OR_gate port map (A=>G5OUT, B=>G6OUT, X=>G8OUT); G9 OR_gate port map (A=>G7OUT, B=>G8OUT, X=>OUT); end architecture LogicOperation; b) Un DEMUX de 1 a 4 tiene lo siguiente:

Programa para el DEMUX de 1 a 4. HAREMOS LOS SIGUIENTES CAMBIOS: C1=IN1, C0=IN2, E=IN3, A=OUT1, B=OUT2, C=OUT3, D=OUT4 Puesto que el DEMUX tiene 4 salidas(a funciones), tenemos: Library ieee; Use ieee.std_logic.1164.all; entity DEMUX_1_a_4 is port (IN1,IN2,IN3: in bit; OUT1,OUT2,OUT3,OUT4: out bit); end entity DEMUX_4_a_1; architecture LogicOperation of DEMUX_1_a_4 is component AND_gate3 is port (A,B,C: in bit X: out bit); end component AND_gate3;

19 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

component Inverter is port (A: in bit; X: out bit); end component Inverter; signal G5OUT, G6OUT: bit; begin G6: Inverter port map (A=>IN1, X=>G6OUT); G5: Inverter port map (A=>IN2, X=>G5OUT); G1: AND_gate3 port map (A=>G6OUT, B=>G5OUT, C=>IN3, X=>OUT1); G2: AND_gate3 port map (A=>G6OUT, B=>IN2, C=>IN3, X=>OUT2); G3: AND_gate3 port map (A=>IN1, B=>G5OUT, C=>IN3, X=>OUT3); G4: AND_gate3 port map (A=>IN1, B=>IN2, C=>IN3, X=>OUT4); end architecture LogicOperation;

2010-B

c) Un DECODER decimal 3/8 tiene lo siguiente.

Programa para el DECODER de 3 a 8. HAREMOS LOS SIGUIENTES CAMBIOS: A=IN1, B=IN2, C=IN3, Y0=OUT1, Y1=OUT2, Y2=OUT3, Y3=OUT4, Y4=OUT5, Y5=OUT6, Y6=OUT7, Y7=OUT8 Su programacin es la siguiente: Library ieee; Use ieee.std_logic.1164.all; entity DECORER_3_a_8 is port (IN1,IN2,IN3: in bit; OUT1,OUT2,OUT3,OUT4,OUT5,OUT6,OUT7,OUT8: out bit);

20 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

end entity DECORER_3_a_8; architecture LogicOperation of DECORER_3_a_8 is component AND_gate3 is port (A,B,C: in bit X: out bit); end component AND_gate3; component Inverter is port (A: in bit; X: out bit); end component Inverter; signal G9OUT,G10OUT,G11OUT: bit; begin G9: Inverter port map (A=>IN1, X=>G9OUT); G10: Inverter port map (A=>IN2, X=>G10OUT); G11: Inverter port map (A=>IN3, X=>G11OUT); G1: AND_gate3 port map (A=>G9OUT, B=>G10OUT, C=>G11OUT, X=>OUT1); G2: AND_gate3 port map (A=>G9OUT, B=>G10OUT, C=>IN3, X=>OUT2); G3 AND_gate3 port map (A=>G9OUT, B=>IN2, C=>G11OUT, X=>OUT3); G4 AND_gate3 port map (A=>G9OUT, B=>IN2, C=>IN3, X=>OUT4); G5 AND_gate3 port map (A=>IN1, B=>G10OUT, C=>G11OUT, X=>OUT5); G6 AND_gate3 port map (A=>IN1, B=>G10OUT, C=>IN3, X=>OUT6); G7 AND_gate3 port map (A=>IN1, B=>IN2, C=>G11OUT, X=>OUT7); G8 AND_gate3 port map (A=>IN1, B=>IN2, C=>IN3, X=>OUT8); end architecture LogicOperation; d) SUMADOR TOTAL. Recordemos: Un sumador acepta dos bits de entrada y un acarreo de entrada, y genera una salida de suma y un acarreo de salida.

) (

Library ieee; Use ieee.std_logic.1164.all; entity Sumador_completo is port (a, b, cin: in bit; s, cout: out bit); end entity Sumador_completo; architecture dataflow of Sumador_completo is begin s<=a XOR B XOR cin; cout<=(a AND b) OR (a AND cin) OR (b AND cin);

21 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

end dataflow; e) COMPARADOR BINARIO Un comparador binario de dos bits tiene lo siguiente:

2010-B

Haremos (

Library ieee; Use ieee.std_logic.1164.all; entity COMPARADOR_2_BITS is port (A1,A0,B1,B0: in bit; OUT1,OUT2,OUT3: out bit); end entity DECORER_3_a_8; architecture LogicOperation of COMPARADOR_2_BITS is component AND_gate is port (A,B: in bit; X: out bit); end component AND_gate; component AND_gate3 is port (A,B,C: in bit; X: out bit); end component AND_gate4; component AND_gate4 is port (A,B,C,D: in bit; X: out bit);

22 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

end component AND_gate4; component OR_gate is port (A,B: in bit; X: out bit): end component OR_gate; component Inverter is port (A: in bit; X: out bit); end component Inverter; signal G1OUT,G2OUT,G3OUT,G4OUT,G5OUT,G6OUT,G7OUT,G8OUT,G9OUT,G10OUT, G11OUT,G12OUT,G13OUT,G14OUT,G15OUT,G16OUT,G17OUT,G18OUT,G19OUT, G20OUT,G21OUT: bit; begin G1: Inverter port map (A=>IN1, X=>G1OUT); G2: Inverter port map (A=>IN2, X=>G2OUT); G3: Inverter port map (A=>IN3, X=>G3OUT); G4: Inverter port map (A=>IN4, X=>G4OUT); G5: AND_gate port map (A=>G1OUT, B=>IN3, X=>G5OUT); G6: AND_gate3 port map (A=>G1OUT, B=>G2OUT, C=>IN4, X=>G6OUT); G7: AND_gate3 port map (A=>G9OUT, B=>IN3, C=>IN4, X=>G7OUT); G8: AND_gate port map (A=>IN1, B=>G3OUT, X=>G8OUT); G9: AND_gate3 port map (A=>IN2, B=>G3OUT, C=>G4OUT, X=>G9OUT); G10: AND_gate3 port map (A=>IN1, B=>IN2, C=>G4OUT, X=>G10OUT); G11: AND_gate4 port map (A=>G1OUT, B=>G2OUT, C=>G3OUT, D=>G4OUT, X=>OUT7); G12: AND_gate4 port map (A=>G1OUT, B=>IN2, C=>G3OUT, D=>IN4, X=>G12OUT); G13: AND_gate4 port map (A=>IN1, B=>G2OUT, C=>IN3, D=>G4OUT, X=>G13OUT); G14: AND_gate4 port map (A=>IN1, B=>IN2, C=>IN3, D=>IN4, X=>G14OUT); G15: OR_gate port map (A=>G5OUT, B=>G6OUT, X=>G15OUT); G16: OR_gate port map (A=>G8OUT, B=>G9OUT, X=>G16OUT); G17: OR_gate port map (A=>G11OUT, B=>G12OUT, X=>G17OUT); G18: OR_gate port map (A=>G13OUT, B=>G14OUT, X=>G18OUT); G19: OR_gate port map (A=>G15OUT, B=>G7OUT, X=>OUT1); G20: OR_gate port map (A=>G16OUT, B=>G10OUT, X=>OUT2); G21: OR_gate port map (A=>G17OUT, B=>G18OUT, X=>OUT3); end architecture LogicOperation; f) FLIP-FLOP JK Library ieee; Use ieee.std_logic.1164.all; entity Flip_Flop_JK is port (sJ, sK, clock: in std_logic; : out std_logic; end Flip_Flop_JK; architecture Operation of Flip_Flop_JK is

23 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

begin process (sJ, sK, clock ) begin if (event clock and clock=1) then; if (sJ=0 and sK= 0) then ; ; elsif (sJ=0 and sK=1) then ; ; if (event clock and clock=1) then; if (sJ=1 and sK=0) then ; ; else ; ; end if; end process; end Operation; FLIP FLOP D Library ieee; Use ieee.std_logic.1164.all; entity Flip_Flop_D is port ( sD, CLK: in std_logic; sQ: out std_logic); end Flip_Flop_D; architecture Operation of Flip_Flop_D is begin process (CLK) begin if (CLK event and CLK=1) then sQ<=sD; end if; end process; end Operation; g) REGISTRO DE 4BITS Library ieee; Use ieee.std_logic.1164.all; entity REGISTER_4 is port (D:in stf_logic_vector (0 downto 3); Q: out std_logic_vector (0 downto 3); CLK: in std_logic; end REGISTER_4; architecture Operation of REGISTER_4 is begin process (CLK) begin if (event clock and clock=1) then;

2010-B

24 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

; end if; end process; end Operation;

2010-B

h) CONTADOR ASNCRONO DE MODULO 16 Library ieee; Use ieee.std_logic.1164.all; entity COUNTER_16 is port (Q:out std_logic_vector (0 downto 15) CLK: in std_logic;) end COUNTER_16; architecture Operation of COUNTER_16 is begin process (CLK) begin if (event clock an clock=1) then; end if; end process; end Operation;

PREGUNTA N9 Dado el circuito de la figura, formado por un registro de 4 bits y una ROM de 16x3, se pide responder lo siguiente: a) El circuito representado, Es una mquina de Mealy o de Moore? Discuta brevemente en qu te basas para realizar tu afirmacin.

25 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

b) Rellena la tabla de transiciones de estados del circuito, explica que funcin realiza el circuito y defnelo. Representa el funcionamiento mediante su diagrama de estados. c) Explica la secuencia de seales que activaras para hacer que el sistema comience a operar desde el estado 0 y evolucione hasta el estado 5, dibujando la forma de onda de las seales del circuito. Incluido el reloj. Cul es el mnimo nmero de ciclos de reloj que se necesitaran? d) Materializa el circuito mediante el nmero adecuado de biestables de tipo SR y puertas lgicas bsicas. e) Materializa el circuito mediante el tipo de biestables y mdulos y puertas bsicas combinacionales que prefieras.

SOLUCION a) Podemos ver que este circuito nicamente tiene 1 entrada independiente (SB), las otras 3 son de la ROM de 16x3. Adems notaremos que este circuito realiza un cambio dependiendo del valor de SB. Debido a que este cambio es dependiente de una variable ajena a los estados internos del circuito, puedo decir que se trata de una mquina de Mealy. b) Tenemos la siguiente tabla de transiciones: SB=0 001 011 100 101 110 SB=1 110 000 111 001 010

000 001 010 011 100

26 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

101 110 111 111 000 010 011 100 101

2010-B

Tal y como lo sospechaba, se trata de un contador, en este caso un escalador. La seal de control es la entrada SB. Representando a cada estado por la simbologa utilizada en clases, es decir, por ejemplo , y llevndolos al diagrama de grafos siguiente tenemos: 0 1 0 1 1 1 0 0 1 0 c) Viendo el diagrama de grafos del contador, vemos que el camino ms corto que realiza lo pedido (ir de 000 a 101) es la secuencia , donde en todos los casos se requiere que por SB ingrese un nivel bajo. 0 1 0 1 1 0

PREGUNTA N10 Para las tablas de estados mostrados, determinar: i. El tipo de FSM que corresponde. ii. Desarrollar el grafo correspondiente. iii. Disear los circuitos FSM, en cada caso, utilizando: a) Flip Flpos JK. b) Flip Flops T.

27 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

SOLUCION Para FSM 1 Es una mquina de Mealy, tenemos el siguiente diagrama de grafo. 0/0 X/0 0/0 1/1 1/1 0/0 1/0

Dando un cdigo binario a cada estado, tenemos: X 0 1 0 1 0 1 0 1 Y 0 0 0 1 0 0 0 1

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 0 1 0 X X X X

X X X X 1 0 0 1

1 1 X X 1 1 X X

X X 1 1 X X 1 0

0 0 1 0 1 0 0 1

1 1 1 1 1 1 1 0

0 0 1 0 0 1 1 0

1 1 0 0 1 1 0 1

28 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Para FSM 2 Es una mquina de Mealy, tenemos el siguiente diagrama de grafo.

Dando un cdigo binario a cada estado, tenemos: Y 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 1 0 1 1 0 1 1 X X X X X X X X

X X X X X X X X 1 0 0 0 0 0 1 0

0 1 0 1 X X X X 0 0 1 1 X X X X

X X X X 0 0 0 0 X X X X 0 0 1 0

0 1 0 1 1 0 1 1 1 0 0 0 0 0 1 0

0 1 0 1 0 0 0 0 0 0 1 1 0 0 1 0

0 1 0 1 1 0 1 1 0 1 1 1 1 1 0 1

0 1 0 1 1 1 1 1 0 0 1 1 1 1 0 1

29 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Para FSM 3 Es una mquina de Mealy, tenemos el siguiente diagrama de grafo.

Dando un cdigo binario a cada estado, tenemos: Y 0 0 0 0 1 1 0 0 1 0 X X X X X

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0

0 0 0 0 0 0 0 0 X X X X X X X

X X X X X X X X 1 0 0 0 0 0 1

1 0 0 0 X X X X 1 0 X X X X X

X X X X 0 0 0 1 X X X X X X X

0 0 X X 1 0 X X 0 0 X X X X X

X X 0 1 X X 0 0 X X X X X X X

0 0 0 0 0 0 0 0 1 1 X X X X X

1 0 0 0 0 0 0 1 1 0 X X X X X

0 0 0 1 1 0 0 0 0 0 X X X X X

0 0 0 0 0 0 0 0 0 0 X X X X X

1 0 0 0 1 1 1 0 1 0 X X X X X

0 0 1 0 1 0 1 1 0 0 X X X X X

30 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

1 1 1 1 X X 0 X X X X X X X X

2010-B

X X

Para FSM 4 Es una mquina de Mealy, tenemos el siguiente diagrama de grafo.

Dando un cdigo binario a cada estado, tenemos: Y 0 0 0 1 0 0 0 1

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

0 0 1 0 X X X X

X X X X 1 0 0 1

1 1 X X 1 1 X X

X X 1 1 X X 1 0

0 0 1 0 1 0 0 1

1 1 1 1 1 1 1 0

0 0 1 0 0 1 1 0

1 1 0 0 1 1 0 1

31 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

Para FSM 5 Es una mquina de Mealy, tenemos el siguiente diagrama de grafo.

Dando un cdigo binario a cada estado, tenemos: Y 1 0 0 0 0 1 0 0

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

1 0 1 0 X X X X

X X X X 0 1 1 0

1 1 X X 0 0 X X

X X 0 0 X X 1 1

1 0 1 0 1 1 1 0

1 1 0 0 0 0 1 1

1 0 1 0 1 0 0 1

1 1 1 1 0 0 0 0

32 Flores Pacheco Alonso Mario

082646H

TAREA DOMICILIARIA N2 DE SISTEMAS DIGITALES

2010-B

33 Flores Pacheco Alonso Mario

082646H

You might also like

- Informe ConferenciaDocument24 pagesInforme ConferenciaElvis ShahuanoNo ratings yet

- Informe ConferenciaDocument24 pagesInforme ConferenciaElvis ShahuanoNo ratings yet

- LAB5Document7 pagesLAB5Elvis ShahuanoNo ratings yet

- Laboratorio N3 CONTROLDocument5 pagesLaboratorio N3 CONTROLElvis ShahuanoNo ratings yet

- Solucionario Ex. FinalDocument5 pagesSolucionario Ex. FinalElvis ShahuanoNo ratings yet

- I2c Practico TC74Document10 pagesI2c Practico TC74Rafael ChavezNo ratings yet

- Linea Del Tiempo Del MicroprocesadorDocument1 pageLinea Del Tiempo Del MicroprocesadorHECTOR BENJAMIN MONTEPEQUE ALVARADONo ratings yet

- Arquitectura Interna Del ComputadorDocument5 pagesArquitectura Interna Del ComputadorDiego Cruz GonzalesNo ratings yet

- 2.3 Estructura Lógica de Un OrdenadorDocument8 pages2.3 Estructura Lógica de Un OrdenadorLuis UbeNo ratings yet

- Reconocimiento de MainboardDocument64 pagesReconocimiento de MainboardDarwin Jesús Arela QuispeNo ratings yet

- Primera Entrega Sistemas Digitales y EnsambladoresDocument2 pagesPrimera Entrega Sistemas Digitales y EnsambladoresAlexander JoyaNo ratings yet

- Capitulo 3 - Factor de Forma Atx-AtDocument11 pagesCapitulo 3 - Factor de Forma Atx-AtCesar Gabriel BallesterNo ratings yet

- 6Document12 pages6Panche RootNo ratings yet

- Elementos Básicos de Una ComputadoraDocument8 pagesElementos Básicos de Una ComputadoraAmylkr Ely Bravo SanchezNo ratings yet

- Quiz 1Document5 pagesQuiz 1Luis Fdo JaramilloNo ratings yet

- Clase 7 Detectores de Paridad y Comparadores AD2013 PDFDocument6 pagesClase 7 Detectores de Paridad y Comparadores AD2013 PDFJESUS ROBERTO SOLANO DURANNo ratings yet

- CONTROL DE AUTOMATIZACION DE UN SEMAFORO EN FLUID SIM Avance 2Document6 pagesCONTROL DE AUTOMATIZACION DE UN SEMAFORO EN FLUID SIM Avance 2backhuseinhotmail.com100% (1)

- El Entorno de DiseñoDocument30 pagesEl Entorno de DiseñoOsmel Gómez AcostaNo ratings yet

- Tarea UnidadDocument2 pagesTarea Unidadjhoiner100% (3)

- 1-Introduccion A La Informatica - PpsDocument16 pages1-Introduccion A La Informatica - PpsEver CallarelliNo ratings yet

- LCDDocument38 pagesLCDEddy León RamírezNo ratings yet

- Guia Practica 4 PDFDocument8 pagesGuia Practica 4 PDFJuanAldairRiveraDueñas0% (1)

- Descripcion de Las Caracteristicas Internas de La FPGA Spartan 2Document3 pagesDescripcion de Las Caracteristicas Internas de La FPGA Spartan 2Helen Sosa0% (1)

- Apuntes de MicrocontroladoresDocument66 pagesApuntes de MicrocontroladoresIgnacio CarvajalNo ratings yet

- Informe Digitales 2Document3 pagesInforme Digitales 2Jonathan QuilumbaquinNo ratings yet

- Arquitectura Semana 4Document77 pagesArquitectura Semana 4Victor Junco RenteraNo ratings yet

- Informe #1 MplabDocument6 pagesInforme #1 Mplabmauricio mesaNo ratings yet

- Practica Primer ParcialDocument4 pagesPractica Primer ParcialMauricio Calderon FrontanillaNo ratings yet

- Circuitos Digitales Trabajo 1Document12 pagesCircuitos Digitales Trabajo 1Jose Eduardo Villanueva FerrerNo ratings yet

- Bies TableDocument27 pagesBies TablemarialaurarodriguezNo ratings yet

- Practica 1 Electronica Digital (Tablas de Verdad)Document5 pagesPractica 1 Electronica Digital (Tablas de Verdad)Lalo GarzaNo ratings yet

- Arduino MoqueguaDocument65 pagesArduino Moqueguajoshua100% (1)

- T1 ProblemasDocument4 pagesT1 ProblemasMiguelMoretónNo ratings yet

- Memoria VirtualDocument10 pagesMemoria VirtualIvan Elias Carrasco LupintaNo ratings yet

- Ofimatica-UTESA Tarea 2Document5 pagesOfimatica-UTESA Tarea 2Melanie ValdezNo ratings yet