Professional Documents

Culture Documents

Contadores Digitais

Uploaded by

Ricardo AkermanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Contadores Digitais

Uploaded by

Ricardo AkermanCopyright:

Available Formats

Sistemas Digitais (I)

Trabalho de Laboratrio

ESTG

SISTEMAS DIGITAIS (I) CONTADORES

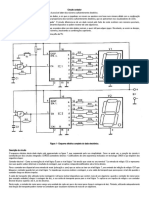

Introduo A capacidade de contar uma operao fundamental em electrnica digital. Um contador fornece uma sada binria igual ao nmero de impulsos binrios ocorridos na sua entrada. Os contadores podem ser construdos com flip flop's sendo o seu limite de contagem de 2n-1 em que n o nmero de flip flop's colocados em cascata. Neste trabalho utilizaremos alguns CI que j realizam a funo de contagem. Na primeira parte do trabalho utilizaremos um contador BCD (74190) para realizar a contagem de 0 a 9, um descodificador BCD para 7 segmentos (74LS48) e um display de 7 segmentos para observar a contagem. Na segunda parte do trabalho usaremos outro contador (74LS90) em cascata com o primeiro para podermos efectuar contagens at 99 e um segundo conjunto descodificador/display para observarmos a contagem. Usaremos ainda alguma lgica adicional para limitarmos a contagem de 0 a 59. Usaremos tambm um circuito baseado num flip flop para realizar a interface de uma chave mecnica que evita que o rudo existente no fechar e abrir do interruptor seja interpretado pelo contador como vrias transies do impulso de entrada. Objectivos So objectivos deste trabalho a familiarizao com os CI contadores, descodificadores e displays, bem como a sua interligao e funcionamento. Material 1 CI 74LS190 ou 74HCT190 contador BCD 1 CI 74LS90 contador decimal 2 CI 74LS48 descodificador BCD para 7 segmentos de ctodo comum 1 CI 74LS01 quatro NAND de duas entradas 1 Display duplo de ctodo comum 10 resistncias de 1M 1 Interruptor 1 Placa de ligao 1 Fonte de alimentao de 0 e 5 V.

2003/04

JPT

Sistemas Digitais (I)

Trabalho de Laboratrio

ESTG

1 Parte - Contador Decimal Nesta montagem vai usar os circuitos integrados 74190 (74LS190 OU 74HCT190) e o CI 74LS48. Para conhecer o seu funcionamento aconselha-se uma consulta folha de caractersticas destes CI's. O CI 74LS190 um contador sncrono, BCD que efectua, portanto, contagens entre 0 e 9, reversvel (up/down) e pr-ajustvel. As suas sadas so actualizadas transio ascendente do clock. Este contador tem uma linha de "count enable" CTEN, activa ao nvel baixo, que permite habilitar o contador a efectuar contagem. Contm uma linha de controlo do modo ascendente/descendente D/U. Contm tambm uma linha LOAD, activa ao nvel baixo, que permite efectuar um pr ajuste do valor de contagem inicial com o valor das linhas de entrada DCBA. Contm ainda duas linhas de sada max/min e RCO que indicam quando o contador passa do seu valor final ao valor inicial (9->0). O CI 74LS48 um descodificador de BCD para 7 segmentos. Dispe de uma linha de teste LT ("lamp test"), activa ao nvel baixo, que permite verificar se todos os 7 segmentos acendem. Dispe ainda de uma linha RBI, activa ao nvel baixo, que permite apagar o display quando este tem valor nulo sua entrada. O display duplo de que dispe de ctodo comum, indicado pelas linhas gnd. O "pinout" deste dispositivo o indicado no desenho do circuito. Procedimento 1. Usando o circuito 1 em anexo identifique (escrevendo no circuito) o nmero do pino dos CI correspondente a cada linha que vai usar. 2. Disponha os circuitos integrados que vai usar (nas 1 e 2 partes do trabalho) pela placa de ligao de forma homognea. 3. Defina as linhas que vai usar para massa e alimentao. 4. Ligue as linhas de alimentao dos CI, procurando usar fios de cores sugestivas. 5. Implemente de forma metdica e atenta o circuito contador. (Lembre-se que a melhor forma de corrigir erros evit-los). Tenha o cuidado de deixar espao por cima dos CI's para os poder retirar sem desmontar o circuito. 6. Use etiquetas para identificar os fios correspondentes a cada interruptor. 7. Coloque a linha CTEN do contador a 0. Teste o funcionamento do circuito contador respondendo s questes que se seguem. 8. Teste o funcionamento do contador em modo ascendente e em modo descendente. 9. Experimente ajustar o contador num valor inicial diferente de zero. Registe a sequncia de contagem. 10. Desfaa a ligao da sada da porta NAND entrada de clock do contador e coloque uma resistncia de pull down para simular um interruptor manual. Experimente o funcionamento do contador com este interruptor. 11. Refaa a ligao desfeita na alnea anterior. 12. Substitua a entrada de clock por um sinal rectangular com uma frequncia de 1 Hz gerado pelo gerador de sinal. Verifique a sequncia de contagem.

2003/04

JPT

Sistemas Digitais (I)

Trabalho de Laboratrio

ESTG

Questes 1. Qual a funcionalidade das linhas LOAD, D/U e CTEN do contador? 2. Qual a funcionalidade das linhas LT e RBI do descodificador? 3. Explique a funcionalidade do circuito de interface da chave com a linha de clock. 2 Parte - Contagem at 60 Nesta parte do trabalho pretende-se que implemente o circuito 2 em anexo que realiza contagens entre 0 e 59. Para isso, usar as restantes portas NAND do CI 74LS01 e o segundo digito do display. Usar o CI 74LS90 que um contador decimal. A ligao da sada QA entrada de clock B faz este CI funcionar como um contador decimal. O "reset" deste contador feito com as duas entradas de R0 ao nvel alto e uma entrada R9 ao nvel baixo. Procedimento 1. Usando o circuito 2 em anexo identifique (escrevendo no circuito) o nmero do pino dos CI correspondente a cada linha que vai usar. 2. Implemente de forma metdica e atenta o circuito contador. (Lembre-se que a melhor forma de corrigir erros evit-los). Tenha o cuidado de deixar espao por cima dos CI's para os poder retirar sem desmontar o circuito. 3. Use etiquetas para identificar os fios correspondentes a cada interruptor. 4. Teste o funcionamento do circuito. Para isso, ligue novamente um sinal rectangular com uma frequncia de 1 Hz gerado pelo gerador de sinal na entrado de clock do primeiro contador. Verifique a sequncia de contagem. Questes 1. Porque razo ligou R0(1) e R0(2) a Qb e Qc, R9(2) a gnd e deixou R9(1) no ar ? 2. Por que que ligou a sada max/min, e no RCO, do primeiro contador entrada de clock A do segundo contador ? 3. O que alteraria no circuito se pretende-se que a contagem fosse apenas at 29 ?

2003/04

JPT

Sistemas Digitais (I)

Trabalho de Laboratrio

ESTG

Vcc

CTEN D/U Vcc 1M

LOAD

CTEN D/U LOAD CLK

D C B A

Vcc 1M

74LS190

QD QC QB QA

Vcc

LT

RBI

LT

RBI

D C B A

74LS48

a b c d e f

f1 g1 a1 b1 gnd1 gnd2 f2 a2 b2

e1 d1 c1 h1 e2

d2 g2 c2 h2 4

2003/04

JPT

Sistemas Digitais (I)

Trabalho de Laboratrio

ESTG

Vcc

CTEN Vcc 1M

D/U

LOAD R0(1) R0(2) R9(1) R9(2)

CTEN D/U LOAD CLK

D C B A max/min

Vcc 1M

74LS190

CLKA CLKB

74LS90

QD QC QB QA

QD QC QB QA

Vcc

Vcc

LT

RBI

LT

RBI

D C B A

LT

RBI

LT

RBI

D C B A

74LS48

74LS48

4 4 3

f1 g1 a1 b1 gnd1 gnd2 f2 a2 b2 4

e1 d1 c1 h1 3

e2

d2

g2 c2 h2 4

2003/04

JPT

You might also like

- 2a Lista de Exercicios de Sistemas Digitais I 1 2012Document8 pages2a Lista de Exercicios de Sistemas Digitais I 1 2012Alexandre JuniorNo ratings yet

- Cronômetro digital com LogisimDocument11 pagesCronômetro digital com LogisimRosCibelyNo ratings yet

- Manual YAMAHA PSR-640Document42 pagesManual YAMAHA PSR-640ClarkCassyNo ratings yet

- Coletanea Probabilidades Sinal+Document25 pagesColetanea Probabilidades Sinal+.No ratings yet

- Coletanea - Probabilidades - Versão 2Document23 pagesColetanea - Probabilidades - Versão 2isabel silvaNo ratings yet

- Apostila Fisica Aplicada À EngenhariaDocument81 pagesApostila Fisica Aplicada À EngenhariaAllecxsNo ratings yet

- Curso Raciocínio Logico CompletoDocument1 pageCurso Raciocínio Logico CompletoConcurseiro BrasileiroNo ratings yet

- Área e volume do cilindro: fórmulas e exercícios resolvidosDocument5 pagesÁrea e volume do cilindro: fórmulas e exercícios resolvidosSoliene da Silva100% (1)

- Conceitos GrafosDocument31 pagesConceitos GrafosKarina MartinsNo ratings yet

- Atividade 1-Matemática BásicaDocument1 pageAtividade 1-Matemática Básicaarthur sengerNo ratings yet

- Aula Arte 05 - Arte de PapelDocument7 pagesAula Arte 05 - Arte de PapelPriscila SantosNo ratings yet

- Lista Exercicios FTC 01 2008Document32 pagesLista Exercicios FTC 01 2008Ratao890% (1)

- Projeto geométrico de rodoviasDocument107 pagesProjeto geométrico de rodoviasitamaridlNo ratings yet

- OrigamiDocument31 pagesOrigamiMarcos PlácidoNo ratings yet

- Construção de gráficos em escala mono-logarítmicaDocument8 pagesConstrução de gráficos em escala mono-logarítmicaRafaelNo ratings yet

- Cálculo Numérico - Lista N°2 com problemas de integrais, derivadas numéricas e interpolaçãoDocument3 pagesCálculo Numérico - Lista N°2 com problemas de integrais, derivadas numéricas e interpolaçãoHendrick ZarateNo ratings yet

- Origami: Arte japonesa de dobrar papelDocument11 pagesOrigami: Arte japonesa de dobrar papeljose joaquim da costa fonsecaNo ratings yet

- Solução de placas retangulares por diferenças finitasDocument19 pagesSolução de placas retangulares por diferenças finitasFilipe GuedesNo ratings yet

- Modelos de pipa passo-a-passoDocument30 pagesModelos de pipa passo-a-passojacintojuniorNo ratings yet

- Curvas cíclicas: ciclóide, epiciclóide e hipociclóideDocument5 pagesCurvas cíclicas: ciclóide, epiciclóide e hipociclóideCezzar OliveiraNo ratings yet

- Processo seletivo 2018 ensino técnicoDocument19 pagesProcesso seletivo 2018 ensino técnicoCamila Assis0% (1)

- Freqüencímetro Digital de Bancada ICEL FC-2700Document13 pagesFreqüencímetro Digital de Bancada ICEL FC-2700scanner139No ratings yet

- Deduzindo as equações de campo de EinsteinDocument3 pagesDeduzindo as equações de campo de EinsteinPedro VenturaNo ratings yet

- Modelo artigo PIBICDocument2 pagesModelo artigo PIBICRoniCasaNo ratings yet

- Geometria Esférica: Fundamentos e Conceitos BásicosDocument86 pagesGeometria Esférica: Fundamentos e Conceitos BásicosJoão Felipe SantelliNo ratings yet

- Aula 25 e 26 exercícios tolerânciasDocument2 pagesAula 25 e 26 exercícios tolerânciasAlexander Luthor100% (1)

- Trabalho IsometriasDocument10 pagesTrabalho IsometriasÂngelo MarianoNo ratings yet

- Geometria espacial posição lista questõesDocument1 pageGeometria espacial posição lista questõesAna Claudia ZaqueuNo ratings yet

- Como Resolver Circuitos Misto em 4 PassosDocument5 pagesComo Resolver Circuitos Misto em 4 PassosDiego Ferreira da SilvaNo ratings yet

- Módulo I Matemática Aplicada A Logística: 3 Edição - 2022Document26 pagesMódulo I Matemática Aplicada A Logística: 3 Edição - 2022Israel ConstantinoNo ratings yet

- Pêndulo SimplesDocument2 pagesPêndulo Simplesbrusribeiro100% (1)

- Matemática Solon Aulas 5 e 6 Previsão 2023Document33 pagesMatemática Solon Aulas 5 e 6 Previsão 2023alice.c.freire.alNo ratings yet

- Calculo 2Document2 pagesCalculo 2fernando meloNo ratings yet

- Tronco de ConeDocument9 pagesTronco de Conedfremy50% (2)

- Experimento 01Document5 pagesExperimento 01Magna NegreirosNo ratings yet

- Sólidos de RevoluçãoDocument12 pagesSólidos de RevoluçãoLeandro ZardoNo ratings yet

- Shuki Kato Origami Nature Study PDFDocument243 pagesShuki Kato Origami Nature Study PDFDynamic MightNo ratings yet

- Trigonometria: Lei dos Senos e CossenosDocument11 pagesTrigonometria: Lei dos Senos e CossenosSara Vitória CarvalhoNo ratings yet

- 1º Ano - Funções TrigonometricasDocument110 pages1º Ano - Funções TrigonometricasProf. Pedro ValentimNo ratings yet

- Cronômetro DigitalDocument6 pagesCronômetro Digitalpaulohss1985No ratings yet

- Relatório - Elaboração de Um ContadorDocument13 pagesRelatório - Elaboração de Um ContadorMatheus AraujoNo ratings yet

- Circuito contador aleatório de dois númerosDocument5 pagesCircuito contador aleatório de dois númerosRonaldo RochaNo ratings yet

- Cronômetro DigitalDocument5 pagesCronômetro DigitalDavid Da Silva BorgesNo ratings yet

- Projeto de relógio digital PLDDocument5 pagesProjeto de relógio digital PLDWeslley AlmeidaNo ratings yet

- Portas lógicas: Coletor aberto, Tri-state e Schmitt triggerDocument6 pagesPortas lógicas: Coletor aberto, Tri-state e Schmitt triggerRobert MaxelNo ratings yet

- Relatório Técnico Projeto Final Electra 2010Document16 pagesRelatório Técnico Projeto Final Electra 2010Ricardo AkermanNo ratings yet

- Caderno Questoes Eletronica Ed113 FinalDocument27 pagesCaderno Questoes Eletronica Ed113 Finalzdn100% (1)

- Cronometro DigitalDocument5 pagesCronometro DigitalJosevaldo ArrudaNo ratings yet

- CLP-Questões-Técnico-EletrotécnicaDocument5 pagesCLP-Questões-Técnico-EletrotécnicabetoNo ratings yet

- Automação II: CLP, programação e aplicaçõesDocument99 pagesAutomação II: CLP, programação e aplicaçõeswa_moreira100% (2)

- Projeto de Um Micro-Clp de Baixo Custo Com Programação em LadderDocument10 pagesProjeto de Um Micro-Clp de Baixo Custo Com Programação em Ladderluis gomezNo ratings yet

- Desenvolvendo Um Display Indicador De Atendimento Com ArduinoFrom EverandDesenvolvendo Um Display Indicador De Atendimento Com ArduinoNo ratings yet

- Relógio Digital Com DespertadorDocument4 pagesRelógio Digital Com DespertadormarcelolucasbrNo ratings yet

- Contador Binário 7490 e 4511 Com Display e LedsDocument9 pagesContador Binário 7490 e 4511 Com Display e LedssergioNo ratings yet

- Controlador Motor PassoDocument36 pagesControlador Motor PassoBernardo CamposNo ratings yet

- Aprendendo A Programar - Programando Na Linguagem CDocument139 pagesAprendendo A Programar - Programando Na Linguagem CAllanDenis100% (5)

- Palestra NBR 5410Document23 pagesPalestra NBR 5410renanjpedrosaNo ratings yet

- Recon MTDocument70 pagesRecon MTTatiana de SouzaNo ratings yet

- Metrologia PDFDocument89 pagesMetrologia PDFSergio Gomes Ferreira86% (7)

- Ferramentas PDFDocument59 pagesFerramentas PDFSergio Gomes Ferreira100% (21)

- Relatório Técnico Projeto Final Electra 2010Document16 pagesRelatório Técnico Projeto Final Electra 2010Ricardo AkermanNo ratings yet

- Guia Rápido de Manutenção Da Y-35Document4 pagesGuia Rápido de Manutenção Da Y-35Ricardo AkermanNo ratings yet

- Segurancaintrinseca PDFDocument68 pagesSegurancaintrinseca PDFSergio Gomes Ferreira100% (5)

- Trabalho de Linhas de Transmissão de 12.09Document16 pagesTrabalho de Linhas de Transmissão de 12.09Ricardo AkermanNo ratings yet

- Caldeiraria TraçadosDocument141 pagesCaldeiraria Traçadossancosta77783% (6)

- Segurança Do Trabalho PDFDocument126 pagesSegurança Do Trabalho PDFsancosta777100% (1)

- Instrumentacaobasica2 PDFDocument242 pagesInstrumentacaobasica2 PDFSergio Gomes Ferreira100% (5)

- SENAI-Eletrotecnica BasicaDocument198 pagesSENAI-Eletrotecnica BasicaAntonio Italo LunaNo ratings yet

- Valvula PDFDocument180 pagesValvula PDFSergio Gomes Ferreira100% (40)

- Instrumentação Basica1 PDFDocument123 pagesInstrumentação Basica1 PDFsancosta777No ratings yet

- Tabela Kva - CV - AmperesDocument1 pageTabela Kva - CV - Amperesjorge_lyon111973% (11)

- Eletronicageral PDF Apostila Senai PetrobrasDocument127 pagesEletronicageral PDF Apostila Senai Petrobrasanon-71165167% (3)

- Metrologia ElétricaDocument131 pagesMetrologia Elétricawinstontecnico100% (1)

- Ladder PLCDocument46 pagesLadder PLCHugo Bernard ArmondNo ratings yet

- Materiais Equipamentos2Document98 pagesMateriais Equipamentos2sancosta777No ratings yet

- Apostilas - Senai - A BasicaDocument125 pagesApostilas - Senai - A BasicagilbertolealNo ratings yet

- Eletrica - SENAI - Medidas EletricasDocument57 pagesEletrica - SENAI - Medidas Eletricasanon-721944100% (19)

- SENAI Ferramentas EletricasDocument88 pagesSENAI Ferramentas EletricasLuminariaeluz100% (4)

- Catalogo Eletrocalha MEGADocument6 pagesCatalogo Eletrocalha MEGARicardo Akerman75% (4)

- Desenhos EletricosDocument61 pagesDesenhos Eletricosirving100% (1)

- Medidor de Condutividade Digimed TC 406Document2 pagesMedidor de Condutividade Digimed TC 406Ricardo AkermanNo ratings yet

- Apostila CLP Com Exercícios para o Clic Da WegDocument44 pagesApostila CLP Com Exercícios para o Clic Da Wegjpbn185% (34)

- K0001 - Multimedidor Mult-K (Rev06)Document6 pagesK0001 - Multimedidor Mult-K (Rev06)Ricardo AkermanNo ratings yet

- Tabela de Amperagem de Cabos ElétricosDocument1 pageTabela de Amperagem de Cabos ElétricosRicardo AkermanNo ratings yet

- Inova 2 Da TaskDocument1 pageInova 2 Da TaskRicardo AkermanNo ratings yet

- Circuitos Codificadores e DecodificadoresDocument15 pagesCircuitos Codificadores e DecodificadoresNathan SousaNo ratings yet

- Sistemas de Numeração e CódigosDocument4 pagesSistemas de Numeração e CódigosTiago Miguel VidinhaNo ratings yet

- Noções Básicas Programação Step7Document13 pagesNoções Básicas Programação Step7Jose Marques Junior100% (1)

- Curso Eletrônica DigitalDocument88 pagesCurso Eletrônica DigitalvaldeiraguiarNo ratings yet

- Circuitos CombinacionaisDocument5 pagesCircuitos CombinacionaisResimasNo ratings yet

- Microprocessador 8085 - Arquitetura, Pinagem, Instruções e Sistema MínimoDocument51 pagesMicroprocessador 8085 - Arquitetura, Pinagem, Instruções e Sistema MínimoMaickson LeãoNo ratings yet

- Relatório Decodificador BCD7 SegmentosDocument9 pagesRelatório Decodificador BCD7 SegmentosVitória Loureiro PimentelNo ratings yet

- Conversor binário para BCDDocument11 pagesConversor binário para BCDGabriel Miro100% (1)

- Circuitos Digitais ExercíciosDocument15 pagesCircuitos Digitais ExercíciosAdriano SantosNo ratings yet

- Codificação BCDDocument3 pagesCodificação BCDalltomatizeNo ratings yet

- Sistemas de numeração binária, decimal e hexadecimalDocument15 pagesSistemas de numeração binária, decimal e hexadecimalOster GoulartNo ratings yet

- Arquitetura de Computadores Universidade Guarulhos Prof Erwin A UhlmannDocument12 pagesArquitetura de Computadores Universidade Guarulhos Prof Erwin A UhlmannFoto AdonayNo ratings yet

- Circuitos Codificadores e DecodificadoresDocument5 pagesCircuitos Codificadores e DecodificadoresAugusto Ribas HermesNo ratings yet

- UFMS Lógica Digital Códigos numéricos e alfanuméricosDocument47 pagesUFMS Lógica Digital Códigos numéricos e alfanuméricosLucas SilvaNo ratings yet

- Simulação de lançamento de dados e geração de números aleatóriosDocument8 pagesSimulação de lançamento de dados e geração de números aleatóriosGame PassNo ratings yet

- O Sistema BinárioDocument10 pagesO Sistema BináriocavilaiNo ratings yet

- Livro Texto - Unidade IIIDocument48 pagesLivro Texto - Unidade IIIGeovana DaniellaNo ratings yet

- Aula 7 - Codificadores e DecodificadoresDocument56 pagesAula 7 - Codificadores e Decodificadoresluciel castroNo ratings yet

- 03 Apostila Automação Industrial Por CLP 105 PágDocument105 pages03 Apostila Automação Industrial Por CLP 105 PágTiago José de CamposNo ratings yet

- S7 AvançadoDocument372 pagesS7 AvançadoIvanir Ferreira da SilvaNo ratings yet

- Codificadores e DecodificadoresDocument13 pagesCodificadores e DecodificadoresEngenharia ElétricaNo ratings yet

- Cálculo NuméricoDocument103 pagesCálculo NuméricoLucasPeerMartinsNo ratings yet

- Fundamentos da programação para sistemas embarcadosDocument82 pagesFundamentos da programação para sistemas embarcadosmcbneto5470No ratings yet

- Slides - AcessibilidadeDocument55 pagesSlides - Acessibilidademcb mcbNo ratings yet

- Sistemas Numeração Codificação DadosDocument17 pagesSistemas Numeração Codificação DadosJoao Paulo John PaulNo ratings yet

- Notas de Aula 01 AlunoDocument25 pagesNotas de Aula 01 AlunoDonaldo QuissicoNo ratings yet

- Cap 9Document47 pagesCap 9Bruno MigueresNo ratings yet

- PLANIFICAÇÃO ANUAL DE CONTEÚDOS Curso Profissional de Técnico de Inst. Elétricas 2012 - 2013 Eletricidade e Eletrónica (117 H 156t)Document5 pagesPLANIFICAÇÃO ANUAL DE CONTEÚDOS Curso Profissional de Técnico de Inst. Elétricas 2012 - 2013 Eletricidade e Eletrónica (117 H 156t)Magda RafaelNo ratings yet

- Lista de Exercícios Sobre Lógica CombinacionalDocument7 pagesLista de Exercícios Sobre Lógica CombinacionalLorde-SanNo ratings yet

- Unidade Aritmética 4 bitsDocument32 pagesUnidade Aritmética 4 bitsCaio PegoraroNo ratings yet