Professional Documents

Culture Documents

IJCER (WWW - Ijceronline.com) International Journal of Computational Engineering Research

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IJCER (WWW - Ijceronline.com) International Journal of Computational Engineering Research

Copyright:

Available Formats

International Journal Of Computational Engineering Research (ijceronline.com) Vol. 2 Issue.

FPGA Implementation and Functional Verification of a Pipelined MIPS Processor

1

1, 2, 3

PG Scholor, 2 Asst. Professors, 3Assoc. Professor, Avanthis St. Theressa Institute of Engineering & Technology, Garividi ,A.P.

Balaji valli, 2 A. Uday Kumar, 3 B.Vijay Bhaskar

1

Abstract:

This project targets the implementation design of a pipelined MIPS RISC Processor using VHDL (Very high speed integrated circuit Hardware Description Language). In this paper MIPS instruction format, instruction data path, decoder modules are analyzed. Furthermore, instruction fetch (IF) module of a CPU is designed based on RISC CPU instruction set. Function of IF module mainly includes fetch instruction and latch module address arithmetic module check validity of instruction module synchronous control module.

Keywords: MIPS, RISC, CPU, VHDL, FPGA, ID, IF, EX, MEM 1. Introduction

Pipeline is one of the basic techniques to improve the CPUs performance. This paper based on MIPS instruction set, designed a five-stage pipeline CPU. MIPS processor is basically a RISC micro processor. RISC CPU has extensive use in embedded system. Developing CPU with RISC structure is necessary choice. The MIPS Architecture defines thirty-two, 32-bit general purpose registers (GPRs). Instruction Set Architecture (ISA) of processor is composed of instruction set and corresponding registers. Program based on same ISA can run on the same instruction set. MIPS instruction has been developed from 32-bit MIPSI to 64-bit MIPSIII and MIPSIV since it was created. To assure downward compatibility, every generation production of MIPS instruction directly extends new instruction based on old instruction but not abnegates any old instruction, so MIPS processor of 64-bit instruction set can execute 32-bit instruction.

2. Implementation of Pipelined MIPS Processor

There are three formats of MIPS instructions: (i) Register Format (R-type) OPCODE (31 to 26) RS (25to21) RT (20to16) RD (15to11) Shift (10to6) FUN (5to 0)

The first two 5-bit register specifications are the two read registers and the last 5-bit register specification is the destination register, that the instruction will use. The last 6-bits in the instruction are used as function bits. (ii) Immediate Format (I-type) OPCODE (31 to 26) RS (25to21) RT (20to16) RD (15to11) Shift (10to6) FUN (5to 0)

The I-type is similar to the R-type except the second read register and the 5 function bits are replaced by a 16-bit immediate value. Each I-type opcode can have only one instruction because it has no function bits like the R-type. (iii) Jump Type Format (J- type) The J-type format consists of a 6-bit opcode and remaining bit indicates branching address. OPCODE (31 to 26) RS (25to21) RT (20to16) RD (15to11) Shift (10to6) FUN (5to 0)

3. Architecture

The MIPS pipelined processor involves five steps, the division of an instruction into five stages implies a five-stage pipeline: 1. Instruction Fetch (IF): fetching the instruction from the memory 2. Instruction Decode (ID): reading the registers and decoding the instruction

Issn 2250-3005(online) September| 2012 Page 1559

International Journal Of Computational Engineering Research (ijceronline.com) Vol. 2 Issue. 5

3. Execution (EX): executing an operation or calculating an address 4. Data Memory (MEM): accessing the data memory 5. Write Back (WB): writing the result into a register. The key to pipelining the single-cycle implementation of the MIPS processor is the introduction of pipeline registers that are used to separate the data path into the five sections IF, ID, EX, MEM and WB. Pipeline registers are used to store the values used by an instruction as it proceeds through the subsequent stages. The MIPS pipelined registers are labeled according to the stages they separate. (e.g. IF/ID, ID/EX, EX/MEM, MEM/WB)

Fig.1. Pipelined MIPS Processor To implement the MIPS pipelined processor, pipeline registers are placed into the corresponding VHDL modules that generate the input to the particular pipeline register. For example, the Instruction Fetch component will generate the 32-bit instruction and the PC+4 value and store them into the IF/ID pipeline register. When that instruction moves to the Instruction Decode stages it extracts those saved values from the IF/ID pipeline register.

4. RESULTS

Implementation is done using XILINX 10.1. RTL schematic and Floor plan view are shown in Fig.3 and Fig.4. Simulation snap is shown in Fig.2.

Fig.2. Functional simulation

Issn 2250-3005(online)

September| 2012

Page 1560

International Journal Of Computational Engineering Research (ijceronline.com) Vol. 2 Issue. 5

Fig.3. RTL Schematic

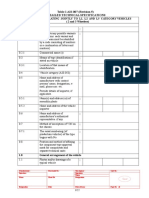

Fig.4. Floor Plan View Hardware utilization summery is reported in Table. 1. S.No. 1. 2. 3. 4. Logic Utilization Number of Slices Number of Slice Flip Flops Number of 4input LUTs Number of bonded IOBs Utilized Hardware 354 256 458 85

Table 1. Device Utilization Summery

5. Conclusion

In this paper, top-down design method adopted and VHDL is used for the implementation. Design is implemented on XILINX 11.1. Data Memory and Instruction Memory are generated using XILINX COREGEN.

REFERENCES

[1]

[2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] Hui Ma, Dinglei Wang, The Design of Five-stage Pipeline CPU Based on MIPS, 978-1-4244-8165-1/11, 2011 IEEE. Mrs. Rupali S. Balpande, Mrs.Rashmi S. Keote, Design of FPGA based Instruction Fetch & Decode Module of 32-bit RISC (MIPS) Processor, 2011 International Conference on Communication Systems and Network Technologies, 978-0-7695-4437-3/11, 2011 IEEE, Wang-Yuan Zhen, IBM-PC Macro Asm Program, Huazhong University of Science and Technology Press, 1996.9. MIPS Technologies, Inc. MIPS32 Architecture For Programmers Volume II: The MIPS32 Instruction Set June 9, 2003. Zheng-WeiMin, Tang-ZhiZhong. Computer System Structure (The second edition), Tsinghua University Press, 2006. Pan-Song, Huang-JiYe, SOPC Technology Utility Tutorial, Tsinghua University Press, 2006. MIPS32 4KTMProcessor Core Family Software User's Manual, MIPS Technologies Inc. [M]. BeiJing, Engine Industry Press. 2003. Yi-Kui, Ding-YueHua, Application of AMCCS5933 Controller in PCI BUS, DCABES2007, 2007.7.759 Rapid Prototyping of digital Systems, a tutorial approach By James O. Hamblen and Michael D.Furman. Charles E. Gimarc, Veljko M. Mhtinovic, "RISC Principles, Architecture, and Design", Computer Science Press Inc., 1989. Whte paper, "Wide range of comprehensive tools speed, Development of high-pafomance embedded system", MIPS Technologies Inc.,hnp:/lwww.mips.com/whitepapers/030399Wl .hml (current Sep. 30,2002). S. Chen, B. Mulgrew, and P. M. Gran< "A clustering technique for digital communications channel equalization using radial basis function networks," EEE Trans. Neuml Nerworkr, vol. 4, pp. 570-578, July 1993.

Issn 2250-3005(online)

September| 2012

Page 1561

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Effect of Bottom Sediment Transport On Wave Set-UpDocument10 pagesThe Effect of Bottom Sediment Transport On Wave Set-UpInternational Journal of computational Engineering research (IJCER)No ratings yet

- Analysis of The Pedestrian System in Jayapura City (A Case Study of Pedestrian Line On Percetakan StreetDocument9 pagesAnalysis of The Pedestrian System in Jayapura City (A Case Study of Pedestrian Line On Percetakan StreetInternational Journal of computational Engineering research (IJCER)No ratings yet

- An Analysis of The Noise Level at The Residential Area As The Impact of Flight Operations at The International Airport of Sultan Hasanuddin Maros in South Sulawesi ProvinceDocument4 pagesAn Analysis of The Noise Level at The Residential Area As The Impact of Flight Operations at The International Airport of Sultan Hasanuddin Maros in South Sulawesi ProvinceInternational Journal of computational Engineering research (IJCER)No ratings yet

- An Analysis of The Implementation of Work Safety System in Underpass Development Projects of The Intersection of Mandai Makassar-IndonesiaDocument5 pagesAn Analysis of The Implementation of Work Safety System in Underpass Development Projects of The Intersection of Mandai Makassar-IndonesiaInternational Journal of computational Engineering research (IJCER)No ratings yet

- Stiffness Analysis of Two Wheeler Tyre Using Air, Nitrogen and Argon As Inflating FluidsDocument8 pagesStiffness Analysis of Two Wheeler Tyre Using Air, Nitrogen and Argon As Inflating FluidsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Wave-Current Interaction Model On An Exponential ProfileDocument10 pagesWave-Current Interaction Model On An Exponential ProfileInternational Journal of computational Engineering research (IJCER)No ratings yet

- Analysis of Metamaterial Based Microstrip Array AntennaDocument2 pagesAnalysis of Metamaterial Based Microstrip Array AntennaInternational Journal of computational Engineering research (IJCER)No ratings yet

- Parametric Study On Analysis and Design of Permanently Anchored Secant Pile Wall For Earthquake LoadingDocument16 pagesParametric Study On Analysis and Design of Permanently Anchored Secant Pile Wall For Earthquake LoadingInternational Journal of computational Engineering research (IJCER)No ratings yet

- Parametric Study On Analysis and Design of Permanently Anchored Secant Pile Wall For Earthquake LoadingDocument16 pagesParametric Study On Analysis and Design of Permanently Anchored Secant Pile Wall For Earthquake LoadingInternational Journal of computational Engineering research (IJCER)No ratings yet

- The Influence of Price Offers For Procurement of Goods and Services On The Quality of Road ConstructionsDocument7 pagesThe Influence of Price Offers For Procurement of Goods and Services On The Quality of Road ConstructionsInternational Journal of computational Engineering research (IJCER)No ratings yet

- A Real Time Abandoned Object Detection and Addressing Using IoTDocument5 pagesA Real Time Abandoned Object Detection and Addressing Using IoTInternational Journal of computational Engineering research (IJCER)No ratings yet

- A Real Time Abandoned Object Detection and Addressing Using IoTDocument5 pagesA Real Time Abandoned Object Detection and Addressing Using IoTInternational Journal of computational Engineering research (IJCER)No ratings yet

- The Influence of Price Offers For Procurement of Goods and Services On The Quality of Road ConstructionsDocument7 pagesThe Influence of Price Offers For Procurement of Goods and Services On The Quality of Road ConstructionsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Comparison of Different Evapotranspiration Estimation Techniques For Mohanpur, Nadia District, West BengalDocument7 pagesComparison of Different Evapotranspiration Estimation Techniques For Mohanpur, Nadia District, West BengalInternational Journal of computational Engineering research (IJCER)No ratings yet

- A Holistic Approach For Determining The Characteristic Flow On Kangsabati CatchmentDocument8 pagesA Holistic Approach For Determining The Characteristic Flow On Kangsabati CatchmentInternational Journal of computational Engineering research (IJCER)No ratings yet

- Drag Optimization of Bluff Bodies Using CFD For Aerodynamic ApplicationsDocument8 pagesDrag Optimization of Bluff Bodies Using CFD For Aerodynamic ApplicationsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Effect of The Nipah Mall Development On The Performance Roads of Urip Sumohardjo in Makassar CityDocument5 pagesEffect of The Nipah Mall Development On The Performance Roads of Urip Sumohardjo in Makassar CityInternational Journal of computational Engineering research (IJCER)No ratings yet

- Multi-Response Optimization of WEDM Process Parameters of Monel 400 Using Integrated RSM and GADocument8 pagesMulti-Response Optimization of WEDM Process Parameters of Monel 400 Using Integrated RSM and GAInternational Journal of computational Engineering research (IJCER)No ratings yet

- Location of Zeros of PolynomialsDocument7 pagesLocation of Zeros of PolynomialsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Modeling The Frictional Effect On The Rip Current On A Linear Depth ProfileDocument6 pagesModeling The Frictional Effect On The Rip Current On A Linear Depth ProfileInternational Journal of computational Engineering research (IJCER)No ratings yet

- Investigation of Vibration On Suspension Systems at Different Load and Operating ConditionsDocument5 pagesInvestigation of Vibration On Suspension Systems at Different Load and Operating ConditionsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Time-History Analysis On Seismic Stability of Nuclear Island Bedrock With Weak InterlayerDocument9 pagesTime-History Analysis On Seismic Stability of Nuclear Island Bedrock With Weak InterlayerInternational Journal of computational Engineering research (IJCER)No ratings yet

- Anatomy of The Traffic Accidents On The RoadDocument6 pagesAnatomy of The Traffic Accidents On The RoadInternational Journal of computational Engineering research (IJCER)No ratings yet

- Effect of Turbulence Model in Numerical Simulation of Single Round Jet at Low Reynolds NumberDocument16 pagesEffect of Turbulence Model in Numerical Simulation of Single Round Jet at Low Reynolds NumberInternational Journal of computational Engineering research (IJCER)No ratings yet

- PCB Faults Detection Using Image ProcessingDocument5 pagesPCB Faults Detection Using Image ProcessingInternational Journal of computational Engineering research (IJCER)No ratings yet

- Study of The Class and Structural Changes Caused by Incorporating The Target Class Guided Feature Subsetting in High Dimensional DataDocument13 pagesStudy of The Class and Structural Changes Caused by Incorporating The Target Class Guided Feature Subsetting in High Dimensional DataInternational Journal of computational Engineering research (IJCER)No ratings yet

- An Evaluation of The Taxi Supply Management at The International Airport of Sultan Hasanuddin in Makassar - IndonesiaDocument4 pagesAn Evaluation of The Taxi Supply Management at The International Airport of Sultan Hasanuddin in Makassar - IndonesiaInternational Journal of computational Engineering research (IJCER)No ratings yet

- Urban Town PlanningDocument4 pagesUrban Town PlanningInternational Journal of computational Engineering research (IJCER)No ratings yet

- Wi MAX Deinter Leaver's Address Generation Unit Through FPGA ImplementationDocument3 pagesWi MAX Deinter Leaver's Address Generation Unit Through FPGA ImplementationInternational Journal of computational Engineering research (IJCER)No ratings yet

- Modelling, Fabrication & Analysis of Pelton Turbine For Different Head and MaterialsDocument17 pagesModelling, Fabrication & Analysis of Pelton Turbine For Different Head and MaterialsInternational Journal of computational Engineering research (IJCER)No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- RGNQA Parameters ConsolidatedDocument186 pagesRGNQA Parameters ConsolidatedpendialaNo ratings yet

- PCD 2 MarksDocument23 pagesPCD 2 MarksVignesh VickyNo ratings yet

- AIS - 007 - Rev 5 - Table - 1Document21 pagesAIS - 007 - Rev 5 - Table - 1Vino Joseph VargheseNo ratings yet

- LabVIEW Project Report Complete HPK Kumar DetailedDocument62 pagesLabVIEW Project Report Complete HPK Kumar DetailedDanny Vu75% (4)

- Be Katalog-Grabenfr 2013 Engl RZ KleinDocument36 pagesBe Katalog-Grabenfr 2013 Engl RZ Kleincherif100% (1)

- 8D ReportDocument26 pages8D ReportEbenezer FrancisNo ratings yet

- Type of Ac StatementDocument3 pagesType of Ac StatementRoberto SmithNo ratings yet

- GB 2626 - 2006 Respiratory Protective Equipment Non-Powered Air-Purifying Particle RespiratorDocument22 pagesGB 2626 - 2006 Respiratory Protective Equipment Non-Powered Air-Purifying Particle RespiratorCastañeda Valeria100% (1)

- Failure Mechanisms of C-Steels (API 571)Document90 pagesFailure Mechanisms of C-Steels (API 571)Abdul Gafoor Shaikh50% (2)

- Nathan and NickDocument73 pagesNathan and Nickapi-237623449No ratings yet

- OxyGEN Router User's GuideDocument83 pagesOxyGEN Router User's Guidemakro100% (1)

- Reducing Tee PDFDocument4 pagesReducing Tee PDFpankrasius herbudiNo ratings yet

- Accomplishment Report in ESPDocument7 pagesAccomplishment Report in ESPAldrin Perez85% (39)

- Muse Score 3Document246 pagesMuse Score 3lejuan0No ratings yet

- On Phase ChangesDocument28 pagesOn Phase Changesapi-313517608No ratings yet

- ALR Compact Repeater: Future On DemandDocument62 pagesALR Compact Repeater: Future On DemandmickycachoperroNo ratings yet

- Final Informatics Practices Class XiDocument348 pagesFinal Informatics Practices Class XisanyaNo ratings yet

- Aadhaar Application FormDocument4 pagesAadhaar Application Formpan cardNo ratings yet

- Hand Free DrivingDocument8 pagesHand Free DrivingNurulAfikaNo ratings yet

- Manual Do Consumo de Gases DC - TruLaser - 1030 - 2011-08-09 - METRIC - VERSIONDocument65 pagesManual Do Consumo de Gases DC - TruLaser - 1030 - 2011-08-09 - METRIC - VERSIONveraNo ratings yet

- Xiaopan OS InstallationDocument6 pagesXiaopan OS InstallationMuhammad SyafiqNo ratings yet

- Lexium Motion Control 200401Document130 pagesLexium Motion Control 200401Mohamed Elsayed HasanNo ratings yet

- 07-GB Column BasesDocument14 pages07-GB Column BasesAUNGPSNo ratings yet

- Organic PoolsDocument163 pagesOrganic PoolsEdu Socolovsky100% (3)

- Philips AZ 1839 Service ManualDocument7 pagesPhilips AZ 1839 Service ManualEdwardNo ratings yet

- Motor Driver Board Tb6560-5axisDocument14 pagesMotor Driver Board Tb6560-5axisAli Asghar MuzzaffarNo ratings yet

- Truss Operating Manual: Version 7aDocument28 pagesTruss Operating Manual: Version 7adoyoudeNo ratings yet

- Container Parts in Detail PDFDocument32 pagesContainer Parts in Detail PDFSathishSrs60% (5)

- Utilisation of Electrical Energy May 2008Document8 pagesUtilisation of Electrical Energy May 2008rajaniramNo ratings yet

- BE Enus DP3441DP3441e DP3661e Series Portable Radios Quick Reference GuideDocument6 pagesBE Enus DP3441DP3441e DP3661e Series Portable Radios Quick Reference GuideEduardoNo ratings yet