Professional Documents

Culture Documents

9

Uploaded by

Sachin RathodCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

9

Uploaded by

Sachin RathodCopyright:

Available Formats

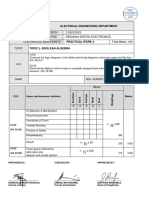

Pg. No. 9 11.

The initial output of the following circuit is 1, if we apply 010101 at input a (first bit is zero) then what is the bit pattern generated at the output Y a) 010101 b) 101010 c) remains at 0 d) remains at 1

12. The circuit shown below is.

a b) 3 input XOR gate c) Half adder. d) 3 input XNOR gate

) Full adder.

13. consider the follwing logic circuit consisting of 2 x 4 line decoders, for each of the decoder F0 = 1 when i1 = 0, i2 = 0 ; F1 = 1 when i1 = 0, i2 = 1 and so on. Then what is g(x, y, z) ? a)xy +xyz b) xyz c) (xy+xy)z d)1

14. Identify the output equations for the following circuit

a) P(A,B,C) = m (1,2,4,7) Q(A,B,C) = m (2,3,4,7) b) P(A,B,C) = m (1,2,4,7) Q(A,B,C) = m (1,2,3,7) c) P(A,B,C) = m (1,2,4,7) Q(A,B,C) = m (3,5,6,7) d) P(A,B,C) = m (3,5,6,7) Q(A,B,C) = m (1,2,4,7) 15. In a digital Computer Binary subtraction is performed a) In the same way we perform subtraction in decimal number system b) using two;s complement method c) Using 9s complement method. d) using 10s complement. Pg.No. 10 16. The logic expression Y = m ( 0,3,6,7,10,12,15) is equivalent to a) Y = (pie)M ( 0,3,6,7,10,12,15) b) Y = (pie) M (1,2,4,5,8,9,11,13,14) c) Y = m (1,2,4,5,8,9,11,13,14) d) Y = m ( 3,0,10,12)

7. The output Boolean equations of the circuit below are

a) X = ab + a b Y = ab b) X = ab + ab Y = ab c) X = ab + ab Y = ab d) X = ab + ab Y = ab

18. The circuit shown in the below fig. represents a) half adder / subtractor X = Sum / difference, Y = carry, Z = Borrew. b) half adder / subtractor X = Carry, Y = Borrow, Z = Sum/difference c) half adder / subtractor X = Sum/difference, Y = borrow, Z = carry d) none of the above

19.What is the output code generated by the following circuit ?

a) Decimal Code b) Octal Code c) One Hot code d) Hexadecimal Code Pg.No. 11

Page11 20. A system which accepts am M-bit and established the stated 1 on one only one of 2^m output is calleda) Decoder b) demultiplexer c) multiplexer d) encoder

21. In a half-adder having two inputs A and B and two outputs S(sum) C (Carry) , the Boolean expressions for S and C in terms of A and B is a) S = A\B + AB\ ; C = AB b) S = AB + A\B ; C = A + B c) S = A\B\+ AV ; C = A+ B\ D) S = A\B + AB\ ; C = A\+B

22. The logic circuit shown in thr figure represents a a) Full adder b) Half adder c) Half subtractor d) Boolean multiplexer 23. Which one of the following can be used as a parallel to series converter ? a) Decoder b) Digital Counter c) multiplexer d) Demultiplexer 24) The number of 4-line to 16 line decoders required to make an 8 line to 256 decoder is a) 16 b) 17 c) 32 d) 64 24. The number of 4-line-to-16-line decoders required to make am 8-line-to-256-line decoder is

a)A b)B c)AB d) AB + AB 26. Consider the following statements: A multiplexer 1.Selets one of the several inputs ant transmits it to a single output 2. Routs the data from a single input and transmits it to a single output 3.converts parallel data into serial data 4. Is a combinational circuit

27. Choose the universal element from the following: a) digital Magnitude comparator b) multiplexer c) encoder d) Binary parallel adder. 28. the minimum number of 2-to-1 multiplexer required to realize a 4-to-1 multiplexer is a) a b) 2 c) 3 4) 4 29. Full adder can be converted into full subtractor by using which of the following gate..? a) NAND b)NOR c) XOR d) Any of the given gates

Page11,12

0. A 3-to-8 decoder is shown beow:

All the output lines of the chip will be high, when all the inputs 1,2 and 3. a) are x ; G1 low, G2 low b) are x ; G1 high, G2 low c) are 000 ; G1 high, G2 low d) are high ; G1 high, G2 low

31. To realize the given truth table from the circuit shown in the figure, the input to j in terms of A and B would have to be. a)(AB) b) A b) B D) AB

34.The circuit shown in the figure is

a) an adder circuit. b) an subtractor circuit. c) one bit comparator circuit d) parity generator circuit

20. A system which accepts an M-bit and established the stated 1 on one only one of 2^m output is calleda) Decoder b) demultiplexer c) multiplexer d) encoder 23. Which one of the following can be used as a parallel to series converter ? a) Decoder b) Digital Counter c) multiplexer d) Demultiplexer 24) The number of 4-line to 16 line decoders required to make an 8 line to 256 decoder is a) 16 b) 17 c) 32 d) 64 25) The function F implemented by the multiplexer chip shown in fig. is

a)A b)B c)AB d) AB + AB 28. the minimum number of 2-to-1 multiplexer required to realize a 4-to-1 multiplexer is a) a b) 2 c) 3 4) 4

Pg. No.13 36. The logic circuit realized by the circuit shown in the given figure will be

1 2 3 4

F F = B (EXOR) C F = A (EXNOR) C F = A (EXOR) C

= B (EXNOR) C

3 the output code is in BCD. a) BCD code b) Gray code c) one hot code d) excess 3 code.

7. Identify input code of the following circuit, if

38. Design clocked J-K , T & D flip flops. 39. Convert S-R F.F.into J-K , T & D flip flops.

Pg. No 17 A 4 bit module 16 ripple counter uses JK filp flop. If the propogation delay of each flipflop is 50ns, the max clock frequency that can be used is. a) 20Mhz b) 10 Mhz c) 5 Mhz d) 4 Mhz 2 A SR flip flop can be converted into a T flip flop. If the connecting--to Q and -- to Q a) Qn +1 = Q b) S = Q, R = Q c) S = Q, R = Q d) S = Q, R = Q 04. A twisted ring counter is made by using a single D flip-Flop. The resulting Circuit a ) SR Filp-Flop b) JK Filp-Flop c) D Filp-Flop d) T Filp-Flop

1

06. The counter shown in the figure has initially Q2 Q1 Q0 = 000. The status of Q2 Q1 Q0 after the first pulse is a) 001 b) 010 c) 100 d)101

11 .figure shows Mod k counter here K is equal to a) 1 b) 2 c) 3 d) 4

Page 18,19

12. The correct cyclic sequens of the outputs (Qo, Q1) for the JK flip flop circuit shown in the fig. when sequens of clock pulses are applied

a) 00, 10, 01, 00, 10, 01 b) 00, 01, 10,00,01, 10.. c) 00, 11, 00, 11, 00. d) ? 13. The digital block in figure is realized using two positive edge triggred D-flip flop .Assume that for t < t0, Q1 = Q2 = 0. The circuit in the digital block is given by a) fig. a b) fig. b c) fig.c d) fig d

14. What is the output signal frequency of the following counter if the clock frequency is 16 Khz ? All J and K Inputs are connected to 1. a) 4 Khz b) 8 Khz c) 10 khz d) 16 Khz

1 Arrangement of J-K flip flop a) Shift registor b) Mod 3 counter c) Mod 2 Counter d) None of the above

5.The function performed by the following

You might also like

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- BEST Question Bank - Digital ElectronicsDocument157 pagesBEST Question Bank - Digital Electronicsabhinav_pundir0% (1)

- IES - Electronics Engineering - Digital Electronic CircuitsDocument66 pagesIES - Electronics Engineering - Digital Electronic Circuitsedwinaustine100% (4)

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- Digital Signal Processing Using the ARM Cortex M4From EverandDigital Signal Processing Using the ARM Cortex M4Rating: 1 out of 5 stars1/5 (1)

- Quiz Questions For DLD LabDocument6 pagesQuiz Questions For DLD LabGerald Carson100% (1)

- (Do Not Print) Digital-Electronics PDFDocument122 pages(Do Not Print) Digital-Electronics PDFMasaruNakaegawaNo ratings yet

- DE09 SolDocument157 pagesDE09 SolRakesh KumarNo ratings yet

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsFrom EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNo ratings yet

- Digital Number Systems 3 AnsDocument3 pagesDigital Number Systems 3 AnsbhagNo ratings yet

- Questions On Digital Electronics and MicroprocessorsDocument12 pagesQuestions On Digital Electronics and MicroprocessorsHarendra KumarNo ratings yet

- Testpaper - 1 NTDocument13 pagesTestpaper - 1 NTGattu SadashivaNo ratings yet

- Digital Electronics and CircuitsDocument12 pagesDigital Electronics and CircuitsGuruKPONo ratings yet

- Ec 2007Document11 pagesEc 2007mallanna4blogsNo ratings yet

- DE Question BankDocument5 pagesDE Question BankKaree MullahNo ratings yet

- Obj 1997paper 2Document15 pagesObj 1997paper 2Uday KakkarNo ratings yet

- Sir Padampat Singhania University Digital Electronics ExamDocument5 pagesSir Padampat Singhania University Digital Electronics ExamIyyakutti GanapathiNo ratings yet

- MCQ de 2022Document11 pagesMCQ de 202201ABHIGYAN MAJINo ratings yet

- Digital Electronics - MCQsDocument38 pagesDigital Electronics - MCQsAbhay ShuklaNo ratings yet

- IES - Electronics Engineering Paper 2 - 1997Document36 pagesIES - Electronics Engineering Paper 2 - 1997visitmajeedNo ratings yet

- Ab+Ab: Base X Base X Base XDocument3 pagesAb+Ab: Base X Base X Base XVani Bindal AgarwalNo ratings yet

- 2006Document11 pages2006simplymeashishNo ratings yet

- II Mid Bits For StudentsDocument9 pagesII Mid Bits For StudentsSurya MukeshNo ratings yet

- IES - Digital Mock Test - 2014Document9 pagesIES - Digital Mock Test - 2014Meenakshi SundaramNo ratings yet

- 08AF302 - DIGITAL INTEGRATED CIRCUITS AND LOGIC DESIGNDocument4 pages08AF302 - DIGITAL INTEGRATED CIRCUITS AND LOGIC DESIGNChandru RamaswamyNo ratings yet

- Boolean Logic and Digital Circuits Multiple Choice QuestionsDocument6 pagesBoolean Logic and Digital Circuits Multiple Choice Questionsprakash chandNo ratings yet

- MsqsDocument5 pagesMsqsYusra MehmoodNo ratings yet

- BC0036 Digital System Paper 3Document13 pagesBC0036 Digital System Paper 3SeekEducationNo ratings yet

- ObjectivesDocument6 pagesObjectivesAarti MasalNo ratings yet

- Sequential CircuitsDocument33 pagesSequential CircuitsPrasun SinghalNo ratings yet

- IES Electrical Engineering Topic wise Questions Analog & Digital Circuits YEAR 2008Document81 pagesIES Electrical Engineering Topic wise Questions Analog & Digital Circuits YEAR 2008Vishal KumarNo ratings yet

- TECHNICAL QUIZ EceDocument7 pagesTECHNICAL QUIZ EceAnonymous eWMnRr70qNo ratings yet

- Logic gates and processor architecture questionsDocument7 pagesLogic gates and processor architecture questionspclr07No ratings yet

- EE370 Assignment-IDocument3 pagesEE370 Assignment-ISandeep TomarNo ratings yet

- QbcsaDocument7 pagesQbcsaMohammad ImthiyazNo ratings yet

- Digital Electronics: An Overview of Key ConceptsDocument14 pagesDigital Electronics: An Overview of Key ConceptsDebbie UzoNo ratings yet

- 5 - 6255737462828565350 (10 Files Merged)Document307 pages5 - 6255737462828565350 (10 Files Merged)Aman PalNo ratings yet

- VHDL, Verilog and Advanced Verilog: Umabalaji, Assistant Professor/ECE, SCSVMV December 2020Document84 pagesVHDL, Verilog and Advanced Verilog: Umabalaji, Assistant Professor/ECE, SCSVMV December 2020Vinoth RathinamNo ratings yet

- Gate - in 2005Document25 pagesGate - in 2005prabhjot singh1No ratings yet

- 08AB303 DIGITAL LOGIC CIRCUITSDocument4 pages08AB303 DIGITAL LOGIC CIRCUITSChandru RamaswamyNo ratings yet

- RCPP QuestionSet 1Document23 pagesRCPP QuestionSet 1Siddhanth SharmaNo ratings yet

- Btech Biomed 4 Sem Digital Electronics Circuit Pbm4i102 2018Document3 pagesBtech Biomed 4 Sem Digital Electronics Circuit Pbm4i102 2018Narinder MauryaNo ratings yet

- Digital Design & Basic CMOS Interview Series Level-1 QuestionsDocument5 pagesDigital Design & Basic CMOS Interview Series Level-1 Questionsdeepakk_alpineNo ratings yet

- Digital Electronics and Microprocessors QuizDocument4 pagesDigital Electronics and Microprocessors Quizrktiwary256034No ratings yet

- Digital Electronics (Pc-Ee-402) MCQ With AnswersDocument11 pagesDigital Electronics (Pc-Ee-402) MCQ With AnswersSanjoy PathakNo ratings yet

- DigitalDocument182 pagesDigitalYeshoda MallikarjunaNo ratings yet

- BCA I Year Digital Computer Oragnisation Practice QuestionsDocument6 pagesBCA I Year Digital Computer Oragnisation Practice Questionsarchana naikNo ratings yet

- Digital Systems1Document5 pagesDigital Systems1kgovindrajanNo ratings yet

- STLD BitsDocument18 pagesSTLD BitsKornepati SureshNo ratings yet

- Digital Logic Solutions: 1. Consider The Following CircuitDocument8 pagesDigital Logic Solutions: 1. Consider The Following CircuitergrehgeNo ratings yet

- The Output F of The Multiplexer Circuit Shown in The Given Figure Can Be Represented byDocument29 pagesThe Output F of The Multiplexer Circuit Shown in The Given Figure Can Be Represented byERMIAS AmanuelNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Topographical Tools for Filtering and Segmentation 2: Flooding and Marker-based Segmentation on Node- or Edge-weighted GraphsFrom EverandTopographical Tools for Filtering and Segmentation 2: Flooding and Marker-based Segmentation on Node- or Edge-weighted GraphsNo ratings yet

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- Fcs Eme DC MPMC Nas Fcs Eme DC MPMC Nas Fcs Eme DC MPMC Nas FcsDocument13 pagesFcs Eme DC MPMC Nas Fcs Eme DC MPMC Nas Fcs Eme DC MPMC Nas FcsSachin RathodNo ratings yet

- Result Analysis SachinDocument1 pageResult Analysis SachinSachin RathodNo ratings yet

- AluDocument2 pagesAluSachin RathodNo ratings yet

- Meninbluegroup - ContactDocument4 pagesMeninbluegroup - ContactSachin RathodNo ratings yet

- UntitledDocument1 pageUntitledSachin RathodNo ratings yet

- Sachin Rathod Sggsie& T Entc 2011Document3 pagesSachin Rathod Sggsie& T Entc 2011Sachin RathodNo ratings yet

- Sachin Rathod SGGS ETC 2011Document7 pagesSachin Rathod SGGS ETC 2011Sachin RathodNo ratings yet

- MXCK LC84 001 SpecificationsDocument5 pagesMXCK LC84 001 SpecificationsSachin RathodNo ratings yet

- Sachin RathodDocument2 pagesSachin RathodSachin RathodNo ratings yet

- Artificial Synchronization of Heart Using PacemakerDocument1 pageArtificial Synchronization of Heart Using PacemakerSachin RathodNo ratings yet

- Study of Antenna Design1Document1 pageStudy of Antenna Design1Sachin RathodNo ratings yet

- MyyDocument2 pagesMyySachin RathodNo ratings yet

- JPEG DECODER USING VHDL AND IMPLEMENTING IT ON FPGA SPARTAN 3A KItProject Main Report1Document21 pagesJPEG DECODER USING VHDL AND IMPLEMENTING IT ON FPGA SPARTAN 3A KItProject Main Report1Sachin RathodNo ratings yet

- Boolean Algebra or Gate: Jessa Fernandez PCEIT-03-801ADocument2 pagesBoolean Algebra or Gate: Jessa Fernandez PCEIT-03-801AGiing FernandezNo ratings yet

- Xilinx Project Navigator HDL Lab ManualDocument72 pagesXilinx Project Navigator HDL Lab Manualshubham100% (1)

- Lect # 06, Floyd, CH # 06 - Adder, Subtractor, Multiplier, Comparator PDFDocument35 pagesLect # 06, Floyd, CH # 06 - Adder, Subtractor, Multiplier, Comparator PDFMuhammad Adnan KhalidNo ratings yet

- ADE Lecture11Document12 pagesADE Lecture11Baraa MuhammadNo ratings yet

- Experiment No.1: AIM: Design The Following Combinational Circuits Using VHDL and Test The Circuits Using TestDocument83 pagesExperiment No.1: AIM: Design The Following Combinational Circuits Using VHDL and Test The Circuits Using Testdelinquent_abhishekNo ratings yet

- Low Power 16×16 Bit Multiplier Design Using Dadda AlgorithmDocument17 pagesLow Power 16×16 Bit Multiplier Design Using Dadda AlgorithmEditor IJTSRDNo ratings yet

- 1985 Mitsubishi Bipolar Digital IC LSTTL IntegradosDocument498 pages1985 Mitsubishi Bipolar Digital IC LSTTL Integradosramon navaNo ratings yet

- Unit-VI Counters and Shift RegistersDocument20 pagesUnit-VI Counters and Shift RegistersVarsha SenthilNo ratings yet

- Introduction To AsicDocument12 pagesIntroduction To AsicSrinivas CherukuNo ratings yet

- Digital Fundamentals: With PLD ProgrammingDocument29 pagesDigital Fundamentals: With PLD ProgrammingNeslynNo ratings yet

- Lab11 - Achmad Mauludin - 165060301111002Document17 pagesLab11 - Achmad Mauludin - 165060301111002Mauudin BRgNo ratings yet

- Memory and Programmable LogicDocument47 pagesMemory and Programmable Logicdewantosatrio50% (2)

- Problem Set 1Document4 pagesProblem Set 1Pradyumn PaliwalNo ratings yet

- Lab 5 Basic Logic GatesDocument5 pagesLab 5 Basic Logic GatesJermain PeartNo ratings yet

- M.tech CPLD & Fpga Architecture & ApplicationsDocument2 pagesM.tech CPLD & Fpga Architecture & Applicationssrinivas100% (1)

- 4 Bit Adder SubtractorDocument15 pages4 Bit Adder SubtractorBiveyNo ratings yet

- Unit 1 Logic Gates - 02Document21 pagesUnit 1 Logic Gates - 02KHUSHI JAINNo ratings yet

- DICA Question Bank Units - 1,2,3Document4 pagesDICA Question Bank Units - 1,2,3mkrNo ratings yet

- Logic Gates ExperimentDocument10 pagesLogic Gates ExperimentRabindraMaharana50% (2)

- Flip-Flops and Its Applications: Module - 3Document41 pagesFlip-Flops and Its Applications: Module - 3Chethan RamachariNo ratings yet

- Digital Electronics - YouTube ListDocument11 pagesDigital Electronics - YouTube ListRahul TripathyNo ratings yet

- Lab - ALUDocument3 pagesLab - ALUERICK BERNARDO TEQUIZ MERCHANNo ratings yet

- Digital QuestionsDocument3 pagesDigital Questionsmdhuq1No ratings yet

- Deld QB EndsemDocument4 pagesDeld QB EndsemUV New MoviesNo ratings yet

- VERIFICATION OF GATES USING ICsDocument14 pagesVERIFICATION OF GATES USING ICsAqib IrshadNo ratings yet

- PW 2 Dee20033 Sesi 2 2022 2023 F2FDocument7 pagesPW 2 Dee20033 Sesi 2 2022 2023 F2FAkmal GaffarNo ratings yet

- XC4000, XC4000A, XC4000H Logic Cell Array Families: Product DescriptionDocument40 pagesXC4000, XC4000A, XC4000H Logic Cell Array Families: Product DescriptionGAGANA PNo ratings yet

- 2019 Summer Question Paper (Msbte Study Resources)Document3 pages2019 Summer Question Paper (Msbte Study Resources)Ashutosh PatilNo ratings yet

- DIC 1 Question PaperDocument1 pageDIC 1 Question PaperHenery KantNo ratings yet

- EE141 s09 Hw3 SolutionDocument6 pagesEE141 s09 Hw3 Solutionanil rajputNo ratings yet