Professional Documents

Culture Documents

TV Tuner Diagram

Uploaded by

tariq76Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TV Tuner Diagram

Uploaded by

tariq76Copyright:

Available Formats

Designing with Multi-PLL and Spread-Spectrum Clocks in Digital Entertainment Equipment

By (Ashwini Raman, Product Marketing Manager, Cypress Semiconductor Corp.)

Executive Summary

The Digital TV industry is growing at a phenomenal rate with LCD and PDP (Flat panel displays) accounting for about 50% of the total shipments. The estimated CAGR for DTV market is a whopping 23% between 2006 and 2010. Rapidly declining finished DTV prices has led OEMs, ODMs and EMSs to focus on component reduction, BOM cost reduction, and integration. With that perspective, it is almost imperative for manufacturers to look at every component that goes into the system, including the heart of it all clocks. Every electronic system irrespective of analog or digital needs a timing reference based off of which the entire circuitry operates. The timing reference or clock has traditionally been crystals (piezoelectric quartz devices) or crystal oscillators (crystal + electronics to control the oscillations). With this integration trend, PLL based (Silicon) timing solutions are becoming more common to provide cleaner, stabler clocking options for designs that need multiple frequencies. The objective of this article is to articulate the value proposition of using silicon based timing solutions for solving design challenges vs. traditional methods of using several independent crystals or crystal oscillators (XOs).

Need for Multiple Frequencies in HDTV Systems: Different Standards and Interfaces

Nearly every electronic system, whether analog or digital, needs a timing reference for its circuitry. The timing reference or clock has traditionally used crystals or crystal oscillators (crystal plus circuitry to control the oscillations). With increasing integration, PLL-based silicon timing devices are becoming more common to provide cleaner, stabler clocking options for designs that need multiple frequencies. This article explores the difference between using silicon-based timing devices for solving design challenges versus traditional methods employing several independent crystals or crystal oscillators (XO). A basic LCD TV tuner diagram, Figure 1, processes an incoming data stream into the appropriate audio and video format of the television set in your living room. Figure 1: Generic LCD TV architecture

Designing with Multi-PLL and Spread-Spectrum Clocks in Digital Entertainment Equipment Published in Planet Analog (http://www.planetanalog.com)

Page 1 of 5 September 2007

[+] Feedback

There are multiple subsystems that go into the tuner boards. Basic functions can be broadly classified under the following blocks: 1. 2. 3. 4. Analog Front End (Demodulator) Audio/Video encoding and decoding (MPEG video decoder/ MPEG audio decoder) Interfaces Display Panel

Almost all the blocks shown in the diagram need a clocking signal. The CPU requires clocks typically in the range 30 to 100 MHz, while the MPEG standard requires a 27-MHz-based clock input. The decoder and encoder need to be synchronized, which is achieved by a VCXO (voltage-controlled crystal oscillator). Audio clocks that source the DACs have stringent partsper-million (ppm) accuracy and stability requirements, since their frequencies depend on sampling frequency and oversampling ratios. For the interfaces, clocks are defined by their respective standards, such as USB, Ethernet, Modem, PCI, PCIExpress, SATA, among others. The flat panel clocks are dependent on the display size and the display standard, with high definition at 1080i, 1080p, and 720p, and standard definition for NTSC and PAL. The panel controller subsystem must convert incoming picture data rate to match the size of the actual panel, such as. 74.17582418 MHz.

TV Architectures and Clock Tree Implementations

One of the key decisions that designers are now forced to make early on in the design process is whether to use the digital or analog signal format. A few years ago, the TV signal chain was primarily analog-based, but now a digital audio-data path is much more common. Both digital and analog paths have inherent advantages and disadvantages. However, there is a worldwide mandate in place to move all transmission to digital in a series of staged phases. HDTV transmissions are digital, so newer TVs tend to use the digital path. The advantage of digital transmission is that it has a higher tolerance of noise, compared to analog signals. Board designers need to take special care while routing, use differential signals with better SNR performance, or use shielding techniques to avoid signal degradation.

Traditional clock-tree design

This uses discrete crystals/XOs for each frequency requirement. The good thing about this approach is that clocks can be placed quite close to the components using them, simplifying routing. The downside is that each of these crystals/XOs has to be procured from vendors ahead of time and does not easily allow last-minute design changes. If even one of the frequencies changes, there is significant lead time that could lead to delays in the overall shipping schedule.

Silicon timing devices

For over a decade, PLL-based timing devices have become increasingly popular, compared to traditional clocking methods. Silicon timing devices enable complex system designs by supporting features that discrete crystals and crystal oscillators do not. While these devices impart flexibility and cost savings, they do come at a tradeoff. Every architectural change eventually needs to be cost-effective to occur, and for the effort to be justifiable. The most compelling benefit that silicon-based timing devices offer by integrating several crystals/XOs is reducing overall bill of materials (BOM) and maintaining, or stepping up, the level of performance. For example, in the typical TV tuner board example shown , with 5 to 6 discrete crystals (each costing $0.12 to $0.50), a silicon-based clock generator with programmable features capable of providing those frequencies reduces system cost if it

Designing with Multi-PLL and Spread-Spectrum Clocks in Digital Entertainment Equipment Published in Planet Analog (http://www.planetanalog.com) Page 2 of 5 September 2007

[+] Feedback

costs under $2.00. Although cost is the major driver for crystal/oscillator integration, there are other benefits that OEMs and end users perceive:

1. Reliability: Crystals are quartz-based devices whihc have a higher failure rate than PLL-based timing devices. Each crystal removed from the system can help increase overall system reliability. Integration also reduces component count on the board, leading to higher stability and lower return rates. 2. Availability of crystals: Crystals in the range of 10-40 MHz are readily available. However, high-frequency crystals, above 40 MHz, are more difficult to manufacture and procure. These higher-order overtone crystals range from $1 to $10. Siliconbased timing devices use one low-frequency crystal (or an available clock reference) to generate several high-frequency outputs. 3. Crystal aging: Crystals are prone to aging, with a +/-2ppm to +/-5ppm error per every few years, caused by impurities in the crystal material and on the crystal surface, as well as mechanical stresses between the crystal material and the deposited electrodes. This error may cause slow system-wide degradation. Long-term frequency drift is a common issue with the use of crystals. PLL-based timing devices maintain their accuracy over their entire lifetime. 4. Programmability: PLL-based clock generators have in-built programmability features that provide flexibility during design. Programmable features include changing output frequencies, drive strength settings, spread spectrum percentages, and pin programming for frequency selection, which means one output can give different frequencies based on need. Programmability can be done in-system, typically using an I2C-interface, to modify certain parameters "on the fly". This is a compelling feature for manufacturers using the same set of frequencies for multiple platforms. 5. Component reduction and board space savings: Programmable clock generators reduce number of components through integration, as system designers migrate towards fewer components to reduce problems caused by routing and maintaining signal integrity. PLL-based clock generators, with the ability to generate several outputs from a low-frequency crystal, reduce the number of total components used in a system and conserve board space. 6. EMI Reduction by Spread Spectrum Clocking: TV tuner boards are typically 5- to 7-layer boards, with dedicated ground planes for keeping interference low. Several high-speed signals must be routed carefully to help improve system performance and avoid crosstalk, skew, and signal-integrity issues. Silicon timing devices help alleviate these board design issues by offering features such as spread spectrum that reduce the peak energy of high-speed signals. EMI must be below limits set by regulatory standards such as CISPR 22 or FCC Part 15 Class B. All consumer products must pass stringent FCC regulations in order to be released to the market. Unfortunately, high-speed designs with frequency harmonics may source energy into inappropriate bands. The spread-spectrum approach reduces, and often eliminates, the need for ferrite beads, filters, coils, and chokes that add to the BOM. This is important because there is a significant redesign effort when a system fails any electromagnetic compliance test. Using a spread-spectrum device is somewhat like having insurance. Programmability allows this to be used when needed and turned off if not required. This feature is especially useful during development and testing. 7. Inventory management: One of the key challenges that procurement teams face today is managing inventory, demand, and forecast planning for every device that goes into a system. Since each OEM has several platforms as well as subplatforms of products, managing this supply chain could be quite cumbersome. (Imagine managing 10 different crystals of different frequencies from different vendors across the globe.) Silicon timing devices resolve this problem by generating different frequencies using software at the designer's desk, which not only simplifies design, but also allows purchasing to procure a single device for multiple platforms. 8. Perfectly synchronized outputs: Some applications may need several copies of the basic clock to be perfectly in sync or aligned. This feature is offered by programmable PLL devices. When using several discrete crystals, it may be difficult to achieve accurate synchronization. 9. Power management: Programmable PLL-based clock generators can cater to the niche demands of the portable market including gaming, smartphones, personal media players, digital cameras, and camcorders. In these power-intensive applications, certain frequencies can be turned off selectively using I2C or pin-programming. This is not easily achieved with traditional crystal designs.

Designing with Multi-PLL and Spread-Spectrum Clocks in Digital Entertainment Equipment Published in Planet Analog (http://www.planetanalog.com)

Page 3 of 5 September 2007

[+] Feedback

Why LCD Panel Controllers Need EMI Reduction

LCD screens are ubiquitous and are becoming increasingly popular. Whether it is the 3.5 inch touch screen of the iPhone, the Sharp Aquos TV, or a laptop PC\, the technology for driving all these displays is nearly the same. This pervasiveness of LCD panels has shown that the technology which drives it has matured. Newer models are now more affordable than ever, and the demands on panel performance continue to grow: create larger panels, reduce electromagnetic interference, reduce power consumption, and provide higher image quality. An LCD panel is essentially an array of transistors that modulates the voltage across the liquid crystal, and thereby controls the amount of light passing through the panel. Color is achieved by virtue of filters that allow red, green, or blue light to pass through a given pixel. Row drivers are attached to the transistor's gates. These control which row of pixels is being programmed at any given time by applying either an "on" or "off" voltage. The sources of the transistors are tied to the column drivers, which supply the specific voltage required to achieve proper pixel luminance. The timing controller takes the display data from the host and transmits it to the column drivers and row drivers through the panel interface. It may include additional features such as overdrive to reduce motion blur and enhance images, as well as gamma correction. The row-driver interface uses TTL signaling levels. The column-driver interface, which needs significant bandwidth for higher-resolution displays, uses a differential bus architecture; typically, this is reduced-swing differential signaling (RSDS), Figure 2. Figure 2: LCD panel-controller block diagram

One of the major challenges in panel electronics is reducing interference to comply with EMC regulations. Panel manufacturers typically support different panel sizes but prefer using a single board for all of them. The challenge is to design a two-layer, size-constrained board for the various sizes and still meet the EMI testing requirements. One approach is to improve the PCB material, and add extra board layers with dedicated ground planes. A dominant percentage of LCD panels use standard FR4 material for their PC boards; higher-cost PCB material and additional layers is not a viable option. Another method used for EMI reduction is filtering, but this is not an assured method that works for all panel sizes. Spread-spectrum clock generators have become a popular method adopted to solve EMI issues. They offer the ability to have a systemic approach to solving EMI issues early in the design process. The spread spectrum feature can be selectively turned on, and the spread percentage can be adjusted to achieve the right amount of spread and pass EMC tests. Spread percentage can be varied for various panel sizes, based on need, with the same device.

Designing with Multi-PLL and Spread-Spectrum Clocks in Digital Entertainment Equipment Published in Planet Analog (http://www.planetanalog.com)

Page 4 of 5 September 2007

[+] Feedback

References

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730 http://www.cypress.com

Cypress Semiconductor Corporation, 2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. PSoC Designer, Programmable System-on-Chip, and PSoC Express are trademarks and PSoC is a registered trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are property of the respective corporations. This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress. Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. Use may be limited by and subject to the applicable Cypress software license agreement.

Designing with Multi-PLL and Spread-Spectrum Clocks in Digital Entertainment Equipment Published in Planet Analog (http://www.planetanalog.com)

Page 5 of 5 September 2007

[+] Feedback

You might also like

- Domestic Electricity Generation Using Waterwheels On Moored Barge 2005 PDFDocument85 pagesDomestic Electricity Generation Using Waterwheels On Moored Barge 2005 PDFtariq76No ratings yet

- Aminou Mtech Elec Eng 2014 PDFDocument193 pagesAminou Mtech Elec Eng 2014 PDFtariq76No ratings yet

- E1-Vlsi Signal ProcessingDocument2 pagesE1-Vlsi Signal Processingtariq76No ratings yet

- How to Send & Receive SMS with GSM Modem - SMS Client & Server AppDocument1 pageHow to Send & Receive SMS with GSM Modem - SMS Client & Server Apptariq76No ratings yet

- 2-Lecture Notes Lesson2 6Document8 pages2-Lecture Notes Lesson2 6kstu1112No ratings yet

- Transformer Health Condition Monitoring Through GSM Technology PDFDocument5 pagesTransformer Health Condition Monitoring Through GSM Technology PDFtariq76No ratings yet

- Television Engg PDFDocument74 pagesTelevision Engg PDFtariq76No ratings yet

- Am186 and Am188 Family Instruction Set Manual: February, 1997Document320 pagesAm186 and Am188 Family Instruction Set Manual: February, 1997nonesuch01No ratings yet

- BPSKDocument1 pageBPSKtariq76No ratings yet

- Television and Video Engineering Lab Manual PDFDocument77 pagesTelevision and Video Engineering Lab Manual PDFtariq76100% (2)

- Digital Energy Meter Monitoring Current VoltageDocument3 pagesDigital Energy Meter Monitoring Current Voltagetariq76No ratings yet

- Advanced Microprocessor & Microcontroller Lab Manual PDFDocument22 pagesAdvanced Microprocessor & Microcontroller Lab Manual PDFtariq76No ratings yet

- Photovoltaic Maximum Power Point Tracking Control System j17Document9 pagesPhotovoltaic Maximum Power Point Tracking Control System j17Tiago RamosNo ratings yet

- 20 PDFDocument4 pages20 PDFtariq76No ratings yet

- Rucker Thesis Rev13Document186 pagesRucker Thesis Rev13tariq76No ratings yet

- Et Ge Pe 20050761Document10 pagesEt Ge Pe 20050761tariq76No ratings yet

- 183929Document77 pages183929tariq76No ratings yet

- L0412046569 PDFDocument5 pagesL0412046569 PDFtariq76No ratings yet

- Induction Motor Main DocumentDocument37 pagesInduction Motor Main Documenttariq76No ratings yet

- SMS Based Remote Control SystemDocument6 pagesSMS Based Remote Control SystemKushan RahulNo ratings yet

- 17voltage SagSwell Compensation Using Z Source - 1 PDFDocument1 page17voltage SagSwell Compensation Using Z Source - 1 PDFtariq76No ratings yet

- 5the Direct Current Control Method of STATCOM and It - S Simulation - 1 PDFDocument1 page5the Direct Current Control Method of STATCOM and It - S Simulation - 1 PDFtariq76No ratings yet

- Leary JL 2008 Thesis 1Document90 pagesLeary JL 2008 Thesis 1tariq76No ratings yet

- 10a Novel Analysis of High Frequency - 1 PDFDocument1 page10a Novel Analysis of High Frequency - 1 PDFtariq76No ratings yet

- 8open End Winding PMSG For Wind Energy Conversion System - 1 PDFDocument1 page8open End Winding PMSG For Wind Energy Conversion System - 1 PDFtariq76No ratings yet

- 109ce0059 PDFDocument48 pages109ce0059 PDFnadeemq_0786No ratings yet

- Pedal Operated Water PurificationDocument5 pagesPedal Operated Water Purificationtariq7675% (4)

- Energy-Efficient Wireless MAC Protocols For Railway Monitoring ApplicationsDocument11 pagesEnergy-Efficient Wireless MAC Protocols For Railway Monitoring Applicationstariq76No ratings yet

- Human-Powered Water PurificationDocument6 pagesHuman-Powered Water Purificationtariq76No ratings yet

- Et0128 Pedalpoweredreverseosmosiswaterpurification 131231212753 Phpapp02Document5 pagesEt0128 Pedalpoweredreverseosmosiswaterpurification 131231212753 Phpapp02tariq76No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- File:Circuit Diagram - Pictorial and Schematic - PNGDocument4 pagesFile:Circuit Diagram - Pictorial and Schematic - PNGBhel_Mortel_6465No ratings yet

- Water Level Controller Using 8051 Circuit PrincipleDocument4 pagesWater Level Controller Using 8051 Circuit PrincipleLappi SchematicsNo ratings yet

- IEE Proceedings - Microwaves Antennas and Propagation Volume 143 Issue 2 1996 [Doi 10.1049_ip-Map-19960260] Langley, J.D.S.; Hall, P.S.; Newham, P. -- Balanced Antipodal Vivaldi Antenna for Wide Bandwidth Phased ArraysDocument6 pagesIEE Proceedings - Microwaves Antennas and Propagation Volume 143 Issue 2 1996 [Doi 10.1049_ip-Map-19960260] Langley, J.D.S.; Hall, P.S.; Newham, P. -- Balanced Antipodal Vivaldi Antenna for Wide Bandwidth Phased Arraysnaji1365No ratings yet

- Analytical Modeling of Double Gate MosfeDocument57 pagesAnalytical Modeling of Double Gate MosfeVijaya Kumar100% (1)

- Quick Charge Device List PDFDocument20 pagesQuick Charge Device List PDFEnoNo ratings yet

- PSIM User ManualDocument216 pagesPSIM User Manualjubin_eldho100% (1)

- Physics and Modeling of Microelectronic Devices: BITS PilaniDocument17 pagesPhysics and Modeling of Microelectronic Devices: BITS PilaniKrunalKapadiya1No ratings yet

- Switching Power SupplyDocument138 pagesSwitching Power SupplyStephen Dunifer95% (22)

- Tda 7269Document8 pagesTda 7269JCMNo ratings yet

- MPPT and Buck ConvertersDocument4 pagesMPPT and Buck ConvertersJuthik BVNo ratings yet

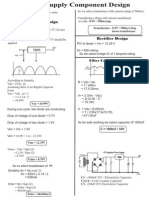

- Power Supply Design 2Document1 pagePower Supply Design 2Kunal Khandelwal100% (2)

- HSPICE Tutorial PDFDocument7 pagesHSPICE Tutorial PDFXman-exNo ratings yet

- Digital Image Forensics Using Sensor Noise: Jessica FridrichDocument11 pagesDigital Image Forensics Using Sensor Noise: Jessica FridrichPushpa Mohan RajNo ratings yet

- BPW17N Data SheetsDocument5 pagesBPW17N Data SheetssegalignoNo ratings yet

- Main Catalogue 9 Transformerer Power SupplyDocument12 pagesMain Catalogue 9 Transformerer Power SupplyRadu Fabian FishyNo ratings yet

- Silicon NPN Triple Diffused: ApplicationDocument8 pagesSilicon NPN Triple Diffused: ApplicationMario Rosas VargasNo ratings yet

- Biopotential Amplifier Design and ApplicationsDocument9 pagesBiopotential Amplifier Design and Applicationsagmnm1962No ratings yet

- Electronic CircuitsDocument3 pagesElectronic CircuitsManoj KavediaNo ratings yet

- Ac Phase Firing Circuit Using MicrocontrollerDocument6 pagesAc Phase Firing Circuit Using MicrocontrollerHarsh Vardhan Singh TomarNo ratings yet

- Operational AmplifierDocument112 pagesOperational AmplifierEdson TorresNo ratings yet

- WP Sierra Capillary Thermal Users GuideDocument29 pagesWP Sierra Capillary Thermal Users Guidegermantoledo244596No ratings yet

- 05understanding Power Quality Standards - DR FuadDocument88 pages05understanding Power Quality Standards - DR FuadMohsin ElgondiNo ratings yet

- Catalog Power Ind Oct-11Document44 pagesCatalog Power Ind Oct-11Suraj MohapatraNo ratings yet

- HTP-538 Service Manual Speaker PackageDocument18 pagesHTP-538 Service Manual Speaker PackagerigaboNo ratings yet

- Capacitors and Dielectric PDFDocument29 pagesCapacitors and Dielectric PDFJACOB MERCADONo ratings yet

- EEE431 Module 2Document27 pagesEEE431 Module 2Victor ImehNo ratings yet

- EC8353 Electron Devices and Circuits: Department of Electronics and Instrumentation EngineeringDocument15 pagesEC8353 Electron Devices and Circuits: Department of Electronics and Instrumentation EngineeringDr G Hari KrishnanNo ratings yet

- NS Analog and Mixed Signal Products1995Document246 pagesNS Analog and Mixed Signal Products1995Id Vágó MiklósNo ratings yet

- How To Build A Wien Bridge Oscillator CircuitDocument5 pagesHow To Build A Wien Bridge Oscillator CircuitLello FloNo ratings yet

- Electrical Transport MechanismsDocument106 pagesElectrical Transport MechanismslindaNo ratings yet

![IEE Proceedings - Microwaves Antennas and Propagation Volume 143 Issue 2 1996 [Doi 10.1049_ip-Map-19960260] Langley, J.D.S.; Hall, P.S.; Newham, P. -- Balanced Antipodal Vivaldi Antenna for Wide Bandwidth Phased Arrays](https://imgv2-2-f.scribdassets.com/img/document/190509945/149x198/aa546ff734/1423132972?v=1)