Professional Documents

Culture Documents

THE MP2905 HYSTERESIS VOLTAGE CONTROLLER by Zhen Li Application Engineer

Uploaded by

Vijay KrishnaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

THE MP2905 HYSTERESIS VOLTAGE CONTROLLER by Zhen Li Application Engineer

Uploaded by

Vijay KrishnaCopyright:

Available Formats

AN023

The MP2905 Hysteresis Voltage Controller

Application Note

AN023 Rev.1.0 www.MonolithicPower.com 1

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

The Future of Analog IC Technology

THE MP2905 HYSTERESIS VOLTAGE CONTROLLER

By Zhen Li

Application Engineer

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 2

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

ABSTRACT

The Hysteretic Voltage Control can provide fast transient response without additional loop

compensation. With the benefits of low cost and ease of implementation, its very popular for

power supplies of microprocessors and other high-slew-rate transition loads.

The MP2905 is a synchronous PWM buck controller with the hysteretic voltage-mode control.

This application note introduces the principle of hysteretic voltage control and several different

methods to design sufficient ripple voltage for stable operation of the synchronous Buck based

on MP2905, and at last, the 25A application design with MP2905.

1. INTRODUCTION OF THE PRINCIPLE OF HYSTERETIC VOLTAGE

CONTROL

High reference

Low reference

Hysteresis

Window

FB Voltage Ripple

High Side

Gate

Low Side

Gate

Figure 1 Principle of hysteretic voltage control

Compared with the fixed-frequency PWM control method, hysteretic voltage control doesnt

have an oscillator and the error amplifier. There is only a hysteresis window with two

references, high reference and low reference as figure 1 shown. The output voltage is fed back

to keep tracking references within the hysteretic window. Both references determine the turn-

on and turn-off of the transistor to control the output voltage.

When FB is higher than the high reference, high side switch turns off, low side switch turns on,

the output voltage falls down, FB falls down, too.

When FB drops to a lower level than the low reference, high side switch turns on, low side

switch turns off, and the output voltage rises up, and FB rise up, too.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 3

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

It can react on the load current transient in the same switching cycle that the transient occurs.

The key factor of hysteretic voltage control is to generate a sufficient amount ripple voltage on

FB-pin to compare with the references.

MPS offers a hysteretic voltage-mode control, synchronous PWM buck controller - MP2905.

This application note introduces several methods to generate the ripple voltage on FB and the

application example based on MP2905.

2. METHODS TO GENERATE THE RIPPLE VOLTAGE ON FB

There are several methods to generate the ripple voltage on FB. This chapter shows three

methods one by one.

2.1 Ripple Voltage from output Cap ESR.

It is known that the voltage ripple determined by ESR is the sawtooth waveform. So we

consider to feed back the ripple voltage on ESR of output capacitor directly to FB as shown in

figure 2.

MP2905

FB

SS

REF

GND

LG BST

SW

HG

IN

ILIM

VIN

VOUT

R1

R2

Cout

L

Cin

R3

C1

C2

C3

Q1

Q2

Figure 2 Method One - Feedback ripple from output cap ESR to FB

Take MP2905 as an example, the required sawtooth signal level is approximately 10 mV at the

comparing point (FB-pin). This determines the Vripple at the output node like this,

Vripple=V

OUT

x10mV/V

FB

, otherwise the circuit may be unstable. Ceramic capacitor is not

suitable due to the very low ESR here. Electrolytic capacitors and tantalum capacitors are

good choices, because of their larger ESR.

The operating frequency of this schematic depends on the ESR of output cap, capacitance,

inductance, V

IN

, V

OUT

and the voltage-divided resistances.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 4

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Figure 3 Equivalent circuit when High-side MOSFET on

VIN

L

ESR

Cout

R1

R2

VOUT

FB

i

L

When the high side MOS is on, the circuit performs as figure 3 indicates. Assume the turn on

period of the high side MOS is

IN OUT

V / V D , T D = where , T is the operating period. The ripple of

the output voltage is mainly determined by the ESR, so:

ESR * i V

L PP ripple

A =

(2.1)

L

i A can be calculated by:

, V V

T D

i

L

OUT IN

L

=

A

f L V

) V V ( V

i

IN

OUT IN OUT

L

= A (2.2)

Where f is the operating frequency.

The ripple voltage at FB:

PP ripple

V

2 R 1 R

2 R

V

+

= A (2.3)

Combining the formula (2.1), (2.2), and (2.3), we get:

f L V

) V V ( V

ESR

2 R 1 R

2 R

V

IN

OUT IN OUT

+

= A

V L V

ESR ) V V ( V

2 R 1 R

2 R

f

IN

OUT IN OUT

A

+

= (2.4)

Actually, the V A is not only due to the Hysteresis windows. It is influenced by the delay in the

circuit, such as driving signal propagation delay. Especially at higher frequency and higher V

IN

,

the delay and noise impact frequency. As a result, the frequency calculated given by (2.4) may

be inaccurate.

Moreover, the frequency is variable with load, because the inductance isnt constant. Its

variable with load and temperature. Figure 4 shows an example that inductance drops as

output current increasing. In this curve, the inductance @ 0A is 0.82uH, and drops to

0.65uH@25A. Suppose the frequency is 500kHz@0A, according to formula (2.4), the

frequency@25A should be (5000.82)/0.65=630kHz. Besides inductance variation, the output

ripple is also influenced by some parasitics such as ESL of output capacitor. This brings a

larger frequency variation with load. This method is not recommended for higher current

application.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 5

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Figure 4 A inductor curve- Inductance vs Current

If we use ceramic cap with lower ESR, the frequency will be very low based on the formula

(2.4). Due to the low frequency and the resultant large output voltage ripple, ceramic caps

cannot be used with this design method. If a ceramic is needed, the next method can

overcome these problems.

2.2 Ripple Voltage from DCR of inductor

In the Buck circuit, the ripple on the DCR of inductor is a sawtooth waveform. So we can feed

back the DCR voltage instead of the ESR ripple of the output cap, as shown in figure 5. R1

and C5 forms a lossless sensing circuit to get the voltage across the DCR of the inductor. R4

and the ceramic cap C4 filter the output ripple for C5. With this filter, the noise on the feedback

ripple of the output voltage can be greatly decreased.

This section will introduce this DCR feedback method based on the MP2905.

MP2905

FB

SS

REF

GND

LG BST

SW

HG

IN

ILIM

VIN

VOUT

Cin

Cout

L

C1

C2

R2

C4

C5

R1

C3

R4

R3

Figure 5 Method Two - Feedback ripple from inductors DCR to FB

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 6

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

2.2.1 Setting frequency

Figure 6 shows the equivalent circuit when low side switch is on. Assuming R4=0 and no C4,

the current going through C5 is:

) 1 ( 1 // 2

5 5

D

f V

C

dt

dv

C

R R

V

i

FB

c

A

= = = (2.5)

Figure 6 Equivalent circuit when Low-side MOSFET on

VOUT

Cout

L

R2

C5

R1

FB

ic

)

V

V

1 (

V

V

C

1

R

1

f

IN

OUT FB

5 FB

=

A

(2.6)

Where

2 1

2 1

2 // 1

R R

R R

R R R

FB

+

= = .

Assuming that V is equal to the hysteresis of the comparing window, it is obvious that the

frequency is variable with V

IN

. The higher input voltage, the higher frequency will be. We have

to also consider the circuit delay when calculating the voltage ripple on FB as Figure 7 shows.

The Delay consists of the FB propagation delay, dead time, driving circuit delay, etc. For

simple calculation, only the hysteresis and FB propagation delay are considered and V is

revised as:

DELAY HY

V V V + = ' A (2.7)

Where V

HY

is hysteresis of the comparing window, V

DELAY

is the voltage caused by delay. To

calculate the voltage caused by delay, V

DELAY

, we need to get the rising and falling slope of FB

ripple.

When high side switch turns on, FB is rising, figure 8 shows the Equivalent circuit. The current

going through C5 is:

FB

FB IN FB FB IN

5 C

R

V

1 R

V

2 R

V

1 R

V V

dt

dv

C i =

= =

Hysteresis

Window

FB

ripple

?V

Caused by delay

Caused by delay

FB

propagation

delay

SW

falls

FB

propagation

delay

SW rise

and Dead

time

SW

Figure 7 Delay Time influence on FB ripple

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 7

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

VOUT

Cout

L

R2

C5

R1

VIN

FB

ic

Figure 8 Equivalent circuit of high side MOS on at DCR ripple

The FB rising speed is:

)

R

V

1 R

V

(

C

1

C

i

dt

dv

FB

FB IN

5 5

C

= = = pe Rising_slo

(2.8)

The falling slope of FB can be calculated from the formula (2.5),

FB

FB C

R

V

5 C

1

5 C

i

= = ope Falling_sl

(2.9)

Table 1 lists the MP2905 FB propagation and dead time. The data are also listed in the

Datasheet of MP2905.

Table 1 FB propagation and dead time

FB

Propagation

Delay

FB Falling to LG Falling 50ns

FB Rising to HG Falling 70ns

Dead time

HG low to LG high 40ns

LG low to HG high 40ns

The voltage caused by FB propagation:

)

R

V

ns 20

1 R

V

ns 70 (

C

1

ns 50 slope _ Falling ns 70 slope _ g sin Ri V

FB

FB IN

5

1 DELAY

=

+ =

(2.10)

During the time SW falls and rises, and the dead time, the FB doesnt fall linearly because it is

affected by the driving circuit. Its difficult to calculate it accurately. We estimate it by 20ns of

linear falling slope.

1 R

V

ns 20

C

1

R

V

C

1

ns 20 )

R

V

1 R

V

(

C

1

ns 20

) ns 20 slope _ Falling ns 20 slope _ g sin Ri V

IN

5

FB

FB

5 FB

FB IN

5

2 DELAY

=

+ =

+ =

(2.11)

Then,

) 20

1

90 (

1

5

2 1

FB

FB IN

DELAY DELAY DELAY

R

V

ns

R

V

ns

C

V V V

=

+ =

(2.12)

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 8

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Combining formula (2.6), (2.7) and (2.12), the more accurate frequency can be obtained:

)

V

V

1 (

)

R

V

ns 20

1 R

V

ns 90 (

C

1

V

V

C

1

R

1

f

IN

OUT

FB

FB IN

5

HY

FB

5 FB

+

=

(2.13)

Where V

HY

is 22mV, V

FB

is 590mV, and

2 1

2 1

R R

R R

R

FB

+

= .

According to formula (2.13), frequency is variable with V

OUT

, V

IN

, C5 and Voltage-divided

resistors R1 and R2. As a result, the variation between frequency and input voltage is

nonlinear, a higher V

IN

doesnt mean a higher frequency.

2.2.2 Setting Output voltage

In this method, the Feedback point is at the SW node, so the voltage regulated is the DC

component of SW. It is equal to V

OUT

plus V

DCR

(inductor series resistance)

DCR FB OUT

V V

2 R

2 R 1 R

V

+

= (2.14)

Since V

DCR

is variable with load, then V

OUT

is also variable with load, which results in bad load

regulation at the output terminal. Choosing an inductor with smaller DCR (several milliohms)

can improve the load regulation.

2.2.3 Transient Response

Because the circuit feeds back the DC component of SW instead of the real V

OUT

, there is a

droop caused by the DCR of inductor in steady state, which benefits the transient

performance. Transient response is highly sensitive to the inductor, the sensing capacitor C5

and the voltage divided resistors R1 and R2. The time constant of the sensing network is

(R1C5), the inductors time constant is (L/DCR). If the time constant of the sensing network

C5 and R1 is the same as the inductor L and DCR, the transient response can be improved.

The formula below shows the relation.

DCR

L

C R = 5 1 (2.15)

If the formula (2.15) is satisfied, the voltage spike during the load transient can be minimized,

below is an example.

Test condition: V

IN

=12V, V

OUT

=1.8V, I

OUT

=0~5A, slew rate=1A/us,

Setting frequency=350KHz,

Selecting C5=10nF, R1=12.7k, R4=1, C4=4.4uF.

The time constant of C5 and R1 is:

s 10 127 5 C 1 R RC _

6

= = t

Choose an inductor L=2.2uH with DCR=10.2m.

The time constant of inductor is:

RC _ s 10 216 DCR / L LR _

6

t t > = =

Figure 9 is the test result. Its not good. There is a spike when load stepping.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 9

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Figure 9 Transient response at R5C1>L/DCR

Select another inductor with L=2.2uH, DCR=14m. The time constant of this inductor is:

s 10 157 DCR / L LR _

6

= = t .

Its near the time constant of R1 and C5. Figure 10 shows the transient response. There is no

spike when load stepping, the transient performance is improved a lot.

Figure 10 Transient Response at R5C1L/DCR

If one chose an inductor L=2.2uH, DCR=21m, then the time constant of inductor is:

RC _ s 10 04 1 DCR / L LR _

6

t t < = =

Figure 11 shows the transient response. There isnt a spike during the load transfer, but

transient response time is a little longer, and the voltage droop is bigger than figure 8 and

figure 9 because of the larger DCR.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 10

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Figure 11 Transient response at R5C1<L/DCR

In a word, to get the good transient response, the time constant of L and DCR should be

accordant with the time constant of R1 and C5.

2.2.4 Output sensing filter - R4 and C4

R4 and C4 filter is used to filter the noise on V

OUT

. If there is no filter or its insufficient, FB

ripple will be influenced by SW noise, badly. Then the frequency is extremely variable with load

current because of the SW noise varying with the load.

Lets monitor waveforms on point A and point B in figure12. The condition is 12V

IN

, 1.8V

OUT

,

I

OUT

=0~5A, C5=10nF, R7=12.7k, R4=10, C4=100nF.

VOUT

Cout

L

R2

C4

C5

R4

A

B

Figure 12 Detect point A and point B

R1

Figure 13 shows waveforms under no load condition. The filter corner frequency is not low

enough to get rid of noise, so there is a ripple at point B. FB ripple (point A) is influenced by

noise a little. The frequency is about 300KHz.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 11

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Figure 13 FB ripple at no load condition with insufficient filter

Figure 14 shows waveforms at 5A load. The noise is bigger at 5A load, therefore the waveform

at point B is not a DC value. The influence of the increased ripple on the FB(point A) causes

the frequency to increase from 300kHz up to about 400kHz.

Figure 14 FB ripple at 5A load with insufficient filter

When we set R4=10, C4=4.7uF, the bandwidth is reduced and the influence from noise is

eliminated.

FB ripple at no load condition FB ripple at 5A load

Figure 15 FB ripple with sufficient filter

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 12

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

In figure15, FB ripple is not influenced by V

OUT

ripple. Point B is very clean, and the frequency

drifts little under different load condition: 340KHz under no load condition and 364KHz under

5A condition. However, this doesnt mean that the lower corner frequency of the filter the

better. Too low corner of a frequency in the filter will worsen the transient response. So, there

is a tradeoff between frequency variation and transient response. Based on the test result, it is

recommended to set R4=1, C4=4.4uF. It also has some relationship with layout. Its better to

keep the wire from V

OUT

to point B as short as possible, and point B should be close to chip.

Then a smaller filter may be enough.

For the other parameters design, please refer to MP2905 datasheet.

Although we can use ceramic caps at the output in this method, there are some additional

disadvantages, such as bad load regulation, variable frequency with load current, and a more

complex design. The third method may be better than the present one with respect to these

issues.

2.3 Ripple Voltage from external circuit

In this method, we use three external components to generate ripple.

MP2905

FB

SS

REF

GND

LG BST

SW

HG

IN

ILIM

VIN

VOUT

Cin

Cout

L

C1

C2

R1

C3

R3

R2

C5

C4

R4

Figure16 Method Three - Feedback ripple from external circuitry to FB

Figure 16 shows a simplified diagram based on MP2905. The voltage divider R1 and R2 feeds

back the output voltage. C4, R4, and C5 circuitry form an additional ramp signal generator. C4

is a DC-blocking capacitor. Its used to block the SWs DC component. Only the AC

component is sent to the filter R4 and C5 to generate the ripple voltage for comparison with the

hysteresis. The two components are summed together at FB. Because the DC component at

FB is only decided by V

OUT

, so there is no droop.

The V

OUT

can be decided by the reference voltage and the R-divider:

FB OUT

V )

2 R

1 R

1 ( V + = (2.16)

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 13

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

By proper selection of R4 and C5, we can get the amplitude of the additional ramp signal

generator which is much higher than the output ripple. As a result, the output ripple can be

ignored, the switching frequency mainly depends on R4, C5 values. It is impacted little by

output filter characteristics including inductance, the DCR of inductor, ESR, ESL and the

capacitance of the output capacitor.

Figure17 shows the process of getting ramp signals. SW is a square waveform including DC

and AC components. After the DC blocking capacitor C4, the DC component is decoupled.

The waveform at point D is a square wave without DC component, its high level is (V

IN

-V

OUT

),

low level is (-V

OUT

). Across the filter R4 and C5, the square wave is integrated to the sawtooth

ripple.

VOUT

Cout

L

R1 C4

R4

SW

FB

DC COMPONENT of

SW = VOUT+V

DCR

Vout

t

V

Vin

0

t

V

Vin-Vout

0

Vout

V

t

FBs ripple

D

R2

C5

Figure17 Waveform of ripple generation.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 14

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

2.3.1 Setting frequency

Figure 18 shows the equivalent circuit of high side MOS on.

VOUT

Cout

L

R1 C4

R4

Vin

FB

C5

R2

D

Vin-Vout

i

R4

i

C5

i

R1

i

R2

Figure 18 Equivalent circuit of high side MOS on

According to Kirchhoffs electric current law (KCL), we can get:

1 4 2 5 R R R C

i i i i + = + (2.17)

Consider V

FB

as a stable DC voltage, the currents through R1 and R2 are:

1

1

2

2

,

R

V V

i

R

V

i

FB OUT

R

FB

R

= =

substituting V

OUT

by (2.16),

2 2 1

/ R V i i

FB R R

= = , therefore,

4 R 5 C

i i = (2.18)

These formulas show that DC component goes through the voltage divider formed by R1 and

R2. AC component goes through R4 and C5. FB can be considered as zero, when analyzing

the AC signal. Therefore:

4

4

R

V V

i

OUT IN

R

= (2.19)

Combining (2.17) and (2.18) yields:

DT

V

C

dt

dv

C

R

V V

i i

OUT IN

R C

A

= =

= =

5 5

4

4 5

(2.20)

V R C V

V V V

f

IN

OUT IN OUT

A

=

4 5

) (

(2.21)

In the same way, V consists of a hysteresis window and a delay component as in formula

(2.7). The delay is the same as that described in figure 6. First, calculate the rising and falling

slope of FB.

According to formula (2.20), FB ripple rising slope is:

4 R 5 C

V V

5 C

i

dt

dv

OUT IN 5 C

= = = Slope Rising (2.22)

Figure 19 shows the equivalent circuit of low side MOS on.

4 4

4 5 5

) ( 0

R

V

R

V

i

dt

dv

C i

OUT OUT

R C

=

= = = (2.23)

FB ripple falling slope is:

4 5 5

Slope Falling

5

R C

V

C

i

dt

dv

OUT C

= = = (2.24)

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 15

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Cout

L

R1 C4

R4

FB

C5

R2

D

-Vout

i

R4

i

C5

Figure 19 Equivalent circuit of low side MOS on at external ripple

Calculate the FB propagation delay voltage as in formula (2.10),

) ns 20 V ns 70 V (

R C

1

ns 50

R C

V

ns 70

R C

V V

ns 50 slope _ Falling ns 70 slope _ Rising V

OUT IN

4 5

4 5

OUT

4 5

OUT IN

1 DELAY

=

+ =

(2.25)

Estimate the dead time and driving circuit delay voltage as in formula (2.11),

4 5

IN

4 5

OUT

4 5

OUT IN

2 DELAY

R C

V

ns 20

R C

V

ns 20

R C

V V

ns 20

ns 20 slope _ Falling ns 20 slope _ Rising V

=

+ =

(2.26)

The total delay voltages are:

) 20 90 (

1

4 5

2 1 OUT IN DELAY DELAY DELAY

V ns V ns

R C

V V V

= + = (2.27)

Combining (2.7), (2.27) and (2.21):

)

20 90

(

) (

) (

4 5

4 5

4 5

R C

V ns V ns

V R C V

V V V

V R C V

V V V

f

OUT IN

HY IN

OUT IN OUT

IN

OUT IN OUT

+

=

A

=

(2.28)

Where V

FB

is 590mV

Frequency is influenced by V

OUT

, V

IN

, C5 and R4. Assuming V

OUT

, V

IN

are constant, we can

easily set the frequency by C5 and R4. And frequency also has nonlinear variation with input

voltage.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 16

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Note: If the time constant of C5 and R4 is too large, and the duty cycle is large, such as

greater than 30%. The frequency calculated by formula 2.28 is not accurate, because the FB

ripple doesnt rise and fall linearly. Usually, we recommend selecting R4 10%~30% less than

the calculation.

2.3.2 Transient Response

In this configuration, there is a cap C5 paralleled with the low side voltage divided resistor.

Obviously, it could worsen the transient response because of the delay. In order to minimize

the effect on the transient, the capacitance of C5 should be small. However, too small of a C5

may influence the stability of FB ripple and introduce noise on FB. Capacitance between 2nF

and 10nF is recommended for C5. Since frequency is set by C5 and R4, so its better to use a

smaller C5 and bigger R4 to set the frequency.

Besides decreasing C5s value, voltage divided resistances R1 and R2 should be small

enough, too. Small R1, R2 and C5 means short time constants, so that the time delay from

V

OUT

to FB pin is short. When the output changes with load stepping, the Vo will be feedback

to FB pin with little delay. So the circuit responds to the Vo quickly. However, the no load

power consumption is higher with smaller voltage divided resistances.

The inductor also influences the transient response. Small inductance will have better transient

response, but higher current ripple, so, there is a tradeoff.

2.4 SUMMARY

Method one is the simplest way to generate the ripple voltage for hysteresis voltage controller.

But, it needs a large ripple on ESR to guarantee the stability and set the frequency. It is well

known that ESR of capacitor cant be designed by application. So the frequency setting has to

depend on the existing ESR parameter. Generally, the higher the frequency, the lower the

voltage ripple for a given output capacitance will be. So if the ESR is not big enough, circuit

may be unstable at higher frequencies.

Method two can use ceramic caps at the output. The frequency is set by R1, R2 and the

sensing capacitor C5 (see figure 4). However, the load regulation characteristics make the

design not suitable for higher current applications.

Method three seems to be a good solution for any current and any frequency application.

Frequency is easy to be set with three additional components, which are independent of the

output inductor and the output capacitor. The load regulation and transient response are good

as well.

3. MP2905 DESIGN EXAMPLE FOR 25A APPLICATION

Compared to the other two, method three is a good choice for 25A application. The 25A

application circuit is shown in figure20. The spec is V

IN

=12V (typ.), V

OUT

=1.8V, and I

OUT

=25A.

The parameter design of the 25A circuit is detailed introduced as follows.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 17

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

MP2905

FB

SS

REF

GND

LG BST

SW

HG

IN

ILIM

VIN

VOUT

Cin

Cout

L

C1

C2

R1

C3

R3 R2

C5

C4

R4

Figure20 Method Three - Feedback ripple from external circuitry to FB

C6

3.1 Setting frequency

With higher switching frequency, the transient can be better, and small output LC filter can be

used, but power dissipation is higher. Considering these factors, the frequency is set at 300

kHz.

First, choose C5. As chapter 2.3.2 described, a 2.2nF is recommended.

Second, calculate R4 as in formula (2.28). Substitute in the known parameters,

k 8 . 83

V C V

) V ns 20 V ns 90 ( V

f

) V V ( V

R

HY 5 IN

OUT IN IN

OUT IN out

4

~

=

Choose R4=82k.

3.2 Setting the output voltage

External voltage divider resistors (R1 and R2 in figure20) are used to set the output voltage.

Per the chapter 2.3.2 description, voltage divider resistances should be small enough to get

good transient performance. So, set R2s value to be 1k, R1 is determined by:

) 1

V

V

( 2 R 1 R

FB

OUT

= (2.29)

Where V

FB

=0.59V, V

OUT

=1.8V, R2=1k. Therefore,

k 05 . 2 ) 1

59 . 0

8 . 1

( 1000

) 1

V

V

( 2 R 1 R

FB

OUT

~ =

=

Choosing a typical value 2.1k for R1

3.3 Selecting the inductor

The inductor is required to supply constant current to the output load while being driven by the

square input voltage. A larger value inductor is favorable to reduce ripple current and lower

output ripple voltage. However, the larger value inductor will have a larger physical size, higher

series DC resistance, and/or lower saturation current. Furthermore, the transient performance

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 18

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

may be poor. A good rule for selecting the inductance is to allow the peak-to-peak ripple

current in the inductor to be approximately 30% of the maximum output current. Also, make

sure that the peak inductor current is below the maximum switch current limit. The inductance

value can be calculated by:

) 1 (

IN

OUT

L S

OUT

V

V

I f

V

L

A

= (2.29)

Where V

IN

is the input voltage, V

OUT

is the output voltage, f

S

is the switching frequency, and I

L

is the peak-to-peak inductor ripple current, recommended to be 30% of the maximum output

current. Substitute all the known parameters,

uH 68 . 0 )

12

8 . 1

1 (

25 3 . 0 10 300

8 . 1

)

V

V

1 (

I f

V

L

3

IN

OUT

L S

OUT

=

=

=

A

The DC current rating of the inductor must be higher than the maximum output current to keep

the temperature rise within the desired range. The inductor also needs to have a low DCR to

achieve good efficiency, as well as enough room above peak inductor current before

saturation. The peak inductor current can be estimated as follows:

) 1 (

2

IN

OUT

S

OUT

LOAD LP

V

V

L f

V

I I

+ = (2.30)

The maximum inductor peak current can by calculated from formula (2.30), as 28.1A.

A 1 . 28 )

12

8 . 1

1 (

10 82 . 0 10 300 2

8 . 1

25

)

V

V

1 (

L f 2

V

I I

6 3

IN

OUT

S

OUT

LOAD LP

~

+ =

+ =

Considering all above factors, select such an inductor: 0.82uH with 0.9m DCR, 27A current

rating, and 35A saturated current which is higher than 28.1A.

3.4 Selecting Power MOSFETs

The MOSFETs are the key points for circuit efficiency. The major parameters we should

consider are:

1) On-resistance, R

DS_ON

: the lower, the better it is.

2) Continuous Drain Current (@10sec), I

DS

: it should be higher than the peak current under full

load condition. Pay attention to the variation of I

DS

with temperature.

3) Maximum drain-to-source voltage, VDS(MAX): it should be at least 20% higher than the input supply

rail.

4) Total gate charge, Qg: the lower, the better it is.

For high-side MOSFET, the main power loss consists of conduction loss, switching loss, and driving

loss.

The high-side MOSFET conduction loss can be calculated by:

D R I P

DSON _ HS

2

LOAD conduction _ HS

= (2.31)

Where D is the duty cycle, its defined by

IN OUT

V / V D =

High-side MOSFET switching loss is estimated by:

S f r LOAD IN switching _ HS

f ) t t ( I V

2

1

P + = (2.32)

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 19

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Where t

r

is the rise time of the high-side MOSFET driving signal Vgs, t

f

is the fall time of the

high-side MOSFET driving signal Vgs, f

S

is the switching frequency.

High-side MOSFET driving loss is calculated by:

drive S HS _ g drive _ HS

V f Q P = (2.33)

Where Vdrive is the high-side MOSFET driving voltage. The value in MP2905 is 5V.

For low-side MOSFET, there isnt switching loss, conduction loss is the main loss. We choose

a MOSFET with lower R

DS_ON

. The low-side MOSFET loss consists of conduction loss, driving

loss and body diode conduction loss.

The Low-side MOSFET conduction loss is calculated by:

) D 1 ( R I P

DSON _ LS

2

LOAD conduction _ LS

= (2.34)

Low-side MOS driving loss is calculated by:

drive S LS _ g drive _ LS

V f Q P = (2.35)

Body diode conduction loss is calculated by:

S deadtime LOAD F bodydiode

f t I V 2 P =

(2.36)

Where V

F

is body diode forward voltage drop, t

deadtime

is the transition time between high-side

MOSFET and low-side MOFETS.

Except for the losses above, there is output cap loss in both the high side MOSFET and the

low side MOSFET. Output cap loss is defined by:

S

2

DS DS Cds

f V C

2

1

P =

(2.37)

where C

DS

is the equivalent output cap of MOSFET.

For the spec: V

IN

=12V, V

OUT

=1.8V, I

OUT

=25A, the duty cycle is very small, then conduction loss

in the high side MOS is limited. Switching loss accounts for the main part. So when selecting

the high side MOS, we should first consider tr and tf of MOS.

For the low side MOS, the main loss is conduction loss, so the Rds-on should be as small as

possible. We can even parallel two MOSFETs at low side to minimize the Rds-on. However,

we should pay attention to the driving loss. The Qg is very large if two MOSFETs are

paralleled on the low side. The driving loss will cause the temperature to rise in MP2905.

Below is an example for MOS selection, use one MOS at high side, two MOS at low side.

Table 2 shows several MOSFETs.

The tr and tf of MOS1 and MOS2 are small, so they are used as high side MOS. MOS3 and

MOS4 are fit for low side MOS because of their low R

DS_ON

. Estimate the power loss in each

MOS.

Table 2 MOSFET for selection

Part Number Rds-

on(m)

Qg(nC) Tr(nS) Tf(nS) V

F

(V)

1 AP3R303GMT-HF 5 13.3 5.5 17 -

2 AP0603GM 10.5 9 4.5 10.5 -

3 Si7658ADP 2.8 34 - - 1.1

4 AP2R403GMT-HF 3.6 20.5 - - 1.3

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 20

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

According to loss analysis table3, the loss of MOS1 is lower, it is a good choice for high side

MOS at the spec because of its lower tr, tf and lower Rds-on. MOS2s loss is higher because

of its higher Rds-on, but its switching loss is very small, so at higher frequency or higher V

IN

spec, MOS2 may have the better performance than MOS1.

Table3 loss analysis M1 and M2 (Vin=12V, Vo=1.8V, Io=25A, fs=300kHz)

MOS1 MOS2

Conduction loss 0.47W 0.98W

Switching loss 1.01W 0.675W

Driving loss 0.02W 0.014W

Total loss

(neglect output cap loss)

1.5W 1.669W

According to loss analysis table4, the loss of MOS3 is much lower than MOS 4, but the Qg and

driving loss is much higher. MP2905s driving signal is generated by internal LDO. If the LDOs

efficiency is not high enough, then larger Qg and higher driving loss could cause higher

temperature rise at chip. The junction to ambient thermal resistance of MP2905 is 150

o

C/W.

0.1W driving loss causes 15

o

C temperature rise. Considering the loss of the MP2905 internal

LDO, the temperature rise may be higher than 30

o

C. As a tradeoff, MOS4 with higher total loss

but lower driving loss is a more reasonable choice.

Table4 loss analysis M3 and M4 (Vin=12V, Vo=1.8V,Io=25A,fs=300kHz)

MOS3 MOS4

Conduction loss 0.74W 0.96W

Body diode conduction loss 0.66W 0.78W

Driving loss 0.1W 0.06W

Total loss

(neglect output cap loss)

1.5W 1.8W

For the driving circuit of the MOS, its better to slow down the high side and low side MOS turn

on speed. It reduces the noise caused by switching, and insures enough dead time to avoid

shoot through. We recommend placing series driving resistor to slow down the turn on speed.

The resistance shouldnt be too large(less than 10 is ok), otherwise the switching loss will

increase. Part of the driving loss is now in the driving resistors which are outside the chip.

Therefore, the temperature rise of chip can be lower. An anti-parallel diode is recommended,

so that the turn-off speed is not reduced.

3.5 Current Limit setting

MP2905 current limit can be set by an external resistor (R3 in figure 16) which is connected

between ILIM pin and the drain of the high side MOSFET. An internal 50uA sink current sets a

voltage drop on the resistor. The voltage drop compares to the high-side MOSFET voltage

drop (V

DS

) to set the peak current limit threshold. Below is the diagram of the current limit

function:

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 21

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

--

+

--

+

+ --

ILIM R

ILIM

V

IN

Rdson_max

High Side

Switch

OC COM

SW

Ids

SW

V+

V-

Figure 21Current Limit Functional Diagram

The voltage drop on the high side MOSFET is:

(max) R (max) I (max) V

ON _ DS DS ON _ DS

= (2.38)

Where I

DS

(max) equals the max peak inductor current ILP (max).

Then, R

ILIM

can be calculated using the V

DS_ON

(MAX) with the following formula:

) (

50

(max)

_

O =

uA

V

R

ON DS

ILIM

(2.39)

R

ILIM

should be kept in the range of 1k~ 8k.

The R

DS_ON

is variable with temperature. At higher temperature, R

DS_ON

is higher, and then the

current limit will be lower than the calculation. We have to consider the temperature coefficient

of R

DS_ON

. Usually, the temperature coefficient kth is 1.2@75

o

C, 1.3@90

o

C, and for more exact

value, please refer to the DS of the MOS you select.

Then the formula 2.39 can be corrected as:

) (

50

(max)

_

O

=

uA

kth R I

R

ON DS DS

ILIM

(2.40)

Design example: suppose we choose a high side MOS with 5m R

DS_ON

, 1.3 kth and 0.82uH

inductor as above. Then the peak to peak value of inductor current is 6.2A. Set the max DC

current at 27A, then the peak current of inductor is:

A I

LP

1 . 30 ) 2 / 2 . 6 ( 27 = + =

Therefore:

V

DS_ON(max)

=30.1A5m1.3=195.7mV.

R

ILIM

=195.7mV/50uA=3.91k.

The oscillation at SW when the high side MOS is on, the distribution of R

DS_ON

, the current

sense program current source and the temperature drift of the current sense program can

influence the precision of the current limit. To ensure the circuit can always work at 25A, its

better to set the R

ILIM

to be 15%~20% higher than the theoretic calculation. In the example, we

can set R

ILIM

at 4.5k.

A small parallel capacitor (C6 in figure 20) is necessary to filter the noise on R3. 10nF is

recommended. Figure22 shows the noise waveform on R3, with C6 and without C6.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 22

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Figure22. Noise Waveform on R3 with C6 and without C6.

3.6 Setting Input Capacitor

The input current to the step-down converter is pulsating, therefore a capacitor is required to

supply the AC current to the step-down converter while maintaining the DC input voltage. Use

low ESR capacitors for the best performance. Ceramic capacitors with X5R or X7R dielectrics

are highly recommended because of their low ESR and small temperature coefficients. The

effect of electrolytic capacitors is limited, because the electrolytic capacitor is not fit to work at

higher frequency.

Since the input capacitor (Cin) absorbs the input switching current, it requires an adequate

ripple current rating. The RMS current in the input capacitor can be estimated by:

) 1 (

IN

OUT

IN

OUT

LOAD Cin

V

V

V

V

I I =

The worse case condition occurs at V

IN

= 2V

OUT

, where I

Cin

= I

LOAD

/2.

For simplification, choose the input capacitor whose RMS current rating greater than half of the

maximum load current.

Make sure that capacitance is enough to provide sufficient charge to prevent excessive voltage

ripple at input. The input voltage ripple can be estimated by:

(1 )

LOAD OUT OUT

IN

S in IN IN

I V V

V

f C V V

A =

Big input ripple worsens efficiency and causes higher temperature rise in capacitors, and

impacts the stability of the circuit.

3.7 Selecting Output Capacitor

The output capacitor (Cout) is required to maintain the DC output voltage. Ceramic, tantalum,

or low ESR electrolytic capacitors are recommended. A low ESR capacitor is preferred to keep

the output voltage ripple low. The output voltage ripple can be estimated by:

1

(1 ) ( )

8

OUT OUT

OUT ESR

S IN S OUT

V V

V R

f L V f C

A = +

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 23

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Where L is the output inductance and R

ESR

is the equivalent series resistance (ESR) of the

output capacitor.

In the case of a ceramic capacitor, the impedance at the switching frequency is dominated by

the capacitance. The output voltage ripple is mainly caused by the capacitance. The output

voltage ripple can be simplified:

2

(1 )

8

OUT OUT

OUT

S OUT IN

V V

V

f L C V

A =

In the case of tantalum or electrolytic capacitors, the ESR dominates the impedance at the

switching frequency. For simplification, the output ripple is approximated to:

(1 )

OUT OUT

OUT ESR

S IN

V V

V R

f L V

A =

In method three, the output ripple will influence the FB ripple. The system will be unstable with

large output ripple. So, we should minimize the output ripple with a big capacitance and low

ESR. A POSCAP is recommended at the output for its large capacitance and low ESR.

3.8 PCB layout guideline

PCB layout is very important to achieve stable operation. Follow these guidelines:

1) Keep the path of switching current short and minimize the loop area formed by the input

cap, high-side MOSFET and low-side MOSFET.

2) IC bypass ceramic capacitors are suggested to be put close to the IN Pin.

3) Ensure all feedback connections are short and direct. Place the feedback resistors as close

to the chip as possible.

4) Route SW away from sensitive analog areas such as FB.

5) Connect IN, SW, and especially GND respectively to a large copper area to improve chip

thermal performance and long term reliability.

6) It is suggested to add a snubber circuit across the high side MOSFET (IN pin and SW pin)

so as to reduce the SW spike.

7) The signal GND and power GND should be connected by a single point. This will ensure a

clean control signal.

8) For 25A application, four-layer or even a six-layer PCB is recommended. If we use a four

layers PCB, make sure the copper area is big enough to create a low thermal resistance and

keep the temperature rise small. If the size of the PCB is limited, another heat sink should be

used.

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 24

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

MP2905

FB

SS

REF

GND

LG BST

SW

HG

IN

ILIM

Vin

Vo

Cin

Cout

L

C1

C2

R1

C3

R3

R2

C5

C4

R4

Figure23 Method Three - Feedback ripple from external circuitry to FB

C6

3.9 25A demo board SCH, BOM, PCB

Figure 24Demo Board SCH

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 25

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Table5 Demo Board BOM

RefDes Value Description Package Manufacturer

C1A,C1B 22uF Ceramic Cap,25V,X5R 1210 Murata

C2A 22uF Ceramic Cap,10V,X7R 1210 Murata

C2B 100uF Ceramic Cap,6.3V,X5R 1210 Murata

C2C 330uF Poscap, 6.3V Poscap Sanyo

C3,C5 10nF Ceramic Cap,50V,X7R 0603 TDK

C4 4.7uF Ceramic Cap,10V,X5R 0805 TDK

C6 1uF Ceramic Cap,50V,X7R 0805 Murata

C7 100nF Ceramic Cap,50V,X7R 0603 TDK

C8 3.9nF Ceramic Cap,50V,X7R 0603 Murata

C9,C11 2.2uF Ceramic Cap,10V,X7R 0603 Murata

C10 2.2nF Ceramic Cap,50V,X7R 0603 TDK

R1 2.1K Film Res,1% 0603 Yageo

R2 1K Film Res,1% 0603 Yageo

R3 4.99K Film Res,1% 0603 Yageo

R4 2.49 Film Res,1%

R5 82K Film Res,1% 0603 Yageo

R6 NS

R7 0 Film Res,5% 0603

R8 2 Film Res,5% 0603

R11 4.99 Film Res,1% 0603 Yageo

D1 B0530-W, 30V0.5A SOD-123 Diodes

D2 B0530-Ws-7-F,30V,0.5A SOD-323 Diodes

Q1 AP3R303GMT-HF, 30V,105A,

Rds_on=5m@4.5Vgs,

Qg=13.3nC,tr=5.5ns,tf=17ns@10Vgen

PowerPAK

SO-8

Apec

Q2,Q3 AP2R403GMTHF,30V,130A,

Rds_on=3.8m@4.5Vgs, Qg=20.5nC

PowerPAK

SO-8

Apec

Q4 NS

L1 0.82uH Inductor, Rated current=27A,Saturation

current=35A,

DCR=0.9m,

SMT Wurth

U1 MP2905 MSOP10 MPS

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 26

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

Top layer IN1

IN2 BOT

Figure 25Demo Board Layout

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 27

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

3.10 Demo board test result

1. FB Ripple

Test condition: Vin=12V, Vout=1.8V

No load 25A load

Figure 26FB Voltage Ripple

2. Output Ripple

Test condition: Vin=12V, Vout=1.8V

No load 25A load

Figure 27Output Voltage Ripple

SW

FB

AC Coupling

SW

FB

AC Coupling

Vo

SW

SW

Vo

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

AN023 Rev.1.0 www.MonolithicPower.com 28

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

3. Transient

Test condition: Vin=12V, Vout=1.8V,0~25A,2.5A/us

Figure 28Transient Response

4. Efficiency

Test condition: Vin=12V, Vout=1.8V

Figure 29Efficiency Curve

0%

10%

20%

30%

40%

50%

60%

70%

80%

90%

100%

0 5 10 15 20 25 30

Io(A)

E

f

f

i

c

i

e

n

c

y

Vo

SW

Vo

SW

Vo

SW

AN023 THE MP2905 HYSTERESIS VOLTAGE CONTROLLER APP. NOTE

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third

party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not

assume any legal responsibility for any said applications.

AN023 Rev.1.0 www.MonolithicPower.com 29

8/30/2011 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

2011 MPS. All Rights Reserved.

4. CONCLUSION

We compared three different methods to do hysteresis control based on the MP2905. Method

three can fulfill any request especially with respect to the high output current case. For method

3, ceramic capacitors can be used as the output capacitors. Ceramic caps keep the output

ripple lower and the physical size very compact. The frequency is independent of output filter

characteristics and parasitics. The transient response of this hysteresis control is excellent with

the careful design of the feedback loop.

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- ECE3204 D2013 Lab2Document9 pagesECE3204 D2013 Lab2Khalil2097No ratings yet

- Prekidačka NapajanjaDocument48 pagesPrekidačka NapajanjaDamir PranjkovicNo ratings yet

- AN1114 - Switch Mode Power Supply (SMPS) Topologies (Part I) - MicrochipDocument48 pagesAN1114 - Switch Mode Power Supply (SMPS) Topologies (Part I) - MicrochipbmmostefaNo ratings yet

- Switch Mode Power Supply (SMPS) Topologies (Part I) - MicrochipDocument48 pagesSwitch Mode Power Supply (SMPS) Topologies (Part I) - MicrochipGhulam AbbasNo ratings yet

- FM Modulators: Experiment 7Document17 pagesFM Modulators: Experiment 7banduat83No ratings yet

- OP TypesDocument17 pagesOP TypesAhmad DboukNo ratings yet

- EE680Lab Experiment6-7Document21 pagesEE680Lab Experiment6-7Amro AbusailNo ratings yet

- Frequency Modulator Experiment ReportDocument7 pagesFrequency Modulator Experiment ReportreganoctNo ratings yet

- Digital Control of A Three Phase 4 Wire PWM Inverter For PVDocument9 pagesDigital Control of A Three Phase 4 Wire PWM Inverter For PV7788778887No ratings yet

- Experiment E1.07 Differential AmplifierDocument16 pagesExperiment E1.07 Differential AmplifierMohd FuadNo ratings yet

- Design of Cmos BufferDocument5 pagesDesign of Cmos BufferVarunKaradesaiNo ratings yet

- Boost ConvertersDocument4 pagesBoost ConvertersSyed Mohammad FarooqueNo ratings yet

- A Technique For Improving Input Current Zero-Crossing Distortion of Boost PFC Converters For Airborne SystemDocument7 pagesA Technique For Improving Input Current Zero-Crossing Distortion of Boost PFC Converters For Airborne SystemInternational Journal of Research in Engineering and ScienceNo ratings yet

- Design Differentiator AmplifierDocument10 pagesDesign Differentiator Amplifierhareesh.makesu0% (1)

- Applications of Balanced ModulatorDocument5 pagesApplications of Balanced ModulatorSomeshwar GaddalaNo ratings yet

- Design Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED LightingDocument13 pagesDesign Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED Lightingshiva1luNo ratings yet

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsFrom EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNo ratings yet

- Application Note AN-6027: Design of Power Factor Correction Circuit Using FAN7530Document16 pagesApplication Note AN-6027: Design of Power Factor Correction Circuit Using FAN7530Malanie Sriya De SilvaNo ratings yet

- Implementation of PSR in Flyback ConvertersDocument9 pagesImplementation of PSR in Flyback ConvertersNehaoua FaresNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Acl-03-04 - Exp-03-A1 PR PDFDocument11 pagesAcl-03-04 - Exp-03-A1 PR PDFDESMALANILS48No ratings yet

- Question Bank - 20200813205900Document4 pagesQuestion Bank - 20200813205900M N ChethanNo ratings yet

- Impact of Variable Switching Frequency Over Power Loss On Converter TopologiesDocument6 pagesImpact of Variable Switching Frequency Over Power Loss On Converter TopologiesskrtamilNo ratings yet

- Very Wide Input Voltage Range-Flyback (90V To 600V AC)Document12 pagesVery Wide Input Voltage Range-Flyback (90V To 600V AC)senkum812002No ratings yet

- Dynamic Offset Cancellation TechniquesDocument30 pagesDynamic Offset Cancellation TechniquesashishmanyanNo ratings yet

- Acl-03-04 - Exp-03-E PR PDFDocument14 pagesAcl-03-04 - Exp-03-E PR PDFDESMALANILS48No ratings yet

- RESEARCH of Communications Research No. 2Document19 pagesRESEARCH of Communications Research No. 2Princess EsmejardaNo ratings yet

- Understanding Power Factor: Application NoteDocument6 pagesUnderstanding Power Factor: Application NoteAsghar MajeedNo ratings yet

- Closed Loop DC-DC Buck ConverterDocument8 pagesClosed Loop DC-DC Buck ConverterKarThiNo ratings yet

- Smart Voltage Stabilizer Using PIC16F877ADocument8 pagesSmart Voltage Stabilizer Using PIC16F877AAswathy CjNo ratings yet

- Experiment 5Document21 pagesExperiment 5Jervin JamillaNo ratings yet

- Chapter 1: Understanding Op-AmpsDocument11 pagesChapter 1: Understanding Op-Ampsrockrockyrocker123No ratings yet

- Expt.3 ME2612L Individual Report Group 5Document15 pagesExpt.3 ME2612L Individual Report Group 5Dan Joshua EspinaNo ratings yet

- Op-Amps: I. Practical Op-AmpDocument7 pagesOp-Amps: I. Practical Op-AmpSteven Nelson100% (1)

- Am Am: QRP QRPDocument6 pagesAm Am: QRP QRPagama1188No ratings yet

- Unijunction Transistor: by Matthew H. Williams Back To TheDocument6 pagesUnijunction Transistor: by Matthew H. Williams Back To TheRachmat Guntur Dwi PutraNo ratings yet

- Exp 9 Boost ConverterDocument8 pagesExp 9 Boost ConverterusmpowerlabNo ratings yet

- Phase-Locked Loop With Leakage and Power/Ground Noise Compensation in 32nm TechnologyDocument6 pagesPhase-Locked Loop With Leakage and Power/Ground Noise Compensation in 32nm TechnologytonyNo ratings yet

- Implementing The TL431 Feedback LoopDocument10 pagesImplementing The TL431 Feedback LoopAnand KumarNo ratings yet

- Electronics Lab Exp3.pdfDocument17 pagesElectronics Lab Exp3.pdfgacc4sitesNo ratings yet

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesFrom EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesNo ratings yet

- How To Measure RF TransformersDocument16 pagesHow To Measure RF Transformersعلاء الليبيNo ratings yet

- AN848 DynamicDocument9 pagesAN848 DynamicAnonymous QakmLc3kTINo ratings yet

- AM Modulation and Demodulation LabDocument8 pagesAM Modulation and Demodulation LabAhmadAkhbariNo ratings yet

- Current Mirrors: Basic BJT Current MirrorDocument8 pagesCurrent Mirrors: Basic BJT Current MirrorjagruthimsNo ratings yet

- Exp 8 Buck ConverterDocument7 pagesExp 8 Buck Converterusmpowerlab50% (2)

- Electronics Laboratory DC Power Supply CircuitsDocument10 pagesElectronics Laboratory DC Power Supply CircuitsDen CelestraNo ratings yet

- Bridgeless PFCDocument18 pagesBridgeless PFCsolid690No ratings yet

- TR Netzfilter-Die Letzte Huerde Im Schaltnetzteil enDocument9 pagesTR Netzfilter-Die Letzte Huerde Im Schaltnetzteil enDavid Isaias Jaimes ReyesNo ratings yet

- Sample Lab ReportDocument8 pagesSample Lab ReportbakerkjNo ratings yet

- Compensation Method Peak Current Mode Control Buck AN028 enDocument13 pagesCompensation Method Peak Current Mode Control Buck AN028 ensadqazwsxNo ratings yet

- ECE20L - 2 - Expt4Document10 pagesECE20L - 2 - Expt4Niko de LemosNo ratings yet

- How To Generate Auxiliary Supplies From A Positive Buck DC-DC ConverterDocument15 pagesHow To Generate Auxiliary Supplies From A Positive Buck DC-DC ConverterAlex KarimNo ratings yet

- Machine Lab Non ElectricalDocument16 pagesMachine Lab Non ElectricalAbhishek MishraNo ratings yet

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- Lesson 4 Thyristors and TriacsDocument39 pagesLesson 4 Thyristors and TriacsChacko Mathew100% (1)

- Fuzzy based MC-DPFC for Power Quality EnhancementDocument12 pagesFuzzy based MC-DPFC for Power Quality EnhancementVijay KrishnaNo ratings yet

- A Novel Power Quality Improvement Technique Using Multi-Connected Distributed Power Flow Controller (MC-DPFC)Document11 pagesA Novel Power Quality Improvement Technique Using Multi-Connected Distributed Power Flow Controller (MC-DPFC)Vijay KrishnaNo ratings yet

- VitaminsDocument29 pagesVitaminsVijay KrishnaNo ratings yet

- Improving Power Quality Using DPFCDocument5 pagesImproving Power Quality Using DPFCVijay KrishnaNo ratings yet

- Lesson 3 Power Bipolar Junction Transistor (BJT)Document45 pagesLesson 3 Power Bipolar Junction Transistor (BJT)Chacko MathewNo ratings yet

- Lesson 2 Constructional Features, Operating Principle, Characteristics and Specification of Power Semiconductor DiodeDocument31 pagesLesson 2 Constructional Features, Operating Principle, Characteristics and Specification of Power Semiconductor DiodeChacko MathewNo ratings yet

- Power Quality Enhancement and Mitigation of Voltage Sag Using DPFCDocument7 pagesPower Quality Enhancement and Mitigation of Voltage Sag Using DPFCVijay KrishnaNo ratings yet

- Improvement of Power Quality by Using DPFCDocument4 pagesImprovement of Power Quality by Using DPFCVijay KrishnaNo ratings yet

- PSSEDocument6 pagesPSSESyed Faizan AliNo ratings yet

- Lesson 5 Gate Turn Off Thyristor (GTO)Document23 pagesLesson 5 Gate Turn Off Thyristor (GTO)Chacko Mathew100% (1)

- Power Semiconductor Device NptelDocument14 pagesPower Semiconductor Device NptelMohammad Aminul IslamNo ratings yet

- Modeling of The Generalized Unified Power Flow Controller Gupfc in A Nonlinear Interior Point OpfDocument4 pagesModeling of The Generalized Unified Power Flow Controller Gupfc in A Nonlinear Interior Point OpfVijay KrishnaNo ratings yet

- Digital Simulation of The Generalized Unified Power Flow Controller System With 60-Pulse GTO-Based Voltage Source ConverterDocument9 pagesDigital Simulation of The Generalized Unified Power Flow Controller System With 60-Pulse GTO-Based Voltage Source ConverterVijay KrishnaNo ratings yet

- Digital Simulation of The Generalized Unified Power Flow Controller System With 60-Pulse GTO-Based Voltage Source ConverterDocument9 pagesDigital Simulation of The Generalized Unified Power Flow Controller System With 60-Pulse GTO-Based Voltage Source ConverterVijay KrishnaNo ratings yet

- Electrical Power and Energy Systems: D.B. Valle, P.B. AraujoDocument8 pagesElectrical Power and Energy Systems: D.B. Valle, P.B. AraujoVijay KrishnaNo ratings yet

- Load Flow Analysis of IEEE-3 Bus System by Using Mipower SoftwareDocument8 pagesLoad Flow Analysis of IEEE-3 Bus System by Using Mipower SoftwareVijay KrishnaNo ratings yet

- Fzzy Hyst Control and Parameter OptimizationDocument18 pagesFzzy Hyst Control and Parameter OptimizationVijay KrishnaNo ratings yet

- V3i6 Ijertv3is060677 PDFDocument4 pagesV3i6 Ijertv3is060677 PDFVijay KrishnaNo ratings yet

- IJECCE 1739 Final PDFDocument6 pagesIJECCE 1739 Final PDFVijay KrishnaNo ratings yet

- Implementation of Unified Power Flow Controller (UPFC) For Power Quality Improvement in IEEE 14-Bus SystemDocument8 pagesImplementation of Unified Power Flow Controller (UPFC) For Power Quality Improvement in IEEE 14-Bus SystemVijay KrishnaNo ratings yet

- Ijireeice 42Document7 pagesIjireeice 42Vijay KrishnaNo ratings yet

- IJSRD - International Jdpfcournal For Scientific Research & Development - VolDocument6 pagesIJSRD - International Jdpfcournal For Scientific Research & Development - VolVijay KrishnaNo ratings yet

- Ice Cts P 052014Document7 pagesIce Cts P 052014Vijay KrishnaNo ratings yet

- Ijest10 02 06 78Document6 pagesIjest10 02 06 78Phani SantoshNo ratings yet

- A Wavelet-Based Algorithm For Disturbances Detection Using Oscillographic DataDocument6 pagesA Wavelet-Based Algorithm For Disturbances Detection Using Oscillographic DataVijay KrishnaNo ratings yet

- IEEE Bus SystemDocument54 pagesIEEE Bus Systemsamtt_29No ratings yet

- 11 PDFDocument7 pages11 PDFVijay KrishnaNo ratings yet

- PE - 2010!25!10 - A FACTS Device Distributed Power Flow ControllerDocument9 pagesPE - 2010!25!10 - A FACTS Device Distributed Power Flow ControllerSudeepth GaddamNo ratings yet

- 10Document11 pages10Vijay KrishnaNo ratings yet

- Compact Microstrip Feeding Network For Mobile Base Station AntennaDocument5 pagesCompact Microstrip Feeding Network For Mobile Base Station AntennaInnovative Research PublicationsNo ratings yet

- PMIC System HW-Validation EngineerDocument3 pagesPMIC System HW-Validation EngineerSai KrishnaNo ratings yet

- CapacitorsDocument10 pagesCapacitorsrsrtnj100% (1)

- PSC WP Energising Ireland A Guide To Grid Code Compliance K.YumakDocument14 pagesPSC WP Energising Ireland A Guide To Grid Code Compliance K.Yumakp61466365No ratings yet

- HCB User ManualDocument3 pagesHCB User ManualJesús David Diaz MontesNo ratings yet

- 12 Pulse ConverterDocument5 pages12 Pulse ConvertersumitchintuNo ratings yet

- At-CP1E CPU Unit SoftwareDocument450 pagesAt-CP1E CPU Unit SoftwareNikolas Kolasni Lakenir Ckerde DockosNo ratings yet

- Module 6 - Current Divider RuleDocument10 pagesModule 6 - Current Divider RuleNoel Jr. CornelioNo ratings yet

- Basics of Minilink Microwave Networks GoodDocument19 pagesBasics of Minilink Microwave Networks GoodFarzand Ali100% (3)

- 2VAA000720R0001 A en S Control Harmony Bridge Controller With Ethernet (BRC-410) User ManualDocument95 pages2VAA000720R0001 A en S Control Harmony Bridge Controller With Ethernet (BRC-410) User ManualanbarasanNo ratings yet

- Scorpion Z4120C Z6020C Z8020C Installer ManualDocument23 pagesScorpion Z4120C Z6020C Z8020C Installer ManualNazriNo ratings yet

- Modelos Maquina Sicor ItalianaDocument104 pagesModelos Maquina Sicor ItalianaAscensores MbsasNo ratings yet

- Transformer Class 12 ProjectDocument21 pagesTransformer Class 12 ProjectAbhishek Sen50% (2)

- Tiger TO-92 Plastic Transistor SpecsDocument3 pagesTiger TO-92 Plastic Transistor SpecsVinod kumarNo ratings yet

- Balanced Cable Measurement Using The 4-Port ENADocument9 pagesBalanced Cable Measurement Using The 4-Port ENAA. VillaNo ratings yet

- Arteche Mu HV Ug User+Manual enDocument17 pagesArteche Mu HV Ug User+Manual enPrime useNo ratings yet

- E-Wallet: Paper Presentation OnDocument7 pagesE-Wallet: Paper Presentation OnSiddhartha Choudary100% (1)

- Quidway S3900 Series Ethernet Switches Installation ManualDocument102 pagesQuidway S3900 Series Ethernet Switches Installation Manualcharliil100% (1)

- Uygulama 211130 160308Document5 pagesUygulama 211130 160308Joao Nogueira ClementeNo ratings yet

- UTCPanel+ Guide EDocument65 pagesUTCPanel+ Guide Ejroyal692974100% (1)

- Numerical Busbar Protection: Technical Data SheetDocument24 pagesNumerical Busbar Protection: Technical Data SheetamitdhamijaNo ratings yet

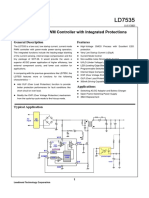

- Green-Mode PWM Controller With Integrated Protections: General Description FeaturesDocument18 pagesGreen-Mode PWM Controller With Integrated Protections: General Description FeaturesRUSLANNo ratings yet

- AMB4520R1 (G+Usplit)Document2 pagesAMB4520R1 (G+Usplit)Thaw GyiNo ratings yet

- GUI Based Control System Analysis Using PID Controller For EducationDocument11 pagesGUI Based Control System Analysis Using PID Controller For Educationpascal toguNo ratings yet

- DSP Processor and ArchitectureDocument45 pagesDSP Processor and ArchitectureAlemayehu AsmareNo ratings yet

- Parker Valve Industrial Electrohydraulic ElectronicsDocument54 pagesParker Valve Industrial Electrohydraulic Electronicssureshlls100% (1)

- Multi Channel AV Receiver: Operating InstructionsDocument155 pagesMulti Channel AV Receiver: Operating InstructionsMichael ErnstNo ratings yet

- TD Docomo IntegrationDocument3 pagesTD Docomo IntegrationVishal SuryawaniNo ratings yet

- 3SU11000AB401FA0 Datasheet enDocument4 pages3SU11000AB401FA0 Datasheet enpatrykk11195No ratings yet

- Impedance Measurement Instruments: 26.1. Introduction To Impedance MeasurementsDocument26 pagesImpedance Measurement Instruments: 26.1. Introduction To Impedance MeasurementsHeiner Farid Castillo AvellaNo ratings yet