Professional Documents

Culture Documents

Sigdel PDF

Uploaded by

raju.kprr8862Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sigdel PDF

Uploaded by

raju.kprr8862Copyright:

Available Formats

Sigma-Delta modulator

ECE262 Project Report Spring 2010

Bhawana Singh Fangming Ye Luyao Li

ECE 262 Integrated Analog Circuit Design Final Report

Contents

Introduction .................................................................................................................................................. 3 1.1 1.2 1.3 Project Function ............................................................................................................................ 3 System Verification Simulation ..................................................................................................... 4 Performance Estimation ............................................................................................................... 5

Sub-circuit Design ......................................................................................................................................... 6 2.1 2.2 2.3 2.4 Summer ......................................................................................................................................... 6 Integrator ...................................................................................................................................... 8 Comparator ................................................................................................................................. 11 D Flip-flop .................................................................................................................................... 12

Complete System ........................................................................................................................................ 14 3.1 3.2 3.3 Whole system simulation............................................................................................................ 14 Whole system output analysis .................................................................................................... 19 System schematic and Layout ..................................................................................................... 20

Conclusion ................................................................................................................................................... 21 Reference .................................................................................................................................................... 22 Appendix ..................................................................................................................................................... 22

ECE 262 Integrated Analog Circuit Design Final Report

Introduction

1.1 Project Function

In this project, we built a Sigma Delta modulator. The most striking feature of a sigma delta modulator, which is the main component of sigma delta ADCs, is that these modulators use a very high sampling rate. The sampling rate used is in the range of MHz, which is much higher than the Nyquist rate, generally in the range of kHz. Hence, the oversampling ratio is very high, because of which these are sometimes referred to as oversampling ADCs. The advantage of using this very high sampling ratio is high resolution of the digital output and better noise shaping. The main components of a sigma delta modulator are: a summer, an integrator, a comparator, a D flip-flop and a DAC. The difference of the analog input and the output of the modulator, fed back to the input through a DAC, is fed to the integrator. The integrator ramps up or down depending upon whether the difference being fed is positive or negative. The output of the integrator goes into a comparator. The comparator produces 5V or 0V depending on whether the output of the integrator is above or below the threshold voltage being compared by the comparator. The comparators output is fed to a D Flip-flop which operates at a very high frequency (~MHz), which in turn connects to a DAC. The output of this DAC is fed to the summer at the input stage. For our project, we omitted the DAC, and instead used a resistordivider circuit after the D Flip-flop to make sure that the input being fed back into the summer is within the appropriate range. Thus, the main components for our project were: Summer Integrator Comparator D Flip-flop

To arrange four components in the floor-plan, we make each component as below. Besides, Since integrator includes a large capacitance and a large resistance. We make them off-chip.

ECE 262 Integrated Analog Circuit Design Final Report

Figure 1 Sigma delta modulator floorplan

1.2

System Verification Simulation

In the mean time, we make block diagram of this sigma-delta modulator in Matlab/Simulink. And simulate the sigma-delta modulator using digital simplified method to verify the functionality of the device. Block diagram of sigma-delta is shown below,

Figure 2 Sigma Delta modulator Matlab/Simulink model In each stage, we can get different output. First we add up the original signal and negative adjusted pulse output of dff. After we integrate the difference of this stage, and quantize the result. We get result of 0 and 1 output signal representing a sinusoidal waveform. We get more 0/1 oscillation in the center of input range; and we could get more 1 when input is high, otherwise more 0 when input is low.

ECE 262 Integrated Analog Circuit Design Final Report

Fig 3 each stage output of Sigma delta modulator

1.3

Performance Estimation

Total number of transistors used: 39. Total power consumption: 12.2573 mW Total area of the circuit: 864 um* 340 um = 0.29mm2 besides we need a 1uf off-chip capacitance and a 20 Meg off-chip resistance Sampling frequency: 2.5 MHz Input Signal frequency: 2kHz These components are discussed in detail in the following chapter.

ECE 262 Integrated Analog Circuit Design Final Report

Sub-circuit Design

The whole system consists of a summer, an integrator, a comparator and a d flip-flop. Below, we will discuss each component by its function, simulation verification, schematic and its layout.

2.1

Summer

The summer was simulated using HSpice, and was found to function correctly. Its output range was 1.5V to 5V. Below 1.5V, distortion occurs and above 5V, clipping occurs. The simulation results for the summer are shown below. The first simulation was done using a DC voltage as the 1st input to the summer and pulse as the 2nd input. The value of the DC voltage was 1V and the pulse low and high values were 0V and 1V respectively. The output of the summer in this case was a pulse varying from 1.5V to 2.5V. This is shown in figure 1. The second test on the summer was done using a DC voltage of 1V as 1st input, and a sine wave with amplitude of 1V and centered at 2.5V as the 2nd input. The result, in this case, was a sine wave centered at 3.5V, and having amplitude of 1V. This is shown in figure 2. The schematic and layout for the summer are shown in Figures 3 and 4 respectively.

Figure 4: Output of Summer for a DC voltage of 1.5V and a pulse varying from 0V to 1V

ECE 262 Integrated Analog Circuit Design Final Report

Figure 4: Output of Summer for a DC voltage of 1V and a sine wave of 1V centered at 2.5V

Figure 5: Schematic for Summer

ECE 262 Integrated Analog Circuit Design Final Report

Figure 6: Layout of Summer

2.2

Integrator

The integrator used a high capacitance of 1u to make its working robust. It was tested using both, a DC input voltage, in which case the output was a ramp, and a pulse input, in which case the output was ramping up or down depending upon whether the input was higher or lower than 2.5V. The integrator was centered at 2.5V. Since the capacitance used was very large, therefore, in the layout, this capacitor was kept as an off-chip component. The simulation results are shown in Figures 5 and 6 below.

ECE 262 Integrated Analog Circuit Design Final Report

Figure 7: Output of Integrator for a constant DC input of 3V

Figure 8: Output of Integrator for a pulse input

ECE 262 Integrated Analog Circuit Design Final Report

Figure 9: Schematic for Integrator (off chip capacitance of 1uF connected between IntRC & OUT)

Figure 10: Layout of Integrator

ECE 262 Integrated Analog Circuit Design Final Report

2.3

Comparator

The comparator was also centered at 2.5V. Thus for input voltage higher than 2.5V, the output was 5V, and for input voltage lower than 2.5V, the output was 0V. The simulation results are shown in Figure 9.

Figure 11: Output of Comparator (threshold voltage is 2.5V)

Figure 12: Comparator Schematic (PIN_Comp is connected to 2.5V which is the threshold and the input signal being compared is connected to NIN)

ECE 262 Integrated Analog Circuit Design Final Report

Figure 13: Comparator Layout

2.4

D Flip-flop

This is the only digital component in our system. It was simulated using HSpice and was found to function correctly. The simulation results are shown in Figure 12. Following the simulation results, the schematic and layout for the D Flip-flop are shown. Both the D Flipflop and the whole of the analog section of the circuit were surrounded by guard rings to ensure that these parts are isolated from each other. The Qbar output of the D Flipflop was made to pass through a

ECE 262 Integrated Analog Circuit Design Final Report

resistor-divider circuit and then fed back as the 2nd input of the summer.

Figure 14: Simulation result for D Flipflop

Figure 15: Schematic of D Flipflop

ECE 262 Integrated Analog Circuit Design Final Report

Figure 16: Layout of D Flipflop along with the resistor divider circuit (In the final layout for the complete system, the resistor-divider circuit is combined with the analog components and is isolated from the D Flipflop by means of guard rings)

Complete System

3.1 Whole system simulation

Till then, all the components were combined together, and the digital and analog parts of the circuit were separated from each other by using guard rings. The complete system simulation gave the desired result. System was initially tested for DC input voltages, and the final test was conducted using a sine wave. The simulation results for sine wave are shown below. The complete sine wave is shown first, followed by zoomed in sections of this same sine wave. The last simulation waveform shows the output of each stage in the complete system simulation, starting with the inputs and output of summer, followed by integrator output, comparator output and D Flip-flop output, which is the same as the system output.

ECE 262 Integrated Analog Circuit Design Final Report

Figure 17: Output of the system for an analog sine wave input There are more 1s near the top of the sine wave, and more 0s near the bottom of the sine wave. The first half of the sine wave above threshold has been zoomed in and shown in Figure 14.

Figure 19: Portion of the sine wave above threshold

ECE 262 Integrated Analog Circuit Design Final Report

Figure 20: Portion of the sine wave below threshold

Figure 21: Increasing portion of sine wave above threshold. Since this is above threshold, therefore there are more 1s than 0s

ECE 262 Integrated Analog Circuit Design Final Report

Figure 22: Increasing portion of sine wave below threshold. Since this is above threshold, therefore there are more 0s than 1s

ECE 262 Integrated Analog Circuit Design Final Report

Figure 23: PIN1-Analog input to Summer, PIN2-output of modulator that is fed back to Summer through a resistor-divider circuit, OUTSUMMER- output of Summer, OUT1- output of integrator, OUTCOMP- output of Comparator, Q- output of D-Flipflop which is also the system output

ECE 262 Integrated Analog Circuit Design Final Report

3.2

Whole system output analysis

Since the output of sigma-delta modulator is either 0 or 1, which are used to represent an analog signal. Thus, it is not easy to identify whether or not the system can convert signal into digital format correctly. So, we use some method to return pwm signal back to analog signal. I used signal output generated from system hspice net list simulation and input the signal in Matlab through hspice toolbox. Writing m-file adding several voltages and get average value, I can draw a plot based on those average values. Bottom left one is the signal input into sigma delta modulates, the bottom right one is the transformed output based on 0 and 1. Basically, we can see output signal follows input signal, but there is some clipping and the waveform is not smooth at all. Quantitative analysis: Total point from output have 180,000 points, I pick average point every 500 points. Thus I have 360 points at all, making the graph below. Accordingly, our sigma delta modulator is around 8 bits (28=256).

Fig 25 System input signal

Fig 26 System output transformed signal

ECE 262 Integrated Analog Circuit Design Final Report

3.3

System schematic and Layout

Figure 27: Schematic of complete system (Integrating capacitor is off-chip and is to be connected between IntRC and Output of integrator)

Figure 28: Layout of complete System

ECE 262 Integrated Analog Circuit Design Final Report

The complete system was DRC and LVS clean. Shown below is a screenshot which shows that the system is LVS clean.

Figure 29: System is LVS clean

Conclusion

From the simulation and numerical analysis, we conclude that this sigma delta A/D converter can work in a proper condition and implement basic function as a converter. This device also inherits the merits of sigma delta A/D converter: high resolution but large area and low response time. In design of this converter, our input range is from 1.5 3v while normal sigma delta ad converter has a positive-negative large input range and center their working voltage range at 0v, which leads to little or no off-set, while in our design center of working range is positive 3v, which leads to a certain off-set as well as some clipping during sampling. The quantitative analysis is based on hspice simulation rather than layout extract netlist, since we have two off-chip components, a large capacitance and resistance. If we take them into account and wire capacitance and those parasite effects, it will be more difficult to expect the real output of our sigma delta converter. Besides, we did well in layout that we separate digital part (dff) and the rest analog part by surrounding and isolating, i.e. providing guard ring between them. Some parts of our circuit are common-centroided, thus effectively avoiding process variation locally.

ECE 262 Integrated Analog Circuit Design Final Report

Reference

[1] B. Razavi , Design of analog CMOS integrated circuits: Boston : McGraw-Hill, c2001. [2] Hein, Sren, Sigma Delta modulator: nonlinear decoding algorithms and stability analysis: Boston : Kluwer Academic Publishers, c1993.

Appendix

1. M- file summing output

h=500; i=180000/h; ret=[0]; timeret=[0]; for j=1:i temp = 0; for n=1:h m=(j-1)*h+n; now = q(m,1); temp = now+temp; end ret= [ret;temp/h*1.5/5+1.5]; timeret= [timeret;j]; end

You might also like

- S V University Exams Branch Enhancement of Rates For Various Examinations Fee With Effect From 01-07-2017 Communicated RegDocument12 pagesS V University Exams Branch Enhancement of Rates For Various Examinations Fee With Effect From 01-07-2017 Communicated Regraju.kprr8862No ratings yet

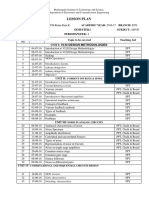

- Lesson Plan ADVD 2016-17Document5 pagesLesson Plan ADVD 2016-17raju.kprr8862No ratings yet

- Kang 1Document58 pagesKang 1123vidyaNo ratings yet

- 9A02406 Network TheoryDocument8 pages9A02406 Network TheorysivabharathamurthyNo ratings yet

- CyberDocument2 pagesCyberraju.kprr8862No ratings yet

- 02 WholeDocument160 pages02 Wholeraju.kprr8862No ratings yet

- Ch4 ISI and EqualizationDocument24 pagesCh4 ISI and Equalizationsuper_lativoNo ratings yet

- 9D06106c Low Power VLSI DesignDocument1 page9D06106c Low Power VLSI Designraju.kprr8862No ratings yet

- PHD Physics EntranceDocument18 pagesPHD Physics Entrancekvanps_kumarNo ratings yet

- 9D38104 Digital Communication TechniquesDocument1 page9D38104 Digital Communication Techniquesraju.kprr8862No ratings yet

- 4lab Moddemod PDFDocument9 pages4lab Moddemod PDFKhoirul Anam Al ImanNo ratings yet

- 9A04601 Digital CommunicationsDocument4 pages9A04601 Digital Communicationsraju.kprr8862No ratings yet

- M. Tech I Semester Exam QuestionsDocument1 pageM. Tech I Semester Exam Questionsraju.kprr8862No ratings yet

- Analog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 3Document4 pagesAnalog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 3raju.kprr8862No ratings yet

- 9A02406 Network TheoryDocument8 pages9A02406 Network TheorysivabharathamurthyNo ratings yet

- Midterm1 PDFDocument8 pagesMidterm1 PDFraju.kprr8862No ratings yet

- 4lab Moddemod PDFDocument9 pages4lab Moddemod PDFKhoirul Anam Al ImanNo ratings yet

- Analog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 1Document4 pagesAnalog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 1raju.kprr8862No ratings yet

- Sigma-Delta Modulator Design for 10MHz BandwidthDocument1 pageSigma-Delta Modulator Design for 10MHz Bandwidthraju.kprr8862No ratings yet

- ECE Test Series ScheduleDocument3 pagesECE Test Series Scheduleraju.kprr8862No ratings yet

- 5 Linear Block CodesDocument29 pages5 Linear Block CodesSuprit PaulNo ratings yet

- Analog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013)Document4 pagesAnalog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013)raju.kprr8862No ratings yet

- AnalogDocument38 pagesAnalogecessecNo ratings yet

- Comparator SDocument57 pagesComparator Sraju.kprr8862No ratings yet

- 9309 - CMOS Analog Design Chapter 8Document54 pages9309 - CMOS Analog Design Chapter 8raju.kprr8862No ratings yet

- Switched-Capacitor FundamentalsDocument20 pagesSwitched-Capacitor Fundamentalscleopatra2121No ratings yet

- CMOS Analog Design Using All-Region MOSFET Modeling Fundamentals of Sampled-Data CircuitsDocument23 pagesCMOS Analog Design Using All-Region MOSFET Modeling Fundamentals of Sampled-Data Circuitsraju.kprr8862No ratings yet

- Control Systems2Document4 pagesControl Systems2Peruru MuraliNo ratings yet

- B.Tech Digital Communications RR310406 Exam QuestionsDocument1 pageB.Tech Digital Communications RR310406 Exam Questionsraju.kprr8862No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Se License Manager GuideDocument93 pagesSe License Manager GuideRoberto Gutierrez SaezNo ratings yet

- Oracle ADF Study Guide - StudentDocument1,251 pagesOracle ADF Study Guide - StudentDeepak BhagatNo ratings yet

- Photometer AdjustmentsDocument3 pagesPhotometer AdjustmentsTrần Thanh ViệnNo ratings yet

- MillMinder Audio Signal MonitorDocument15 pagesMillMinder Audio Signal Monitorescorpion311No ratings yet

- FlasherDocument6 pagesFlasheriwanbossemeNo ratings yet

- SMA34 More Power To SMA20 Decoders With Tips and Additions - Model Railroad Hobbyist MagazineDocument8 pagesSMA34 More Power To SMA20 Decoders With Tips and Additions - Model Railroad Hobbyist MagazinepapirojedecNo ratings yet

- Control System Design For Motor Based On Temperature DynamicsDocument11 pagesControl System Design For Motor Based On Temperature DynamicsInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Project MediTrackDocument21 pagesProject MediTrackneeleshchopra3459No ratings yet

- Modul PBM 5 (Assembly)Document18 pagesModul PBM 5 (Assembly)Fajar FatahillahNo ratings yet

- Automatic Water Level ControllerDocument40 pagesAutomatic Water Level Controllerritesh chauhanNo ratings yet

- Ict Project FinalDocument8 pagesIct Project FinalJham Ellen DaylusanNo ratings yet

- 5g, Oran & Lte Premium SyllabusDocument12 pages5g, Oran & Lte Premium SyllabusVishwaNo ratings yet

- 03 VESDA HLI Sliding Windows TDS A4 IE LoresDocument2 pages03 VESDA HLI Sliding Windows TDS A4 IE LoresEduardo ParrudoNo ratings yet

- Obd 1 Ecus Component List: Chipping Components All EcusDocument1 pageObd 1 Ecus Component List: Chipping Components All EcusGaragem do FerreiraNo ratings yet

- Easy Ups On-Line - Srv10krirkDocument3 pagesEasy Ups On-Line - Srv10krirkGrandy VpNo ratings yet

- Arduino Programming (The Beginning)Document33 pagesArduino Programming (The Beginning)Dennis Feliciano VirayNo ratings yet

- Three Tier Client-ServerDocument5 pagesThree Tier Client-ServerIsaiah NgareNo ratings yet

- Epson Service Manual TM-U220 Impact Printer Service Manual RevBDocument104 pagesEpson Service Manual TM-U220 Impact Printer Service Manual RevBeburksNo ratings yet

- Introducing Snowflake: Data Warehousing For EveryoneDocument15 pagesIntroducing Snowflake: Data Warehousing For EveryoneMorozov AlexanderNo ratings yet

- 41-NC Maint PDFDocument510 pages41-NC Maint PDFakirenaviNo ratings yet

- Project Book of AtmDocument35 pagesProject Book of Atmpavan puppalaNo ratings yet

- Software Testing Fundamentals GuideDocument3 pagesSoftware Testing Fundamentals GuideJohn SmithNo ratings yet

- Smart Host Microcontroller For Optimal Battery PDFDocument3 pagesSmart Host Microcontroller For Optimal Battery PDFsrcembeddedNo ratings yet

- Kafkacomet OverviewDocument5 pagesKafkacomet OverviewVinicius AlexandreNo ratings yet

- PPTDocument9 pagesPPTsindhuvindhya100% (1)

- 17fin6542 Atm Fraud Inspection Guide NCR RGBDocument11 pages17fin6542 Atm Fraud Inspection Guide NCR RGBBoby JosephNo ratings yet

- Intelligent Network Principle: ZTE UniversityDocument32 pagesIntelligent Network Principle: ZTE UniversityyosephwansaraNo ratings yet

- Benchmarking Cryptography and Stenography: Introduction To CrypotgraphyDocument21 pagesBenchmarking Cryptography and Stenography: Introduction To CrypotgraphyprofessionalwritersNo ratings yet

- Module 7 CSS G11 2nd Sem Week 3 4 PDFDocument59 pagesModule 7 CSS G11 2nd Sem Week 3 4 PDFKenkenNo ratings yet

- 11 and .NET 7 Part12Document50 pages11 and .NET 7 Part12sladjanNo ratings yet