Professional Documents

Culture Documents

Design of A Low Power 5Ghz Cmos Radio Frequency - Low Noise Amplifier

Uploaded by

Vignesh BarathiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design of A Low Power 5Ghz Cmos Radio Frequency - Low Noise Amplifier

Uploaded by

Vignesh BarathiCopyright:

Available Formats

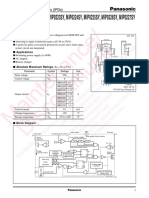

Design of a Low Power 5GHz CMOS Radio Frequency Low Noise Amplifier

Rakshith Venkatesh

Abstract

A 5GHz low power consumption LNA has been designed

here for the receiver front end using 90nm CMOS

technology. The current reuse technique has been used

here to reuse the bias current for two amplifier stages

stacked upon each other. An inverter type amplifier acts

the second stage to a common source first stage thereby

giving a good gain for the amplifier. The gain achieved is

around 13dB with a power consumption of 4.8mW.

Key Words: Low Power, RF CMOS, LNA, 90nm,

5GHz.

1. Introduction

Power consumption is a very important criterion in

wireless communication systems. At the same time we

need to have a cost effective solution for the problem of

constructing RF circuits using non SiGe technologies. We

need a substitute that can provide the benefits of the SiGe

technology like low power and high gain. This is one of

the reasons why the use of the CMOS technology is

increasing in the design of the Low Noise Amplifiers of

the RF Front end. There are certain CMOS designs that

consume several tens of milli watts, this approach reduces

the power consumption to just a few milli watts.

In this work, a current reuse technique is employed to

increase the transconductance of the LNA without

increasing the power consumption compared to the

standard cascode technology. The design comprises of a

common source amplifier followed by an inverter type

amplifier in a stacked up arrangement as shown in the

circuit diagram in Figure 1. The PMOS-NMOS inverter

type amplifier gives a major part of the gain we are

looking for.

The traditional approach towards design of CMOS

LNAs involves the use of multiple cascade stages to

achieve the gain which results in higher power

consumption because a single cascade stage consumes

four to five times more current than the low power LNA

design under comparison. Hence we get more power

dissipation. Typical power dissipations for the cascade

design for a gain of 13 14dB range from 8mW to 20mW

[1-5]. The goal of this work is to achieve at least a fifty

percent reduction in that.

2. Design of the Low Power LNA

The circuit diagram of the LNA can be found in Figure

1. The RF input is fed into the common source input stage

whose input impedance is matched to the source

impedance. The charactereistic impedance of the circuit is

50 Ohm and hence the source impedance is chosen to be

the same. It has to be noted that the impedance matching

circuits has not been shown completely just to keep things

simple before begginning.

Figure 1, The LNA Circuit without matching at input

and output

The amplified output of the transistor M1 is fed into

the gates of the inverter type amplifier pair comprising

M2 and M3 using the coupling capacitor C4. As it can be

seen from Figure 1, the two stages have been stacked up

between Vdd and ground. Which means we need an

isolation between M1 and M3 and that is provided by L1

and C3. The inductor-capacitor pair resonates and causes

a high impedance path between the nodes they are

connected thereby giving the required isolation. Capacitor

C5 acts as a bypass for the second stage. The RF output is

taken from the common drain terminals of M2 and M3

transistors.

It can be seen that all the 3 transistors use the same

bias current. When compared to the traditional design

where multiple stages of cascode amplifiers are used

with each stage having a bias current, this design should

consume at least fifty percent less power.

The first step towards the design of the amplifier is to

find the optimum transistor widths. The transistor widths

decide the amount of bias current that will be used and

hence the power consumption. For this design the width is

chosen to be 20 because this width gives a good drain

current density of 0.13mA per micro meter width, which

is needed for an NFmin of less than 3dB and a power

dissipation limit of 4mW for a supply of 1.2V.

Then we need to look into the input matching, which

involves both noise matching and impedance matching.

Since it is very hard to achieve both at the same time, a

trade off is done between the two. We need to choose the

value of Cgs of M1 for noise matching such that,

s =

2uopt

2n]

(1)

Here Gopt is the optimum admittance of the source for a

lower Noise Figure, here it is 1/50 or 0.02. For 5GHz we

get the value of Cgs to be 1.2pF. Since the transistor

gate-source capacitance found through spice analysis is

only 30fF we choose to add a parallel capacitance C6 of

1.2pF across the gate and the source.

Impedance matching at the input and the output are the

next two things that need to be considered. For matching

at the input we need to make sure that your impedance is

50. A technique called inductive degeneration is used

for the same, where the capacitances are cancelled out by

the inductors and we are left with only 50Ohms as the

input impedance. Considering the coupling capacitor C1

as well, we get an expression for the input impedance as,

Zn = s(I + I) +

1

s(C1)

+

1

s(Cgs1)

+ .

L2

Cgs1

(1)

The coupling capacitor C1 is chosen as 1pF, L2 is chosen

such that the last term gives us exactly 50Ohms and also

to cancel out the capacitance Cgs. L3 does the job of

cancelling out the impedance of C1. L2 needs to be small

enough to be implemented as a spiral inductor and hence

it is chosen at around 1nH or less. Gm1 is the

transconductance of transistor M1. A similar calculation

is done for the output impedance and it is found to be

given by the expression,

Zo =

1

s(Cds2)

+

1

s(Cds3)

+

1

cC2

+.

L1

Cds3

(2)

Cds2 and Cds3 are the drain to source capacitance of M2

and M3 and Gm3 is the transconductance of M3, found

through spice simulation. L1 is used for the isolation that

we talked about between the two amplifier stages.

After calculating the input and output matching

circuits using the above expressions we get a circuit

shown in Figure 2. L1 and C3 are chosen to resonate at

5GHz and C5 acts as a bypass capacitor for the source of

M3. C3 and the coupling capacitor C4 are chosen to be

1pF to aid in the calculations. Since we cannot use

inductive degeneration for the output of the second stage,

a matching circuitry comprising of C8 and L4 will give

the necessary matching of 50Ohms at the output side.

Figure 2, same circuit as in Figure 1 but with input and

output matching circuits and input biasing.

The biasing circuitry also needs to be added as we

need to bias the two stages at exactly the center of the

slope on the transfer characteristics of that stage. M5 and

M4 are small transistors which are of widths 0.09um and

0.036um respectively chosen such that a bias of 0.5 volts

is applied to the gate of the transistor M1. These

transistors consume very little power compared to the

main amplification stages. A similar job is done for the

second stage with M7 and M6 for a bias point of 0.35

volts. These voltages are determined by sweeping the

input of the transistor stages and evaluating the transfer

characteristics using spice.

The circuit is simulated using spice tools like HSPICE

and the circuit S parameters, Noise Figure, NFmin

and power are measured by analyzing the plots. The

circuit should essentially consume lower power but one of

the demerits of this design comes because of the fact that

the bandwidth is smaller compared to the cascode

approach as we use a resonating circuit between the two

stages which limits a huge chunk of frequencies. So it

results in a good design but more of a tuned circuit and

more suitable for RF applications that use such tuned

circuits. The circuit parameter values and the results are

analyzed in the next section. The gain that it is calculated

using small signal models of the stages is around 12dB

with a power consumption of 4mW.

3. Analysis of the results

The parameters of the circuit are analyzed with respect

to the frequency of operation and their behavior outside

and around the 5GHz frequency. Since the circuit

comprises of a lot of reactive elements, we get abrupt

changes around the operating frequency and this is what

is expected.

A plot of the S parameters is shown from Figure 3 to

Figure 5. The S21 plot is of importance as it gives the

gain of the amplifier. As it can be seen from Figure 3, a

gain of 13dB is obtained at 5GHz which falls right in our

desired range.

Figure 3, a plot of the power gain of the circuit versus

frequency

Figure 4 shows a plot of the input and output reflection

coefficients S11 and S22. The values are -10.3 dB and -

14.5dB respectively for the input and output sides. The

negative value of S11 indicates that a good matching has

been provided at both the input and the output.

Figure 4, a plot of input and output reflection

coefficients S11 and S22.

Figure 5 gives the plot of the reverse isolation or S12 that

is provided by the circuit. The value of the isolation that

was got is -45.86dB which is very good figure. This is

attributed to the resonating circuit that is inserted between

the two stages.

Figure 5, Reverse Isolation S12

Figure 6, Noise Figure and NFmin plot

The plots of Noise Figure and NFmin are shown in the

Figure 6 here. A NF of 5.6dB is obtained with the NFmin

being 3.5dB. Input noise matching is the most probable

reason for the NF to have exceeded our expectations. The

expression for NF is given by [6],

= n +

Rn{(us-uopt)

2

-(Bs-Bopt)

2

]

us

(3)

Here, NFmin directly depends on the amount of current

biasing we provide for the circuit. Since we had a limit of

the amount of current that can be used for biasing because

of the power constraints the current could was chosen to

give us a small NFmin. The NF also depends on the noise

matching at the input port which again is given by the

second term in the above expression for NF. Gs + jBs is

the source admittance presented to the transistor M1 and

Gopt + jBopt is the optimum source admittance [6] and

both need to be equal to get a good noise match. This

calls for a tradeoff between impedance matching and

noise matching as they never result in the same values for

the matching circuits and hence both are not possible at

the same time. Even though Cgs was enhanced for noise

matching as explained in the design, the addition of C1 as

an input coupler has resulted in a noise mismatch and

hence a value of NF that is high compared to the results in

[1-5].

The power is the main consideration here and power

measurements yielded 4.8mW power consumption. It is

calculated by multiplying the supply voltage with the bias

current which was found through simulation to be around

3.2mA. This is comparable to other low power designs

and also when compared to the conventional cascode

designs a good power saving of more than 40 percent is

achieved [4, 5]. The supply was slightly increased to get a

better gain and NFmin and hence the power dissipation

went out of our desired range of 4mW.

The results are summarized and compared to other

related works in the area of low power LNA design and

also with some designs employing the cascode strategy.

The results are tabulated in tables 1 and 2.

parameter [1] [2] This work

Technology (nm)

250 90 90

Voltage Supply (V)

2 1.2 1.5

Frequency (GHz)

2.4 5.5 5.0

Gain (dB)

14.7 15.4 13

Noise Figure(dB)

2.5 2.7 5.6

Power (mW)

1.97 20.6 4.8

S12 (dB)

-28 -32 -45.86

S11 (dB)

-20 -14 -10.3

S22 (dB)

-22 -8.8 -14.5

Table 1, comparison of this work with other low power

LNA designs

4. Conclusions and Future work

An RF LNA is designed here using CMOS 90nm

technology for low power operation with a current reuse

technique for biasing. The bias current is shared between

the two transistor stages and a method for feeding the

signal from the first stage to second stage using parallel

resonance for isolation of the drain and source regions of

the transistors in the two different stages is employed.

This is different from the conventional cascode approach

where multiple cascode stages or a single cascode stage

with more current bias is used resulting in more power

consumption.

parameter [3] [4] This work

Technology (nm)

90 90 90

Voltage Supply (V)

1.2 1.2 1.5

Frequency (GHz)

5.5 3.1 5.9 5.0

Gain (dB)

13.3 13.5 13

Noise Figure(dB)

2.9 2.8-3.8 5.6

Power (mW)

9.72 5.4 4.8

S12 (dB)

-28 <-57 -45.86

S11 (dB)

-14.4 ~-15 -10.3

S22 (dB)

-19 NA -14.5

Table 2, comparison of this work with some cascode

designs

As a part of the future work the noise matching of the

circuit can be improved by understanding the concept of

matching the optimum noise admittance of the source to

the actual source admittance and its relation to the input

impedance of the circuit.

The power supply voltage and the voltage needed to

keep the transistors in saturation usually limit the number

transistors that can be stacked up. An analysis of optimum

number of transistor stages that can be used to receive a

good gain can be done. This would enable us to

understand the limit for a particular supply voltage. If we

can have more stages stacked for the same supply, we will

get a huge gain compared to the cascode design with

lesser power consumption.

One of the most basic things about an amplifier that

was clearly visible in this design and simulation is that

when we supply more DC power to the circuit through an

increase in the Vdd and bias current, we get more gain. So

during the design for low power of an amplifier, the entire

power supplied is not injected into the signal, some

quantity gets dissipated or lost as heat. We just need to

utilize this lost power such that a larger percentage of

supplied power is converted into gain.

References

[1] Ickjin Kwon and Hyungcheol Shin, Design of a

New Low-Power 2.4 GHz CMOS LNA, Journal

of the Korean Physical Society, Vol. 40, No. 1,

January 2002, pp. 47.

[2] D. Linten et.al, Low-power 5 GHz LNA and

VCO in 90 nm RF CMOS, VLSI Circuits 2004,

Digest of Technical Papers. 2004 Symposium,

17-19 June 2004, 372- 375.

[3] Dimitri Linten et.al, A 5-GHz Fully Integrated

ESD-Protected Low-Noise Amplifier in 90-nm

RF CMOS, IEEE journal of solid state circuits,

VOL. 40 No. 7 JULY 2005.

[4] A 90-nm CMOS Two-Stage Low-Noise

Amplifier for 3-5-GHz Ultra-Wideband Radio ,

Radio Frequency Integrated Circuits Symposium

2008, p489 492.

[5] Yao T et.al, 60-GHz PA and LNA in 90-nm RF-

CMOS, Radio Frequency Integrated Circuits

Symposium, 2006, IEEE, 4 pp.

[6] Introduction to LNA Design, queens learning

wiki.

http://bmf.ece.queensu.ca/mediawiki/index.php/I

ntroduction_to_LNA_Design

[7] http://bwrc.eecs.berkeley.edu/Research/RF/proje

cts/60GHz/matching/ImpMatch.html Impedance

Matching.

[8] RF Microelectronics by B Razavi, Prentice Hall

Communications Engineering and Emerging

Technologies Series.

[9] Radio Frequency Electronics by Jon B Hagen,

Cambridge University Press.

You might also like

- Self Oscillating Class-D Audio Amplifier Circuit DesignDocument29 pagesSelf Oscillating Class-D Audio Amplifier Circuit DesignnicchioNo ratings yet

- Simple AM Receiver and Transmitter CircuitsDocument4 pagesSimple AM Receiver and Transmitter CircuitsGokulk2011100% (2)

- DoD Standard for Electronic Component Case OutlinesDocument175 pagesDoD Standard for Electronic Component Case OutlinesAndersonNo ratings yet

- Motorola AN758Document16 pagesMotorola AN758xavir111No ratings yet

- An-779 Low-Distortion 1.6 To 30 MHZ SSB Driver DesignsDocument10 pagesAn-779 Low-Distortion 1.6 To 30 MHZ SSB Driver DesignsEdward YanezNo ratings yet

- D1 5 VSD TransformersDocument51 pagesD1 5 VSD TransformersalgotrNo ratings yet

- Architecture of FPGAs and CPLDS: A TutorialDocument41 pagesArchitecture of FPGAs and CPLDS: A Tutorialgongster100% (5)

- Transformer-Coupled Front-End For Wideband A/D Converters: Primary SecondaryDocument4 pagesTransformer-Coupled Front-End For Wideband A/D Converters: Primary SecondaryAvinash SharmaNo ratings yet

- An-791 A Simplified Approach To VHF Power Amplifier DesignDocument10 pagesAn-791 A Simplified Approach To VHF Power Amplifier DesignEdward YanezNo ratings yet

- Linsley Hood Class PDFDocument129 pagesLinsley Hood Class PDFBenedekEduardNo ratings yet

- Designing Loop AntennasDocument18 pagesDesigning Loop AntennasCesar AvilaNo ratings yet

- Cooling Fan DiagramsDocument10 pagesCooling Fan DiagramsRay MurphyNo ratings yet

- An Ultra-Low-Voltage and Ultra-Low-Power 2.4 GHZ Lna Design: Baimei Liu, Chunhua Wang, Minglin Ma, Shengqiang GuoDocument5 pagesAn Ultra-Low-Voltage and Ultra-Low-Power 2.4 GHZ Lna Design: Baimei Liu, Chunhua Wang, Minglin Ma, Shengqiang GuoLaxmi GuptaNo ratings yet

- DC DC Converters Output NoiseDocument10 pagesDC DC Converters Output NoiseMallickarjuna AsNo ratings yet

- Microelectronics Journal: S. Toofan, A.R. Rahmati, A. Abrishamifar, G. Roientan LahijiDocument4 pagesMicroelectronics Journal: S. Toofan, A.R. Rahmati, A. Abrishamifar, G. Roientan LahijiRF_RAJANo ratings yet

- A 5-Ghz 11.6-Mw Cmos Receiver For Ieee 802.11A ApplicationsDocument4 pagesA 5-Ghz 11.6-Mw Cmos Receiver For Ieee 802.11A ApplicationsDamodar TeluNo ratings yet

- G Contents Papers 380Document4 pagesG Contents Papers 380Mn RajuNo ratings yet

- Design and Simulation of LNA (Cadence Spectre RFDocument19 pagesDesign and Simulation of LNA (Cadence Spectre RFKushal GajavellyNo ratings yet

- A 2.4GHz Front-End With On-Chip Balun in A 0.13um CMOS TechnologyDocument3 pagesA 2.4GHz Front-End With On-Chip Balun in A 0.13um CMOS TechnologyphithucNo ratings yet

- A Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active PixelsDocument5 pagesA Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active Pixelstajmjcet_123No ratings yet

- Application: Design For ProcessDocument4 pagesApplication: Design For ProcessjaberyemeniNo ratings yet

- Low Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationsDocument5 pagesLow Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationssunilsheelavantNo ratings yet

- A 500Μw 2.4Ghz Cmos Subthreshold Mixer For Ultra Low Power ApplicationsDocument4 pagesA 500Μw 2.4Ghz Cmos Subthreshold Mixer For Ultra Low Power ApplicationsRF_RAJANo ratings yet

- Document 1Document8 pagesDocument 1Ali HassanNo ratings yet

- Performance Very Low Frequency Filters: Design Considerations For HighDocument4 pagesPerformance Very Low Frequency Filters: Design Considerations For Highmvmuthukumar88No ratings yet

- A Comparative Study of CMOS LNAsDocument4 pagesA Comparative Study of CMOS LNAsMohammad Arif SaberNo ratings yet

- Design of A 2.0 GHZ Low Noise AmplifierDocument4 pagesDesign of A 2.0 GHZ Low Noise AmplifierVaibhav TiwariNo ratings yet

- Ref (1) Refered CircuitDocument13 pagesRef (1) Refered Circuitraja_ramalingam07No ratings yet

- A 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ADocument4 pagesA 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ARitika SinghNo ratings yet

- A Broadband Folded Gilbert Cell CMOS MixerDocument6 pagesA Broadband Folded Gilbert Cell CMOS MixerMohammedIrshadAhNo ratings yet

- A 2.4 GHZ CMOS Low Noise Amplifier Using An Inter-Stage Matching InductorDocument4 pagesA 2.4 GHZ CMOS Low Noise Amplifier Using An Inter-Stage Matching InductorphithucNo ratings yet

- 2.4-Ghz Single-Ended Input Low-Power Low-Voltage Active Front-End For Zigbee Applications in 90 NM CmosDocument4 pages2.4-Ghz Single-Ended Input Low-Power Low-Voltage Active Front-End For Zigbee Applications in 90 NM CmosdilixyzNo ratings yet

- A Current-Mode 6-9Ghz Uwb Transmitter With Output Power Flattening TechniqueDocument4 pagesA Current-Mode 6-9Ghz Uwb Transmitter With Output Power Flattening TechniqueSantosh Kumar GembaliNo ratings yet

- LNADocument11 pagesLNASunil KumarNo ratings yet

- Linear Amps For Mobile OperationDocument10 pagesLinear Amps For Mobile OperationIan McNairNo ratings yet

- A Low Noise Amplifier Optimized For A GPS Receiver RF Front EndDocument6 pagesA Low Noise Amplifier Optimized For A GPS Receiver RF Front EndterrozerNo ratings yet

- Cmos OpampDocument3 pagesCmos OpampTànVìĐọcNo ratings yet

- A Low Noise and Power Consumption, High-Gain Lna in 130 NM Sige Bicmos Using Transmission LinesDocument4 pagesA Low Noise and Power Consumption, High-Gain Lna in 130 NM Sige Bicmos Using Transmission LinessaidNo ratings yet

- An 762 Rev 0Document10 pagesAn 762 Rev 0Diego MotoqueroNo ratings yet

- A 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanDocument4 pagesA 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanSunil PandeyNo ratings yet

- Design of A 2.5Ghz Differential Cmos Lna: Z SC G C L S (L SC LDocument4 pagesDesign of A 2.5Ghz Differential Cmos Lna: Z SC G C L S (L SC LnaveenmotamarriNo ratings yet

- 06616415Document5 pages06616415jitu_4No ratings yet

- Power Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationDocument5 pagesPower Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationM ANo ratings yet

- Subwoofer Active Low Pass FilterDocument11 pagesSubwoofer Active Low Pass FilterFrank De Leon VailNo ratings yet

- Design of 1.8V 1Ghz 0.18 Mu M Cmos Lna For GPS: October 2008Document5 pagesDesign of 1.8V 1Ghz 0.18 Mu M Cmos Lna For GPS: October 2008Dũng ĐặngNo ratings yet

- Design and Implementation of A Low-Voltage 2.4-Ghz Cmos RF Receiver Front-End For Wireless CommunicationDocument6 pagesDesign and Implementation of A Low-Voltage 2.4-Ghz Cmos RF Receiver Front-End For Wireless CommunicationPaul ShineNo ratings yet

- Modelling and Simulation of Sigma-Delta ADCs in VHDL-AMSDocument5 pagesModelling and Simulation of Sigma-Delta ADCs in VHDL-AMSVitu VituNo ratings yet

- Ieee Delangen 1998Document15 pagesIeee Delangen 1998kurabyqldNo ratings yet

- How To Measure RF TransformersDocument16 pagesHow To Measure RF Transformersعلاء الليبيNo ratings yet

- Design of A Low-Power 10-Bit DAC in 130 NM CMOS Technology: Mamun Bin Ibne Reaz Md. Torikul Islam BadalDocument5 pagesDesign of A Low-Power 10-Bit DAC in 130 NM CMOS Technology: Mamun Bin Ibne Reaz Md. Torikul Islam BadalSunil KumarNo ratings yet

- LC balun design for microwave power amplifiersDocument19 pagesLC balun design for microwave power amplifiersAgus SantosaNo ratings yet

- IEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFDocument3 pagesIEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFQuoc Thang TranNo ratings yet

- Capacimetre FemtoDocument30 pagesCapacimetre FemtoJean-Marie ChaputNo ratings yet

- NJ 10 WDocument14 pagesNJ 10 WmuszereszNo ratings yet

- Linsley Hood Class A PDFDocument17 pagesLinsley Hood Class A PDFMastroghettiNo ratings yet

- Classd A Mj480Document9 pagesClassd A Mj480bladybochoNo ratings yet

- A 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSDocument4 pagesA 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSThanos van RamNo ratings yet

- CMOS Low-Power Analog Circuit DesignDocument55 pagesCMOS Low-Power Analog Circuit DesignRajesh_Nagaraj_9325No ratings yet

- A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-m CMOS For Medical Implant DevicesDocument9 pagesA 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-m CMOS For Medical Implant DevicesAshish JoshiNo ratings yet

- A Self-Biased High Performance Folded Cascode Op-Amp: of ofDocument6 pagesA Self-Biased High Performance Folded Cascode Op-Amp: of ofBodhayan PrasadNo ratings yet

- Self Biased High Performance Folded Cascode Cmos OpampDocument6 pagesSelf Biased High Performance Folded Cascode Cmos OpampArvind MishraNo ratings yet

- 169 T562 PDFDocument5 pages169 T562 PDFYulian Deni AdhitamaNo ratings yet

- IT Service Management Practice Qs Preview PDFDocument23 pagesIT Service Management Practice Qs Preview PDFVignesh BarathiNo ratings yet

- Noise Immunity of Touchscreens: How to Handle Noise from Displays and ChargersDocument13 pagesNoise Immunity of Touchscreens: How to Handle Noise from Displays and ChargersVignesh BarathiNo ratings yet

- The Design and Modeling of Microscale ElectroDocument7 pagesThe Design and Modeling of Microscale ElectroVignesh BarathiNo ratings yet

- ProjectDocument5 pagesProjectVignesh BarathiNo ratings yet

- 3d SensorDocument22 pages3d SensorVignesh BarathiNo ratings yet

- Resource Management On Multi-Core Systems: The ACTORS ApproachDocument9 pagesResource Management On Multi-Core Systems: The ACTORS ApproachVignesh BarathiNo ratings yet

- LXB - Linux BasicsDocument35 pagesLXB - Linux BasicsIvan Narki MarkovićNo ratings yet

- Challenges in Development, Manufacturing and Use of Underfill in Flip Chip Package - Rev5bDocument8 pagesChallenges in Development, Manufacturing and Use of Underfill in Flip Chip Package - Rev5bgauti140% (1)

- Mr. S.C. Bansal: (Lecturer)Document96 pagesMr. S.C. Bansal: (Lecturer)Aizat RazakNo ratings yet

- Semiconductor Physics IntroductionDocument54 pagesSemiconductor Physics IntroductionGod KillerNo ratings yet

- Ans B4Document4 pagesAns B4StudentNo ratings yet

- A SemiconductoresDocument19 pagesA Semiconductoresajcl_1987No ratings yet

- Sam OkDocument81 pagesSam OkItseed CorcaNo ratings yet

- 2SD1351 PDFDocument3 pages2SD1351 PDFmasakpNo ratings yet

- Chiller MemoryDocument21 pagesChiller MemoryminguelameazzaNo ratings yet

- 08146-400-040 ML467 ML267 VGA Mono Monitor ServiceDocument36 pages08146-400-040 ML467 ML267 VGA Mono Monitor ServiceMahesh Pbk BMNo ratings yet

- Infrared Led Based Non Invasive Blood GlucometerDocument5 pagesInfrared Led Based Non Invasive Blood GlucometerYến Nhi Nguyễn ThịNo ratings yet

- Mech Vi Non Traditional Machining (10me665) NotesDocument45 pagesMech Vi Non Traditional Machining (10me665) Notesnikhil0% (1)

- Digital - Linear Electronics Circuits PDFDocument2 pagesDigital - Linear Electronics Circuits PDFGunjan100% (1)

- Elementos ElectrónicosDocument9 pagesElementos ElectrónicosKratt DeividNo ratings yet

- CapacitorDocument7 pagesCapacitorFery YelyantoNo ratings yet

- Practice Exam2 Physics202 MultiplechoiceDocument40 pagesPractice Exam2 Physics202 MultiplechoiceMaram AlbakriNo ratings yet

- Gpdk090 DRMDocument108 pagesGpdk090 DRMAnand ThibbaiahNo ratings yet

- Chapter7 PDFDocument47 pagesChapter7 PDFCailla ReyesNo ratings yet

- Intelligent Power Device IPDs Guide MIP0221SY-MIP0227SY Silicon MOSDocument3 pagesIntelligent Power Device IPDs Guide MIP0221SY-MIP0227SY Silicon MOSChekaraou MageNo ratings yet

- Phase LockDocument35 pagesPhase Lockmoma52No ratings yet

- Lab Manual EE1251 PDFDocument35 pagesLab Manual EE1251 PDFImran KhanNo ratings yet

- ScP037 Circuits ToolboxDocument2 pagesScP037 Circuits ToolboxORBeducationNo ratings yet

- Everlast Is Launching New Models of TIG Welding MachinesDocument3 pagesEverlast Is Launching New Models of TIG Welding MachinesPR.comNo ratings yet

- Static Transfer Switch Design by NoelDocument4 pagesStatic Transfer Switch Design by Noeldarshan chirkeNo ratings yet

- Bluesun Solar Panel BSM455-72HPH 435-455WDocument2 pagesBluesun Solar Panel BSM455-72HPH 435-455WMarcel BekešNo ratings yet

- ASTM G62 87 Reapproved 1998 PDFDocument5 pagesASTM G62 87 Reapproved 1998 PDFGuha ArnabNo ratings yet

- SDC606 SDC PDFDocument11 pagesSDC606 SDC PDFGopalNo ratings yet

- Basic Electrical Engineering Problem Sheet 2Document5 pagesBasic Electrical Engineering Problem Sheet 2ud54No ratings yet