Professional Documents

Culture Documents

Simplified EEE

Uploaded by

vishiwizardCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Simplified EEE

Uploaded by

vishiwizardCopyright:

Available Formats

Simplified Multilevel Inverter Topology

V.Prasath, K.Prem kumar M.Tech-Power Electronics And Drives, SRM University

AbstractMultilevel converters offer high

power capability, associated with lower output harmonics and lower commutation losses. This work reports a new multilevel inverter topology using an H-bridge output stage with a bidirectional auxiliary switch. Many different PWM-strategies for multilevel inverters exist. This paper proposes the various multi-level circuits with PWM strategies for Inverters. Operating

such

as

reduction

in

the

commutation

frequency applied to the power components reduction in the voltages applied to the main power switches, enabling operation at higher load voltage transient voltages automatically limited. The main disadvantage associated with the multilevel configurations is requiring a high number of power switches. Multilevel

converters were used only in some high power applications such as high power motor drivers in marine, mining, or chemical industries applications, high power transmission, power line conditioners, etc. The continuing

principles with switching functions are analyzed for Single Phase Five level PWM inverter. The controller is also designed to keep the output voltage sinusoidal and to have high dynamic performances. The new topology is used in the design of a five-level inverter; only five controlled switches, eight diodes, and two capacitors are required to implement the five-level inverter using the proposed topology.

development of high power high switch frequency devices such as insulated-gate bipolar transistors (IGBTs) working at 3.3, 4.5, and 6.5 kV, and insulated-gate commutated thyristors (IGCT) working at 4.5 or 6 kV[1] has improved overall converter performance, renewing the interest in multilevel topologies, that may be able to compete in the market with

INTRODUCTION:

The different topologies presented in the literature as multilevel converters are show as characteristics in common, giving them some clear advantages over bi-level converters,

the standard two-level pulse width modulation (PWM) converters at lower power ranges. As a contribution to solve these twin problems (cumbersome power stages and complex firing control circuits), this work proposes a new

converter topology, presented as a block diagram in Fig. 1. This topology includes an Hbridge stage with an auxiliary bidirectional switch, drastically reducing the power circuit complexity. [3] These two concepts are used in the design of the five-level bridge converter presented below.[1] The new converter

COMPARISON AMONG THREE MULTILEVEL INVERTERS IN APPLICATION ASPECTS:

In high power system, the multilevel inverters can appropriately replace the exist system that use traditional multi-pulse

converters. All three multilevel inverters can be used in reactive power compensation without having the voltage unbalance problem. Table 1.1 compares the power component

topology used in the power stage offers an important improvement in terms of lower component count and reduced layout

complexity when compared with the five-level converters presented in the literature. The new topology achieves almost a 40% reduction in the number of main power switches required and uses no more diodes or capacitors.

requirements per phase leg among the three multilevel voltage source inverter mentioned below. It shows that the number of main

switches and main diodes, needed by the inverters to achieve the same number of voltage levels.[6] Clamping diodes were not needed in flying-capacitor and cascadedinverter configuration, while balancing

capacitors were not needed in diode clamp and cascaded-inverter configuration. Implicitly, the multilevel converter using cascaded-inverters requires the least number of components. [7]

Comparison of power component requirements per phase leg among

Fig 1

three multilevel inverters

In very high power application especially with very high input voltage, traditional two-level VSIs could not avoid to sue the series connected semiconductor

switches so as to cope with limitations of

device rating utilized and it may be very cumbersome and even problematic mainly due to difficulty of device matching deteriorating utilization factor of switching devices.[5] The multilevel topology, however, suggests a good solution for such a problem.

Additionally, since the two capacitors are connected in parallel with the main dc power supply, no significant capacitor voltage swing is produced during normal operation, avoiding a problem that can limit operating range in some other multilevel configurations.[4][6]

Table 1.1

Inverter Config H bridge Auxiliary switch Main switch Auxiliary switch diodes Capacitors 8 2 20 4 8 10 8 2 1 0 0 0 4 8 8 Diode clamped Capacitor clamped cascade Asymmetric

Power stage operation:

The required five voltage output levels (Vs, Vs/2, 0,-Vs/2,-Vs)

Maximum positive output (Vs):

Switch1 is ON, connecting the load positive terminal to Vs, and switch 4 is ON, connecting the load negative terminal to ground. All other controlled switches are OFF;

Auxiliary devices (diodes, capacitor):

the voltage applied to the load terminal is Vs. Fig.2shows the current paths that are active at

The new configuration reduces the number of diodes by 60 %( eight instead of 20) and the number of capacitors by 50 %( two instead of four) when compared with the diode clamped configurations.[6] The new

this stage.[8]

Half-level positive output (Vs/2):

The auxiliary switch, switch 5 is ON, connecting the load positive terminal to point A, through diodes D5 and D8, and switch 4 is ON, connecting the load negative terminal to ground. All other controlled switches are OFF; the voltage applied to the load terminals is Vs/2.

configuration reduces the number of capacitors by 80 %( two instead of 10) when compared with capacitor clamped configuration. The new configuration uses no more diodes or

capacitors that the second best topology in the table, the symmetric cascade configuration.

Zero output: Two main switches switch3 and switch4 are ON, short-circuiting the load. All other controlled switches are OFF; or the main switches switch1 and switch2 are ON, shortcircuiting the load. All other controlled switches are OFF; the voltage applied to the load terminal is zero.[8] Half-level negative output (-Vs/2): The auxiliary switch, switch 5 is ON, connecting the load positive terminal to point A, through diodes D6 and D7, and switch 2 is ON, connecting the load negative terminal to Vs. All other controlled switches are OFF; the voltage applied to the load terminals is (-Vs/2). Maximum negative output (-Vs): Switch2 is ON, connecting the load negative terminal to Vs, and switch3 is ON, connecting the load positive terminal to ground. All other controlled switches are OFF; the voltage applied to load terminals is (Vs).Fig.9 shows the current paths that are active at this stage. . In this configuration the two capacitors in the capacitive voltage divider are connected directly across the DC bus, and since all switching combinations are activated in an output cycle, the dynamic voltage balance between the two capacitors is automatically restored. The switching combinations that generate the required five output levels (Vs, Vs/2, 0,-Vs/2,-Vs).[4] OFF ON ON OFF OFF ON -VS/2 -VS ON OFF OFF ON ON ON OFF ON OFF VS VS/2 0 Fig.2 waveform of 5-level output.

Table 1.2 Switching combinations required to generate the five-level output voltage waveform

S1 S2 S3 S4 S5 VRL

OFF OFF OFF OFF OFF ON

OFF OFF OFF OFF

SIMULATION RESULTS:

Fig.3 The switching patterns adopted in the proposed inverter Fig.4 Switching Pattern of the proposed single Generally, it is important that the harmonic components of output voltage The figure given above represents the switching pattern developed for the proposed inverter. The figure represents the carrier and reference signal in the first part, the remaining parts gives the pulse for switches 1,2,3,4, and 5 respectively. There are two carrier waves generated along with a reference wave. The switching pattern is developed by the PWM block for the proposed inverter. The switches are turned on and off according to the gate signals given for the switches. The output voltage according to the switch ON-OFF conditions are given in the Table. phase five level PWM inverter

produced by inverter itself should be reduced to alleviate the output current ripple and the core loss of inductor.[7] The developed inverter is simulated and the output voltages waveforms are represented. The figures given below represent the simulated results of output voltage and current for various modulation index from 0.4-1.4.

Table 1.3 Output Voltage according to the Switch ON-OFF Conditions

ON Switches Node A voltage VA S1,S4 S5,S4 S3,S4 (or S1,S2) S2,S5 S2,S3 0 0 Vd/2 Vd -Vd/2 -Vd Vd Vd /2 0(Vd) Node B voltage VB 0 0 0(Vd) Output Voltage VAB= Vo +Vd +Vd/2 0

levels the output waveform in comparison to a single cell inverter. 4) Lower switching losses. 5) Higher voltage capability. 6) Higher power quality. 7) They are 8) The efficiency is very high (>98%) because of the minimum

switching frequency .9) They can improve the power quality and dynamic stability for utility systems.10) They are suitable for medium to high power applications. Thus the multi-level inverters are used in various fields. There are many multilevel inverters developed according to the voltage levels required. This project deals with the design and implementation of single-phase five-level

PWM inverter. The sinusoidal PWM technique is involved in the design which has several advantages over other modulation techniques. The operational and the switching functions are analyzed in detail. In addition it is compared

CONCLUSION:

Multilevel inverters have become an effective and practical solution for increasing power and reducing harmonics of ac waveforms. The main advantages of multilevel PWM inverters are 1) The series connection allows higher voltage without increasing voltage stress on switches.2) Multilevel waveforms reduce the dv/dt at the output of an inverter.3) At the same switching frequency, a multilevel inverter can achieve lower harmonic distortion due to more

with

the

conventional

three-level

PWM

inverter, smaller filter size, improved output waveform and other advantages. The simulation results shows that the developed five-level PWM inverter has many merits such as reduce number of switches, lower EMI, less harmonic distortion. And the THD of the proposed inverter is considerably alleviated and the dynamic responses are also improved significantly. Thus proposed inverter involves many advantages over the

conventional inverter. The study can further be investigated by employing control schemes to have higher dynamic responses and by using higher level inverters. REFERENCES: [1] G. Sinha and T. A. Lipo, A four-level inverter based drive with a passive front end, IEEE Trans. Power Electron., vol. 15, no. 2, pp.285294, Mar. 2000. [2] N. P. Schibli, T. Nguyen, and A. C. Rufer, A three-phase multilevelconverter for highpower induction motors, IEEE Trans. Power. Electron.,vol. 13, no. 5, pp. 978986, Sep. 1998. [3] M. D. Majrekar, P. K. Steimer, and T. A. Lipo, Hybrid multilevel power conversion system: a competitive solution for high-power applications, IEEE Trans. Ind. Appl.., vol. 36, no. 3, pp. 834841, May/Jun. 2000. [4] L. M. Tolbert and T. G. Habertler, Novel multilevel inverter carrier-based PWM method, IEEE Trans. Ind. Appl., vol. 35, no. 5, pp.10981107, Sep./Oct. 1999. [5] M. Marchesoni and P. Tensa, Diodeclamped multilevel converters: a practicable way to balance DC-link voltages, IEEE Trans. Ind. Electron.,vol. 49, no. 4, pp. 752765, Aug. 2002 [6] E. J. Bueno, R. Garcia, M. Marrn, and F. Espinosa, Modulation Techniques

Comparison for Three Levels VSI Converters, in Proc. IEEE 28th Annu. Conf. Ind. Electron. Soc., Nov. 2002, vol. 2, pp. 908913.. [7] D. E. Soto-Sanchez and T. C. Green, Voltage balance and control in a multi-level unified power flow controller, IEEE Trans. Power Delivery, vol. 16, no. 4, pp. 732738, Oct. 2001. [8] Gerardo Ceglia, Vctor Guzmn A New Simplified Multilevel Inverter Topology for DCAC Conversion

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Toyota 1ZZ FE 3ZZ FE Engine Repair Manual RM1099E PDFDocument141 pagesToyota 1ZZ FE 3ZZ FE Engine Repair Manual RM1099E PDFJhorwind Requena87% (15)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- ACM2 TAU Datasheet enDocument5 pagesACM2 TAU Datasheet envishiwizardNo ratings yet

- Sensors Used in HEVDocument4 pagesSensors Used in HEVvishiwizard100% (1)

- OpenSees Geotechnical Analysis Workshop 2017Document70 pagesOpenSees Geotechnical Analysis Workshop 2017Tariq MahmoodNo ratings yet

- Self PublishingDocument84 pagesSelf PublishingFrancesco CusumanoNo ratings yet

- Engineered PlasticsDocument61 pagesEngineered Plastics고병석No ratings yet

- Electrical Resin BenefitsDocument2 pagesElectrical Resin BenefitsvishiwizardNo ratings yet

- Aramco Electrical Safety HandbookDocument5 pagesAramco Electrical Safety HandbookFarhan M100% (1)

- Copper Wire and Cable: From Wikipedia, The Free EncyclopediaDocument16 pagesCopper Wire and Cable: From Wikipedia, The Free Encyclopediatanwar_anuj1990No ratings yet

- 50 SCS Automotive Coatings - Rev0913Document4 pages50 SCS Automotive Coatings - Rev0913vishiwizardNo ratings yet

- Part Winding Startting The Three-Phase Squirrel Cage Induction Motor Air Gap Magnetic Field AnalysisDocument6 pagesPart Winding Startting The Three-Phase Squirrel Cage Induction Motor Air Gap Magnetic Field AnalysisIjabiNo ratings yet

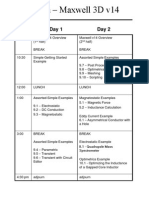

- Maxwell 3D v14 Training AgendaDocument1 pageMaxwell 3D v14 Training AgendavishiwizardNo ratings yet

- LJLVJK LVJJV LKJVDocument5 pagesLJLVJK LVJJV LKJVvishiwizardNo ratings yet

- Hardware Inloop Simulation IEEE LabVIEWDocument1 pageHardware Inloop Simulation IEEE LabVIEWvishiwizardNo ratings yet

- Electric Vehicle Motor Design NotesDocument131 pagesElectric Vehicle Motor Design NotesvishiwizardNo ratings yet

- 5 SmanualDocument16 pages5 SmanualMark ThomasNo ratings yet

- Maxwell 2dDocument7 pagesMaxwell 2dvishiwizardNo ratings yet

- TRL Definitions PDFDocument1 pageTRL Definitions PDFBHARadwajNo ratings yet

- ReadmeDocument4 pagesReadmevishiwizardNo ratings yet

- Op - XT546 246 346 - Op288 V03Document2 pagesOp - XT546 246 346 - Op288 V03vishiwizardNo ratings yet

- Recent Advances in Materials For Use in Permanent Magnet Machines - A ReviewDocument7 pagesRecent Advances in Materials For Use in Permanent Magnet Machines - A ReviewvishiwizardNo ratings yet

- Jeas 1012 787Document5 pagesJeas 1012 787vishiwizardNo ratings yet

- Nit 3600 1Document5 pagesNit 3600 1vishiwizardNo ratings yet

- FAB Resistivity White PaperDocument8 pagesFAB Resistivity White PapervishiwizardNo ratings yet

- How to Check a MOSFETDocument2 pagesHow to Check a MOSFETvishiwizardNo ratings yet

- Big Energy Series 11.5.2012 Qing-Chang ZhongDocument1 pageBig Energy Series 11.5.2012 Qing-Chang ZhongvishiwizardNo ratings yet

- Presentation 1Document1 pagePresentation 1vishiwizardNo ratings yet

- Motor Primer1Document2 pagesMotor Primer1vishiwizardNo ratings yet

- Brushless Motor FundamentalsDocument13 pagesBrushless Motor FundamentalsvishiwizardNo ratings yet

- Wittich2011 SonkusaleVanderveldeDocument1 pageWittich2011 SonkusaleVanderveldevishiwizardNo ratings yet

- Lit Survey RamamurthyDocument9 pagesLit Survey RamamurthyvishiwizardNo ratings yet

- FTF Aut f0234Document38 pagesFTF Aut f0234vishiwizardNo ratings yet

- A Brief Overview of Electric & Hybrid Electric Vehicle TechnologiesDocument1 pageA Brief Overview of Electric & Hybrid Electric Vehicle TechnologiesvishiwizardNo ratings yet

- Cam DesignDocument13 pagesCam DesignvishiwizardNo ratings yet

- Sona SPEED CatalogueDocument13 pagesSona SPEED CataloguevishiwizardNo ratings yet

- LbiDocument13 pagesLbiAac AacNo ratings yet

- Article - Content Management Maturity ModelDocument4 pagesArticle - Content Management Maturity Modelprasannalaldas100% (3)

- Special cables for hybrid vehiclesDocument1 pageSpecial cables for hybrid vehiclesVlado PetkovskiNo ratings yet

- Data Visualization Nanodegree Program Syllabus PDFDocument4 pagesData Visualization Nanodegree Program Syllabus PDFsergio paredesNo ratings yet

- Solar Home Lighting System 40 Watt: (GST Inclusive Price)Document5 pagesSolar Home Lighting System 40 Watt: (GST Inclusive Price)nachiNo ratings yet

- Labnet International 2011 International CatalogDocument60 pagesLabnet International 2011 International CataloglabnetinternationalNo ratings yet

- BassoonBocals PDFDocument3 pagesBassoonBocals PDFnheyminkNo ratings yet

- Singtel Satellite Coverage Maps1Document12 pagesSingtel Satellite Coverage Maps1Anh TúNo ratings yet

- Ramon Magsaysay Memorial College-Marbel INC Bachelor of Science in Tourism ManagementDocument7 pagesRamon Magsaysay Memorial College-Marbel INC Bachelor of Science in Tourism ManagementRam G. MorteraNo ratings yet

- Ale For Abapers - Day3Document15 pagesAle For Abapers - Day3Supratim RayNo ratings yet

- Versidrain 150: Green RoofDocument2 pagesVersidrain 150: Green RoofMichael Tiu TorresNo ratings yet

- GHX-308A/616 Hybrid Key Telephone System ManualDocument109 pagesGHX-308A/616 Hybrid Key Telephone System ManualJoel García100% (1)

- Capilary Tube For Ac and RefrigeratorDocument4 pagesCapilary Tube For Ac and RefrigeratorJoko SubagyoNo ratings yet

- A5 Service Manual 2.8Document223 pagesA5 Service Manual 2.8Anahi Calle Velasco0% (1)

- Applied Machine Learning ANNDocument6 pagesApplied Machine Learning ANNGilbe TestaNo ratings yet

- Safety Bulletin 35 HOT WORKDocument3 pagesSafety Bulletin 35 HOT WORKTrebor SantosNo ratings yet

- BC Zong ProjectDocument25 pagesBC Zong Projectshahbaz awanNo ratings yet

- Investment Opportunities in OdishaDocument28 pagesInvestment Opportunities in OdishaNiladri MandalNo ratings yet

- Cyberspace in National Perspective AbstractDocument5 pagesCyberspace in National Perspective AbstractJiri HofmanNo ratings yet

- Presentation Title: Debugging Simulation ModelsDocument74 pagesPresentation Title: Debugging Simulation ModelsflyingdreamsNo ratings yet

- Recruitment of Junior Associates (Customer Support & Sales)Document5 pagesRecruitment of Junior Associates (Customer Support & Sales)Revanth TallaNo ratings yet

- Application of PWM Speed ControlDocument7 pagesApplication of PWM Speed ControlJMCproductsNo ratings yet

- Fujitsu-General ASYG07-12 LLC 2014Document2 pagesFujitsu-General ASYG07-12 LLC 2014Euro-klima BitolaNo ratings yet

- Assignment # La 01 Name: Muhammad Ghufran Siddiqui F.Name: Abdul Sami Class: BSSE (Ii) Section: A Roll No: 32Document5 pagesAssignment # La 01 Name: Muhammad Ghufran Siddiqui F.Name: Abdul Sami Class: BSSE (Ii) Section: A Roll No: 32Mehak AnsariNo ratings yet

- Manual en Español Kip 3000Document2 pagesManual en Español Kip 3000Ja De OstiaNo ratings yet