Professional Documents

Culture Documents

001-64560 00 V

Uploaded by

priyosantosaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

001-64560 00 V

Uploaded by

priyosantosaCopyright:

Available Formats

Ha

Hardware Multiplexing of SAR ADC PSoC 5

Project Name: HardwareMultiplexing_SAR Programming Language: C Associated Part Families: CY8C55xx Software: PSoC Creator Related Hardware: CY8CKIT-001 Prerequisites: EP61959: 8-Bit ADC Data Buffering Using DMA - PSoC 3 / PSoC 5, EP62512: Using SAR ADC in PSoC 5 Author: Pavankumar Vibhute

EP64560

Project Objective Overview

The project demonstrates the multiplexing of SAR ADC using hardware multiplexer component.

When there are several signals to be measured using a single ADC, the ADC needs to be time multiplexed to convert the signals one after the other. In PSoC 5, SAR ADC can be multiplexed completely in hardware without involvement of CPU, using the hardware multiplexer component (AMuxHw). In this example project, three-channel multiplexing is shown. The SAR ADC converts at one Msps speed at 8-bit resolution. Each channel is converted at the rate around 333 Ksps. A DMA is configured to transfer the channel results to voltage DACs. Three different waveforms are given as inputs to the multiplexer and the same waveforms are reproduced at the DAC outputs to verify the working of multiplexing.

Component List

Instance Name ADC_SAR AMuxHw Component Name SAR ADC Analog Hardware Mux (GPIO) Clock Clock PWM Version 1.5 1.5 Component Category Analog ADC Analog Analog MUX System System Digital Functions Digital Logic System Analog DAC Analog Amplifiers Ports and Pins Comments The ADC is configured in continuous mode and 8 bit resolution It is configured for 3 channels

Clock_ADC Clock_Mux PWM_ClockGenerator

1.5 1.5 1.5

It is set to 14 MHz so that SAR ADC operates at 1 Msps. It is synchronization clock to AMuxHw. It is set to BUS_CLK It is used to generate a clock for the LUT switching logic. A pulse is generated 5 clock cycles after EOC of ADC The LUT changes the select lines to select the next channel. It is given a clock from LUT It is configured to have three TDs. It transfers the ADC result to DACs. It is set in the 4 V range. The DAC has high output impedance therefore the DAC output is buffered before routed to pin. -

LUT_SwitchingLogic DMA VDAC8_1, VDAC8_2, VDAC8_3 Opamp_Buffer_1, Opamp_Buffer_2, Opamp_Buffer_3, Pin_Channel_1, Pin_Channel_2, Pin_Channel_3, Pin_MuxOut, Pin_DAC_1, Pin_DAC_2, Pin_DAC_3 Pin_EOC, Pin_SwitchingClock, Pin_SAR_Clock

October 13, 2010

Lookup Table DMA VDAC Opamp

1.5 1.5 1.5 1.5

Analog Pin

1.5

Digital Output Pin

1.5

Ports and Pins

These signals are put on the pins for monitoring.

1

Document No. 001-64560 Rev. **

[+] Feedback

EP64560

Top Design

Page 1: ADC_Muliplexing

Page 2: Switching Logic

Page 3: DMA and DAC

October 13, 2010

Document No. 001-64560 Rev. **

[+] Feedback

EP64560

The following figure shows the pin placement as it appears in the .cydwr file.

Component Configuration

ADC_SAR

AMuxHw

October 13, 2010

Document No. 001-64560 Rev. **

[+] Feedback

EP64560

PWM_ClockGenerator

The PWM is configured to generate a pulse one clock cycle wide. This pulse occurs five clock cycles after it is triggered by the ADC EOC.

LUT_SwitchingLogic

LUT outputs out1 and out0 are connected to select lines of AMuxHw. There are three valid states in the LUT; each state provides output to select a unique channel. The transition to the next state occurs on every rising edge of the clock input.

October 13, 2010

Document No. 001-64560 Rev. **

[+] Feedback

EP64560

DMA

DMA is configured in the function DMA_Initialize() in main.c file using DMA APIs.

VDAC8_1

The same configuration is done for the VDAC8_2 and VDAC8_3.

Opamp_Buffer_1

The same configuration is done for the Opamp_Buffer_2 and Opamp_Buffer_3.

October 13, 2010 Document No. 001-64560 Rev. ** 5

[+] Feedback

EP64560

Design Wide Resources

Configure the clocks as shown in the following figure. The Master clock is set to 42 MHz so that with integer divider the SAR ADC gets 14 MHz clock. Open the Clocks tab in the cydwr and click on the BUS_CLK to get the system clocks configuration window as shown in the following figure.

Remaining settings in the design wide resources are left as default.

Operation

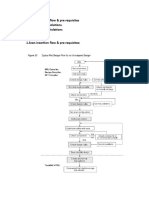

The SAR ADC is configured for 8-bit resolution and in continuous mode operation. A 14-MHz clock is given to clock input of the SAR ADC. It takes 14 clock cycles for each conversion resulting in conversion rate of one Msps. It samples the input for four clock cycles. The number of cycles for sampling is configurable in register ADC_SAR_SAR_CSR2_REG. The default number of cycles for sampling is four. After sampling, it converts the signal from analog to digital for next 10 clock cycles. During these ten clock cycles, the input is not being used by the ADC and channel is switched during this time. Following is the timing diagram.

14 clock cycles

5 clock cycles

Switching Clock

EOC

4 cycles of sampling

ADC Clock

ADC generates the EOC signal after every end of conversion and it starts sampling the input for next conversion. The channel is switched five clock cycles after EOC. A switching clock is generated using PWM, it is a pulse with width of one ADC clock cycle. It occurs six cycles after the EOC as shown earlier. This clock is given as a trigger to channel switching logic that changes the select lines of the mux to select the next channel.

October 13, 2010

Document No. 001-64560 Rev. **

[+] Feedback

EP64560

The channel switching logic is built with LUT. The outputs of the LUT are connected to select lines. The LUT states are written such that the channel 1, channel 2 and channel 3 are selected one after the other in round robin manner. Whenever there is a rising edge on the LUT clock, it changes the select lines to select the next channel. The AMuxHw senses the select lines on every rising edge of its clock. A BUS_CLK (42 MHz) is connected to AMuxHw for synchronization and implementing Break before Make feature. It detects any change on the select lines on rising edge of the clock, if there is a change, it disconnects all the channels (Break). On the next rising edge of the clock, it connects the new channel selected by the select lines (Make). Therefore, there can be maximum delay of two clock cycles of 42 MHz after the select lines select the new channel and the channel is actually switched. DMA is configured to transfer the ADC results to VDAC. Three Transaction Descriptor (TDs) are used to transfer three channel results to three VDACs. The ADC range is set to Vssa to Vdda but the VDAC has range Vssa to 4.08 V. Therefore, though the ADC and DAC both have 8-bit resolution, the VDAC output will be scaled voltage of the actual ADC input. The waveforms are shown in the Output section.

Hardware Connections

The project is tested with PSoC Development Kit CY8CKIT-001 (DVK). The kit is used with jumpers in the default state. Refer to the PSoC Development Kit Board Guide, provided with the kit. Two-channel function generator is used, two channels are set to give different waveforms like sine, square or triangular. The voltage range of the signals should be within the Vssa and Vdda, otherwise it may damage the device. The first channel is connected to P0[3] with respect to ground. The second channel is connected to P0[4]. These signals are channel 1 and channel 2 of mux. The potentiometer on the DVK is powered by placing the jumper on the J11. The VR (potentiometer output) is connected to P0[5] on P14 of DVK. This is third channel of the mux. Connect Pin P0[0], P0[1] and P3[6] to oscilloscope to observe the outputs. Use two-channel function generator and set both channels to give triangular wave of frequency 100 Hz, 1 V p-p and with phase difference 00. Set the offsets of both the channels to a voltage equal to Vdda/2.

Output

Build the project and program the PSoC 5 device. Note The default device selection is PSoC 3 (CY8C3866AXI-040), for using this project with PSoC 5 device follow the given steps. Go to Project Device Selector Select PSoC 5 device (CY8C5588AXI-060), build the project again and program the PSoC 5 device as shown in the following figure.

October 13, 2010

Document No. 001-64560 Rev. **

[+] Feedback

EP64560

The pin P0[0], P0[1] and P3[6] are observed on the oscilloscope. Vary the frequency, amplitude and shape of the waveform and observe the same on the output. Note that the input signal range should be within the Vssa to Vddd. Below are the example waveforms. o Inputs: Channel 1 of mux (P0[3]): Sine waveform from function generator channel 1. Freq= 10 kHz, 2 Vp-p, Offset = Vdda/2 (Vdda=5 V) Channel 2 of mux (P0[4]): Triangular waveform from function generator channel 2. Freq= 10 kHz, 2 Vp-p, Offset = Vdda/2 (Vdda= 5V) Channel 3 of mux (P0[5]): DC voltage from potentiometer on the DVK. o DAC Outputs: Channel 1:Pin P0[0] Channel 2:Pin P0[1] Channel 3:Pin P3[6] Note Only four signals are shown on oscilloscope, two inputs from function generator and two DAC outputs. The DAC output will be scaled down version of the input because ADC range is 0 to Vdda and the DAC range is 0 to 4.08 V. Vdda is set at 5 V.

October 13, 2010

Document No. 001-64560 Rev. **

[+] Feedback

EP64560

PSoC is a registered trademark of Cypress Semiconductor Corporation. PSoC Creator and PSoC Designer are trademarks of Cypress Semiconductor Corporation. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730

http://www.cypress.com/

Cypress Semiconductor Corporation, 2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and i s protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conj unction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress. Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in lif e-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress ag ainst all charges. Use may be limited by and subject to the applicable Cypress software license agreement.

October 13, 2010

Document No. 001-64560 Rev. **

[+] Feedback

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- MPU6050Document1 pageMPU6050priyosantosaNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Wall E List of PartsDocument2 pagesWall E List of PartspriyosantosaNo ratings yet

- Video KB How To Install HDP 3Document2 pagesVideo KB How To Install HDP 3priyosantosaNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Video KB How To Install HDP 3Document2 pagesVideo KB How To Install HDP 3priyosantosaNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Install ESP8266 Core For Arduino IDEDocument3 pagesInstall ESP8266 Core For Arduino IDEpriyosantosaNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Install HDP3 Using Ambari 2.7.00Document1 pageInstall HDP3 Using Ambari 2.7.00priyosantosaNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Chord WheelDocument3 pagesChord Wheelukrobbz100% (1)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- CVAVR Getting Started With Atmel Studio PDFDocument31 pagesCVAVR Getting Started With Atmel Studio PDFJhonyAmbaritaNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Readme PDFDocument9 pagesReadme PDFDieGoOChoaNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Text Deep Neural NetworkDocument5 pagesText Deep Neural NetworkpriyosantosaNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Pivot ExcelDocument50 pagesPivot ExcelpriyosantosaNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Pengendalian Electronic Home Appliances Berbasis IP Dengan Mengunakan Modul Wiznet NM7010ADocument24 pagesPengendalian Electronic Home Appliances Berbasis IP Dengan Mengunakan Modul Wiznet NM7010ApriyosantosaNo ratings yet

- How To Download and Restore or Flash NodeMCU V3 Stock FirmwareDocument4 pagesHow To Download and Restore or Flash NodeMCU V3 Stock FirmwarepriyosantosaNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Cheatsheet A5Document24 pagesCheatsheet A5Vipul SharmaNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- LCD GDM12864HDocument13 pagesLCD GDM12864HSintesoftNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Da00 Numicronuc100f1Document523 pagesDa00 Numicronuc100f1priyosantosaNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Install ESP8266 Core For Arduino IDEDocument3 pagesInstall ESP8266 Core For Arduino IDEpriyosantosaNo ratings yet

- 130101011Document3 pages130101011priyosantosaNo ratings yet

- X-CTU ManualDocument16 pagesX-CTU ManualAb PerezNo ratings yet

- An1023en Iec60730-1 Class BDocument14 pagesAn1023en Iec60730-1 Class BpriyosantosaNo ratings yet

- DP83848C PDFDocument84 pagesDP83848C PDFpriyosantosaNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Breadboard Arduino KitDocument8 pagesBreadboard Arduino KitMC. Rene Solis R.100% (3)

- Arduino: An Open Electronics Prototyping Platform: David A. MellisDocument11 pagesArduino: An Open Electronics Prototyping Platform: David A. Mellissmeneses741No ratings yet

- Next Generation Graphical Programming With LabVIEWDocument34 pagesNext Generation Graphical Programming With LabVIEWpriyosantosaNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- X-CTU ManualDocument16 pagesX-CTU ManualAb PerezNo ratings yet

- Sensar Temperatura Con LM34 y ArduinoDocument1 pageSensar Temperatura Con LM34 y ArduinosalokaNo ratings yet

- Breadboard Arduino KitDocument8 pagesBreadboard Arduino KitMC. Rene Solis R.100% (3)

- Et STM32F103Document25 pagesEt STM32F103priyosantosaNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Sensar Temperatura Con LM34 y ArduinoDocument1 pageSensar Temperatura Con LM34 y ArduinosalokaNo ratings yet

- NMEA Parser DesignDocument4 pagesNMEA Parser DesignpriyosantosaNo ratings yet

- 93096v00 Beamforming Whitepaper PDFDocument22 pages93096v00 Beamforming Whitepaper PDFEmre KilcioğluNo ratings yet

- 12v Audio AmplifierDocument13 pages12v Audio AmplifierSusrita Barai100% (1)

- Scan Insertion FlowDocument9 pagesScan Insertion Flowsharath ANo ratings yet

- Modicon Momentum - 172JNN21032Document2 pagesModicon Momentum - 172JNN21032Larry PLCHNo ratings yet

- Electronic Instrumentation and Measurements, 3/e David A. BellDocument31 pagesElectronic Instrumentation and Measurements, 3/e David A. Bellsabak gardiaNo ratings yet

- Nanotechnology in ElectronicsDocument28 pagesNanotechnology in ElectronicsAbhishek RajNo ratings yet

- 02-02 The Benefits of SAN and NAS Storage PDFDocument18 pages02-02 The Benefits of SAN and NAS Storage PDFJosecriz DalmacioNo ratings yet

- CS Fallback (CSFB) : Radio Access ProcedureDocument26 pagesCS Fallback (CSFB) : Radio Access ProcedurerazafarhanNo ratings yet

- Modem and Fax Pass ThroughDocument46 pagesModem and Fax Pass ThroughmypdNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- P-Audio BM-D446Document1 pageP-Audio BM-D446Adina PredaNo ratings yet

- R-J2 Mate Controller - B81315Document181 pagesR-J2 Mate Controller - B81315Marek Grysko100% (1)

- Brkarc 2003Document114 pagesBrkarc 2003alfagemeoNo ratings yet

- P.E.L Iec 60076-3-2000 2021-7-20Document2 pagesP.E.L Iec 60076-3-2000 2021-7-20Luis Alfredo Ramos FernandezNo ratings yet

- Semiconductor KTA1266: Technical DataDocument2 pagesSemiconductor KTA1266: Technical Dataserrano.flia.coNo ratings yet

- 1 (CHS) Materials, Tools, Equipment and Testing DevicesDocument5 pages1 (CHS) Materials, Tools, Equipment and Testing DevicesArtem ParriñasNo ratings yet

- Opa1692 Low-Power, Low-Noise and Low-Distortion Soundplus™ Audio Operational AmplifiersDocument42 pagesOpa1692 Low-Power, Low-Noise and Low-Distortion Soundplus™ Audio Operational Amplifierskishore_bulli6666No ratings yet

- Pioneer 1005 SMDocument22 pagesPioneer 1005 SMe2140r03No ratings yet

- 1MRK504086-UEN - en Technical Reference Manual Transformer Protection IED RET 670 1.1 PDFDocument1,042 pages1MRK504086-UEN - en Technical Reference Manual Transformer Protection IED RET 670 1.1 PDFeletricarec0002No ratings yet

- Argus For Asia Sae Ue Ms Cu WeDocument2 pagesArgus For Asia Sae Ue Ms Cu WeAANo ratings yet

- P 4Document25 pagesP 4RanganokNo ratings yet

- HD K-BUS Home & Buildind Automation Catalog 2014 PDFDocument20 pagesHD K-BUS Home & Buildind Automation Catalog 2014 PDFlfrn20044593No ratings yet

- 04 Antenna ArraysDocument53 pages04 Antenna Arrayshabtemariam mollaNo ratings yet

- 100 Top Operational Amplifiers Questions and Answers PDF Operational Amplifiers Questions and AnswersDocument12 pages100 Top Operational Amplifiers Questions and Answers PDF Operational Amplifiers Questions and AnswersSharanya50% (2)

- User Manual User Manual User Manual User Manual: FA-2 Frequency CounterDocument15 pagesUser Manual User Manual User Manual User Manual: FA-2 Frequency CounterCarlos Guillermo VahnovanNo ratings yet

- 1244153Document86 pages1244153Caétano B MascarénhasNo ratings yet

- L18 HornsDocument29 pagesL18 Hornsmzohaib_awan1418No ratings yet

- Tapcon - 240 en PDFDocument6 pagesTapcon - 240 en PDFyebriNo ratings yet

- E1 Pin AssignmentDocument4 pagesE1 Pin Assignmentihab_abdullahNo ratings yet

- IoT RF Reverse EngineeringDocument79 pagesIoT RF Reverse EngineeringpijocrejicNo ratings yet

- WS C2960X 24PSQ L - ManualDocument102 pagesWS C2960X 24PSQ L - ManualAlejandro SandovalNo ratings yet