Professional Documents

Culture Documents

Microchip PIC16F8x Instruction Set

Uploaded by

duo2coreOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Microchip PIC16F8x Instruction Set

Uploaded by

duo2coreCopyright:

Available Formats

Introduction

As I was getting sick and tired of re-reading the instruction set information in the datasheet for the PIC16F8x microcontroller (very informational, but difficult to read, and spread over several pages), I decided to compile this easy to read, two page thing of all the instructions and register files. The information presented here has been compiled from the datasheet, but since typos may appear please use this document with appropriate care. Thank you! //denMike, April 4th, 2002

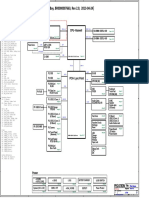

Microchip PIC16F8x Instruction Set Summary

Instruction Description ADDLW ADDWF ANDLW ANDWF BCF BSF BTFSC BTFSS CALL CLRF CLRW CLRWDT COMF DECF DECFSZ Add constant to W Add W to register, store in register Add W to register, store in W AND constant with W AND W with register, store in register AND W with register, store in W Bit clear in register Bit set in register Bit test, skip if clear Bit test, skip if set Call subroutine Clear register Clear W Clear watchdog timer Complement register, store in register Complement register, store in W Decrement register, store in register Decrement register, store in W Decrement register, store in register, skip if 0 Example ADDLW 0x15 ADDWF reg,F ADDWF reg,W ANDLW b01010101 ANDWF reg,F ANDWF reg,W BCF reg,7 BSF reg,7 BTFSC reg,7 next instruction BTFSS reg,7 next instruction CALL label CLRF reg CLRW CLRWDT COMF reg,F COMF reg,W DECF reg,F DECF reg,W DECFSZ reg,F next instruction DECFSZ reg,W next instruction GOTO label INCF reg,F INCF reg,W INCFSZ reg,F next instruction INCFSZ reg,W next instruction IORLW d137 IORWF reg,F IORWF reg,W MOVF reg,W MOVF reg,F MOVLW 13 MOVWF reg NOP RETFIE RETLW 0AAh RETURN RLF Reg,F RLF Reg,W RRF Reg,F RRF Reg,W SLEEP SUBLW 4 SUBWF reg,F SUBWF reg,W SWAPF reg,F SWAPF reg,W XORLW 137 XORWF reg,F XORWF reg,W Result W := W + 15h Reg := Reg + W W := Reg + W W := W and 01010101b Reg := Reg and W W := Reg and W Reg[bit 7] := 0 Reg[bit 7] := 1 if Reg[bit 7] = 1 then NEXT INSTRUCTION if Reg[bit 7] = 0 then NEXT INSTRUCTION TOS := PC+1; PC := label Reg := 0 W := 0 WDT := 0 Reg := not Reg W := not Reg Reg := Reg - 1 W := Reg - 1 Reg := Reg - 1 if Reg <> 0 then NEXT INSTRUCTION W := Reg - 1 if W <> 0 then NEXT INSTRUCTION PC := label Reg := Reg + 1 W := Reg + 1 Reg := Reg + 1 if Reg <> 0 then NEXT INSTRUCTION W := Reg + 1 if W <> 0 then NEXT INSTRUCTION W := W or 137d Reg := Reg or W W := Reg or W W := Reg Z flag updated W := 13h Reg := W PC := TOS; GIE enabled W := 0AAh; PC := TOS PC := TOS Reg := RCL Reg W := RCL Reg Reg := RCR Reg W := RCR Reg WDT := 0 W := 4 - W Reg := Reg - W W := Reg - W Reg := RegHi xchg RegLo W := RegHi xchg RegLo W := W xor 137h Reg := Reg xor W W := Reg xor W Flags affected C,DC,Z C,DC,Z C,DC,Z Z Z Z none none none none none Z := 1 Z := 1 none Z Z Z Z none

Decrement register, store in W, skip if 0

none

GOTO INCF INCFSZ

Unconditional branch Increment register, store in register Increment register, store in W Increment register, store in register, skip if 0

none Z Z none

Increment register, store in W, skip if 0

none

IORLW IORWF MOVF MOVLW MOVWF NOP RETFIE RETLW RETURN RLF RRF SLEEP SUBLW SUBWF SWAPF XORLW XORWF

Inclusive OR constant with W Inclusive OR W with register, store in reg Inclusive OR W with register, store in W Move register to W Nothing moved, but Z flag updated Move constant to W Move W to register No operation Return from interrupt Return from subroutine with constant in W Return from subroutine Rotate register left through carry, store in reg Rotate register left through carry, store in W Rotate register right through carry, store in reg Rotate register right through carry, store in W Enter power-down mode Subtract W from constant Subtract W from register, store in register Subtract W from register, store in W Swap nibbles in register, store in register Swap nibbles in register, store in W Exclusive OR constant with W Exclusive OR W with register, store in reg Exclusive OR W with register, store in W

Z Z Z Z Z none none none GIE := 1 none none C C C C none C,DC,Z C,DC,Z C,DC,Z none none Z Z Z

Note: TOS = Top of Stack

BANK0 Address 00h 01h 02h 03h 04h 05h 06h 07h 08h 09h 0Ah 0Bh BANK1 Address 80h 81h 82h 83h 84h 85h 86h 87h 88h 89h 8Ah 8Bh Name INDF TMR0 PCL STATUS FSR PORTA PORTB EEDATA EEADR PCLATH INTCON

Microchip PIC16F8x Memory Layout

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Indexed addressing data read/write (not a physical register) 8-bit real-time clock/counter Low order 8 bits of the Program Counter (PC) IRP RP1 RP0 !TO !PD Z Indexed addressing address pointer 0 Unimplemented, read as 0 RA4/TOCKI RA3 RA2 RB7 RB6 RB5 RB4 RB3 RB2 Unimplemented location, read as 0 EEPROM data register EEPROM address register Unimplemented, read as 0 Write buffer for upper 5 bits of the PC GIE EEIE T0IE INTE RBIE T0IF Bit 1 Bit 0

DC RA1 RB1

C RA0 RB0/INT

INTF

RBIF

Name INDF OPTION_REG PCL STATUS FSR TRISA TRISB EECON1 EECON2 PCLATH INTCON

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Maps address 00h !RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 Maps address 02h Maps address 03h Maps address 04h Unimplemented, read as 0 PORTA data direction register (1=input (default), 0 = output) PORTA data direction register (1=input (default), 0 = output) Unimplemented location, read as 0 Unimplemented, read as 0 EEIF WRERR WREN WR RD EEPROM control register 2 - used internally for EEPROM writes (not a physical register) Unimplemented, read as 0 Maps address 0Ah Maps address 0Bh

STATUS REGISTER bit Name Description 7 IRP Not used - should be maintained clear 6 RP1 Not used - should be maintained clear 5 RP0 Register bank select bit 4 !TO Time-out bit 3 !PD Power-down bit 2 Z Zero bit 1 DC Digit carry/!borrow bit (for ADDWF and ADDLW instructions) 0 C Carry/!borrow bit (for ADDWF, ADDLW, RRF, and RLF instructions) INTCON REGISTER bit Name Description 7 GIE Global interrupt enable bit 6 EEIE EE write complete interrupt enable bit 5 T0IE TMR0 Overflow interrupt enable bit 4 INTE RB0/INT interrupt enable bit 3 RBIE PortB[7:4] Change interrupt enable bit 2 T0IF TMR0 oferflow interrupt flag bit 1 INTF RB0/INT interrupt flag bit 0 RBIF PortB[7:4] change interrupt flag bit

0 always always bank 0 (00h-7Fh) WDT time-out occured by execution of the SLEEP instr Last result was NOT zero No carry-out No carry-out

1 never never bank 1 (80h-FFh) after power-up, CLRWDT or SLEEP instr after power-up or by the CLRWDT instr Last result was zero A carry-out from the 4th low order bit of the result A carry-out from the MSB of the result occured

0 Disable all interrupts Disable Disable Disable Disable No overflow occured No interrupt occured No pin have changed

1 Enables all un-masked ints Enable Enable Enable Enable TMR0 has overflowed (must be cleared in software) An RB0/INT interrupt occured At least one pin changed (must be cleared in software)

OPTION_REG REGISTER bit Name Description 7 !RBPU PortB pull-up enable bit 6 INTEDG Interrupt edge select bit 5 T0CS TMR0 clock source select pin 4 T0SE TMR0 external (RA4/T0CLK) source edge select bit 3 PSA Prescaler assignment bit 2:0 PS2:PS0 Prescaler rate select bits Bit value 000 001 010 011 EECON1 bit Name 7:5 4 EEIF 3 WRERR 2 WREN 1 WR 0 RD TMR0 rate 1:2 1:4 1:8 1:16 WDT rate 1:1 1:2 1:4 1:8

0 Disable pull-ups RB0/INT intr on falling edge Internal (clk/4) Increment on low-to-high Assigned to TMR0 See below TMR0 rate 1:32 1:64 1:128 1:256

1 Enable pull-ups RB0/INT intr on rising edge Transition on RA4/T0CLK pin Increment on high-to-low Assigned to watchdog timer See below

Bit value 100 101 110 111

WDT rate 1:16 1:32 1:64 1:128

Description Unimplemented read as 0 EE write operation interrupt flag bit EE error flag bit EE write enable bit Write control bit Read control bit

0 Always Not complete Write completed Inhibits writes Write complete Does nothing

1 Never The write operation completed (must be cleared in software) Write didnt complete Allows writes Initiates a write (cleared in hardware) Initiates an EE read (cleared in hardware)

You might also like

- ZX4800Document198 pagesZX4800pkleinstNo ratings yet

- 8051 MicrocontrollerDocument222 pages8051 Microcontrollergirish100% (1)

- ARM Teaching MaterialDocument33 pagesARM Teaching MaterialViswa PraveenNo ratings yet

- Onyxworks®: Fire Systems Command InterfaceDocument4 pagesOnyxworks®: Fire Systems Command InterfacePabloNo ratings yet

- CPU Architecture: Control Unit (CU)Document10 pagesCPU Architecture: Control Unit (CU)i study100% (1)

- 6 BCP-DCPDocument19 pages6 BCP-DCPWriter CourseNo ratings yet

- Embedded Systems With 8051 CDocument190 pagesEmbedded Systems With 8051 CPayal SinghNo ratings yet

- Week 04Document68 pagesWeek 04aroosa naheedNo ratings yet

- Complete Manual Updated-MergedDocument59 pagesComplete Manual Updated-MergedTayyaba AsifNo ratings yet

- Avr Set IntructionsDocument160 pagesAvr Set IntructionsLuuLu Gaarciaa CeervaanteesNo ratings yet

- Laboratory Introduction: 35 Instructions Same As Previous PIC Versions (Eg 16F74)Document12 pagesLaboratory Introduction: 35 Instructions Same As Previous PIC Versions (Eg 16F74)dhivakargunalanNo ratings yet

- An Introduction To The PIC Microcontroller: EE2801 - Lecture 19Document9 pagesAn Introduction To The PIC Microcontroller: EE2801 - Lecture 19Reddy BabuNo ratings yet

- CMS16P53Document32 pagesCMS16P53kowinthawNo ratings yet

- 8080 Assembly Language MnemonicsDocument3 pages8080 Assembly Language MnemonicsDavid StaudacherNo ratings yet

- New Embedded Manual 2020Document75 pagesNew Embedded Manual 2020malikabdullah1082No ratings yet

- 80511Document123 pages80511snehith009100% (1)

- Block Diagram of Processor (Harvard)Document48 pagesBlock Diagram of Processor (Harvard)Nichita IonutNo ratings yet

- PIC 16F877A Microcontroller Core Features: Unit 6Document10 pagesPIC 16F877A Microcontroller Core Features: Unit 6Altaaf MulaniNo ratings yet

- Status Registers (Address 03h, 83h, 103h, and 183h) R/W - 0 R/W-0 R/W-0 R-1 R-1 R/W-X R/W-X R/W-X IRP RP1 RP0 TO PD Z DC CDocument9 pagesStatus Registers (Address 03h, 83h, 103h, and 183h) R/W - 0 R/W-0 R/W-0 R-1 R-1 R/W-X R/W-X R/W-X IRP RP1 RP0 TO PD Z DC Criyasudeen786No ratings yet

- PIC18F4520 Instruction SetDocument4 pagesPIC18F4520 Instruction SetCongtan94No ratings yet

- 330 03Document39 pages330 03navydevilzNo ratings yet

- PIC Microcontrollers: Low-End ArchitecturesDocument46 pagesPIC Microcontrollers: Low-End Architecturesvivek2585No ratings yet

- ARM Teaching MaterialDocument33 pagesARM Teaching MaterialbalaNo ratings yet

- Lesson3 (On $mod51)Document8 pagesLesson3 (On $mod51)hdquanNo ratings yet

- Micro ControllerDocument17 pagesMicro ControllerdilNo ratings yet

- PIC 18 Introduction: GCS250 Computer Architecture Gustavo Rodriguez-Rivera Purdue UniversityDocument36 pagesPIC 18 Introduction: GCS250 Computer Architecture Gustavo Rodriguez-Rivera Purdue Universityamhosny2010No ratings yet

- 16f877a Pic ControllerDocument30 pages16f877a Pic Controlleryuvakirani100% (1)

- Microprocessor and Microcontrroller Module 1 - Calicut UniversityDocument32 pagesMicroprocessor and Microcontrroller Module 1 - Calicut UniversityAshwin GopinathNo ratings yet

- 4.5 Register Organisation in 8051Document6 pages4.5 Register Organisation in 8051Smarajit MishraNo ratings yet

- Lec10 Pic InstDocument37 pagesLec10 Pic InstSalah DahouathiNo ratings yet

- DIGPRA3 - Assignment 2 - 34006559Document22 pagesDIGPRA3 - Assignment 2 - 34006559Themba MaviNo ratings yet

- Assembly Language Instructions: ELEC 330 Digital Systems Engineering Dr. Ron HayneDocument47 pagesAssembly Language Instructions: ELEC 330 Digital Systems Engineering Dr. Ron HayneMohammad Hafiz OthmanNo ratings yet

- Lab 4 Rev. 2.4 Parallel I/O and Keyboard ScanningDocument13 pagesLab 4 Rev. 2.4 Parallel I/O and Keyboard ScanningEduardo GuzmánNo ratings yet

- PIC18Document112 pagesPIC18Keshav Reddy100% (1)

- EECE416: Microcomputer Fundamentals and Design: PIC Instruction Set and Some Tips For ProgrammingDocument37 pagesEECE416: Microcomputer Fundamentals and Design: PIC Instruction Set and Some Tips For ProgrammingJagadish PalNo ratings yet

- V1000 DatasheetDocument12 pagesV1000 DatasheetHermanherdiantoNo ratings yet

- Architecture of 8085Document6 pagesArchitecture of 8085Ananda SaikiaNo ratings yet

- Registers 8051Document6 pagesRegisters 8051chanty chantyNo ratings yet

- Unit 1 MaDocument29 pagesUnit 1 MaEljameely JamaleldeenNo ratings yet

- Computers and Processors: Reference ManualDocument40 pagesComputers and Processors: Reference ManualbarryNo ratings yet

- Supporting Document For Assembly ProgrammingDocument7 pagesSupporting Document For Assembly ProgrammingJoginder YadavNo ratings yet

- Micro-Processors 8085: D.Arun KumarDocument52 pagesMicro-Processors 8085: D.Arun Kumarsrihari yandrapragadaNo ratings yet

- Architecture and Instruction SetDocument50 pagesArchitecture and Instruction SetVantharAlaNo ratings yet

- Microprocessor and Interfacing ECX 4236 PDFDocument37 pagesMicroprocessor and Interfacing ECX 4236 PDFDK White LionNo ratings yet

- Atmega328 - P Avr Mcu With Picopower Technology - Seleção RegisterDocument123 pagesAtmega328 - P Avr Mcu With Picopower Technology - Seleção RegisterclaudioandrevalverdeNo ratings yet

- 4) PIC IO Port ProgrammingDocument18 pages4) PIC IO Port ProgrammingArryshah Dahmia100% (2)

- Pic Microcontroller: Technological University of The PhilippinesDocument15 pagesPic Microcontroller: Technological University of The PhilippinesRonnel Joseph Cooper Renedo100% (1)

- GBCrib Sheet 000129Document4 pagesGBCrib Sheet 000129mistershrubberNo ratings yet

- Designing Embedded Systems With 8bit Microcontrollers-8051Document34 pagesDesigning Embedded Systems With 8bit Microcontrollers-8051Nyein NyeinNo ratings yet

- LG192641 Sflyh6vDocument20 pagesLG192641 Sflyh6vPunchis PanchisNo ratings yet

- FusesDocument8 pagesFusesLugo Aldair Cobeñas PereyraNo ratings yet

- 4 Experiment 4 Interrupt and I/O InterfacingDocument17 pages4 Experiment 4 Interrupt and I/O InterfacingSuhas NipaneNo ratings yet

- Unit 4Document108 pagesUnit 4Rasool NayabNo ratings yet

- Instrucciones PicDocument15 pagesInstrucciones PicRodrigo NolascoNo ratings yet

- (A) Suppose The Main Memory of The Pep8 Were Completely Filled WithDocument8 pages(A) Suppose The Main Memory of The Pep8 Were Completely Filled WithJackNo ratings yet

- 8051 Learning BoardDocument6 pages8051 Learning BoardEmin KültürelNo ratings yet

- ARM Teaching MaterialDocument33 pagesARM Teaching MaterialVishal NairNo ratings yet

- 04 AVR ALU and SREG SetDocument12 pages04 AVR ALU and SREG SetDerbendeNo ratings yet

- Pic Instruction SetDocument7 pagesPic Instruction Setdavid.mort6889No ratings yet

- F 818Document9 pagesF 818Eric YangNo ratings yet

- 7 PIC18 InstructionSet Assembly Machine PDFDocument15 pages7 PIC18 InstructionSet Assembly Machine PDFbaseer khanNo ratings yet

- The One With I - o Port ProgrammingDocument33 pagesThe One With I - o Port Programmingyug varshneyNo ratings yet

- 1670 Petra UMA MB-Aspire V5-531 V5-571-11324Document103 pages1670 Petra UMA MB-Aspire V5-531 V5-571-11324juan carlosNo ratings yet

- Veo Usb 2.0 Camera Driver: Click Here To DownloadDocument3 pagesVeo Usb 2.0 Camera Driver: Click Here To DownloadZdravko PeranNo ratings yet

- Splitter LogDocument1 pageSplitter LogBRAYAN HUMBERTO SALAMANCA TOVARNo ratings yet

- OPCOM3500E PresentationDocument44 pagesOPCOM3500E PresentationWilliam BlackNo ratings yet

- Fire Control PanelDocument2 pagesFire Control PanelBrillyanNo ratings yet

- Helm PCB - 8088 ComputerDocument9 pagesHelm PCB - 8088 ComputerGabriela FrederickNo ratings yet

- 8-Bit Microcontroller With 8K Bytes In-System Programmable Flash Atmega48/V Atmega88/V Atmega168/V PreliminaryDocument33 pages8-Bit Microcontroller With 8K Bytes In-System Programmable Flash Atmega48/V Atmega88/V Atmega168/V PreliminaryRubén Pérez ArmasNo ratings yet

- Micro MartDocument116 pagesMicro Marttenebris_obortisNo ratings yet

- Architecture of A Computer SystemDocument6 pagesArchitecture of A Computer SystemJohn VibarNo ratings yet

- New Surface ProDocument2 pagesNew Surface Proarjun2014No ratings yet

- UNIT 4 Digital Integrated CircuitsDocument161 pagesUNIT 4 Digital Integrated CircuitssimhadriNo ratings yet

- CSE1000M Training DocumentsDocument204 pagesCSE1000M Training Documentssalemail100% (1)

- UMA Schematics Document Storm 2: Wistron Corporation Wistron Corporation Wistron CorporationDocument102 pagesUMA Schematics Document Storm 2: Wistron Corporation Wistron Corporation Wistron Corporationamier jrsNo ratings yet

- Konica Minolta 1600f DTS LFF3 4 enDocument168 pagesKonica Minolta 1600f DTS LFF3 4 enMurat Harun Kılıç100% (1)

- Block Diagram 2404908Document1 pageBlock Diagram 2404908sinedla Fernández BermúdezNo ratings yet

- Red Hat Virtualization-4.4-Planning and Prerequisites Guide-En-UsDocument38 pagesRed Hat Virtualization-4.4-Planning and Prerequisites Guide-En-UsAnoopNo ratings yet

- Computer Science CS SAIL MTT ExamDocument5 pagesComputer Science CS SAIL MTT ExamsovitNo ratings yet

- LogDocument62 pagesLogShela DiahNo ratings yet

- Microprocessors and Microcontrollers Lab: Title: ComponentsDocument8 pagesMicroprocessors and Microcontrollers Lab: Title: ComponentsGhulam E Muhammad UsmanNo ratings yet

- Osw 1x8 Multi Channel Rotary Optical Switch Data Sheet 550401Document9 pagesOsw 1x8 Multi Channel Rotary Optical Switch Data Sheet 550401GLsun MallNo ratings yet

- Here, We Study Computer OrganizationDocument37 pagesHere, We Study Computer Organizationvijay rajNo ratings yet

- Tutorial 2 - 3Document2 pagesTutorial 2 - 3Ahan TejaswiNo ratings yet

- Powershot Sx740 Hs Firmware Update Procedures: - EnglishDocument4 pagesPowershot Sx740 Hs Firmware Update Procedures: - EnglishVG GalloNo ratings yet

- PS2 HackingDocument10 pagesPS2 HackingvadivelanNo ratings yet

- MAME RetroPie - RetroPie-Setup WikiDocument4 pagesMAME RetroPie - RetroPie-Setup WikiBobbyNo ratings yet

- Assignement IVDocument1 pageAssignement IVChirag Don JohnsonNo ratings yet