Professional Documents

Culture Documents

Part 2

Uploaded by

bmbsnpOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Part 2

Uploaded by

bmbsnpCopyright:

Available Formats

1.

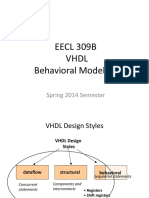

4 Modeling in VHDL

There are two main types of modeling in VHDL which are: 1.4.1 Behavioral Modeling Sequential statements are executed in sequence. Changing the order of the statements will change the outcome, but concurrent statements are executed based on the flow of signal values. Changing the order of the statements will not change the outcome. A comparison between sequential and concurrent modeling is shown in the following example: Concurrent Entity XNOR2 is Port (A, B:in std_logic; Z: out std_logic); End XNOR2; Architecture concurrent of XNOR2 is -- signal declaration (of internal -- signals X, Y) Signal X, Y: std_logic; Begin X <=A and B; Y <= ( not A) and (not B); Z <= X or Y; End concurrent; Sequential Entity XNOR2 is Port (A, B: in std_logic; Z: out std_logic); End XNOR2; Architecture sequential of XNOR2 is Begin XNOR2 : Process (A,B) Begin If ((A = '0' and B= '0') I (A = '1' and B= '1')) then Z<= '1 ; Else Z <='0'; End if; End process xNOR2; End sequential;

1.4.1.1 Sequential Modeling The Process is the basis for sequential modeling, a process uses sequential statements to describe the behavior of a system over time, and the syntax for a process statement is as follows: [Process label]: Process [(Signal sensitivity list)] [is] [Process declarations] Begin List of sequential statements such as: Signal assignments - variable assignments - Case statements - exit statements - if statements - Loop statements - next statements - null statements - Wait statements - procedure calls End process [process label]

A process is declared within architecture and is a concurrent statement; however the statements inside a process are executed sequentially. The sensitivity list is a set of signals to which the process is sensitive. Any change in the value of the signals in the sensitivity list will cause immediate execution of the process. Variables and constants that are used inside a process must be defined in the process declarations part before the keyword begin, variable assignments inside a process are executed immediately and denoted by the ":=" operator, while Signal assignments are denoted by "<=" and changes occur after a delay. If Statements The If statement executes a sequence of statements depending on one or more conditions, the syntax is as follows: If condition then Sequential statements [Elsif condition then Sequential statements] [Else Sequential statements] End if; The if statement is performed by checking each condition in the order they are presented until a "true" is found, this statement must be inside a process construct. Is often used to implement Finite State Machines ( FSM ) . Example Entity MUX_4_1a is Port (S1, S0, A, B, C, D: in std_logic; Z: out std_logic); End MUX_4_1a; Architecture ALGORITHMIC_IF of MUX_4_1a is Begin P1 : Process (S1, S0, A, B, C, D) Begin If S1='0' and S0='0' then Z <= A; Elsif S1='0' and S0='1' then Z <= B; Elsif S1='1' and S0='0' then Z <= C; Elsif S1= ' 1 ' and S0= ' 1 ' then Z <= D; End if; End process P1; End ALGORITHMIC_IF;

Case Statement The case statement executes one of several sequences of statements, based on the value of a single expression, the syntax is as follows: Case expression is When choices => Sequential statements When choices => Sequential statements [When others => Sequential statements ) End case; The case statement evaluates the expression and compares the value to each of the choices, the when clause corresponding to the matching choice will have its statements executed, there is no two choices can overlap (i.e. each choice can be covered only once). If the "when others" choice is not present, all possible values of the expression must be covered by the set of choices. loop Statements The loop statements are used to repeatedly execute a sequence of sequential statements, iteration schemes defined by the VHDL: Basic-loop While-Loop For-Loop [loop label:] Iteration scheme loop Wait Statement Sequential statements [Next [label] [when condition]; [Exit [label] [when condition]; End loop [loop_label]; This loop has no iteration scheme. It will be executed continuously until it encounters an exit or next statement, the basic loop (as well as the while-loop) must have at least one wait statement. The next statement terminates the rest of the current loop iteration and execution will proceed to the next loop iteration, while the exit statement skips the rest of the statements, terminating the loop entirely, and continues with the next statement after the exited loop. Example entity COUNT31 is Port (CLK : in std_logic; COUNT : out integer); End COUNT31;

Architecture AlGORITHMIC_B_lOOP of COUNT31 is Begin P_COUNT: process Variable intern_value: integer :=0; Begin COUNT<= intern_value; loop Wait until CLK='1'; intern_value := (intern_value + 1) mod 32; COUNT<= intern_value; End loop; End process P_COUNT; End ALGORITHMIC_B_lOOP; A wait statement has been included so that loop will execute every time the clock changes from '0' to '1', then we defined a variable intern_value inside the process because output ports cannot be read inside the process. While-Loop Statement The while-loop evaluates a Boolean iteration condition. When condition is TRUE ,the loop repeats, otherwise the loop is skipped and the execution will halt, the syntax is as follows: [Loop label:] While condition loop Wait Statement Sequential statements [Next [label] [when condition]; [Exit [label] [when condition]; End loop [loop label]; The condition of the loop is tested before each iteration, including the first iteration. If it is false, the loop is terminated, For-loop Statement The for-loop uses an integer iteration scheme that determines the number of iterations, the syntax is as follows: [loop label:] for identifier in range loop sequential statements [Next [label] [when condition]; [Exit [label] [when condition]; End loop [loop_label]; The value of the identifier can only be read inside the loop and is not available outside its loop, the range must be a computable integer range in one of the following forms: integer_expression to integer_expression , integer_expression downto integer_expression

You might also like

- BE EXPERT IN JAVA Part- 2: Learn Java programming and become expertFrom EverandBE EXPERT IN JAVA Part- 2: Learn Java programming and become expertNo ratings yet

- VHDL TutorialDocument22 pagesVHDL TutorialAracely ChicoNo ratings yet

- EECL 309B VHDL Behavioral Modeling: Spring 2014 SemesterDocument55 pagesEECL 309B VHDL Behavioral Modeling: Spring 2014 SemesterDan M StoneNo ratings yet

- 8 9behDocument24 pages8 9behKaniniAnbazhaganNo ratings yet

- VHDL StatementsDocument30 pagesVHDL StatementsEr Deepak GargNo ratings yet

- Sequential VHDL StatementsDocument15 pagesSequential VHDL StatementsChutiyaNo ratings yet

- Digital Design Using VHDL: Using Xilinx'S Tool For Synthesis and Modelsim For Verification Part (Iii)Document20 pagesDigital Design Using VHDL: Using Xilinx'S Tool For Synthesis and Modelsim For Verification Part (Iii)Rakesh Kumar DNo ratings yet

- C Language Ch2Document21 pagesC Language Ch2mihirbhuva1No ratings yet

- VHDL 1 AniruddhaDocument29 pagesVHDL 1 AniruddhaHussein A. AlsameeNo ratings yet

- Lab7 - Behavioral Modeling and Timing ConstraintsDocument6 pagesLab7 - Behavioral Modeling and Timing Constraintswert1a2No ratings yet

- Experiment 6 Title: Compose and Simulate VHDL Code For The Following Sequential Elements and CircuitsDocument5 pagesExperiment 6 Title: Compose and Simulate VHDL Code For The Following Sequential Elements and CircuitsVidya SagvekarNo ratings yet

- Unit-2 Question and AnsweresDocument23 pagesUnit-2 Question and Answeresmallajasmitha7No ratings yet

- Operators and Statements in VHDLDocument24 pagesOperators and Statements in VHDLpatilojas16No ratings yet

- VHDL StatementsDocument34 pagesVHDL StatementsP. VENKATESHWARINo ratings yet

- Ch01 (PDF Library)Document10 pagesCh01 (PDF Library)Baba AkbarNo ratings yet

- VHDL ControlDocument18 pagesVHDL ControljajaNo ratings yet

- QA Unit2Document16 pagesQA Unit2alysonmicheaalaNo ratings yet

- CC317-Spring 22-Lec 10Document24 pagesCC317-Spring 22-Lec 10reem mohamedNo ratings yet

- C++ ChaDocument15 pagesC++ ChaYE' JEMBRU Lige EshetuNo ratings yet

- MODULE 2Document6 pagesMODULE 2lijin bNo ratings yet

- ADE Lecture5Document39 pagesADE Lecture5mohammedNo ratings yet

- Modern Programming Tools and Techniques-I: Lecture 4: Control StructuresDocument38 pagesModern Programming Tools and Techniques-I: Lecture 4: Control StructuresVinay PrakashNo ratings yet

- ConstructsDocument22 pagesConstructsOumaymaNo ratings yet

- C++ Conditional Statements: Prepared By: Engr. Yolly D. AustriaDocument14 pagesC++ Conditional Statements: Prepared By: Engr. Yolly D. AustriaMelissaTaanNo ratings yet

- Modern Programming Tools and Techniques-I: Lecture 4: Control StructuresDocument43 pagesModern Programming Tools and Techniques-I: Lecture 4: Control StructuresMachipeddi RajeshNo ratings yet

- Control Structure CDocument12 pagesControl Structure CagasyabutoliaNo ratings yet

- Unit I HDL DesignDocument81 pagesUnit I HDL DesignvinodNo ratings yet

- Drill 5Document13 pagesDrill 5Ash LeeNo ratings yet

- Lesson 7:control FlowDocument17 pagesLesson 7:control FlowhoaNo ratings yet

- Vlsi Chapter3 FinishDocument10 pagesVlsi Chapter3 FinishDinesh PalavalasaNo ratings yet

- Control StructuresDocument34 pagesControl StructuresVISHNU SHANKAR SINGHNo ratings yet

- LoopsDocument14 pagesLoopskavyaNo ratings yet

- VHDL Notes PDFDocument10 pagesVHDL Notes PDFUlises Castro Olvera100% (1)

- VHDL SEQUENTIAL STATEMENTSDocument5 pagesVHDL SEQUENTIAL STATEMENTSjaskirat_salujaNo ratings yet

- JONATHANBATMANDocument8 pagesJONATHANBATMANJonathan BedeshiNo ratings yet

- SSC06 2004 eDocument41 pagesSSC06 2004 eDragosFlorinLismanNo ratings yet

- VHDL Cookbook 4Document7 pagesVHDL Cookbook 4Charbel TadrosNo ratings yet

- Switch Statement in CDocument3 pagesSwitch Statement in CJiNo ratings yet

- VHDL Combinational CircuitsDocument24 pagesVHDL Combinational CircuitsAmru_NNo ratings yet

- Introduction To Processes: Dr. Yann-Hang Lee GWC 224 Yhlee@asu - EduDocument19 pagesIntroduction To Processes: Dr. Yann-Hang Lee GWC 224 Yhlee@asu - EduChutiyaNo ratings yet

- C SyntaxrulesDocument5 pagesC SyntaxrulesHanif PayandehNo ratings yet

- C Programming UNIT 3.1 LoopsDocument32 pagesC Programming UNIT 3.1 LoopsrishikaNo ratings yet

- Java Fundamentals For Android DevelopmentDocument17 pagesJava Fundamentals For Android DevelopmentRajatKumarNo ratings yet

- VHDL and Processes: Defining Sequential Circuit BehaviorDocument30 pagesVHDL and Processes: Defining Sequential Circuit Behaviorcsazeredo_2010No ratings yet

- C Prog. Assignment 1 and 2 CombinedDocument14 pagesC Prog. Assignment 1 and 2 Combinedweiner1No ratings yet

- Flow Control, Exceptions and AssertionsDocument41 pagesFlow Control, Exceptions and AssertionsManuel GalganaNo ratings yet

- Control StructuresDocument7 pagesControl StructuresGagan BansalNo ratings yet

- Verilog Interview QuestionsDocument39 pagesVerilog Interview QuestionsV SharmaNo ratings yet

- Vlsi Chapter3 FinishDocument14 pagesVlsi Chapter3 FinishDinesh PalavalasaNo ratings yet

- Programming in Java: Topic: Control Flow StatementsDocument32 pagesProgramming in Java: Topic: Control Flow StatementssohamNo ratings yet

- Coe133l Drill-5 Behavioral ModelingDocument15 pagesCoe133l Drill-5 Behavioral ModelingLesterNo ratings yet

- Pps Notes Set1Document33 pagesPps Notes Set1Saloni MaggoNo ratings yet

- Programing In: ShrabantiDocument29 pagesPrograming In: ShrabantiKing RickNo ratings yet

- C Programming 2Document5 pagesC Programming 2SANJIB BEJNo ratings yet

- Programming Using C++: Presented By: Abhishek SharmaDocument25 pagesProgramming Using C++: Presented By: Abhishek SharmaAbhishek SharmaNo ratings yet

- Behav FinDocument55 pagesBehav Finflampard24No ratings yet

- Unit 2 VHDLDocument55 pagesUnit 2 VHDLசெல்வம் முத்துராமன்No ratings yet

- Module 5Document47 pagesModule 5Dr. Madhumathy PNo ratings yet

- Sequential and Concurrent Statements in The VHDL LanguageDocument41 pagesSequential and Concurrent Statements in The VHDL LanguageRobinJamesPayyappillilNo ratings yet

- Banking AwarenessDocument41 pagesBanking AwarenessApeksha Rajoriya100% (1)

- Static G.K. Tornado AVIKDocument45 pagesStatic G.K. Tornado AVIKdassreerenjiniNo ratings yet

- One WordDocument15 pagesOne WordVamshi KrishnaNo ratings yet

- Introduction To Accounting: ContentsDocument251 pagesIntroduction To Accounting: ContentsJaya Bala ChandranNo ratings yet

- Bank Not of UK, Telangana Charitra, Telangana Coins, Telangana Language, Indian Banknote, Musham Damodhar, Banknotes Auction, Ancient Coins Auction, Bank of Bengal Half Notes AuctionDocument16 pagesBank Not of UK, Telangana Charitra, Telangana Coins, Telangana Language, Indian Banknote, Musham Damodhar, Banknotes Auction, Ancient Coins Auction, Bank of Bengal Half Notes Auctionmusham9No ratings yet

- Platinum Points For IBPS clerk-IV PDFDocument22 pagesPlatinum Points For IBPS clerk-IV PDFAniruddha SahasrabuddheNo ratings yet

- Sbi Assistant Clerk Notification 2014Document5 pagesSbi Assistant Clerk Notification 2014Telugu VaahiniNo ratings yet

- Bank NotesDocument68 pagesBank NotesbmbsnpNo ratings yet

- Banking TerminologyDocument8 pagesBanking TerminologybmbsnpNo ratings yet

- Sbi ADocument5 pagesSbi AJeshiNo ratings yet

- Interview TipsDocument11 pagesInterview TipsIkshvaku KansaraNo ratings yet

- Cenpeid Leaflet 1Document4 pagesCenpeid Leaflet 1bmbsnpNo ratings yet

- Sbi Assistant Clerk Notification 2014Document5 pagesSbi Assistant Clerk Notification 2014Telugu VaahiniNo ratings yet

- 1.4.1.2 Concurrent StatementsDocument3 pages1.4.1.2 Concurrent StatementsbmbsnpNo ratings yet

- Introduction To Electrical Drives: Figure 1 Conventional Variable Speed Electrical Drive SystemDocument19 pagesIntroduction To Electrical Drives: Figure 1 Conventional Variable Speed Electrical Drive SystemChakradhara TheppavariNo ratings yet

- Syllabus CWCDocument5 pagesSyllabus CWCDowlath BashaNo ratings yet

- Part 6Document5 pagesPart 6bmbsnpNo ratings yet

- III. Fast Fourier Transform: Digital Signal Processing - 3Document17 pagesIII. Fast Fourier Transform: Digital Signal Processing - 3Sathish BalaNo ratings yet

- JK Lecture Notes On Electric Power SystemsDocument80 pagesJK Lecture Notes On Electric Power Systemstabibujuha84100% (6)

- VHDL NotesDocument14 pagesVHDL Notesumang_1010100% (2)

- Part 1Document3 pagesPart 1bmbsnpNo ratings yet

- Binomial Formulas: Definition of Factorial NumbersDocument2 pagesBinomial Formulas: Definition of Factorial NumbersbmbsnpNo ratings yet

- 2.1 Combinational Circuit Desion ExampleDocument2 pages2.1 Combinational Circuit Desion ExamplebmbsnpNo ratings yet

- Part 4Document5 pagesPart 4bmbsnpNo ratings yet

- Coordinate GeometryDocument78 pagesCoordinate Geometrybmbsnp100% (1)

- Wall MartDocument22 pagesWall MartbmbsnpNo ratings yet

- IQBots Introduction Assessment3Document2 pagesIQBots Introduction Assessment3fjgutierrezpa63% (8)

- Effective Pandas. Patterns For Data Manipulation (Treading On Python) - Matt Harrison - Independently Published (2021)Document392 pagesEffective Pandas. Patterns For Data Manipulation (Treading On Python) - Matt Harrison - Independently Published (2021)Anonymous dTrW1iA100% (4)

- Inheritance JavaDocument10 pagesInheritance Javaujjwol100% (1)

- InstallingJDFJMF3 0Document33 pagesInstallingJDFJMF3 0liaDownloadNo ratings yet

- How Control Korg Krome With An External Midi ControllerDocument8 pagesHow Control Korg Krome With An External Midi ControllerY FelixNo ratings yet

- Integrating Usability Engineering and Agile Software Development A Literature ReviewDocument8 pagesIntegrating Usability Engineering and Agile Software Development A Literature ReviewafdtukasgNo ratings yet

- Agile Maturity ModelDocument27 pagesAgile Maturity ModelfredcyrilNo ratings yet

- 02-Steps To Analyze AWR Report in OracleDocument8 pages02-Steps To Analyze AWR Report in OracleAnonymous 8RhRm6Eo7hNo ratings yet

- Upgrading The Time Zone File Version After Upgrading Oracle DatabasesDocument6 pagesUpgrading The Time Zone File Version After Upgrading Oracle DatabasesNishan KathNo ratings yet

- En Fpba 01 Um G A4Document196 pagesEn Fpba 01 Um G A4Jitendra AnneNo ratings yet

- An 96017Document21 pagesAn 96017Victor Hugo Zamalloa BarreraNo ratings yet

- What Are Some Good Book For SAP ABAP Programing As A Beginner - QuoraDocument2 pagesWhat Are Some Good Book For SAP ABAP Programing As A Beginner - QuorafiestamixNo ratings yet

- Nortel CMDDocument1,054 pagesNortel CMDbarone_28No ratings yet

- Avr 2807Document130 pagesAvr 2807bechaseNo ratings yet

- Oracle Lab 4Document4 pagesOracle Lab 4Khanh TranNo ratings yet

- 2018 Snote 2581369 - Vat Ksa and Uae Imports Process Ksa April 2018Document27 pages2018 Snote 2581369 - Vat Ksa and Uae Imports Process Ksa April 2018prasad kkavNo ratings yet

- Search Algorithm PDFDocument59 pagesSearch Algorithm PDFNguyen Minh DaoNo ratings yet

- PDF CycloneII DatasheetDocument110 pagesPDF CycloneII DatasheetSatvik HardatNo ratings yet

- 099 DefectDocument11 pages099 DefectKumud TembhareNo ratings yet

- Vendor Wira Makmur PratamaDocument1 pageVendor Wira Makmur PratamaferyNo ratings yet

- Transport Layer STDDocument8 pagesTransport Layer STDMd Habibur RahmanNo ratings yet

- Anudnya ResumeDocument2 pagesAnudnya Resumeanudnya44No ratings yet

- Laboratory Journal: Signal Coding Estimation TheoryDocument63 pagesLaboratory Journal: Signal Coding Estimation Theoryrudra_1No ratings yet

- Rot Op Robe ExDocument2 pagesRot Op Robe ExSiva KumarNo ratings yet

- Proposal Smart Lifestyle ProjectDocument7 pagesProposal Smart Lifestyle ProjectFaiz YunNo ratings yet

- Fitzpatrick's Color Atlas and Synopsis of Clinical DermatologyDocument1 pageFitzpatrick's Color Atlas and Synopsis of Clinical DermatologyFadhillaFitriAmi0% (1)

- HCIA-WLAN V2.0 Training PDFDocument24 pagesHCIA-WLAN V2.0 Training PDFandreu cerdan50% (2)

- Blue Toot 1Document25 pagesBlue Toot 1shanin2006No ratings yet

- 4.3RISE PCE CAA Connectivity - Options - Wave4Document17 pages4.3RISE PCE CAA Connectivity - Options - Wave4Islam El SemmaryNo ratings yet

- Immulite 1000Document2 pagesImmulite 1000أبو عبد الله المصريNo ratings yet