Professional Documents

Culture Documents

A 6.6-kV Transformerless STATCOM

Uploaded by

manish_chaturvedi_6Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A 6.6-kV Transformerless STATCOM

Uploaded by

manish_chaturvedi_6Copyright:

Available Formats

A 6.

6-kV Transformerless STATCOM Based on a

Five-Level Diode-Clamped PWM Converter:

System Design and Experimentation of a

200-V, 10-kVA Laboratory Model

Hirofumi Akagi, Fellow, IEEE, Hideaki Fujita, Member, IEEE, Shinsuke Yonetani, and Yosuke Kondo

Department of Electrical and Electronic Engineering

Tokyo Institute of Technology

E-mail: akagi@ee.titech.ac.jp

AbstractThis paper discusses a potential of a transformerless

STATCOM (STATic synchronous COMpensator) intended for

installation on the 6.6-kV industrial and utility distribution

systems. The STATCOM consists of a ve-level diode-clamped

PWM converter rated at 1 MVA, and a voltage-balancing circuit

rated at 6 kVA. Moreover, this paper designs, constructs, and

tests a 200-V 10-kVA STATCOM based on a ve-level converter

with a carrier frequency of 3 kHz and a voltage-balancing circuit

with a switching frequency of 3 kHz. The STATCOM and its

experimental waveforms verify the viability and effectiveness of

the 6.6-kV transformerless STATCOM.

I. INTRODUCTION

Since the three-level neutral-point-clamped, or diode-

clamped, converter was invented in 1980 [1], comprehensive

research has been achieved on the three-level converter and its

expansion to multilevel converters, along with their applica-

tions to industry and utility [2], [3]. Among them, three-level

diode-clamped converters have been put into practical use,

for example, steel mill drives, traction drives for the Japanese

bullet train or the so-called Shinkansen, the 160-MVA UPFC

(unied power ow controller) in the USA, and so on.

As for four-level, ve-level or seven-level diode-clamped

converters [4]-[10], however, few application has been reported

in spite of continuous efforts of power electronics researchers

and engineers. A simple reason seems to be that no one has

found out reasonable applications of four-level or ve-level

converters in terms of cost and performance. In the 1990s,

the 6.6-kV ve-level converter was intended to use the 4.5-kV

GTO (gate-turn-off) thyristor that was only the 4.5-kV power

switching device available on the market. However, the 4.5-kV

GTO thyristor imposed limitations on switching frequencies

up to 200 Hz from a practical point of view.

Recently, signicant progress has been made in power

semiconductor technology, thus resulting in emergence of

the 4.5-kV IGBT (insulated-gate bipolar transistor) and the

fth-generation 1.2-kV IGBT. Both are available from the

market at present. Sasagawa, et. al., have proposed a simple

and reliable gate-drive circuit capable of voltage balancing

of IGBTs connected in series [11]. This gate-drive circuit

enables to replace a single 4.5-kV IGBT by a string of four

general-purpose 1.2-kV IGBTs connected in series. This may

bring a signicant increase in switching frequency to the 6.6-

kV ve-level converter. These developments in power devices

and circuits including the gate-drive circuit will help to apply

the 6.6-kV transformerless ve-level converter to industry and

utility in the near future.

This paper describes a design concept of a transformerless

STATCOM intended for installation on the 6.6-kV industrial

and utility distribution systems. It is followed by designing,

constructing, and testing of a 200-V 10-kVA STATCOM con-

sisting of a ve-level diode-clamped converter with a carrier

frequency of 3 kHz and two bi-directional buck-boost choppers

with a switching frequency of 3 kHz. Experimental waveforms

show that the STATCOM can control a reactive power rated at

10 kVA from lagging to leading (or leading to lagging) within

20 ms, keeping the four capacitor voltages balanced well, even

during the transient state.

II. DESIGN CONCEPT OF THE 6.6-KV STATCOM

A. The 6.6-kV Five-Level Diode-Clamped PWM Converter

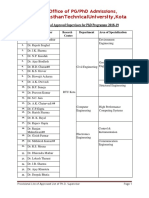

Fig. 1 shows the circuit conguration of the 6.6-kV trans-

formerless STATCOM consisting of a ve-level diode-clamped

converter rated at 1 MVA and a voltage-balancing circuit rated

at 6 kVA. Each IGBT symbol represents either a single 4.5-

kV IGBT or a string of four 1.2-kV IGBTs connected in

series. Each clamping-diode symbol represents a single 4.5-kV

device. Note that actual switching frequencies of the IGBTs

range from 500 to 1,000 Hz although a carrier frequency for

PWM is kept constant as 3 kHz.

When one tries to design the 6.6-kV 1-MVA STATCOM

without transformer, the STATCOM requires a medium-

voltage power converter that can be directly connected to

the 6.6-kV industrial or utility grid. Since the maximum

voltage of the line-to-line voltage reaches 10-kV, the dc-link

voltage of the power converter equipped with an 10% ac-link

inductor per phase should be designed as 12 kV to guarantee

satisfactory current-control performance. The ac-link inductor

is mandatory for supporting a difference in instantaneous

voltage between the grid and the ac terminals of the converter.

IAS 2005 557 0-7803-9208-6/05/$20.00 2005 IEEE

6.6 kV

6 kV

M

P1

N1

6 kV

Voltage-balancing

circuit

Fig. 1. The 6.6-kV transformer-less STATCOM using a ve-level diode-

clamped PWM converter rated at 1 MVA and a voltage-balancing circuit rated

at 6 kVA.

Therefore, the converter requires a string of eight 4.5-kV

IGBTs per leg to withstand the dc-link voltage as high as

12 kV. This justies the use of a three-level or ve-level diode-

clamped converter taking the place of a conventional two-level

converter.

The ve-level converter produces less line harmonic cur-

rents and less EMI (electro-magnetic interference) emissions

than the three-level converter does. However, the ve-level

converter pays the penalty of requiring additional clamping

diodes and dc capacitors. The additional clamping diodes

are accompanied by increased device and assembly costs.

The additional dc capacitors make voltage balancing more

complicated. The increased costs may be absorbed or canceled

out by superior performance in terms of harmonics and EMI.

B. Voltage Balancing of the Four DC Capacitors

When a current including a dc component ows into, or out

of, one of three nodes P1, N1 and M of the four dc capacitors

connected in series, voltage imbalance occurs between the

corresponding two capacitors. The ve-level converter causes

an ac-voltage uctuation with a frequency of 150 Hz (=

50 Hz 3) to each of the four dc capacitors. This voltage

uctuation is inherent in the ve-level converter. Therefore,

an appropriate design of the four dc capacitors may reduce

it to an acceptable level. The voltage imbalance discussed in

this paper means a dc-voltage deviation from one-fourth of the

rated dc-link voltage.

Existing solutions to the voltage imbalance can be classied

into the following two ways: One is to install a voltage-

balancing circuit on the dc side of the converter [4], and the

50Hz

L

AC

200V

i

S

e

S

e

S i

S

e

L

CP

L

CN

i

CP

i

CN

i

P1

i

M

P1

M

N1

N2

P2

Voltage-balancing

circuit

A/D PLL

A/D

(DSP)

Calculation

(FPGA)

PWM

v

P2P1

v

P1M

v

MN1

v

N1N2

q

4V

dc

T1

T2

T3

T4

T5

T6

T7

T8

DC

CT

PT

Fig. 2. The 200-V 10-kVA laboratory STATCOM.

TABLE I

CIRCUIT PARAMETERS OF THE 200-V 10-KVA STATCOM.

Inductance of ac-link inductor L

AC

1.2 mH (9.5% )

Resistance of ac-link inductor R

AC

2 m (0.5 % )

DC capacitor voltage V

dc

100 V

Capacitance of dc capacitor C

dc

6,600 F

DC-link voltage 4V

dc

400 V

Unit capacitance constant H 13 ms

Chopper inductor L

CP

=L

CN

110 mH (0.3 A)

Carrier frequency f

C

3 kHz

on a three-phase, 50-Hz, 200-V, 10-kVA base

other is to introduce a sophisticated PWM method capable of

controlling reactive power, regulating the dc-link voltage, and

balancing the four dc capacitor voltages simultaneously [2],

[7]. The latter is denitely preferable to the former in terms

of cost. As for the latter, however, voltage balancing would

inuence reactive-power control if the priority were given to

voltage balancing. Moreover, a medium-voltage power con-

verter intended for installation on a utility grid is required to

be more reliable and more robust against line faults, transients,

and disturbances.

From these considerations, the authors decide to combine a

PWM method capable of voltage balancing of the mid-point

node M with a voltage-balancing circuit for the positive and

negative nodes P1 and N1. Hence, the ve-level converter can

devote itself mainly to meeting a demand of reactive power,

and complementarily to regulating both the dc-link voltage and

the mid-point voltage.

III. EXPERIMENTAL SYSTEM CONFIGURATION

Fig. 2 shows the 200-V 10-kVA STATCOM designed,

constructed, and tested in this paper. No switching-ripple lter

is installed upstream of the ac-link inductor L

AC

. The control

IAS 2005 558 0-7803-9208-6/05/$20.00 2005 IEEE

v

P2N2

v

P2M

v

MN2

v

P2P1

v

P1M

v

MN1

v

N1N2

P2

P1

M

N1

N2

Fig. 3. The dc-link voltage and capacitor voltages.

V

P2M

V

P1M

0

V

N1M

V

N2M

e

Fig. 4. The reference signal and four carrier signals for sine-triangle PWM.

system of the ve-level converter is independent of that of the

voltage-balancing circuit consisting of two bi-directional buck-

boost choppers. Fig. 3 shows the dc-link voltage v

P2N2

, or

the voltage of P2 with respect to N2, and the four dc capacitor

voltages, along with ve nodes, P2, P1, M, N1 and N2.

Table I summarizes the circuit parameters of the experimen-

tal system. Each IGBT integrated with a free-wheeling diode,

and each clamping diode have the same ratings as 600 V and

100 A. The unit capacitance constant [12], given in Table I,

H is useful and effective in associating a total capacitance

value of the four series-connected dc capacitors with its dc-link

voltage. It is dened as a ratio between the capacitor-stored

energy in joules or [J] and the power conversion capacity in

watts or [W]. In general, H ranges from 1 to 20 ms, and it

is determined, taking into account various factors including

the objective, voltage class, system conguration, and power

circuit of a STATCOM being installed. Considering that the

transformerless STATCOM based on the ve-level diode-

clamped converter is intended for direct installation on the

6.6-kV utility and industrial power distribution systems, the

authors have selected each of the four dc capacitors connected

in series as C

dc

= 6, 600 F, and so the unit capacitance

constant is 13 ms. This value may be slightly higher than that

in a conventional STATCOM.

Fig. 4 shows four carrier signals with the same frequency

as 3 kHz, and a voltage reference signal e

, to achieve pulse-

width modulation (PWM). Note that the four triangle-carrier

signals have the same amplitude and phase, and their dc levels

are shifted appropriately.

IV. ANALYSIS OF DC MEAN CURRENTS FLOWING INTO

THREE NODES P1, N1 AND M

When even a small amount of dc current continues owing

into one of the nodes P1, N1 and M in a ve-level converter

with neither voltage-balancing circuit nor control, dc-voltage

e

D

: D

P1

: D

M

0 2V

dc

V

dc

V

dc

2V

dc

1

Fig. 5. Output voltage e

and duty factor D.

imbalance occurs between the corresponding capacitors. This

section conducts theoretical analysis of dc mean currents

i

P1

and

i

M

, considering the symmetry of

i

P1

and

i

N1

.

A. Voltage reference and duty factors

Fig. 5 shows relations between a voltage reference e

of a

ve-level converter, and duty factors D

P1

and D

M

[13]. Each

duty factor represents a ratio of a time interval, during which

the source current i

S

ows into each node, with respect to a

line cycle of 20 ms. Thus, the product of each duty factor and

the source current results in an instantaneous current owing

into each node. The duty factors D

P1

and D

M

are given as

follows:

D

P1

=

_

_

_

0 (V

N2M

e

< 0)

e

/V

P1M

(0 e

< V

P1M

)

2 e

/V

P1M

(V

P1M

e

V

P2M

)

(1)

D

M

=

_

_

0 (V

N2M

e

< V

N1M

)

1 +e

/V

MN1

(V

N1M

e

< 0)

1 e

/V

P1M

(0 e

< V

P1M

)

0 (V

P1M

e

V

P2M

)

(2)

B. The dc mean current owing into node P1

It is possible to derive dc mean currents owing into nodes

P1 and M,

i

P1

and

i

M

, assuming that the voltage reference

e

, and the source current i

S

are the following sinusoidal

waveforms.

e

=

2E sin t (3)

i

S

=

2I

S

sin(t +)

=

2I

Sd

sin t

2I

Sq

cos t (4)

The dc mean current

i

P1

in a steady state can be dened

as an average value of the instantaneous current owing into

the node P1, i

P1

over a line period of T = 20 ms. Therefore,

it is given by

i

P1

=

3

T

_

T

0

D

P1

i

S

dt =

6

T

_ T

4

0

D

P1

i

S

dt. (5)

The time at which

2E sin t is equal to V

P1M

is dened

as T

VP1M

T

VP1M

=

1

sin

1

_

V

P1M

2E

_

. (6)

IAS 2005 559 0-7803-9208-6/05/$20.00 2005 IEEE

When

2E V

P1M

1

,

i

P1

can be derived as

i

P1

=

6I

Sd

T

_

E

V

P2M

_

4T

VP1M

2 sin(2T

VP1M

)

} +2

2 cos(T

VP1M

)

_

(7)

It should be noted that I

Sq

is excluded from (7) although I

Sd

is included in (7). This means that no dc current ows into

node P1 as long as the ve-level converter is operated as an

ideal lossless STATCOM. This consideration from (7) agrees

with the statement in [10]. However, a small amount of dc

current ows in an actual STATCOM because the STATCOM

is accompanied by conducting and switching losses in the

converter, as well as copper and iron losses in L

AC

. The

200-V 10-kVA STATCOM produced a total loss of 340 W

(a measured value), when it was operated at a capacitor of

10 kVA. This implies that I

Sd

corresponds to 1.0 A. The rms

value of e

, E was measured to be 127 V. Substituting these

values into (7) leads to

i

P1

= 0.3 A, that is only 1% of the

rated current of 30 A. This dc current continues owing into

the node P1, thus resulting in dc-voltage imbalance between

the positive two capacitors. Hence, such a voltage-balancing

circuit is installed on the dc side of the converter, as shown in

Fig. 2. Note that the dc current of 0.3 A ows in the chopper

inductor L

CP

. The voltage-current rating of the chopper for

voltage balancing between the positive two capacitors is 30 VA

(=100 V 0.3 A). Since the identical chopper is required

for voltage balancing between the negative two capacitors, the

total voltage-current rating of the voltage-balancing circuit is

60 VA, that is only 0.6% of 10 kVA.

C. The dc mean current owing into node M

Like the above derivation of

i

P1

, the dc current owing into

node M,

i

M

can be derived as follows:

i

M

=

3

T

_

T

0

D

M

i

S

dt = 0. (8)

This equation means that no dc current ows in the node M,

independent of whether the ve-level converter draws either

active or reactive current from the ac mains. In an actual ve-

level converter, however, a small amount of dc current ows

into the node M because unavoidable imbalance and tuning

errors exist in both the power and control circuits. Hence,

this justies the authors to introduce an additional function of

voltage-balancing control to the ve-level converter, instead of

installing another buck-boost chopper on the dc side.

V. CONTROL OF THE FIVE-LEVEL CONVERTER

Fig. 6 shows the simplied block diagram of a control

circuit of the ve-level converter. It is a fully-digital control

circuit based on DSPs and FPGAs. Each data sampling of the

source voltage and current, and the four dc-capacitor voltages

is performed at every top or bottom of the carrier signals in

Fig. 4, and the voltage reference e

is renewed at the following

top or bottom with a time delay of 167 s.

1

Generally, the other operating condition of

2E < V

P1M

does not

exist in a STATCOM using the ve-level converter.

i

Su

i

Sv

i

Sw

e

Su

e

Sv

e

Sw

4V

dc

v

P2N2

e

Sd

e

Sq

i

Sd

i

Sq

q

Sd

i

Sq

e

d

e

q

e

u

e

v

e

w

v

MN2

v

P2M

v

M

+

d-q

d-q

trans.

trans.

K

dc

Cal. of

current

reference

Decoupled

current

control

Inv.

d-q

trans.

DC voltage controller

Voltage-balancing controller

PI

sin 6t

1

1+sT

Fig. 6. The control block diagram of the ve-level converter.

A. Decoupled current control

The following set of voltage and current equations can be

obtained from Fig. 2.

_

_

e

Su

e

Sv

e

Sw

_

_

_

_

e

u

e

v

e

w

_

_

=

_

R

AC

+L

AC

d

dt

_

_

_

i

Su

i

Sv

i

Sw

_

_

(9)

Invoking the - and d-q transformation yields

_

R

AC

L

AC

L

AC

R

AC

_ _

i

Sd

i

Sq

_

=

_

e

Sd

e

d

e

Sq

e

q

_

. (10)

Here, e

d

and e

q

are the d-axis and q-axis components corre-

sponding to the three-phase ac voltages of the converter, and

e

Sd

and e

Sq

are those corresponding to the three-phase source

voltages, respectively. Note that e

Sq

is always zero because

e

Su

is in alliance with the d-axis. The instantaneous real and

imaginary powers p and q, drawn by the converter, are given

as follows:

p = e

Sd

i

Sd

(11)

q = e

Sd

i

Sq

. (12)

The d-axis voltage reference e

d

and the q-axis voltage

reference e

q

of the converter are given by

_

e

d

e

q

_

=

_

e

Sd

0

_

_

R

AC

L

AC

L

AC

R

AC

_ _

i

Sd

i

Sq

_

K

IP

_

i

Sd

i

Sd

i

Sq

i

Sq

_

K

II

_ _

i

Sd

i

Sd

i

Sq

i

Sq

_

dt. (13)

Here, i

Sd

and i

Sq

are the reference currents on the d-axis

and q-axis, which are determined in the following subsection.

The rst and second terms of the right hand side in (13) are

introduced to cancel out the source voltage and the voltage

appearing across the ac-link inductor. The third and fourth

terms form a proportional plus integral controller with a

IAS 2005 560 0-7803-9208-6/05/$20.00 2005 IEEE

V

P2M

V

P1M

V

N1M

V

N2M

5ms

0

1

0

0

0

e

D

M

i

S

i

M

(a) (b)

Including zero-sequence voltage

No zero-sequence voltage

Fig. 7. The current waveform of i

M

, owing into the mid-point node M,

when a zero-sequence voltage is superimposed on each voltage reference in

capacitive operation. (a) a dc zero-sequence voltage, (b) a 6th-harmonic zero-

sequence voltage.

proportional gain of K

IP

= 1.8 V/A and an integral gain of

K

II

= 90 V/As. The digital control based on (13) causes a

one-sampling delay to the rst term. This one-sampling delay

corresponds to a delay of /60 rad in a line frequency of

50 Hz because the carrier frequency of PWM is 3 kHz. Thus,

the modied voltage references with lead compensation of the

one-sampling delay are given by

_

e

d

e

q

_

=

_

e

Sd

cos(/60)

e

Sd

sin(/60)

_

_

R

AC

L

AC

L

AC

R

AC

_ _

i

Sd

i

Sq

_

K

IP

_

i

Sd

i

Sd

i

Sq

i

Sq

_

K

II

_ _

i

Sd

i

Sd

i

Sq

i

Sq

_

dt. (14)

B. DC-link voltage control

It is easy to detect the dc-link voltage v

P2N2

, and to

control it by means of forming a voltage feedback loop with

a proportional gain of K

dc

= 1.0 A/V. This determines

the current reference on the d-axis, while the instantaneous

imaginary power command q

determines the current reference

on the q-axis as follows:

i

Sd

= K

dc

(4V

dc

v

P2N2

) (15)

i

Sq

=

q

e

Sd

. (16)

Here, the dc-link voltage reference 4V

dc

is set to 400 V in the

following experiments.

VI. VOLTAGE-BALANCING CONTROL AND CIRCUIT

A. Voltage-balancing control

Fig. 7 shows the current owing into the mid-point node

M, i

M

in capacitive operation under ideal conditions when

either a dc or 6th-harmonic (300 Hz) zero-sequence voltage is

superimposed on each of the three-phase voltage references.

When a dc zero-sequence voltage is superimposed, the dc

+

v

P2P1

v

P1M

v

CP

PI

control

Carrier signal (3 kHz)

Comparator

Gate

signals

Fig. 8. The control block diagram of the positive chopper in the voltage-

balancing circuit.

component of i

M

, or the dc mean current

i

M

is equal to zero,

as shown in Fig. 7 (a). The reason is that the STATCOM draws

only a reactive current from the ac mains. On the other hand,

i

M

is not equal to zero when a 6th-harmonic zero-sequence

voltage is superimposed, as shown in Fig. 7 (b). This enables

to adjust

i

M

in such a way as to achieve voltage balancing

between v

P2M

and v

MN2

. The reason for selecting the

6th-harmonic frequency is that it is the minimal frequency in

double and triple line frequencies. The superimposed zero-

sequence voltage v

M

is controlled by

v

M

=

_

K

MP

(v

MN2

v

P2M

)

+ K

MI

_

(v

MN2

v

P2M

)dt

_

sin 6t. (17)

The polarity of the reactive-power reference q

determines

either positive or negative sign in (17) because the polarity

of i

S

in inductive operation is opposite to that in capacitive

operation.

As shown in Fig. 6, the voltage-balancing controller consists

of a low-pass lter with a cut-off frequency of f

C

= 10 Hz

(T = 16 ms), and a PI regulator with a proportional gain of

K

MP

= 0.5 V/V and an integral gain of K

MI

= 0.1 V/Vs.

The low-pass lter is used for ltering of a 150-Hz component

included in v

MN2

v

P2M

, detecting its dc component. The

6th-harmonic zero-sequence voltage reference v

M

, that is the

output signal from the PI regulator, is commonly added to all

the three-phase voltage references e

u

, e

v

and e

w

.

B. Voltage-balancing circuit

As shown in Fig. 2, the voltage-balancing circuit is installed

on the dc side of the ve-level converter. It consists of two

positive and negative buck-boost choppers that are operated

independent of each other; one is used for voltage balancing of

the positive two capacitors, and the other for voltage balancing

of the negative two capacitors. Fig. 8 shows the control block

diagram of the positive chopper. The voltage reference v

CP

is

given by

v

CP

=

_

K

CP

(v

P2P1

v

P1M

)

+ K

CI

_

(v

P2P1

v

P1M

)dt

_

. (18)

Here, K

CP

= 0.01 V/V and K

CI

= 0.01 V/Vs. This

voltage referece is compared to a triangle carrier signal with

a frequency of 3 kHz, to determine the PWM gate signals for

the upper chopper.

IAS 2005 561 0-7803-9208-6/05/$20.00 2005 IEEE

VII. ACTUAL SWITCHING FREQUENCIES OF THE IGBTS

IN THE FIVE-LEVEL CONVERTER

It is a well-known fact that actual switching frequencies of

individual switching devices are not equal to (exactly speaking,

lower than) the carrier frequency in the ve-level converter,

unlike traditional two-level converters. As shown in Fig. 2,

eight IGBTs per leg are referred to as T1, T2, T8 from

the top. During the instantaneous value of e

is larger than

V

P1M

, T1 and T5 are switched on and off, and the other

IGBTs keep unswitched. During 0 < e

< V

P1M

, T2 and

T6 are switched on and off. Circuit symmetry concludes that

T1, T4, T5, and T8 have the same switching frequency, while

T2, T3, T6, and T7 have the same switching frequency that

is different from that of T1, T4, T5, and T8. Therefore, it is

sufcient to consider the switching frequencies of T1 and T2,

f

S1

and f

S2

.

The use of e

in (3) enables to specify an interval of time,

during which T1 is switched on and off, as follows:

T

VP1M

t

T

2

T

VP1M

. (19)

Thus, the switching frequencies of f

S1

and f

S2

are given by

f

S1

=

T/2 2T

VP1M

T

f

C

(20)

f

S2

=

f

C

2

f

S1

. (21)

When

2E = V

P2M

, f

S1

gets a maximal value of 1 kHz

because of f

C

= 3 kHz, while f

S2

gets a minimal value of

500 Hz.

As

2E gets lower than V

P1M

, f

S1

gets lower. When the

STATCOM is operated as an inductor rated at 10 kVA, the

rms value of e

gets a minimal value of E = 0.85E

S

, taking

into account that the STATCOM has an ac inductor of L

AC

=

9.5%. This results in a minimal value of f

S1

= 800 Hz, and in

a maximal value of f

S2

= 700 Hz. These theoretical results

of the actual switching frequencies can summarize that f

S1

ranges from 800 to 1,000 Hz and f

S2

ranges from 500 to

700 Hz.

VIII. EXPERIMENTAL RESULTS

A. Steady-State Performance

Fig. 9 shows experimental waveforms at the steady state

when the STATCOM is operated as a capacitor of 10 kVA.

The waveform of e

uM

looks based on ve levels of dc

voltages, while the waveform of e

uv

looks based on nine levels

of dc voltages. These waveforms characterize the ve-level

converter in terms of including much less voltage harmonics

than traditional two-level converters.

Table II summarizes the measured current THD (total har-

monic distortion) and harmonic-current components of i

Su

,

where each value is a ratio with respect to the fundamental

current. Note that harmonic components, of which the values

are less than 0.1%, are excluded from Table II. Power con-

verters intended for connection to utility grids in Japan should

comply with the following two requirements simultaneously.

v

P2M

v

P1M

v

N1M

v

N2M

e

Su

i

Su

e

uM

e

uv

v

P2N2

i

CP

i

CN

-0.5

0

0.5

-0.5

0

0.5

-200

0

200

350

400

450

-400

0

400

-200

0

200

-40

0

40

-200

0

200

10 ms

[A]

[A]

[V]

[V]

[V]

[V]

[A]

[V]

Fig. 9. Experimental waveforms in capacitive operation at 10 kVA.

TABLE II

CURRENT THD AND HARMONIC CURRENTS OF i

Su

IN CAPACITIVE

OPERATION AT 10 KVA, EXPRESSED AS %.

THD 2nd 3rd 4th 5th 7th 9th 11th 19th 26th 38th

1.7 0.4 0.4 0.6 0.9 0.9 0.2 0.5 0.2 0.2 0.2

The current THD is less than 5%.

Each harmonic current with respect to its fundamental

current is less than 3%.

Table II concludes that the waveform of i

Su

meets both

requirements completely.

B. Actual Switching Frequencies of the IGBTs

Fig. 10 shows the time-expanded waveforms of Fig. 9.

Table III summarizes actual switching frequencies of each

IGBT in capacitive operation at 10 kVA, which are counted

up from the waveform of e

uM

in Fig. 10. From Table III, the

actual switching frequencies of T1, T4, T5 and T8 were the

same as 950 Hz in a range of 800 to 1,000 Hz, while those of

T2, T3, T6 and T7 were the same as 550 Hz in a range of 500

to 700 Hz. This means that these actual frequencies were in

the theoretical frequency ranges obtained from (20) and (21)

IAS 2005 562 0-7803-9208-6/05/$20.00 2005 IEEE

e

uM

i

CP

i

CN

-0.5

0

0.5

-0.5

0

0.5

-200

0

200

2 ms

[A]

[A]

[V]

Fig. 10. Time-expanded waveforms of e

uM

, i

CP

and i

CN

in Fig.9.

TABLE III

ACTUAL SWITCHING FREQUENCY OF EACH IGBT IN CAPACITIVE

OPERATION AT 10 KVA.

X 1, 4, 5, 8 2, 3, 6, 7

fSX [Hz] 950 550

in the previous section.

C. The Voltage-Balancing Control and Circuit

The waveform of v

P2N2

in Fig. 9 reveals that the dc-link

voltage includes a voltage ripple of 0.5%. The dc-link mean

voltage was observed to be equal to its voltage reference of

400 V. It is clear from the waveforms of v

P2M

, v

P1M

,

v

N1M

and v

N2M

in Figs. 9 and 10 that the combination

of the voltage-balancing control and circuit keeps each dc

capacitor voltage balanced well. In other words, each dc

capacitor voltage can be controlled to be equal to 100 V.

However, each dc capacitor voltage uctuates at 150 Hz (triple

the line frequency). Note that this phenomenon is inherent in

the ve-level converter, and no 150-Hz component appears in

the dc-link voltage. The 150-Hz components present in v

P2M

and v

P1M

are 3.0% and 4.0%, respectively. However,

they produce no bad effect on current-control performance.

The dc mean currents owing in the chopper inductors L

CP

and L

CM

were observed to be about 0.2 A and 0.1 A,

respectively. The 3-kHz current ripples caused by switching

operation at 3 kHz were superimposed on the dc currents i

CP

and i

CN

. Each chopper inductor with an inductance value of

110 mH has a continuous-current rating of 0.3 A, and a peak-

current rating of 0.5 A. This suggests that the chopper inductor

rated at 110 mH and 0.3 A is theoretically the same in physical

size as a dc inductor rated at 10 H and 30 A (the rated current

of the STATCOM). Therefore, the chopper inductor is much

smaller in physical size and much lower in cost than the ac-

link inductor L

AC

rated at 1.2 mH and 30 A, although a slight

difference may exist between dc and ac inductors.

D. Transient Performance

Fig. 11 shows experimental waveforms in the transient state

when a ramp change from 10 kVA to +10 kVA with a line

v

P2M

v

P1M

v

N1M

v

N2M

q

e

Su

i

Su

e

uM

e

uv

v

P2N2

i

CP

i

CN

-0.5

0

0.5

-0.5

0

0.5

-200

0

200

350

400

450

-400

0

400

-200

0

200

-40

0

40

-200

0

200

-10

0

10

20 ms

20 ms

[A]

[A]

[V]

[V]

[V]

[V]

[A]

[V]

[kvar]

Fig. 11. Transient performance from inductive to capacitive operation at

10 kVA.

cycle of 20 ms was given to the reactive-power reference q

.

Note that q

= 10 kVA means inductive operation at 10 kVA,

while q

= +10 kVA means capacitive operation at 10 kVA.

The 200-V STATCOM provided satisfactory operating per-

formance including dc-link voltage regulation, even in the

transient state. In addition, no dc-voltage imbalance occurred

in the four dc capacitors without causing any overcurrent to

i

CP

or i

CN

.

Fig. 12 shows experimental waveforms before and after the

voltage-balancing circuit for the node P1 and N1 were inten-

tionally stopped at the time of 50 ms in capacitive operation

at 10 kVA. Note that the voltage-balancing control of the node

M remained operated through this experiment. It was observed

that the capacitor voltages of v

P2M

and v

MN2

were well

balanced, independent of whether the voltage-balancing circuit

was operated or not.

After stopping the voltage-balancing circuit, the capacitor

voltage v

P2P1

was decreasing, while the capacitor voltage

IAS 2005 563 0-7803-9208-6/05/$20.00 2005 IEEE

v

P2M

v

P1M

v

N1M

v

N2M

e

Su

i

Su

e

uM

e

uv

v

P2N2

i

CP

i

CN

-0.5

0

0.5

-0.5

0

0.5

-200

0

200

350

400

450

-400

0

400

-200

0

200

-40

0

40

-200

0

200

200 ms

Two choppers

stopped

Overvoltage detected

[A]

[A]

[V]

[V]

[V]

[V]

[A]

[V]

Fig. 12. Experimental waveforms before and after stopping the voltage-

balancing circuit in capacitive operation at 10k VA, keeping the voltage-

balancing control operated.

v

N1N2

was increasing. Finally, an overvoltage-protection

circuit of v

P2P1

worked at the time of 1.02 s, or in 970 ms,

and then the STATCOM was shut down automatically. The ex-

perimental waveforms justify installing the voltage-balancing

circuit on the dc link of the ve-level converter.

IX. CONCLUSIONS

This paper has described a design concept of the 6.6-

kV transformerless STATCOM based on a ve-level diode-

clamped converter, with focus on voltage balancing of the

four dc capacitors connected in series. The STATCOM is

characterized by combining a small-rated voltage-balancing

circuit consisting of two bi-directional buck-boost choppers

with voltage-balancing control integrated into a PWM method

for the ve-level converter. Experimental results obtained from

a 200-V 10-kVA laboratory model have veried the viability

and effectiveness of the voltage-balancing circuit and control,

even in transient states.

The design concept presented, along with the experimental

results shown in this paper, would encourage power electronics

researchers and engineers to put the 6.6-kV transformerless

STATCOM on the market in the near future. The authors

expect the STATCOM to compete well with traditional static

var compensators using capacitors, inductors and/or thyristors

in terms of cost and performance.

X. ACKNOWLEDGMENT

The authors would like to thank Dr. Yasushi Matsumoto and

Mr. Jiro Toyosaki of Fuji Electric Advanced Technology for

their technical support through this research.

REFERENCES

[1] A. Nabae, I. Takahashi, and H. Akagi, A new neutral-point-clamped

PWM inverter, IEEE Trans. Ind. Appl., vol. 17, no. 5, pp. 518-523,

1981.

[2] J. S. Lai, and F. Z. Peng, Multilevel convertersa new breed of power

converters, IEEE Trans. Ind. Appl., vol. 32, no. 3, pp. 506-517, 1996.

[3] J. Rodrigues, J. S. Lai, and F. Z. Peng, Multilevel Inverters: a survey

of topologies, controls, and applications, IEEE Trans. Ind. Electron.,

vol. 49, no. 4, pp. 724-738, 2002.

[4] N. S. Choi, J. G. Cho, and G. H. Cho, A general circuit topology of

multilevel inverter, in Conf. Rec. IEEE-PESC, 1991, pp. 96-103.

[5] R. W. Menzies, P. Steimer, and J. K. Steinke, Five-level GTO inverters

for large induction motor drives, IEEE Trans. Ind. Appl., vol. 30, no.

4, pp. 938-944, 1994.

[6] C. Hochgraf, and R. H. Lasseter, A transformer-less static synchronous

compensator employing a multi-level inverter, IEEE Trans. Power

Deliv., vol. 12, no.2, pp. 881-887, 1997.

[7] Y. Chen, B. Mwinyiwiwa, Z. Wolanski, and B. T. Ooi, Regulating

and equalizing dc capacitance voltages in multilevel STATCOM, IEEE

Trans. Power Deliv., vol. 12, no.2, pp. 901-907, 1997.

[8] G. Sinha, and T. A. Lipo, A four-level inverter based drive with a

passive front end, IEEE Trans. Power Electron., vol. 15, no. 2, pp.

285-294, 2000.

[9] K. Corzine, X. Kou, and J. R. Baker, Dynamic average-value modeling

of a four-level drive system, IEEE Trans. Power Electron., vol. 18, no.

2, pp. 619-627, 2003.

[10] J. Pou, R. Pindado, and D. Boroyevich, Voltage-balancing limits in

four-level diode-clamped converters with passive front ends, IEEE

Trans. Ind. Electron., vol. 52, no. 1, pp. 190-196, 2005.

[11] K. Sasagawa, Y. Abe, and K. Matsuse, Voltage-balancing method for

IGBTs connected in series, IEEE Trans. Ind. Appl., vol. 40, no. 4, pp.

1025-1030, 2004.

[12] H. Fujita, S. Tominaga, and H. Akagi, Analysis and design of a dc

voltage-controlled static var compensator using quad-series voltage-

source inverters, IEEE Trans. Ind. Appl., vol. 32, no. 4, pp. 970-978,

1996.

[13] S. Ogasawara, and H. Akagi, Analysis of variation of neutral-point

potential in neutral-point-clamped voltage-source PWM inverters, in

Conf. Rec. IEEE-IAS Ann. Meeting, 1993, pp. 965-970.

IAS 2005 564 0-7803-9208-6/05/$20.00 2005 IEEE

You might also like

- Electrical Power System Fault Analysis PDFDocument60 pagesElectrical Power System Fault Analysis PDFKumardeep MukhopadhyayNo ratings yet

- Syllabus I YearDocument25 pagesSyllabus I YearDipesh PatelNo ratings yet

- Switchgear Notes PDFDocument134 pagesSwitchgear Notes PDFGorla RamuNo ratings yet

- Switchgear Notes PDFDocument134 pagesSwitchgear Notes PDFGorla RamuNo ratings yet

- Electrical Power System Fault Analysis PDFDocument60 pagesElectrical Power System Fault Analysis PDFKumardeep MukhopadhyayNo ratings yet

- Syllabus I Year 2019 20 Onwards PDFDocument24 pagesSyllabus I Year 2019 20 Onwards PDFRitik KalwarNo ratings yet

- Power SystemsDocument47 pagesPower Systemsmanish_chaturvedi_6No ratings yet

- PS Lab ManualDocument25 pagesPS Lab ManualPhani PhaniNo ratings yet

- Ph.D. Pre Synopsis Seminar Examination ReportDocument4 pagesPh.D. Pre Synopsis Seminar Examination Reportmanish_chaturvedi_6No ratings yet

- Supervisor 2018 19Document8 pagesSupervisor 2018 19manish_chaturvedi_6No ratings yet

- Provisional List of Research Centers For The Session 2018 191Document4 pagesProvisional List of Research Centers For The Session 2018 191manish_chaturvedi_6No ratings yet

- PHD Thesis Format and GuidelinesDocument15 pagesPHD Thesis Format and GuidelinesPranayNo ratings yet

- PHD Thesis Evaluation FormDocument2 pagesPHD Thesis Evaluation Formmanish_chaturvedi_6No ratings yet

- PHD Oral Defence Evaluation FormDocument2 pagesPHD Oral Defence Evaluation Formmanish_chaturvedi_6No ratings yet

- Half Yearly Exam - Class3 - ComputerDocument5 pagesHalf Yearly Exam - Class3 - Computermanish_chaturvedi_6No ratings yet

- Half Yearly Exam - Class 3 - English 1Document3 pagesHalf Yearly Exam - Class 3 - English 1manish_chaturvedi_6No ratings yet

- PHD Oral Defence Evaluation FormDocument2 pagesPHD Oral Defence Evaluation Formmanish_chaturvedi_6No ratings yet

- PHD Thesis Format and GuidelinesDocument15 pagesPHD Thesis Format and GuidelinesPranayNo ratings yet

- PHD Thesis Evaluation FormDocument2 pagesPHD Thesis Evaluation Formmanish_chaturvedi_6No ratings yet

- Ph.D. Pre Synopsis Seminar Examination ReportDocument4 pagesPh.D. Pre Synopsis Seminar Examination Reportmanish_chaturvedi_6No ratings yet

- Half Yearly Exam English - IDocument2 pagesHalf Yearly Exam English - Imanish_chaturvedi_6No ratings yet

- Half Yearly Exam General Science Class 3Document3 pagesHalf Yearly Exam General Science Class 3manish_chaturvedi_6No ratings yet

- Final Year Exam MATHS1Document2 pagesFinal Year Exam MATHS1manish_chaturvedi_6No ratings yet

- Half Yearly Exam English - IDocument2 pagesHalf Yearly Exam English - Imanish_chaturvedi_6No ratings yet

- Ist Year Branchwise Batch AllottmentDocument1 pageIst Year Branchwise Batch Allottmentmanish_chaturvedi_6No ratings yet

- Half Yearly Exam - Deepta - Evs - 1Document3 pagesHalf Yearly Exam - Deepta - Evs - 1manish_chaturvedi_6No ratings yet

- Ist Year Branchwise Batch AllottmentDocument1 pageIst Year Branchwise Batch Allottmentmanish_chaturvedi_6No ratings yet

- Counselor For Ist Year StudentsDocument1 pageCounselor For Ist Year Studentsmanish_chaturvedi_6No ratings yet

- List of Officials of UTDDocument1 pageList of Officials of UTDmanish_chaturvedi_6No ratings yet

- Mba Brochure1 PDFDocument17 pagesMba Brochure1 PDFMadhusudan DadhichNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Controller-Based Temperature Control Application Building BlockDocument56 pagesController-Based Temperature Control Application Building Blocknelhani01No ratings yet

- Avaneesh Arduino Design BriefDocument3 pagesAvaneesh Arduino Design BriefAvaneesh Aravind HangalurNo ratings yet

- Joystick 1Document28 pagesJoystick 1Nuñez JesusNo ratings yet

- Roland SH 101 Nova ModDocument13 pagesRoland SH 101 Nova ModmarkpsilosNo ratings yet

- PF Silent Fan eDocument5 pagesPF Silent Fan eAlessio RomanNo ratings yet

- Arduino Shield ManualDocument24 pagesArduino Shield Manualzhalim2001No ratings yet

- PMG PDFDocument6 pagesPMG PDFrajan_2002eeeNo ratings yet

- SD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetDocument10 pagesSD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage Mosfetحسین مشعلNo ratings yet

- On-Bright Confidential To IVT: General Description FeaturesDocument12 pagesOn-Bright Confidential To IVT: General Description FeaturesGabriel GarciaNo ratings yet

- E5-02 - Scientech Nvis 3000A Control System Lab and Nvis 630Document3 pagesE5-02 - Scientech Nvis 3000A Control System Lab and Nvis 630waleed.murad@gmail.comNo ratings yet

- ECM (Hydrostatic Transmission)Document5 pagesECM (Hydrostatic Transmission)Hamilton MirandaNo ratings yet

- MXD7202Document10 pagesMXD7202adfumegaNo ratings yet

- Eblocks2 DatasheetDocument82 pagesEblocks2 DatasheetAbel Alejandro Castro M.No ratings yet

- Measurement of Adjustable Speed Drives With Fluke MetersDocument28 pagesMeasurement of Adjustable Speed Drives With Fluke MetersnaveedfndNo ratings yet

- Chapter-1: 1.1.1 The Principle of WindmillDocument22 pagesChapter-1: 1.1.1 The Principle of WindmillVijay BavikattiNo ratings yet

- Data Sheet: Part No. Package Code No. SSOP016-P-0225EDocument32 pagesData Sheet: Part No. Package Code No. SSOP016-P-0225Ekarti0660No ratings yet

- Sae J2534 - 2002-1116Document48 pagesSae J2534 - 2002-1116goldpen1234100% (1)

- Lab 2 - myRIO Analog Basics PDFDocument6 pagesLab 2 - myRIO Analog Basics PDFguigo170_321273986No ratings yet

- User's Manual: LED Portable Industrial Film ViewerDocument2 pagesUser's Manual: LED Portable Industrial Film ViewerMuhammed Abo-FandoodNo ratings yet

- Preface: Speed Control of DC Motor Using PWM By-Yash DoshiDocument11 pagesPreface: Speed Control of DC Motor Using PWM By-Yash Doshirochmat100% (1)

- Automated Door OpenerDocument15 pagesAutomated Door OpenerMuheeb100% (1)

- CP Bourg BSTD CDDocument118 pagesCP Bourg BSTD CDtraminer80% (5)

- Microcontrollers: Open Loop Universal Motor Chopper Based On The MC68HC908QT4 MicrocontrollerDocument42 pagesMicrocontrollers: Open Loop Universal Motor Chopper Based On The MC68HC908QT4 MicrocontrollerturuceluNo ratings yet

- Green-Mode PWM Controller With High-Voltage Start-Up Circuit and Adjustable OLP Delay TimeDocument19 pagesGreen-Mode PWM Controller With High-Voltage Start-Up Circuit and Adjustable OLP Delay TimeЕвгений ПNo ratings yet

- VSSUT (EEE) SyllabusDocument47 pagesVSSUT (EEE) SyllabusAshutosh GuptaNo ratings yet

- Application of Modular Multilevel Converter in Medium Voltage High Power Permanent Magnet Synchronous Generator Wind Energy Conversion SystemsDocument10 pagesApplication of Modular Multilevel Converter in Medium Voltage High Power Permanent Magnet Synchronous Generator Wind Energy Conversion SystemsAbu Bakr M. SaeedNo ratings yet

- Aitecs 2015 - Service ManualDocument79 pagesAitecs 2015 - Service Manualoswaldo_apaza_1No ratings yet

- DC Motor Speed Controller 1 PDFDocument1 pageDC Motor Speed Controller 1 PDFRyn YahuFNo ratings yet

- Appendix - Codes Mbe PDFDocument10 pagesAppendix - Codes Mbe PDFFernandez DieselNo ratings yet

- LP156WF1Document29 pagesLP156WF1helpquickNo ratings yet