Professional Documents

Culture Documents

DMAin TMS320 C54 XX

Uploaded by

gurudatha265Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DMAin TMS320 C54 XX

Uploaded by

gurudatha265Copyright:

Available Formats

Direct Memory Access (DMA)

•What is DMA? A facility

o transfer data from memory to memory

o / memory to peripheral

o memory and peripherals can be internal / external

o no intervention of CPU

o DMA controller takes care of memory transfer

• DMA has 6 channels for memory transfer

o Each channel connects to a source location and destination location

o Total 6 source and destination locations can be connected

o Single transfer at a time

o High priority channel is serviced before a low priority channel

o For same priority it is serviced in a circular way 2,3,4,5,0,1

o Transfer in terms of blocks of data

o Block contains frames

o For internal memories 4 clock cycles

o 2 read + 2 write

DMA Operation Configuration

• Prior to transfer sub bank addressed registers have to be configured

o Which channel?

o Source and destination address

o Priorities and enabling of channels with DMPREC register 16 bit

o Size of the block

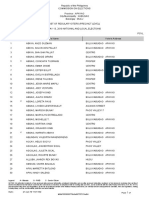

DMA Sub bank Addressed Registers

Name Address Sub Addr Description

DMSRC0 56h/57h 00h DMA channel 0 source address register

DMDST0 56h/57h 01h DMA channel 0 destination address register

DMCTR0 56h/57h 02h DMA channel 0 element count register

DMSFC0 56h/57h 03h DMA channel 0 sync select and frame count register

DMMCR0 56h/57h 04h DMA channel 0 transfer mode control register

DMSRC1

………..

DMSRCP 56h/57h 1Eh DMA source program page address (common channel)

• 5 registers for each channel

• Total 30 registers for 6 channels

• +other control registers

• Total 62 registers

Register Sub addressing

• Technique used for configuring the DMA registers

• Intervention of CPU required

• Code for configuration is loaded into access registers DMSDI or DMSDN

• Sub address to be configured is loaded into DMSA

• DMSDI is auto-incremented

• DMSDI for entire sets of registers

• DMSDN for a single register access

SUBBANK

ACCESS DMSDI

REGISTERS Sub-addressed

DMSDN Registers

DMSA

SUBBANK

ADDRESS

REGISTER

Example Program 1: Write code to show how the DMA channel 2 source address

register can be initialized with the value 1111h.

Following program is simulated in CCS:

; Program name ex9p6.s

.def _c_int00

dmsa .set 55h ; address of subbank address register

dmsdn .set 57h ; address of subbank access register

dmsrc2 .set 0ah ; subaddress

.text

_c_int00:

stm dmsrc2, dmsa ; DMSA= address of DMSRC2= 0Ah

stm #1111h, dmsdn ; write 1111h to DMSRC2

.end

After execution:

Peripheral register DMSA=000A

DMPREC =0000h

Example Program 2: Write TMS320C54xx code to show how the DMA channel 5

context registers can be initialized. Choose arbitrary values to be written to the

registers.

Solution: Since a set of registers are to be configured DMSDI is used.

DMSA .set 55h ; address of subank address register

DMSDI .set 56h ; address of subbank access register

DMSRC5 .set 19h ; subaddress of DMSRC5

DMDST5 .set 1Ah

DMCTR5 .set 1Bh

DMSFC5 .set 1Ch

DMMCR5 .set 1Dh

STM DMSRC5, DMSA ; DMSA= first sub address

STM #2000h, DMSDI ; write 2000h to DMSRC5

STM #3000h, DMSDI ; write 3000h to DMDST5

STM #0010h, DMSDI ; write 0010h to DMCTR5

STM #0002h, DMSDI ; write 2h to DMSFC5

STM #0000h, DMSDI ; write 0h to DMMCR5

Example 3: Write a TMS320C54xx code to transfer a block of data from the

program memory to the data memory. Following are the specifications:

Source address: 26000h in program space (extended memory page 2)

Destination address: 07000h in data space

Transfer size: 1000h single (16-bit) words

Channel use: DMA channel #0

Solution:

DMA registers should be defined with appropriate directives

STM DMSRCP, DMSA ; set source program page

STM #2h, DMSDN

STM DMSRC0, DMSA ; channel 0 to be used

STM #6000h, DMSDI ; source program address is set to 6000h

; DMSA points to DMDST0 after transfer

STM #7000h, DMSDI ; set destination address to 7000h

; after transfer DMSA points to DMCTR0

STM #(1000h-1), DMSDI ; set for 1000h transfers

; DMSA points to DMSFC0

STM #00000h, DMSDI ; Configure DMSFC0

; DMSA points to DMMCR0

STM #00105h, DMSDI ; configure DMMCR0

; DMSA points to DMSRC0

STM #00101h, DMPREC ; configure DMPREC

You might also like

- Log PowerPointDocument1 pageLog PowerPointgurudatha265No ratings yet

- Sol 10 U8 Companion Ga Md5sumDocument1 pageSol 10 U8 Companion Ga Md5sumgurudatha265No ratings yet

- DSProcessorsDocument11 pagesDSProcessorsgurudatha265100% (2)

- Speech Processing SystemDocument2 pagesSpeech Processing Systemgurudatha265No ratings yet

- Wavelength Division MultiplexingDocument14 pagesWavelength Division Multiplexinggurudatha265100% (3)

- MultimediaDocument18 pagesMultimediagurudatha265100% (3)

- Programming Concepts C LanguageDocument42 pagesProgramming Concepts C Languagegurudatha265100% (2)

- Wireless Comm 1Document89 pagesWireless Comm 1gurudatha265100% (2)

- Control SystemDocument179 pagesControl Systemgurudatha26583% (6)

- Power FlowDocument7 pagesPower Flowgurudatha265No ratings yet

- Lossy Compression AlgorithmsDocument18 pagesLossy Compression Algorithmsgurudatha265100% (2)

- Loss Less CompressionDocument17 pagesLoss Less Compressiongurudatha265100% (1)

- The 555 TimerDocument14 pagesThe 555 Timergurudatha265100% (4)

- Tomorrows Living WorldDocument3 pagesTomorrows Living Worldgurudatha265No ratings yet

- Introductionto VLSIDESIGNDocument64 pagesIntroductionto VLSIDESIGNgurudatha265100% (2)

- Introductionto VLSIDESIGNDocument64 pagesIntroductionto VLSIDESIGNgurudatha265100% (2)

- Programming Inc SharpDocument4 pagesProgramming Inc Sharpgurudatha265No ratings yet

- Windows Application Programming Inter FaDocument3 pagesWindows Application Programming Inter Fagurudatha265No ratings yet

- Feature Representation GMMDocument25 pagesFeature Representation GMMgurudatha265No ratings yet

- Communication SystemsDocument111 pagesCommunication Systemsgurudatha265100% (2)

- IEEEkeywordsDocument140 pagesIEEEkeywordsgurudatha265No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Fundamentals of Database System Prelim ExamDocument5 pagesFundamentals of Database System Prelim ExamKim JulongbayanNo ratings yet

- CollectionDocument628 pagesCollectionjralbendinNo ratings yet

- Advanced Data Structures Lab ManualDocument84 pagesAdvanced Data Structures Lab ManualKarthikeya Sri100% (1)

- Lab Manual of DbmsDocument106 pagesLab Manual of Dbmsgouthami jukantiNo ratings yet

- AccountingExcelConferenceStart - Data ModelDocument322 pagesAccountingExcelConferenceStart - Data ModelShams Tabrez50% (2)

- Map Date and Time API with JPA 2.2Document4 pagesMap Date and Time API with JPA 2.2AdolfNo ratings yet

- Belajar Mengkonfigurasi Banner, Telnet, SSH, FTP, HTTP and Customizing Account Privileges in JunosDocument6 pagesBelajar Mengkonfigurasi Banner, Telnet, SSH, FTP, HTTP and Customizing Account Privileges in JunosiwingNo ratings yet

- Ips Data Upload 6 7 0 TSDDocument92 pagesIps Data Upload 6 7 0 TSDSuresh PandaNo ratings yet

- CH 7 - Introduction To SQL and Its Commands For Board ExamDocument28 pagesCH 7 - Introduction To SQL and Its Commands For Board ExamameentrafiqNo ratings yet

- Resolve "enq: TX - row lock contentionDocument2 pagesResolve "enq: TX - row lock contentionAlberto Hernandez HernandezNo ratings yet

- How To Create Universes Using BEx Queries As Data Sources With SAP BusinessObjects Information Design Tool 4.1Document23 pagesHow To Create Universes Using BEx Queries As Data Sources With SAP BusinessObjects Information Design Tool 4.1john91067% (6)

- Techlog 2018-2 SynchronizationTool DeploymentGuideDocument20 pagesTechlog 2018-2 SynchronizationTool DeploymentGuidec_b_umashankarNo ratings yet

- Queue ADT Chapter ExplainedDocument33 pagesQueue ADT Chapter ExplainedbharathkumarNo ratings yet

- Parse Decode Convert ISO8583Document10 pagesParse Decode Convert ISO8583Jainer Antonio Marin SerranoNo ratings yet

- Oracle Data Integrator Enterprise EditionDocument5 pagesOracle Data Integrator Enterprise EditionOliveira RubensNo ratings yet

- A Binary Holiday ActivityDocument6 pagesA Binary Holiday ActivityJJ FajardoNo ratings yet

- Memory - Management - Exercises and SolutionDocument21 pagesMemory - Management - Exercises and Solutionkz33252000No ratings yet

- ePO 4.5 and 4.6 Server Backup and Disaster Recovery ProcedureDocument8 pagesePO 4.5 and 4.6 Server Backup and Disaster Recovery ProcedureRAJESHNo ratings yet

- Hw5 C2a VergaraDocument5 pagesHw5 C2a VergaraVergara AaronNo ratings yet

- Abit Ah4t ManualDocument33 pagesAbit Ah4t Manualdcurvers1980No ratings yet

- Infineon-Component Emulated EEPROM V2.20-Software Module Datasheets-V02 02-EnDocument28 pagesInfineon-Component Emulated EEPROM V2.20-Software Module Datasheets-V02 02-EnK M Mosheur RahmanNo ratings yet

- BULUDocument14 pagesBULUCarol Fernandez Rivera AbellaNo ratings yet

- Autocad 2012 DXF Reference PDFDocument270 pagesAutocad 2012 DXF Reference PDFC.E.B.I MAROCNo ratings yet

- Online Exam Management SystemDocument18 pagesOnline Exam Management SystemHardik Gupta100% (2)

- Oracle Hyperion Epm System Certific 131801Document89 pagesOracle Hyperion Epm System Certific 131801BHASKAR SANKARNo ratings yet

- How blockchain works simply explainedDocument4 pagesHow blockchain works simply explainedFelia MandaNo ratings yet

- Tranformer Developer GuideDocument290 pagesTranformer Developer Guidepad23au1225No ratings yet

- SQL-BackTrack™ For Oracle Messages Manual Version 3.2.70Document120 pagesSQL-BackTrack™ For Oracle Messages Manual Version 3.2.70dillonr01No ratings yet

- Python Data Analysis and VisualizationDocument13 pagesPython Data Analysis and VisualizationKrupaNo ratings yet

- Xsl-Fo TutorialDocument12 pagesXsl-Fo Tutorialapi-19921804No ratings yet