Professional Documents

Culture Documents

Problemas de Codificadores

Uploaded by

Marcos AlfaroCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Problemas de Codificadores

Uploaded by

Marcos AlfaroCopyright:

Available Formats

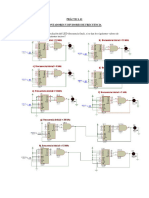

PROBLEMA: Determinar la salida producida por los siguiente circuitos para las entradas binarias mostradas.

(a) Empezaremos con el primer AND de dos entradas alimentado con las palabras binarias10011001 y 10100101. El anlisis se debe llevar a cabo bit-por-bit. Supondremos que las seales binarias van entrando de izquierda a derecha, aunque para los fines del presente problema el orden de entrada de las palabras es irrelevante. En el extremo derecho de ambas palabras binarias tenemos un bit " 1" en la terminal superior entrando al mismo tiempo que un bit "1" entrando en la terminal inferior. Por ser un bloque AND, la salida resultante para la primera combinacin de bits ser un "1". A continuacin, entrarn al bloque AND los bits "0" y "0", los cuales producirn una salida de "0". Con esto, llevamos formada ya una salida cumulativa de "10". Tras esto, entrarn en las dos terminales, respectivamente, los bits "0" y "1", los cuales producirn a la salida del AND un "0", con lo cual la palabra binaria de salida ser ya "100". Continuando de esta manera, bit-por-bit, tendremos a la salida del bloque AND el resultado mostrado en la siguiente tabla:

La palabra a la salida del AND de dos entradas con las dos palabras binarias dadas ser entonces 10000001. (b) Procediendo de la misma manera para el bloque OR de dos entradas, bit-por-bit, podemos construr la siguiente tabla:

La palabra binaria a la salida del OR ser 10111101. (c) Para el bloque AND de tres entradas, extendemos la definicin del AND de dos entradas, afirmando que la salida del AND de tres entradas ser "1" nicamente cuando todas sus tres entradas tengan un valor de "1". Con esto, procediendo con el anlisis bit-por-bit, podemos producir la siguiente tabla:

La palabra binaria a la salida del AND de tres entradas ser 00010000. (d) Para el bloque OR de tres entradas, extendemos la definicin del OR de dos entradas, afirmando que la salida del OR de tres entradas ser "1" cuando cualquiera de sus tres entradas tengan un valor de "1". Con esto, procediendo con el anlisis bit-por-bit, podemos producir la siguiente tabla:

La palabra binaria a la salida del OR de tres entradas ser 11111011. (e) Para el bloque NAND, podemos llevar a cabo el anlisis, bit-por-bit, tomando en cuenta primero la accin inicial del AND sobre dos bits a su entrada, y llevando a cabo inmediatamente tras esto el proceso de negacin lgica como lo especifica la burbuja inversora puesta en la salida del AND con la cual es transformado en un NAND. Los primeros dos bits en entrar son "0" y "1", los cuales por la accin del AND son convertidos en un "0", el cual por la accin de la burbuja inversora es convertido en un "1" como resultado final. Tras esto, los siguientes dos bits en entrar son "1" y "0", los cuales nuevamente por la accin del AND son convertidos en un "0", el cual por la accin de la burbuja inversora es convertido en un "0". Procediendo de esta manera, podemos construr la siguiente tabla, en la cual el resultado "intermedio", la palabra binaria formada por la accin del AND antes de llevarse a cabo la accin inversora, ha sido puesto en color rojo:

La palabra binaria a la salida del NAND ser 111110100. PROBLEMA: Son tiles los siguientes circuitos para el procesamiento de informacin?

(A) Como este circuito tiene una sola terminal de entrada, slo se le puede poner un "1" o un "0". Analizando el primer circuito poniendo la palabra binaria "10" a su entrada, la cual contiene las dos combinaciones posibles, tenemos lo siguiente:

La palabra binaria "10" a la entrada del NOT es convertida en la palabra binaria "01" a la salida del NOT. Al entrar las palabras binarias "10" y "01" al OR, la salida de este ser la palabra binaria "11". Puesto que no importando qu informacin se le introduzca a su entrada, ya sea un "1" o un "0", la salida siempre ser "1", se concluye que este circuito no puede procesar informacin. (B) Al igual que en el caso anterior, como este circuito tiene una sola terminal de entrada, slo se le puede poner en dicha entrada un "1" o un "0". Analizando el segundo circuito con la palabra binaria "10" a su entrada, la cual contiene todas las combinaciones posibles, tenemos lo siguiente:

Nuevamente, la palabra binaria "10" a la entrada del NOT es convertida en la palabra binaria "01" a la salida del NOT. Y al entrar las palabras binarias "10" y "01" al AND, la salida de este ser la palabra binaria "00". Puesto que no importando qu informacin se le introduzca a su entrada, ya sea un "1" o un "0", la salida siempre ser "0", se concluye que este circuito tampoco puede procesar informacin. PROBLEMA: Analizar el siguiente circuito construyendo una Tabla de Verdad para el mismo. Obsrvese cmo en el diagrama est trazado el flujo de seales para la palabra binaria de entrada A3A2A1 = 101.

Podemos ver en el diagrama del circuito que con la palabra A3A2A1 = 101 nicamente la salida del AND 5 estar activada con un "1". La salida de cada uno de los AND restantes estar desactivada con un "0". A continuacin, vamos introduciendo una palabra binaria diferente a la entrada del circuito. Ensayando la combinacin A3A2A1 = 001 y trazando el flujo de seales del mismo modo que fue trazado para la combinacin A3A2A1 = 101, encontramos ahora que nicamente la salida del AND 1 estar activada con un

"1", siendo la salida en cada uno de los AND restantes "0". Siguiendo el mismo procedimiento para cada una de las combinaciones posibles de unos y ceros en la entrada A3A2A1, podemos construr la siguiente Tabla de Verdad:

De acuerdo con la Tabla de Verdad obtenida, para cada combinacin posible de unos y ceros a la entrada del circuito nicamente se activar la salida de un solo AND en particular. El hecho de que cada combinacin posible de unos y ceros a la entrada active nicamente uno de los AND de salida a la vez nos puede decir cul es la palabra binaria a la entrada. Por ejemplo, podemos conectar la salida de cada AND a un indicador luminoso numrico que todava en un pasado reciente podra haber sido un tubo electrnico tipo "Nixie":

el cual est hoy casi obsoleto al haber sido reemplazado por los diodos emisores de luz LED. La conexin a nmeros diferentes sigue siendo directa como se muestra a continuacin:

De esta manera, al aplicar una combinacin de unos y ceros a la entrada del circuito (por ejemplo, la palabra A3A2A1 = 101, la cual equivale al nmero decimal 5), se encender dentro del indicador luminoso seleccionado el numeral que corresponda a dicha combinacin (en este caso, el numeral 5). Tenemos, pues, una configuracin que nos produce informacin decimal a la salida al aplicar informacin binaria a su entrada. O

sea, que al introducir un nmero binario como el "101" leeremos un "5" en nuestro sistema decimal a la salida de la configuracin. La configuracin de hecho est "traduciendo" informacin binaria convirtindola a informacin decimal. Circuitos de este tipo reciben el nombre de decodificador, y su funcin es precisamente traducir (o ms apropiadamente, decodificar) informacin binaria para su uso subsecuente o bien, para lectura en sistema decimal de dicha informacin binaria. Por regla general, todo circuito que produzca una salida nica para cada combinacin de unos y ceros a su entrada es considerado como un decodificador. Generalmente, en un decodificador la tendencia es que sean ms las terminales de salida que las terminales de entrada. El decodificador arriba mostrado no nos sera muy til en la prctica puesto que nicamente nos puede proporcionar dgitos hasta el nmero 7 decimal. Esto se puede remediar agregndole al decodificador un AND y un NOT, con las dos lneas adicionales necesarias para que los dgitos decimales"8" y "9" se puedan encender con las palabras binarias de entrada A4A3A2A1 = 1000 y A4A3A2A1 = 1001 respectivamente. Tendramos entonces un decodificador binario BCD a decimal. Pero existe una alternativa ms econmica y eficiente que volver a inventar la rueda: podemos procurar en el mercado un circuito integrado decodificador que pueda llevar a cabo precisamente esta labor. Un circuito integrado como el 4028:

Este circuito integrado trabaja de la siguiente manera: el nmero binario BCD es puesto en las terminales "pin" de entrada desde la 10 hasta la 13, con el bit menos significativo (LSB) o bit "A" puesto en la terminal 10, y el bit ms significativo (MSB) o bit "D" puesto en la terminal 11. Este decodificador trabaja exactamente de la misma manera que el que se describi en este problema, excepto que tiene capacidad para los nueve dgitos decimales. Si se le pone la entrada DCBA=0101, la terminal "pin" 6 (que corresponde al nmero 5 decimal) se encender con un "1" mientras que todas las dems terminales de salida permanecern en "0". Si se le pone al circuito integrado un nmero binario mayor que el equivalente decimal de 9, entonces todas las salidas se quedarn en "cero", ninguna de las diez salidas se encender. Si vamos a utilizar el decodificador binario BCD con una cartula de indicadores numricos hechos a base de diodos emisores de luz LED de siete segmentos, podemos ir un paso ms adelante recurriendo a un circuito integrado como el 4056:

En este circuito integrado, las entradas BCD estn en las terminales 2, 3, 4 y 5; y las salidas que son conectadas directamente a cada uno de los siete segmentos del indicador numrico LED estn puestas desde la terminal 9 hasta la 15. Otra alternativa al circuito integrado 4056 es el ms reciente 4511:

Este decodificador 4511 es capaz de almacenar el nmero BCD puesto en su entrada, retenindolo en su memoria interna hasta que se le introduzca otro nmero BCD. Para que el circuito integrado "recuerde" el nmero binario puesto a su entrada, es necesario activar la terminal 5 (latch enable) con un "1". (Los registros identificados en el diagrama del circuito como "latches" no son otra cosa ms que cuatro elementos de memoria conocidos como "flip-flops D" que sern estudiados en un captulo posterior, empleados para el almacenamiento de cada uno de los cuatro bits de la palabra BCD.) La terminal de "blanqueo" 4 (blanking input), la cual est complementada, normalmente tiene un "1" puesto en ella; si queremos que todos los segmentos luminosos del indicador LED se apaguen entonces ponemos un "0" en esta terminal. La terminal 3 (lamp test), la cual tambin est complementada, normalmente tiene un "1" puesto en ella; si queremos que todos los siete segmentos luminosos del indicador LED se enciendan sin importar la palabra BCD que est almacenada en el circuito integrado entonces ponemos un "0" en esta terminal. Todos los circuitos integrados mencionados en este problema pertenecen a la familia de circuitos lgicos fabricados con tecnologa CMOS. PROBLEMA: Se desea construr un indicador luminoso de siete segmentos hecho a base de diodos emisores de luz (LED) rojos como el mostrado en la siguiente figura:

el cual indicar en forma decimal el nmero binario que se le aplique al decodificador lgico que se encargar de convertir el nmero binario en el encendido apropiado de segmentos. Constryase la Tabla de Verdad del decodificador requerido considerando que un pulso de voltaje enciende al LED y la ausencia del mismo lo deja apagado. Identificando al pulso de voltaje con un 1 y a la ausencia del mismo con un 0, tenemos entonces la siguiente Tabla de Verdad:

Ntese que para una palabra binaria de 4 bits, hay seis estados (los seis ltimos en la tabla de verdad) que no se pueden representar en el indicador luminoso por la naturaleza del mismo. Estos estados se llaman redundancias. Para poder decodificar apropiadamente un nmero binario grande con este tipo de segmentos, hay que convertir el nmero binario puro a su equivalente en sistema BCD, en el cual se pueden usar directamente este tipo de indicadores basados en segmentos de diodos LED. En el siguiente dibujo animado, tenemos el el indicador luminoso numrico y debajo del mismo la palabra binaria BCD que se le est alimentando, en conteo ascendente, con la secuencia binaria aumentando en magnitud de derecha a izquierda (ampliar imagen para poder ver la accin animada en caso de que el navegador no la muestre dentro de la pgina):

PROBLEMA: Un diseista presenta el siguiente circuito como un decodificador. Verificar si dicha aseveracin es falsa o cierta.

El primer paso para resolver este problema es construr una Tabla de Verdad para el circuito mostrado. No es difcil comprobar, por ejemplo, que para la entrada A2A1=01nicamente la salida X ser activada con un "1". Del mismo modo, trazando el flujo de seales para todas las combinaciones posibles de unos y ceros a la entrada del circuito, tenemos la siguiente Tabla de Verdad:

Puesto que para la combinacin de unos y ceros a la entrada, solamente una terminal a la salida es activada a la vez, se concluye que el circuito es efectivamente un decodificador. PROBLEMA: Analizar el siguiente circuito construyendo una Tabla de Verdad para el mismo. Solamente una entrada puede estar activada a la vez.

La Tabla de Verdad para este circuito ser la siguiente:

Se puede apreciar en la Tabla de Verdad que el circuito "convierte" los nmeros decimales en las terminales de entrada a su equivalente en sistema binario en las terminales de salida. Circuitos de este tipo reciben el nombre de codificador (encoder), y su funcin es la opuesta del decodificador. Las aplicaciones de este circuito son innumerables. Cada terminal, por ejemplo, puede representar una tecla numrica de una calculadora electrnica, con la cual se puede ir introduciendo informacin en forma binaria a la calculadora para su procesamiento subsecuente. PROBLEMA: La siguiente unidad, conocida comnmente como unidad multiplex (MUX) permite nicamente la salida de uno de los cuatro canales de informacin de entrada. El canal deseado es seleccionado usando la palabra binaria A1A0 como selector. Cul es su configuracin interna?

La configuracin interna debe ser algo como lo que se muestra a continuacin:

Es frecuente representar un bloque MUX de la siguiente manera:

La unidad MUX es tambin conocida como Selector de Datos (en ingls, Data Selector). El Selector de Datos est especificado por la salida (o salidas) disponible de un nmero n de entradas. En el caso que acabamos de ver, tenemos un Selector de Datos 1-de-4, porque en cualquier momento dado se puede seleccionar una de las cuatro entradas para ser canalizada hacia afuera a travs de la lnea de salida (Output). Existen varios tipos de circuitos integrados disponibles comercialmente para este propsito, como el circuito integrado TTL 74150:

que contiene un Selector de Datos 1-de-16, o como el circuito integrado TTL 74157 que contiene cuatro Selectores de Datos 1-de-2, o como el circuito integrado TTL 74153 que contiene dos Selectores de Datos 1-de4, o como el circuito integrado TTL 74151 que contiene un Selector de Datos 1-de-8, estos tres ltimos con la siguiente relacin de terminales "pins":

Funcionalmente, el Selector de Datos 1-de-2, como los cuatro que contiene el circuito integrado 74157, puede considerarse constitudo de la siguiente manera en su interior (el circuito lgico de la izquierda y el circuito

lgico de la derecha son equivalentes, la nica diferencia es que el circuito lgico de la derecha est constitudo con bloques NAND que son ms fciles de implementar directamente en la microelectrnica que los bloques OR y AND):

Como lo indica la Tabla de Verdad, cuando la terminal selectora (S)elect tenga puesto un "0" entonces dejar pasar el valor que tenga en la terminal D0, ya sea "0" "1", mientras que cuando la terminal selectora tenga puesto un "1", entonces dejar pasar el valor que tenga en la terminal D2. En el caso del circuito integrado 74157, slo se requiere una terminal selectora, que en este caso es la terminal SELECTAB (en el "pin" 1 del circuito integrado), la cual se usa para seleccionar un bit de la seal A (por ejemplo, 1A, en la terminal 2 del circuito integrado) o de la seal B (1B, en la terminal 3 del circuito integrado) canalizndolo hacia afuera a travs de la terminal Y correspondiente del circuito integrado (1Y, en el "pin" 4). La accin de la terminal selectora afecta a todos los cuatro bits de las palabras A y B por igual. De este modo, este circuito es capaz de escoger entre los cuatro bits de la palabra A o los cuatro bits de la palabra B envindolos al mismo tiempo (en forma paralela) hacia afuera. En lo que respecta al circuito integrado 74153, uno de los cuatro valores binarios posibles que pueda tener la palabra selectora S1S0 canalizar hacia la salida ZA (terminal 7) uno de los cuatro bits a la entrada en I0A, I1A, I2A I3A; y al mismo tiempo canalizar hacia la salida ZB (terminal 9) uno de los cuatro bits a la entrada en I0B, I1B, I2B I3B. Y en el caso del circuito integrado 74151, slo se admite una sola palabra binaria de ocho bits a la entrada, y en un momento dado solo uno de los bits es canalizado hacia afuera (por la terminal de salida Z) dependiendo de los valores binarios que tenga la palabra selectoraS2S1S0 . Podemos interactuar con las distintas combinaciones posibles de este ltimo circuito integrado a travs del programa interactivo visual mantenido por la Universidad de Hamburgo en Alemania, a travs del siguiente enlace (se requiere que la computadora est habilitada con el programa accesorio Java): http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos _______/10-gates/40-mux-demux/SN74151.html PROBLEMA: Para construr un circuito lgico de tres entradas A, B y C, que tenga la siguiente Tabla de Verdad:

en lugar de construrlo a partir de las tres funciones lgicas bsicas se desea utilizar un circuito integrado Selector de Datos obtenible a bajo costo en el mercado, en el cual las lneas selectoras S0, S1 y S2 se utilizarn como las entradas A, B y C, y las lneas de datos se activarn de modo fijo con "unos" y "ceros". Resolver este problema usando: 1) Un Selector de Datos 1-de-8 2) Un Selector de Datos 1-de-4 1) Usando un selector de datos 1-de-8, la solucin es directa:

Segn se puede ver, al tomar la entrada ABC la condicin "000", el primer valor en la lista "1" pasa a la salida. Al tomar ABC la condicin "001", el segundo valor "1" en la lista pasa a la salida. Y as sucesivamente. Obsrvese que los valores sucesivos que deber tener la salida siguiendo un conteo binario ascendente en las entradas selectoras fueron tomados directamente de la Tabla de Verdad. 2) Para llevar a cabo una simplificacin con la cual podamos utilizar un Selector de Datos ms sencillo que tenga nicamente dos entradas selectoras, agrupamos primero pares iguales sucesivos de B y C y comparamos la salida de cada par con los valores que debe tomar A a la entrada segn la Tabla de Verdad:

Aqu la salida siempre ser "1" independientemente del valor que tome la entrada A.

En este caso podemos ver que la salida es el complemento (el inverso lgico) de la entrada A.

En este caso, la salida siempre ser "0" no importando el valor que tome A.

Aqu la salida tomar el mismo valor que tome la entrada A. Tomando en cuenta lo anterior, usando un Selector de Datos 1-de-4 el diseo tomar el siguiente aspecto:

o ms concretamente, en el diseo final:

Obsrvese lo sencillo y econmico que resulta disear circuitos lgicos usando un Selector de Datos. El procedimiento empleado en el presente problema se puede extender a ms variables sin dificultad alguna.

Aunque un Selector de Datos 1-de-16 como el circuito integrado TTL 74150 es ms caro que un Selector de Datos 1-de-4 como el circuito integrado TTL 74151, la diferencia en costo quiz no sea tanta para justificar irse al diseo ms econmico como lo hicimos en este caso simplificando el diseo de modo de requerir un Selector de Datos 1-de-4 en lugar de un Selector de Datos 1-de-8, tomando en cuenta que la lgica detrs del diseo simplificado ser ms difcil de leer para los tcnicos que le darn mantenimiento a un equipo utilzando el diseo simplificado. Por otro lado, si se van a producir decenas de miles de equipos que sern puestos a la venta en el mercado, entonces una diferencia de precio de unos cuantos centavos entre un circuito integrado y otro puede traducirse en un ahorro significativo de varios miles de dlares. PROBLEMA: La siguiente unidad, conocida comnmente como como unidaddemultiplex (DMUX) enva la informacin puesta a su entrada nicamente a uno de los cuatro canales de salida.

El canal deseado es seleccionado usando la palabra binaria A1A0 como selector. Cul es su configuracin interna? Extender el diseo para una unidad demultiplex que pueda ser capaz de enviar su entrada a uno de ocho canales de salida. La configuracin interna es como la que se muestra a continuacin:

La accin de "switcheo" requerida del bloque DMUX es esencialmente la siguiente:

Una forma de representar la configuracin interna de la unidad DMUX en donde sigue existiendo la presencia

interna de un "decodificador" de S1S0 aunque de una manera no tan obvia es la siguiente:

En esta representacin, se sigue llevando a cabo una decodificacin de la palabra binariaS1S0 convirtindola en una de cuatro lneas independientes para cada una de las cuatro combinaciones de "unos" y "ceros" puesta en S1S0, con el propsito de permitir el paso por solo uno de los cuatro bloques AND en un momento dado. Sin embargo, puesto dentro de una "caja negra", este circuito es enteramente equivalente al anteriormente mostrado. Este ltimo diseo puede ser extendido para manejar ocho canales de salida con la adicin de una terminal selectora adicional S2 con la cual la palabra selectora ser S2S1S0, y la adicin de cuatro bloques AND adicionales tambin de tres entradas cada uno (ampliar imagen):

Una forma de representar simblicamente a una bloque demultiplex DMUX en los diagramas esquemticos que conlleva la idea de lo que est realizando (una funcin opuesta a la funcin realizada por el bloque MUX)

es de la siguiente manera:

PROBLEMA: Describir el funcionamiento conjunto de una unidad multiplex con una unidad demultiplex. En la vida real, invariablemente cuando en un sistema se usa una unidad multiplexora MUX es porque ir apareada siempre con una unidad demultiplexora DMUX, y ambas debern trabajar de modo conjunto a travs del selector que actuar al mismo tiempo y en formasincronizada sobre ambas unidades MUX y DMUX de la siguiente manera:

La razn obvia para tener que recurrir a una operacin combinada MUX-DMUX es porque frecuentemente es necesario enviar (o recibir) informacin proveniente de diversos equipos cuando slo hay un canal de comunicacin disponible para la transmisin digital. Un ejemplo de esto lo seran varias computadoras conectadas desde un mismo lugar a Internet, compartiendo una sola lnea telefnica. Como la informacin digital de varias computadoras no puede ser enviada al mismo tiempo por un solo canal de comunicacin, el tiempo disponible del canal es "repartido" en partes iguales, dndole un tiempo breve a la computadora # 1, tras lo cual se le d un tiempo breve a la computadora # 2, y as sucesivamente, tras lo cual vuelve a comenzar una nueva ronda dndosele un tiempo breve a la computadora # 1 seguida por la computadora # 2, y as sucesivamente. Desde el punto de vista de la unidad multiplexora MUX, la informacin ir saliendo de una manera como se muestra a continuacin:

Esquemticamente, en este circuito lo primero en salir, lo primero en ser puesto en la nica lnea disponible para la transmisin externa de los datos, es el primer dato "A" representado por un tringulo rojo en el extremo superior izquierdo, el primer dato en el primer canal de comunicacin. Tras esto, se enva a travs de la lnea el segundo dato "B" representado por el primer paralelogramo verde tomado del segundo canal de comunicacin , el primer dato en el segundo canal de comunicacin. A esto le sigue el dato "C" tomado del tercer canal de comunicacin identificado con un crculo azul. Por ltimo, se enva un dato "D" tomado del cuarto canal de comunicacin, representado con un rombo color magenta, tras lo cual el ciclo empieza de nuevo. Obsrvese cmo marchan "aparentemente" revueltos los datos a travs de la nica lnea disponible para la transmisin externa de datos. Para obtener algn sentido de los datos que estn siendo enviados, el receptor tiene que estar forzosamente sincronizado con el envo de los datos. Es por ello que los selectores del MUX y del DMUX tienen que estar conectados de alguna manera, para ir ruteando (routing) la informacin por los canales adecuados sin que haya posibilidad de que termine revuelta. La accin sincronizada selectora MUX-DMUX se muestra bosquejada en el siguiente archivoGIF (ampliar imagen para poder ver la accin animada):

PROBLEMA: La Tabla de Verdad de un circuito electrnico muestra los siguientes valores de voltaje, tanto para las entradas A y B como para la salida producida. Qu funcin desempea el circuito en lgica positiva? Qu funcin desempea en lgica negativa?

Usando lgica positiva, asignamos al voltaje ms pequeo (o ms cerca de cero volts, o el ms negativo) el valor de "0" y al voltaje mayor (en este caso 3.2 volts) el valor de " 1":

Esta es una funcin NOR. Usando lgica negativa, asignamos al voltaje mayor el valor de "0" y al voltaje ms pequeo el valor de "1", o sea lo contrario que lo que hicimos anteriormente:

Esta es una funcin NAND. PROBLEMA: El circuito mostrado a continuacin recibe el nombre de "compuerta" en un sentido diferente al que frecuentemente se les d a los bloques lgicos AND, OR y NOT. Qu accin se lleva a cabo de acuerdo con el valor que tome la terminal T?

Dada la accin de las funciones AND, cuando la terminal T toma el valor "0", la salida de la compuerta es "000000". Cuando la terminal T toma el valor "1", la salida de la compuerta es A6A7A5A4A3A2A1. Esto es, la terminal T est actuando como un gatillo que detiene o permite el paso de la informacin segn el valor que adquiera. Supngase que A6A7A5A4A3A2A1 = 100110 Entonces tendramos los siguientes casos:

PROBLEMA: Analizar el siguiente circuito construyendo una Tabla de Verdad para el mismo.

En el anlisis de este tipo de circuitos, resulta conveniente buscar aquellas combinaciones de entradas que siempre produzcan un resultado consistente independientemente de los valores que tomen las dems entradas. Para ir "llenando" nuestra Tabla de Verdad inicialmente en blanco, podemos llenar toda la columna que corresponde a los valores de la salida I dndonos cuenta de que esta salida est conectada directamente a la entrada D, de modo tal que cuando la entrada D sea "0" la salida E ser tambin "0" y cuando la entrada Dsea "1" la salida E ser tambin "1". Del mismo modo, podemos ver que la accin del AND de tres entradas que proporciona la salida F solo producir un "1" a la salida de F cuando tenemos ABC=100 tanto para D=0 como para D=1, lo cual nos permite llenar toda la columna correspondiente a la salida F de inmediato con "unos" y el resto con "ceros". Asimismo, cuando la entrada A tiene el valor de "1", abriendo con ello la compuerta que representa el AND que proporciona la salida E, basta con que cualquiera de las entradas B C tengan el valor de "1" para que la salida E tenga tambin un "1", y solo cuando ambas entradas tengan un valor de "0" la salida ser "0". Puesto de otra manera, todas las combinaciones para las cuales A=1 y B=1 "encienden" la salida E, y todas las combinaciones para las cuales A=1 y C=1 tambin "encienden" la salida E. Cuando ambas entradas B y Csean "0" la salida E siempre ser "0". En lo que respecta a la salida G, esta requiere que la entrada B sea "1" y que adems A sea "0" o que C sea "1" para que la salida G se "encienda" con un "1". Y en lo que respecta a la salida H, esta ser "1" nicamente cuando las entradas A y Ctengan el valor AC=01 (por la accin del primer AND que alimenta al OR de la salida I) o cuando las entradas A, B y C tengan el valor ABC=110 (por la accin del segundo AND que alimenta al OR de la salida I), siendo "0" en todos los dems casos. As podemos ir llenando una Tabla de Verdad sin necesidad de tener que ir considerando individualmente cada combinacin posible de "unos" y "ceros" a la entrada, con lo cual eventualmente podemos tener la siguiente Tabla de Verdad terminada:

Comparando la entrada ABCD al circuito (tomando las entradas juntas como una palabra binaria) con la salida EFGHI, observamos una cosa muy interesante: la salida del circuito es idntica a la entrada desde ABCD=0000 hasta ABCD=1001 (lo cual es un conteo binario ascendente), tras lo cual desde ABCD=1010 en adelante la salida empieza a "contar" nuevamente en forma binaria ascendente partiendo otra vez desde "cero". Puesto de otra manera, la salida nos est dando el nmero binario puesto a la entrada convertido a su equivalente en sistema BCD. Si conectramos la palabra FGHI a una cartula decimal numrica (usando un decodificador como el descrito en un problema anterior), estaramos leyendo en nuestro sistema decimal el equivalente del nmero binario puesto a la entrada. La salida E cuando se "enciende" con un "1" es la que se utiliza para indicar que estamos en un nuevo conteo decimal, y se podra utilizar tambin para "encender" un segundo indicador luminoso correspondiente a las decenas de nuestro sistema decimal.Este circuito es un ejemplo de lo que se conoce como un traductor, en este caso un traductor de binario a BCD. PROBLEMA: A continuacin se presenta el diagrama esquemtico de una punta de prueba lgica de construccin econmica que puede ser utilizada para confirmar la presencia de un "0" o de un "1" en un punto cualquiera de un circuito lgico. Explicar el funcionamiento de la misma.

Aunque el diagrama indica que la punta de prueba lgica debe ser alimentada con una fuente de voltaje de +12 volts, en realidad no se requiere una fuente de poder externa independiente, ya que la prctica usual es alimentar estas puntas de prueba tomando energa elctrica del mismo circuito que est siendo analizado. La informacin de entrada a la punta de prueba se encuentra en la punta denominada probe, en la cual se puede poner un "0" o un "1" segn la condicin lgica del punto que est siendo medido. Esta informacin ser puesta a la entrada de un NOR en la terminal # 1 del circuito integrado (IC1a) 4001 que est siendo utilizado para la entrada. Puesto que la otra terminal # 2 del circuito integrado est colocada en el nivel de cero volts, lo cual es un "0" lgico, lo nico que cambiar la salida del NOR ser el valor puesto en su terminal # 1. Si en la

punta "probe" hay un "0" entonces la salida del NOR en su terminal # 3 ser "1", y si en la punta "probe" hay un "1" la salida del NOR ser "0". La terminal de salida # 3 del bloque NOR alimenta una de las terminales de entrada del otro bloque NOR (IC1b), en el cual puesto que su otra entrada est conectada a 0 volts est siendo utilizado simplemente como un inversor lgico de la seal enviada por el NOR que le precede. Siguiendo la ruta de valores binarios, si el valor en "probe" es "0", la salida del NOR a la derecha ser tambin un "0", lo cual equivale a poner el punto intermedio entre las resistencias elctricas a cero volts. Esto hace que la corriente elctrica fluya de la fuente de poder a travs del diodo emisor de luz verde LED1 (LO) continuando hacia la terminal de entrada # 4 del bloque NOR (el "0" a la salida del NOR posibilita que la corriente elctrica pueda flur hacia adentro del NOR, ya que la corriente elctrica siempre fluye del polo positivo "1" al polo negativo "0") en vez de flur a travs del diodo emisor de luz LED2 rojo que permanecer apagado. La corriente elctrica estar limitada por la presencia de la resistencia superior de 680 ohms cuyo valor es justo lo que se requiere para que el LED del diseo pueda iluminarse adecuadamente. En esencia, con un "0" a la entrada de "probe", se encender el LED verde indicando una condicin lgica de "0" LO (bajo). La situacin cambia cuando en "probe" est puesto un "1", lo cual hace que tambin en la terminal # 4 del NOR derecho haya un "1" que podemos tomar como esencialmente igual al voltaje de +12 volts. Puesto que ambos extremos del diodo emisor de luz verde LED1 estn ahora al mismo potencial elctrico de +12 volts, no puede flur corriente alguna a travs del LED verde, el cual estar apagado. En cambio, este "1" estar poniendo un voltaje de +12 volts al diodo emisor de luz rojo LED2, el cual al estar conectado del otro lado al potencial de cero volts tendr una diferencia de voltaje de 12 volts aplicada entre sus dos terminales, lo cual har que el LED2 conduzca con la corriente elctrica limitada por la resistencia de 680 ohms justo a lo que se requiere para que el LED pueda iluminarse adecuadamente. En esencia, con un "1" a la entrada de "probe", se encender el LED rojo indicando una condicin lgica de "1" HI (alto) en el punto que est siendo medido.

You might also like

- Simbología y AplicacionesDocument10 pagesSimbología y AplicacionespolicomiNo ratings yet

- Promodel Ejercicio 1Document13 pagesPromodel Ejercicio 1Richie' ZarateNo ratings yet

- Tema 3 Ao PDFDocument8 pagesTema 3 Ao PDFJorge SGNo ratings yet

- Clase2 IIDocument43 pagesClase2 IIAldahir Garcilazo RomeroNo ratings yet

- Lab 1-3 Amp Clase B AbDocument25 pagesLab 1-3 Amp Clase B AbAlex ArévaloNo ratings yet

- S12.s2 OPAMP Problemas Utp - PDF - ShareDocument10 pagesS12.s2 OPAMP Problemas Utp - PDF - ShareVictor RaulNo ratings yet

- Rectificadores y Fuentes de Alimentación - CompletoDocument50 pagesRectificadores y Fuentes de Alimentación - CompletoJaja LocoNo ratings yet

- Labo 2 - Control DigitalDocument20 pagesLabo 2 - Control DigitalDavid JPNo ratings yet

- 1Clase-Control-Digital 2023-1Document56 pages1Clase-Control-Digital 2023-1Walter Ruiz PorrasNo ratings yet

- L5-Filtro Por CondensadorDocument5 pagesL5-Filtro Por CondensadorLuis Diego Cuzcano RomoNo ratings yet

- Introduccion Al Control Digital - 2011-2012Document47 pagesIntroduccion Al Control Digital - 2011-2012Markos UribeNo ratings yet

- 4-Presentación Muestreador y RetenedorDocument33 pages4-Presentación Muestreador y RetenedorMARIANONo ratings yet

- S11.s1-Representacion de Variables de EstadoDocument28 pagesS11.s1-Representacion de Variables de EstadoAntonio CamiloagaNo ratings yet

- Ejercicio de Promodel Resuelto Con ResultadosDocument11 pagesEjercicio de Promodel Resuelto Con ResultadosDanielNo ratings yet

- Transistores BJTDocument21 pagesTransistores BJTJose100% (1)

- Lab04 Decodificador Display 7segDocument5 pagesLab04 Decodificador Display 7segLC LyonNo ratings yet

- Guia de Problemas Electronica IDocument37 pagesGuia de Problemas Electronica IAntonio Jose Perez ZambranoNo ratings yet

- Teoria de ColasDocument74 pagesTeoria de ColasMateo Orrillo100% (1)

- Practica - 1 Sis Digis 2Document7 pagesPractica - 1 Sis Digis 2Mathy MerinoNo ratings yet

- S01.s1 - Introducción A Los Sistemas de Control DigitalDocument33 pagesS01.s1 - Introducción A Los Sistemas de Control DigitalSteve NuñezNo ratings yet

- Amplificador Clase B ABDocument8 pagesAmplificador Clase B ABsantiagoNo ratings yet

- Unidad 1 Control DigitalDocument13 pagesUnidad 1 Control DigitalEdmundo R. NeriaNo ratings yet

- Ejercicios Control DigitalDocument3 pagesEjercicios Control DigitalRomel PorrasNo ratings yet

- Las Variables de EstadoDocument4 pagesLas Variables de EstadoORLANDO RODRIGUEZNo ratings yet

- Capitulo9 CircuitosLogicosDocument13 pagesCapitulo9 CircuitosLogicosRonald Requejo SamameNo ratings yet

- Clase 9 - Variables de EstadoDocument52 pagesClase 9 - Variables de EstadoYubert Edisson Huanca LimaNo ratings yet

- Clase 16Document22 pagesClase 16Arturo Tadeo Calderón SalazarNo ratings yet

- S3-Invope 2Document18 pagesS3-Invope 2Zaira HurtadoNo ratings yet

- Elec Clase 2Document26 pagesElec Clase 2Celeste SantanderNo ratings yet

- LAB N°1 Amplificadores (1) - 2Document9 pagesLAB N°1 Amplificadores (1) - 2Harold Joel Zurita LinaresNo ratings yet

- Amplificadores de Potencia IDocument34 pagesAmplificadores de Potencia IJuan Manuel MuñozNo ratings yet

- Clase 5, Modelos en Variables de EstadoDocument28 pagesClase 5, Modelos en Variables de EstadoCarlos GarayNo ratings yet

- Amplificador Clase BDocument5 pagesAmplificador Clase Bjosebroce4No ratings yet

- 04a - Programacion Dinamica DeterministicaDocument6 pages04a - Programacion Dinamica DeterministicaKevin Flores AlvarezNo ratings yet

- Amplificadores Clase ADocument6 pagesAmplificadores Clase ALuis AndreNo ratings yet

- Voltaje de Rizado para Un Filtro CDocument8 pagesVoltaje de Rizado para Un Filtro CCarlos BenavidesNo ratings yet

- Leccion 4 El DiodoDocument45 pagesLeccion 4 El DiodoAnibal Muñiz SilvaNo ratings yet

- Laboratorio 2Document19 pagesLaboratorio 2Antony Jose Borbon OspinoNo ratings yet

- Diodos PDFDocument14 pagesDiodos PDFElmer QueaNo ratings yet

- Clase 6 Espacio de Estados PLDocument30 pagesClase 6 Espacio de Estados PLBRYAN FABIAN SIMBA�A FERNANDEZNo ratings yet

- Amplificador Clase ABDocument3 pagesAmplificador Clase ABKorange IkaNo ratings yet

- Tabla de Modelos MatematicosDocument8 pagesTabla de Modelos MatematicosKevinJulianPerezTovillaNo ratings yet

- Resistencia EléctricaDocument29 pagesResistencia EléctricaHernan QuishpeNo ratings yet

- Tecnica de Control Digital IDocument68 pagesTecnica de Control Digital Ijlb1212No ratings yet

- IO - Semana 08Document149 pagesIO - Semana 08Andre AlegreNo ratings yet

- Elec Clase 3Document31 pagesElec Clase 3Celeste SantanderNo ratings yet

- S04.s1 - Filtros Por CondensadorDocument16 pagesS04.s1 - Filtros Por CondensadorAlejandro HigaNo ratings yet

- Filtro de CondensadorDocument3 pagesFiltro de CondensadorWilson daniel castroNo ratings yet

- Laboratorio 1Document14 pagesLaboratorio 1Anderson LopezNo ratings yet

- Evaluacion de Xiomara VogelDocument23 pagesEvaluacion de Xiomara VogelMilena ReyesNo ratings yet

- Filtro de CondensadorDocument6 pagesFiltro de CondensadorJose L Huaman GasparNo ratings yet

- Rectificador de Media Onda Con Filtro Por CondensadorDocument14 pagesRectificador de Media Onda Con Filtro Por CondensadorMarco Antonio Challa ChoqqueNo ratings yet

- Diodo de PotenciaDocument69 pagesDiodo de PotenciaMichael R. ArayaNo ratings yet

- s05 s14 MaterialDocument26 pagess05 s14 MaterialEdison Lujan vicañaNo ratings yet

- Investigacion CAD, CAE, CAMDocument3 pagesInvestigacion CAD, CAE, CAMEmmanuel BravoNo ratings yet

- Ejemplo Problema de TransporteDocument2 pagesEjemplo Problema de TransporteMarianellaTellezLazaroNo ratings yet

- S03.s3 - Material BDocument16 pagesS03.s3 - Material BFlor Gamarra QuispeNo ratings yet

- S02.s1 Material ACCC 1Document32 pagesS02.s1 Material ACCC 1Segundo Estela CubasNo ratings yet

- Fundamentos de Lógica Digital - 2 - Problemas ResueltosDocument32 pagesFundamentos de Lógica Digital - 2 - Problemas ResueltosKarlosMorrisonNo ratings yet

- Informe Previo 5 Casimiro UnmsmDocument15 pagesInforme Previo 5 Casimiro UnmsmFreddy Ipanaqué CastilloNo ratings yet

- E Structur AsDocument9 pagesE Structur AsMarcos AlfaroNo ratings yet

- Arreglo SDocument6 pagesArreglo SMarcos AlfaroNo ratings yet

- Java ScriptDocument2 pagesJava ScriptMarcos AlfaroNo ratings yet

- Tratado de Peru BoliviaDocument2 pagesTratado de Peru BoliviaVan SanchezNo ratings yet

- JDBCDocument11 pagesJDBCneoslayferNo ratings yet

- JDBCDocument11 pagesJDBCneoslayferNo ratings yet

- Ejercicios: Operaciones AritméticasDocument6 pagesEjercicios: Operaciones AritméticasMarcos AlfaroNo ratings yet

- 03 Guiados ListasDocument4 pages03 Guiados Listasanonimato777No ratings yet

- Sistema Dig Intro001Document6 pagesSistema Dig Intro001Marcos AlfaroNo ratings yet

- FirewallDocument3 pagesFirewallMarcos AlfaroNo ratings yet

- Circuitos Combinacionales: Santiago Flores Arturo Equipo 5Document7 pagesCircuitos Combinacionales: Santiago Flores Arturo Equipo 5Arturo Santiago FloresNo ratings yet

- Franco Emanuel Chapilliquen Vasquez - Lab 2-2023-2 - Circuitos Digitales - Sistemas de Numeracion y Codigos BinariosDocument2 pagesFranco Emanuel Chapilliquen Vasquez - Lab 2-2023-2 - Circuitos Digitales - Sistemas de Numeracion y Codigos BinariosYULIANA SORIA AVALOSNo ratings yet

- Introduccion A La InformaticaDocument64 pagesIntroduccion A La InformaticaadrfgfNo ratings yet

- 3 Unidad IIDocument65 pages3 Unidad IIMain Caro VelascoNo ratings yet

- Sumador Restador de 4bitsDocument14 pagesSumador Restador de 4bitsgreomerNo ratings yet

- Práctica 1 Circuitos CombinatoriosDocument3 pagesPráctica 1 Circuitos CombinatoriosJavierNo ratings yet

- Practica 5Document25 pagesPractica 5Renato Beltran CaceresNo ratings yet

- Escuela Politécnica Nacional: Tesis Previo A La Obtención Del Titulo de Ingeniero en Electrónica Y TelecomunicacionesDocument150 pagesEscuela Politécnica Nacional: Tesis Previo A La Obtención Del Titulo de Ingeniero en Electrónica Y TelecomunicacionesAlexis NavarroNo ratings yet

- DigitalesDocument16 pagesDigitalesPame CondoyNo ratings yet

- Circuito TTL 7447Document3 pagesCircuito TTL 7447Alvaro Daniel CandiaNo ratings yet

- Simbologia ElectrónicaDocument29 pagesSimbologia Electrónicadiamante kiraNo ratings yet

- Texto Control Electronica 2109 UNIT 1Document20 pagesTexto Control Electronica 2109 UNIT 1Alex Sandro Flores HualpaNo ratings yet

- Cebek CD-28 PDFDocument52 pagesCebek CD-28 PDFibor747No ratings yet

- Práctica 1Document30 pagesPráctica 1Mauricio RodriguezNo ratings yet

- Grupo 4 - Und 4Document15 pagesGrupo 4 - Und 4SaulThe badboyNo ratings yet

- CED-ISW-B3-Circuitos Combinacionales-12-13Document6 pagesCED-ISW-B3-Circuitos Combinacionales-12-13Dayana Ordóñez BerronesNo ratings yet

- Floyd - Capítulo 2Document65 pagesFloyd - Capítulo 2PatriciaNo ratings yet

- Decodificador BCD A DecimalDocument3 pagesDecodificador BCD A DecimalAncelMedinaNo ratings yet

- Circuitos Combinacionales - Sesion 2Document22 pagesCircuitos Combinacionales - Sesion 2Luis AlbertoNo ratings yet

- SistemasDeCodificacion PDFDocument26 pagesSistemasDeCodificacion PDFesterNo ratings yet

- S09.s1 - MaterialDocument38 pagesS09.s1 - Materialjose miguel castillo vilcaNo ratings yet

- Club 179Document86 pagesClub 179William PadillaNo ratings yet

- Oscilador Digital de Frecuencia ProgramableDocument11 pagesOscilador Digital de Frecuencia ProgramableCalinhosBaoNo ratings yet

- Circuitos CombinacionalesDocument27 pagesCircuitos CombinacionalesHenry TipanNo ratings yet

- Pic DiscoveryDocument82 pagesPic DiscoverygermanNo ratings yet

- Guia Laboratorio 2Document3 pagesGuia Laboratorio 2HannamilleDelRosarioNo ratings yet

- Silabo Sistemas Digitales 2022-2Document5 pagesSilabo Sistemas Digitales 2022-2John Emerson RodrigoNo ratings yet

- Siglas Abreviaturas Terminos Comunes CAD-CAMDocument87 pagesSiglas Abreviaturas Terminos Comunes CAD-CAMJaime GuzmanNo ratings yet

- Cobol 1-Lenguaje de ProgramaciónDocument79 pagesCobol 1-Lenguaje de Programaciónkorn1501No ratings yet