Professional Documents

Culture Documents

Parallel Implementation of A 4 X 4-Bit Multiplier

Uploaded by

Mathew GeorgeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Parallel Implementation of A 4 X 4-Bit Multiplier

Uploaded by

Mathew GeorgeCopyright:

Available Formats

1010

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL.

23, NO. 4, AUGUST 1988

Correspondence

Parallel Implementation of a 4 X 4-bit Multiplier Using Modified Booths Algorithm

NARESH

R.S W N B H A G , STUDENT MEMBER, IEEE, AND

PUSHKAL JUNETA

Abstract-Presented in this paper is a design of a 4x4-bit multiplier using the modified Booths algorithm in Z p m NMOS technology. The main features of this chip are its 62.5-MHz operating frequency and 31.5-mW power dissipation. The chip occupies an area of 1.37 m d . A novel adder-cum-subtractor (ACS) circuit was designed to realize the arithmetic processing part.

I. INTRODUCTION Multiplier chips are undeniably a crucial component of any digital signal processing system. Hence the utility of a multiplier chip cannot be understressed. as it is We have employed a 2-pm NMOS design parameter [l] widely used nowadays. Parallel implementation was resorted to in order to increase the speed of computation. A serial realization was attempted earlier for an 8x8 multiplier and it was found that five clock pulses were required to compute the result. Parallel realization, on the other hand, requires just one clock pulse to generate the result. The inputs and the output of the chip are in signed magnitude form. While incorporating the modified Booths algorithm [2] it was found that the arithmetic processing part involved addition as well as subtraction and hence an adder-cum-subtractor (ACS) module was designed. This module is unique in the sense that addition and subtraction are done without taking the twos complement at any stage. Subsequent cascading of the ACS modules was found to generate the result correctly. This module will be dealt with in greater detail later on.

Fig. 1. System architecture.

It is clear that, except for the first term, the remaining two terms can be expressed individually as 2 multiplied by a function E; where

4 = (-2a,+l + a, + a , - l )

Now, when B is multiplied with A , depending on the value of the function F;, the multiplier B will either have to be shifted left i + 1 or i times and either added or subtracted from the partial result. We also note that for an n x n-bit multiplier N terms have to be evaluated using the modified Booths algorithm, where

N

=

(n +2 ) / 2

11. MODIFIED BOOTHS ALGORITHM

Multiplication of two numbers basically involves multiple shifts of the multiplier and subsequent addition, depending on the bit pattern of the multiplicand. Without using the modified Booths algorithm [2] a maximum of four shifts (for a 4 x 4 multiplier) and four additions are required. On the other hand, through the modified Booths algorithm, a maximum of three terms have to be evaluated and added up. We now elaborate upon the facts given in the previous paragraph. Let A and B be a 4-bit multiplicand and multiplier, respectively. Therefore, A can be written as

A = a , X 2 3 + a,22

This is the reason why the 8xS-bit serial implementation required five clock pulses.

I

1 1 1 . SYSTEM ARCHITECTURE

+ u1 X 2 + a , .

Hence B has to be multiplied with each of the four terms and subsequently added up. For the modified Booths algorithm it can easily be verified that A can also be represented as

A

= u4a3 +2(

-2a,

+ a 2 + ul)+2O( - 2 a 1 + a , + O ) .

Manuscript received October 12, 1987; revised January 4, 1988. The authors are with the Indian Institute of Technology, New Delhi 110016, India. IEEE Log Number 8821661.

The system architecture that we chose inherently simplifies the timing analysis in Section VI because the flow of data is always in one direction, i.e., there are no data feedbacks among any of the modules. Thus we add the individual module delays to get the total system delay. As mentioned before, the final result of the multiplier is the sum of properly shifted versions of B. The extent of the shift is determined by the value of the function E;. Therefore, for all of the terms to be evaluated we note that we have to choose between a shift of i + 1 and i. Hence we decided to multiplex the ( i + 1)th and the ith shifted versions of B. Therefore, in the 4x4-bit case we required three multiplexers. Also two logic blocks, we call them F blocks, were required to generate the control signals for the multiplexers (for choosing the proper shifts) and for the ACS modules (for adding or subtracting the outputs of the multiplexers). As there were three terms to be added/subtracted, we required two ACS modules. These modules will be described in greater detail later. The final system architecture is presented in Fig. 1.

0018-92OO/88/08OO- 1010$01 .OO 01988 IEEE

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 23, NO.

4, AUGUST 1988

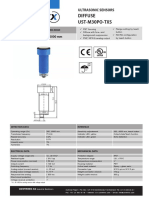

DIFFUSION

POLY

METAL

CONTACT

(4

L

-k

ONO

(b) (4 Fig. 2. Multiplexer details: (a) layout, (b) truth table, and (c) logic diagram.

INPUT

OUTPUT

AA

I

IV. MULTIPLEXERS AND THE F BLOCK

A . Multiplexers

0 0

I I I

There were two 3 x 1 multiplexers on the chip. Two control signals L and L' controlled the generation of the output. In .eality we had one register which acted as a source of two inputs and a ground line as the third. When L' = 1 we get a zero as the multiplexer output irrespective of the status of L. The third multiplexer (2 X 1) selects between a four shift left version of B and zero. The control signal in this case is u3. The layout, the truth table, and the logic diagram are given in Fig. 2.

B. F Block

Fig. 3.

I

I

O

O

0 0

The inputs to the F block are three bits of A and it generates the control signals L , L', and A / S . The function of the first two has already been explained while the third ( A / S ) is a signal to be combined with a similar output of another F block to be given to the ACS in order to convert it to either an adder or a subtractor. The layout, the truth table, and the logic diagram are shown in Fig. 3.

V. ADDER-CUM-SUBTRACTOR MODULE

(b) F-block details: (a) layout, (b) truth table, and (c) logic diagram

4) make the next BP the current BP; 5) transform the current BP to (a,,b,); 6) if U , = 0 then do step 2 onwards; otherwise take the XOR of the bits of the current BP and do step 4 onwards. The algorithm above assumes that for an n-bit subtraction there are (n 1)-bit pairs (including the sign-bit pair) plus a final bit pair which equals (1,O). The actual answer is given by the output of the right-most ( n + 1)-bit pairs. Upon realization of the circuit it was found that one bit slice of the ACS module contained 40 transistors. The design of the XOR gates was done using two pass transistors following the formal design procedure given in [3]. The logic diagram of a bit slice of the ACS module is shown in Fig. 4(a). It also shows the pass-transistor realization of XOR'S. The layout is shown in Fig. 4(b).

As mentioned earlier the arithmetic processing part would require addition as well as subtraction. Thus the ACS module has two modes of operation, one as an adder and the other as a subtractor. At no point is a two's complement required in this application of the ACS, and the final result is in signed magnitude form. The adder is a conventional ripple carry adder while for the subtractor a novel design was implemented. The subtraction algorithm developed is given below. We first of all define a bit pair (BP) as the pair ( U , , b,) of the two operands where B is the subtrahend. The steps are:

1) start from the unit's BP; 2) if the current BP is (0,l) then do step 3 onwards; otherwise take the XOR of the current BP as the output and repeat step 2 for the next BP unless the current BP is the last one; 3) generate 1 as the output of the current BP;

VI. TIMING ANALYSIS

It is quite reasonable to neglect the RC effects of wires if the wire resistance is much smaller than the ON resistance of a MOS transistor [4]. As nowhere on the chip do we have wire lengths greater than 2000X (only then does the wire resistance become comparable to the ON resistance of a MOS transistor), the RC effects were ignored. Thus we modeled the wires as capacitive loads.

1012

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL.

23, NO. 4 .AUGUST 1988

AS

C J i

Oi

a i

bi

Oii

Ozi

A XOR

REALIZATION

&m

(4

Ct

DIFFUSION ... .CONTACT,.

..

(b) Fig. 4. ACS module: (a) logic diagram of bit slice showing pass-transistorrealizationof XORs; and (b) layout.

POLY

......

M E T A L .......

The timing analysis was done by first identifying a critical path passing from the input pads through certain logic blocks to the output pads. This path was quite obvious in our architecture and is shown in Fig. 5. For each of the modules lying in the critical path the delay was estimated and finally added up. If at any stage any module was found to delay the processing by a substantial amount, we identified the exact location of the problem area within the module and redesigned that part. Within the modules themselves the delay was estimated by identifying critical paths. This identification was based on two considerations: 1) the number of gates along the path, and 2) the cumulative length of wires (or output capacitance faced by each gate in the path). The maximum of all the path delays within the module represented the delay of the module as a whole. Delays for each of the modules are tabulated in Table I. It can be seen that the ACS module is responsible for 81 percent of the total delay.

We would like to point out that no layout optimization was carried out on any of the modules and each one of them was a one-go affair. Appreciable reduction in the delays can be expected if such an optimization is carried out.

VII. CONCLUSIONS A multiplier chip using the modified Booths algorithm was designed and simulated. The whole chip contained 250 gates and occupied an area of 1.37 m d . It was designed for a supply voltage of 5 V. The performance of the chip in terms of area and power dissipation is quite comparable to the one given in [SI though it lags far behind in the domain of execution time. The reason for this is the inherently slow NMOS technology and the absence of any layout optimization. Comparison with other multipliers is given in Table 11. The data were culled from [5] and [13].

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 23, NO.

4, AUGUST 1988

1013

REFERENCES

INPUT

--- +CRITICAL

PATH

Fig. 5. Critical path selection.

D E L A Y IN

TABLE I NANOSECONDS

MODULE

REGISTER

F

DELAY

0.961 0.456 1-653

- BLOCK

ACS

6.517

TABLE I1

COMPARISON o t DIFFERENT MULTIPLIERS

~

L. A. Glasser and D. Dobberpuhl, The Design and Analysis of VLSI Circuits. Reading, MA: Addison-Wesley, 1985. 0. L. Mac Sorley, High speed arithmetic in binary computers, Proc. I R E , vol. 49, pp. 67-91, Jan. 1961. D. Radhakrishnan, S. R. Whitaker, and G. K. Maki, Formal design procedures for pass transistor switching circuits, IEEE J. Solid-State Circuits, vol. SC-20, no. 2, pp. 531-536, Apr. 1985. N. Weste and K. Eshraghlan, CMOS VLSI Design. Reading, MA: Addison-Wesley, 1985. E. Delhaye, C. Rocher, J. C. Baelde, J. M. Giabereau, and M. Rocchi. A 2.5-ns, 40-mW. 4 x 4 GaAs multiplier in twos complement mode, IEEE J . Solid-State Circuits, vol. SC-22, no. 3, pp. 409-414, June 1987. Y. Harata, Y. Nakamuya, H. Nagase, M. Takigawa, and N. Takagi, A high-speed multiplier using a redundant binary adder tree, IEEE J. Solid-State Circuits, vol. SC-22, no. 1, pp. 28-34, Feb. 1987. J . Y. Lee, H. L. Garvin, and C. W. Slayman, A high-speed high-density silicon 8 X &bit parallel multiplier, IEEE J. Solid-State Circuits, vol. SC-22, no. 1, pp. 35-40, Feb. 1987. S . Kotani, N. Fujimaki, S. Morohashi, S . Ohara, and S. Hasuo, Feasibility of an ultra-high-speed Josephson multiplier, IEEE J. Solid-State Circuits, vol. SC-22, no. 1, pp. 98-103, Feb. 1987. T. G. Noll, D. Schmitt-Landsiedel, H. Klar, and G . Enders, A pipelined 330-MHz multiplier, IEEE J . Solid-State Circuits, vol. SC-21, no. 3, pp. 411-416, June 1986. Y. Hatano, Y. Harada, K. Yanaashita, Y. Tarutani, and U. Kawabe, A 4-hit x 4-bit multiplier and 3-bit counter in Josephson threshold logic, IEEE J. Solid-State Circuits, vol. SC-22, no. 4, pp. 606-612, Aug. 1987. K. Washio, K. Nakazato, and T. Nakamura, 2.7-11s 8x8-bit parallel array multiplier using sidewall base contact structure, IEEE J . SohdState Circuits, vol. SC-22, no. 4, pp. 613-614, Aug. 1987. M. Hatamian and G. L. Cash, A 70-MHz 8-bitx8-bit parallel pipelined multiplier in 2.5-pm CMOS, IEEE J . Solid-state Circuits, vol. SC-21, no. 4, pp. 505-513, Aug. 1986. K. Gonoi, I. Honbori, M. Wada, K. Togashi, and Y. Kato, A GaAs 8 X 8-bit multiplier/accumulator using JFET DCFL, IEEE J . SolidState Circuits, vol. SC-21, no. 4, pp. 523-529, Aug. 1986.

REERENCE

SNO TIME

I

AREA WWER m(mm9(mrl

I20

I

TECHNOLOGY

16x16

58x63

27um, nEl0 MOS

C61

3

4

I !

1.1

6 % ;

24x2-I

3 1

16x6 8x8

2-5u~JOSEWSON

c.3

I

303

1500

IlOum. NMOS

Implementation of Iterative Networks with CMOS Differential Logic

SHIH-LIEN LU

SlOCS

THOona

When extended to 8~ 8-bit systems we require N ( = 5) F blocks, N - 1 ( = 4) ACS modules, and N ( = 5) multiplexers. Thus we anticipate an increase of 13 ns in the system delay and an increase of 31.9 mW in the total power dissipation. The ACS module accounts for nearly 76.6 percent of the increment in the power dissipation and it is responsible for all of the incremental delay of 13 ns.

Abstract -Differential CMOS logic has many advantages over the static CMOS implemented NAND/NOR logic families. It has the ability to evaluate a complex combinational function in a single gate delay. It also provides high layout density and requires no static power consumption. In this paper we present aq improved differential CMOS logic familyEnabled/disabled CMOS Differential Logic (ECDL). We also present an extension to this logic technique which enables the implementation of iterative networks. Iterative networks are useful in realizing some important logic functions. The simplicity of design, the ease of testing, and the small area-time product make iterative networks a desirable VLSI implementation method of logic functions. Two simple logic functions are implemented to demonstrate this methodology.

I. INTRODUCTION

Differential CMOS logic family has many advantages. Heller

et al. [l] proposed a differential CMOS logic family, cascode

ACKNOWLEDGMENT

The authors would like to acknowledge the constructive criticisms, suggestions, and the whole-hearted encouragement offered by Prof. D. Nagchoudhuri of the Indian Institute of Technology, Delhi. They also wish to thank the reviewers for their helpful suggestions. The heroic efforts of P. Ram, S. M. Pall, and V. S. Rao in the preparation of the manuscript and the figures is appreciated.

voltage switch logic (CVSL). They have shown, with examples, that both n-type and p-type transistor counts are reduced over the two-level NAND/NOR implementation. Since CVSL is capable

Manuscript received October 27, 1987; revised January 26, 1988. This work was supported in part by the Defense Advanced Research Project Agency under Contract MDA903-81-C-0335. The author is with the Information Science Institute, University of Southern California, Marina del Rey, CA 90292 and with the Department of Computer Science, University of California, Los Angeles, CA 90024. IEEE Log Number 8822143.

0018-9200/88/0800-1013$01.00 01988 IEEE

You might also like

- PDFDocument24 pagesPDFOlga Joy Labajo GerastaNo ratings yet

- EDN Design Ideas 2004Document155 pagesEDN Design Ideas 2004chag1956100% (2)

- Title: Multiplexer Instruction AimsDocument5 pagesTitle: Multiplexer Instruction Aimssuv_fame100% (1)

- Final Apr 03 SolnsDocument16 pagesFinal Apr 03 Solnsapi-3755462No ratings yet

- IEEE Carl HamacherDocument4 pagesIEEE Carl HamacherSivakumar SoubrayluNo ratings yet

- CapsaDocument4 pagesCapsasumikannuNo ratings yet

- STLD Unit - Iii (Original Notes)Document70 pagesSTLD Unit - Iii (Original Notes)Saipriya KadiyalaNo ratings yet

- CMOS Based Design Simulation of Adder /subtractor Using Different FoundriesDocument7 pagesCMOS Based Design Simulation of Adder /subtractor Using Different FoundriesRavindra KumarNo ratings yet

- DDDC87ECAA084E5DA4D2D77F7DC80391Document5 pagesDDDC87ECAA084E5DA4D2D77F7DC80391Sameer NandagaveNo ratings yet

- Design of 8 Bit Alu Using Microwind 3.1Document6 pagesDesign of 8 Bit Alu Using Microwind 3.1ijaert100% (1)

- Model QPDocument6 pagesModel QPvlsisivaNo ratings yet

- BE 2008 Electronics&TelecommunicationDocument71 pagesBE 2008 Electronics&TelecommunicationAdib ShaikhNo ratings yet

- Adder Subtractor CircuitsDocument8 pagesAdder Subtractor CircuitsMichael Vincent MonteroNo ratings yet

- Efficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogDocument12 pagesEfficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogAnonymous e4UpOQEPNo ratings yet

- Parity Bit Generator Using 3 Input XOR GDocument6 pagesParity Bit Generator Using 3 Input XOR Gvirat sharma100% (1)

- F Pga Implementation of A Single Precision Floating PointDocument4 pagesF Pga Implementation of A Single Precision Floating PointMohAnVinNo ratings yet

- A Low-Power and High-Performance Radix-4 Multiplier Design Using A Modified Pass-Transistor Logic TechniqueDocument7 pagesA Low-Power and High-Performance Radix-4 Multiplier Design Using A Modified Pass-Transistor Logic TechniquesenthilpariNo ratings yet

- Lab 10Document15 pagesLab 10Jaya Chandra ManchalaNo ratings yet

- Design of A Novel Radix 4 Booth MultiplierDocument4 pagesDesign of A Novel Radix 4 Booth MultiplierKellyLiewNo ratings yet

- Design of Low-Power and High Performance Radix-4 MultiplierDocument4 pagesDesign of Low-Power and High Performance Radix-4 MultiplierAbhishek MatNo ratings yet

- A Vlsi: DSP Chip For Real Time Iterative DeconvolutionDocument4 pagesA Vlsi: DSP Chip For Real Time Iterative DeconvolutionAjinkya DeshmukhNo ratings yet

- Digital Wavelet Decomposition GroupDocument10 pagesDigital Wavelet Decomposition GroupkjnanduNo ratings yet

- Numerically Controlled Oscillator With Spur Reduction: Hans-Jörg Pfleiderer Stefan LachowiczDocument4 pagesNumerically Controlled Oscillator With Spur Reduction: Hans-Jörg Pfleiderer Stefan LachowiczRaffi SkNo ratings yet

- Eeen 810 Final Assignment - 21012012Document5 pagesEeen 810 Final Assignment - 21012012Kabir MohammedNo ratings yet

- Assignment For Applied Electronics - 2014Document3 pagesAssignment For Applied Electronics - 2014Ankush JindalNo ratings yet

- Low Noise AmplifierDocument7 pagesLow Noise AmplifierGautam DhanabalanNo ratings yet

- VLSI Design of Sorting Networks in CMOS TechnologyDocument19 pagesVLSI Design of Sorting Networks in CMOS TechnologyGrissGSNo ratings yet

- Theory Flow Graphs : Feedback - Further SignalDocument7 pagesTheory Flow Graphs : Feedback - Further SignalmeifiusNo ratings yet

- 4 - Bit - Carry - Propagate - Adder PDFDocument32 pages4 - Bit - Carry - Propagate - Adder PDFRennze Dominic DeveraNo ratings yet

- AnalogDocument8 pagesAnalogAhmed F RahimNo ratings yet

- A New Design 6T Full Adder Circuit Using Novel 2T XNOR GatesDocument7 pagesA New Design 6T Full Adder Circuit Using Novel 2T XNOR GatesdycsteiznNo ratings yet

- EE3408E Project Design A Two-Stage Operational AmplifierDocument4 pagesEE3408E Project Design A Two-Stage Operational AmplifierLaSo ASNo ratings yet

- Me3360 HW1-SP2013Document3 pagesMe3360 HW1-SP2013elm391229No ratings yet

- RegelTechniek1 2014Document3 pagesRegelTechniek1 2014John AppleseedNo ratings yet

- GMSK Demodulator Using Costas Loop For Software-Defined RadioDocument5 pagesGMSK Demodulator Using Costas Loop For Software-Defined RadioRanjith ReddyNo ratings yet

- Modified Low-Power and Area-Efficient Carry Select Adder Using D-LatchDocument8 pagesModified Low-Power and Area-Efficient Carry Select Adder Using D-LatchhemanthbbcNo ratings yet

- DD and COmodule 2Document97 pagesDD and COmodule 2Madhura N KNo ratings yet

- Final Question Bank.Document5 pagesFinal Question Bank.arjunjaka6No ratings yet

- 70 72Document3 pages70 72mmmkNo ratings yet

- Design of New Full Adder Cell Using Hybrid-CMOS Logic StyleDocument4 pagesDesign of New Full Adder Cell Using Hybrid-CMOS Logic StyleDaniel CristanchoNo ratings yet

- Barrel ShifterDocument5 pagesBarrel ShifterChunduri SrinuNo ratings yet

- ZucDocument18 pagesZucHui ZhangNo ratings yet

- Optimal Design of A Reversible Full AdderDocument17 pagesOptimal Design of A Reversible Full AdderMohamedNo ratings yet

- Optimal Controller Design of Three-Phase Controlled Rectifier Using Artificial Intelligence TechniquesDocument9 pagesOptimal Controller Design of Three-Phase Controlled Rectifier Using Artificial Intelligence Techniquesankit_elect27No ratings yet

- Review of Linear Time-Invariant (Lti) Multi-Port System TheoryDocument48 pagesReview of Linear Time-Invariant (Lti) Multi-Port System TheoryUtah UtahNo ratings yet

- EESB423 Sem1 1314 Assignment2Document3 pagesEESB423 Sem1 1314 Assignment2Shamraj KunnasagarNo ratings yet

- VLSI Design Overview ProblemsDocument4 pagesVLSI Design Overview ProblemsJorge Ivan Canales VerdialNo ratings yet

- A 5Ghz+ 128-Bit Binary Floating-Point Adder For The Power6 ProcessorDocument4 pagesA 5Ghz+ 128-Bit Binary Floating-Point Adder For The Power6 ProcessorYermakov Vadim IvanovichNo ratings yet

- EEE312 EEE282 Lab4 Spring2015 PDFDocument5 pagesEEE312 EEE282 Lab4 Spring2015 PDFvognarNo ratings yet

- TE 2019 MechatronicsDocument6 pagesTE 2019 MechatronicsVishalNo ratings yet

- Multiplexer-Based Array Multipliers: Kiamal Z. PekmestziDocument9 pagesMultiplexer-Based Array Multipliers: Kiamal Z. Pekmestzisan112358No ratings yet

- Sub-System Design: Designing of Various Arithmetic Building BlocksDocument84 pagesSub-System Design: Designing of Various Arithmetic Building BlocksAdi SaggarNo ratings yet

- Design A Full Adder by Using Two Half Adders. (7M, May-19)Document10 pagesDesign A Full Adder by Using Two Half Adders. (7M, May-19)Sri Silpa Padmanabhuni100% (1)

- A Simple Direct-Torque Neuro-Fuzzy Control of PWM-Inverter-Fed Induction Motor DriveDocument8 pagesA Simple Direct-Torque Neuro-Fuzzy Control of PWM-Inverter-Fed Induction Motor DrivegsmaniprabaNo ratings yet

- 4 - Bit - Carry - Propagate - Adder PDFDocument32 pages4 - Bit - Carry - Propagate - Adder PDFAhmed GadNo ratings yet

- ELX304 Ref ExamDocument13 pagesELX304 Ref ExamNadeesha Bandara0% (1)

- Brent Kung AdderDocument74 pagesBrent Kung AdderVinay ReddyNo ratings yet

- Introduction To Digital System Laboratory PDFDocument32 pagesIntroduction To Digital System Laboratory PDFAdhitya RahmanNo ratings yet

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsFrom EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNo ratings yet

- Design and Implementation of Low Power DSP Core With Programmable Truncated Vedic MultiplierDocument5 pagesDesign and Implementation of Low Power DSP Core With Programmable Truncated Vedic MultiplierMathew GeorgeNo ratings yet

- Estimation of Cubic Nonlinear Bandpass Channels in Orthogonal Frequency-Division Multiplexing SystemsDocument11 pagesEstimation of Cubic Nonlinear Bandpass Channels in Orthogonal Frequency-Division Multiplexing SystemsMathew GeorgeNo ratings yet

- 05983776Document5 pages05983776Mathew GeorgeNo ratings yet

- DyueDocument14 pagesDyueMathew GeorgeNo ratings yet

- Control of A Cascade STATCOM With Star Configuration Under Unbalanced ConditionsDocument14 pagesControl of A Cascade STATCOM With Star Configuration Under Unbalanced ConditionsMathew GeorgeNo ratings yet

- Low Power 6-Transistor Latch Design For Portable DevicesDocument16 pagesLow Power 6-Transistor Latch Design For Portable DevicesjayalakshmisnairNo ratings yet

- Control of A Cascade STATCOM With Star Configuration Under Unbalanced ConditionsDocument14 pagesControl of A Cascade STATCOM With Star Configuration Under Unbalanced ConditionsMathew GeorgeNo ratings yet

- Magic Mirror Table For Social-Emotion Alleviation in The Smart HomeDocument6 pagesMagic Mirror Table For Social-Emotion Alleviation in The Smart HomeMathew GeorgeNo ratings yet

- LISMI Seminar1 Base PaperDocument6 pagesLISMI Seminar1 Base PaperMathew GeorgeNo ratings yet

- Powe Efficient PLLDocument12 pagesPowe Efficient PLLjayalakshmisnairNo ratings yet

- Improved Accuracy Current-ModeMultiplier CircuitsDocument5 pagesImproved Accuracy Current-ModeMultiplier CircuitsjayalakshmisnairNo ratings yet

- Adaptive Streaming of Audiovisual Content Using MPEG DASHDocument8 pagesAdaptive Streaming of Audiovisual Content Using MPEG DASHMathew GeorgeNo ratings yet

- Anu Seminar 1Document9 pagesAnu Seminar 1Mathew GeorgeNo ratings yet

- Implementation of Low Density Parity CheckDocument10 pagesImplementation of Low Density Parity CheckMathew GeorgeNo ratings yet

- USB Receiver/Transmitter For FPGA ImplementationDocument6 pagesUSB Receiver/Transmitter For FPGA ImplementationGuido AvalloneNo ratings yet

- Parallel ProcessingDocument14 pagesParallel ProcessingMathew GeorgeNo ratings yet

- Scalable Architecture For Word HMM-BasedDocument8 pagesScalable Architecture For Word HMM-BasedMathew GeorgeNo ratings yet

- Improved Design of High-Performance Parallel Decimal MultipliersDocument15 pagesImproved Design of High-Performance Parallel Decimal MultipliersMathew GeorgeNo ratings yet

- Multioperand Parallel Decimal Adder: A Mixed Binary and BCD ApproachDocument9 pagesMultioperand Parallel Decimal Adder: A Mixed Binary and BCD ApproachMathew GeorgeNo ratings yet

- Optimal Circuits For Parallel Multipliers: Paul F. Stelling,,, Charles U. Martel, Vojin G. Oklobdzija,,, and R. RaviDocument13 pagesOptimal Circuits For Parallel Multipliers: Paul F. Stelling,,, Charles U. Martel, Vojin G. Oklobdzija,,, and R. RaviMathew GeorgeNo ratings yet

- Co Assignment 2015-16Document2 pagesCo Assignment 2015-16AvinashBitraNo ratings yet

- Building A Processor From ScratchDocument8 pagesBuilding A Processor From Scratchnew accNo ratings yet

- Diffuse Ust-M30Po-Txs: Ultrasonic SensorsDocument9 pagesDiffuse Ust-M30Po-Txs: Ultrasonic SensorsOscar Esau Garcia RajzNo ratings yet

- Ecad & Vlsi Lab Manual - MrecwDocument104 pagesEcad & Vlsi Lab Manual - Mrecwvaseem_ahmedNo ratings yet

- Home Asgn4 BSCS 12ABCDocument2 pagesHome Asgn4 BSCS 12ABCHira SardarNo ratings yet

- DPCO Unit-4Document44 pagesDPCO Unit-4john wickNo ratings yet

- Multiplexer Series: OutlineDocument2 pagesMultiplexer Series: Outlinejohn BronsonNo ratings yet

- Mult and DemultDocument8 pagesMult and Demultkarim mohamedNo ratings yet

- Details of Using SIMULINKDocument54 pagesDetails of Using SIMULINKEngr. Omit DebnathNo ratings yet

- ELEC141Document7 pagesELEC141dazatronNo ratings yet

- TOC From Digital Design Using Digilent FPGA Boards-VerilogDocument5 pagesTOC From Digital Design Using Digilent FPGA Boards-VerilogSmiley CatNo ratings yet

- ASIL D Safety Concept-Assessed High-Speed Traction, Bi-Directional DC/DC Conversion Reference DesignDocument38 pagesASIL D Safety Concept-Assessed High-Speed Traction, Bi-Directional DC/DC Conversion Reference DesignNguyễn Hữu TàiNo ratings yet

- Combinational Logic CircuitsDocument7 pagesCombinational Logic CircuitsYasir ArfatNo ratings yet

- Multiplexer and Demultiplexer (EXPERIMENT-2)Document21 pagesMultiplexer and Demultiplexer (EXPERIMENT-2)SARTHAK VARSHNEYNo ratings yet

- Data Acquisition Systems (DAS) in GeneralDocument3 pagesData Acquisition Systems (DAS) in GeneralArjun SinghNo ratings yet

- Pedroni VHDL 2ed Exercise Solutions v4 PDFDocument37 pagesPedroni VHDL 2ed Exercise Solutions v4 PDFana eht50% (2)

- BU1924Document5 pagesBU1924Laurentiu IacobNo ratings yet

- Unit 3 DCN Lecture Notes 23 45Document41 pagesUnit 3 DCN Lecture Notes 23 45arun kaushikNo ratings yet

- (Total: 80 Marks) INSTRUCTION: Answer ALL QuestionsDocument14 pages(Total: 80 Marks) INSTRUCTION: Answer ALL Questionssyiraa kimNo ratings yet

- Hardware 7300Document206 pagesHardware 7300Claudio SaezNo ratings yet

- DC Lab ManualDocument71 pagesDC Lab ManualVishal NairNo ratings yet

- Max 1718Document35 pagesMax 1718bmmostefaNo ratings yet

- Arduino Plant Monitor: InstructablesDocument9 pagesArduino Plant Monitor: Instructablesguillermo martinNo ratings yet

- Sample Eda Lab (Part-A) Manual: Simulation OutputDocument20 pagesSample Eda Lab (Part-A) Manual: Simulation Outputmdzakir_hussainNo ratings yet

- TLC0834C, TLC0834I, TLC0838C, TLC0838I 8-Bit Analog-To-Digital Converters With Serial ControlDocument14 pagesTLC0834C, TLC0834I, TLC0838C, TLC0838I 8-Bit Analog-To-Digital Converters With Serial ControlTânia RodriguesNo ratings yet

- STM32 DMAMUX: The DMA Request Router: Application NoteDocument14 pagesSTM32 DMAMUX: The DMA Request Router: Application NoteVladNo ratings yet

- Catalog KNXDocument152 pagesCatalog KNXPopescu ConstantinNo ratings yet

- Chap 6 Functions of Combinational LogicDocument24 pagesChap 6 Functions of Combinational LogicDuy Phan PhúNo ratings yet