Professional Documents

Culture Documents

CD74HC238

Uploaded by

roozbehxoxCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CD74HC238

Uploaded by

roozbehxoxCopyright:

Available Formats

Data sheet acquired from Harris Semiconductor SCHS147A

CD74HC138, CD74HCT138, CD74HC238, CD74HCT238

High Speed CMOS Logic 3-to-8 Line Decoder/ Demultiplexer Inverting and Non-Inverting

October 1997 - Revised February 1999

Features

Select One Of Eight Data Outputs Active Low for 138, Active High for 238 l/O Port or Memory Selector Three Enable Inputs to Simplify Cascading Typical Propagation Delay of 13ns at VCC = 5V, CL = 15pF, TA = 25oC Fanout (Over Temperature Range) - Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads - Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads Wide Operating Temperature Range . . . -55oC to 125oC Balanced Propagation Delay and Transition Times Signicant Power Reduction Compared to LSTTL Logic ICs HC Types - 2V to 6V Operation - High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V HCT Types - 4.5V to 5.5V Operation - Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min) - CMOS Input Compatibility, Il 1A at VOL, VOH

[ /Title (CD74 HC138 , CD74 HCT13 8, CD74 HC238 , CD74 HCT23 8) /Subject (High Speed

Pinout

CD74HC138, CD74HCT138, CD74HC238, CD74HCT238 (PDIP, SOIC) TOP VIEW

A0 1 A1 2 A2 3 E1 4 E2 5 E3 6 (Y7) Y7 7 GND 8 16 VCC 15 Y0 (Y0) 14 Y1 (Y1) 13 Y2 (Y2) 12 Y3 (Y3) 11 Y4 (Y4) 10 Y5 (Y5) 9 Y6 (Y6)

Signal names in parentheses are for HC238 and HCT238.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. Copyright

1999, Texas Instruments Incorporated

CD74HC138, CD74HCT138, CD74HC238, CD74HCT238 Description

The Harris CD74HC138, CD74HC238 and CD74HCT138, CD74HCT238 are high speed silicon gate CMOS decoders well suited to memory address decoding or data routing applications. Both circuits feature low power consumption usually associated with CMOS circuitry, yet have speeds comparable to low power Schottky TTL logic. Both circuits have three binary select inputs (A0, A1 and A2). If the device is enabled, these inputs determine which one of the eight normally high outputs of the HC/HCT138 series will go low or which of the normally low outputs of the HC/HCT238 series will go high. Two active low and one active high enables (E1, E2, and E3) are provided to ease the cascading of decoders. The decoders 8 outputs can drive 10 low power Schottky TTL equivalent loads.

Ordering Information

PART NUMBER CD74HCT138E CD74HC238E CD74HCT238E CD74HC138M CD74HCT138M CD74HC238M CD74HCT238M CD74HC138SM NOTES: 1. When ordering, use the entire part number. Add the sufx 96 to obtain the variant in the tape and reel. 2. Wafer and die for this part number is available which meets all electrical specifications. Please contact your local sales office or Harris customer service for ordering information. TEMP. RANGE (oC) -55 to 125 -55 to 125 -55 to 125 -55 to 125 -55 to 125 -55 to 125 -55 to 125 -55 to 125 PACKAGE 16 Ld PDIP 16 Ld PDIP 16 Ld PDIP 16 Ld SOIC 16 Ld SOIC 16 Ld SOIC 16 Ld SOIC 16 Ld SSOP PKG. NO. E16.3 E16.3 E16.3 M16.15 M16.15 M16.15 M16.15 M16.209

Ordering Information

PART NUMBER CD74HC138E TEMP. RANGE (oC) -55 to 125 PACKAGE 16 Ld PDIP PKG. NO. E16.3

Functional Diagram

HC/HCT HC/HCT 238 138 A0 A1 3 A2 12 Y3 4 E1 5 E2 E3 6 9 Y6 7 Y7 Y7 Y6 10 Y5 Y5 11 Y4 Y4 Y3 13 Y2 Y2 1 2 15 14 Y0 Y1 Y0 Y1

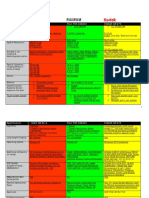

TRUTH TABLE CD74HC138, CD74HCT138 INPUTS ENABLE E3 X L X H H H H E2 X X H L L L L E1 H X X L L L L A2 X X X L L L L ADDRESS A1 X X X L L H H A0 X X X L H L H Y0 H H H L H H H Y1 H H H H L H H Y2 H H H H H L H OUTPUTS Y3 H H H H H H L Y4 H H H H H H H Y5 H H H H H H H Y6 H H H H H H H Y7 H H H H H H H

CD74HC138, CD74HCT138, CD74HC238, CD74HCT238

TRUTH TABLE CD74HC138, CD74HCT138 INPUTS ENABLE E3 H H H H E2 L L L L E1 L L L L A2 H H H H ADDRESS A1 L L H H A0 L H L H Y0 H H H H Y1 H H H H Y2 H H H H OUTPUTS Y3 H H H H Y4 L H H H Y5 H L H H Y6 H H L H Y7 H H H L

NOTE: H = High Voltage Level, L = Low Voltage Level, X = Dont Care TRUTH TABLE CD74HC238, CD74HCT238 INPUTS ENABLE E3 X L X H H H H H H H H E2 X X H L L L L L L L L E1 H X X L L L L L L L L A2 X X X L L L L H H H H ADDRESS A1 X X X L L H H L L H H A0 X X X L H L H L H L H Y0 L L L H L L L L L L L Y1 L L L L H L L L L L L Y2 L L L L L H L L L L L OUTPUTS Y3 L L L L L L H L L L L Y4 L L L L L L L H L L L Y5 L L L L L L L L H L L Y6 L L L L L L L L L H L Y7 L L L L L L L L L L H

NOTE: H = High Voltage Level, L = Low Voltage Level, X = Dont Care

CD74HC138, CD74HCT138, CD74HC238, CD74HCT238

Absolute Maximum Ratings

DC Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7V DC Input Diode Current, IIK For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . . . . .20mA DC Output Diode Current, IOK For VO < -0.5V or VO > VCC + 0.5V . . . . . . . . . . . . . . . . . . . .20mA DC Output Source or Sink Current per Output Pin, IO For VO > -0.5V or VO < VCC + 0.5V . . . . . . . . . . . . . . . . . . . .25mA DC VCC or Ground Current, ICC or IGND . . . . . . . . . . . . . . . . . .50mA

Thermal Information

Thermal Resistance (Typical, Note 3) JA (oC/W) PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90 SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115 SSOP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155 Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150oC Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC (SOIC - Lead Tips Only)

Operating Conditions

Temperature Range (TA) . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, VI, VO . . . . . . . . . . . . . . . . . 0V to VCC Input Rise and Fall Time 2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max) 6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

CAUTION: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specication is not implied.

NOTE: 3. JA is measured with the component mounted on an evaluation PC board in free air.

DC Electrical Specications

TEST CONDITIONS PARAMETER HC TYPES High Level Input Voltage VIH 2 4.5 6 Low Level Input Voltage VIL 2 4.5 6 High Level Output Voltage CMOS Loads High Level Output Voltage TTL Loads Low Level Output Voltage CMOS Loads Low Level Output Voltage TTL Loads Input Leakage Current Quiescent Device Current II ICC VCC or GND VCC or GND VOL VIH or VIL VOH VIH or VIL -0.02 -0.02 -0.02 -4 -5.2 0.02 0.02 0.02 4 5.2 0 2 4.5 6 4.5 6 2 4.5 6 4.5 6 6 6 1.5 3.15 4.2 1.9 4.4 5.9 3.98 5.48 0.5 1.35 1.8 0.1 0.1 0.1 0.26 0.26 0.1 8 1.5 3.15 4.2 1.9 4.4 5.9 3.84 5.34 0.5 1.35 1.8 0.1 0.1 0.1 0.33 0.33 1 80 1.5 3.15 4.2 1.9 4.4 5.9 3.7 5.2 0.5 1.35 1.8 0.1 0.1 0.1 0.4 0.4 1 160 V V V V V V V V V V V V V V V V V V A A SYMBOL VI (V) IO (mA) VCC (V) 25oC MIN TYP MAX -40oC TO 85oC -55oC TO 125oC MIN MAX MIN MAX UNITS

CD74HC138, CD74HCT138, CD74HC238, CD74HCT238

DC Electrical Specications

(Continued) TEST CONDITIONS PARAMETER HCT TYPES High Level Input Voltage Low Level Input Voltage High Level Output Voltage CMOS Loads High Level Output Voltage TTL Loads Low Level Output Voltage CMOS Loads Low Level Output Voltage TTL Loads Input Leakage Current Quiescent Device Current Additional Quiescent Device Current Per Input Pin: 1 Unit Load (Note 4) NOTE: 4. For dual-supply systems theoretical worst case (VI = 2.4V, VCC = 5.5V) specification is 1.8mA. II ICC ICC VCC and GND VCC or GND VCC -2.1 VOL VIH or VIL VIH VIL VOH VIH or VIL -0.02 4.5 to 5.5 4.5 to 5.5 4.5 2 4.4 0.8 2 4.4 0.8 2 4.4 0.8 V V V SYMBOL VI (V) IO (mA) 25oC MIN TYP MAX -40oC TO 85oC -55oC TO 125oC MIN MAX MIN MAX UNITS

VCC (V)

-4

4.5

3.98

3.84

3.7

0.02

4.5

0.1

0.1

0.1

4.5

0.26

0.33

0.4

0 0 -

5.5 5.5 4.5 to 5.5

100

0.1 8 360

1 80 450

1 160 490

A A A

HCT Input Loading Table

INPUT A0-A2 E1, E2 E3 UNIT LOADS 1.5 1.25 1

NOTE: Unit Load is ICC limit specied in DC Electrical Table, e.g., 360A max at 25oC.

Switching Specications Input tr, tf = 6ns

TEST CONDITIONS 25oC VCC (V) MIN TYP MAX -40oC TO 85oC MIN MAX -55oC TO 125oC MIN MAX UNITS

PARAMETER HC TYPES Propagation Delay Address to Output

SYMBOL

tPLH, tPHL CL = 50pF

2 4.5

13 -

150 30 26

190 38 33

225 45 38

ns ns ns ns

CL = 15pF CL = 50pF

5 6

Switching Specications Input tr, tf = 6ns

(Continued) 25oC VCC (V) 2 4.5 6 MIN TYP 67 MAX 150 30 26 75 15 13 10 -40oC TO 85oC MIN MAX 190 38 33 95 19 16 10 -55oC TO 125oC MIN MAX 265 53 45 110 22 19 10 UNITS ns ns ns ns ns ns pF pF

PARAMETER Enable to Output HC/HCT138

SYMBOL

TEST CONDITIONS

tPLH, tPHL CL = 50pF

Output Transition Time (Figure 1)

tTLH, tTHL CL = 50pF

2 4.5 6

Power Dissipation Capacitance, (Notes 5, 6) Input Capacitance HCT TYPES Propagation Delay Address to Output

CPD CIN

CL = 15pF -

5 -

tPLH, tPHL CL = 50pF CL = 15pF

4.5 5 4.5 4.5 4.5 5 -

14 67 -

35 35 40 15 10

44 44 50 19 10

53 53 60 22 10

ns ns ns ns ns pF pF

Enable to Output HC/HCT138 Enable to Output HC/HCT238 Output Transition Time (Figure 2) Power Dissipation Capacitance, (Notes 5, 6) Input Capacitance NOTES:

tPLH, tPHL CL = 50pF tPLH, tPHL CL = 15pF tTLH, tTHL CL = 50pF CPD CIN CL = 15pF -

5. CPD is used to determine the dynamic power consumption, per gate. 6. PD = VCC2 fi (CPD + CL) where: fi = Input Frequency, CL = Output Load Capacitance, VCC = Supply Voltage.

Test Circuits and Waveforms

tr = 6ns INPUT 90% 50% 10% tTLH 90% 50% 10% tPHL tPLH tf = 6ns VCC INPUT GND tTHL tr = 6ns 2.7V 1.3V 0.3V tTLH 90% INVERTING OUTPUT tPHL tPLH 1.3V 10% tf = 6ns 3V

GND

tTHL

INVERTING OUTPUT

FIGURE 7. HC AND HCU TRANSITION TIMES AND PROPAGATION DELAY TIMES, COMBINATION LOGIC

FIGURE 8. HCT TRANSITION TIMES AND PROPAGATION DELAY TIMES, COMBINATION LOGIC

IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TIs standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (CRITICAL APPLICATIONS). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMERS RISK. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TIs publication of information regarding any third partys products or services does not constitute TIs approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

You might also like

- C.I 74HC365Document7 pagesC.I 74HC365DOMINGOS ALADIRNo ratings yet

- 7473Document8 pages7473Merényi OszkárNo ratings yet

- CD54/74HC540, CD74HCT540, CD54/74HC541, CD54/74HCT541: High Speed CMOS Logic Octal Buffer and Line Drivers, Three-StateDocument8 pagesCD54/74HC540, CD74HCT540, CD54/74HC541, CD54/74HCT541: High Speed CMOS Logic Octal Buffer and Line Drivers, Three-StateKelemen MihályNo ratings yet

- CD54HC08, CD74HC08, CD54HCT08, CD74HCT08: Features DescriptionDocument13 pagesCD54HC08, CD74HC08, CD54HCT08, CD74HCT08: Features DescriptionWissam NawfalNo ratings yet

- CD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionDocument16 pagesCD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionAndrea DispoNo ratings yet

- CD54/74HC688, CD54/74HCT688: Features DescriptionDocument6 pagesCD54/74HC688, CD54/74HCT688: Features Descriptionbhavsar_vaibhavNo ratings yet

- CD54HC154, CD74HC154, CD54HCT154, CD74HCT154: High-Speed CMOS Logic 4-To 16-Line Decoder/DemultiplexerDocument17 pagesCD54HC154, CD74HC154, CD54HCT154, CD74HCT154: High-Speed CMOS Logic 4-To 16-Line Decoder/DemultiplexerAndrea DispoNo ratings yet

- 74 HC 4538Document11 pages74 HC 4538vagitusNo ratings yet

- CD 74 HCT 164 MDocument16 pagesCD 74 HCT 164 MfabriziocasNo ratings yet

- CD 74 HC 194Document18 pagesCD 74 HC 194rrebollarNo ratings yet

- 74HC 93 TiDocument7 pages74HC 93 TicataclgNo ratings yet

- CD54/74HC240, CD54/74HCT240, CD74HC241, CD54/74HCT241, CD54/74HC244, CD54/74HCT244Document8 pagesCD54/74HC240, CD54/74HCT240, CD74HC241, CD54/74HCT241, CD54/74HC244, CD54/74HCT244Behzady20No ratings yet

- CD54HC4538, CD74HC4538, CD54HCT4538, CD74HCT4538Document19 pagesCD54HC4538, CD74HC4538, CD54HCT4538, CD74HCT4538Roozbeh BahmanyarNo ratings yet

- CD54/74HC540, CD74HCT540, CD54/74HC541, CD54/74HCT541: High-Speed CMOS Logic Octal Buffer and Line Drivers, Three-StateDocument7 pagesCD54/74HC540, CD74HCT540, CD54/74HC541, CD54/74HCT541: High-Speed CMOS Logic Octal Buffer and Line Drivers, Three-Statefad24071995No ratings yet

- IC-ON-LINE - CN In74hc164a 4331941Document6 pagesIC-ON-LINE - CN In74hc164a 4331941enriquevagoNo ratings yet

- Mid Semester 2012 TID203Document17 pagesMid Semester 2012 TID203peas002No ratings yet

- C.I 74HC175Document7 pagesC.I 74HC175DOMINGOS ALADIRNo ratings yet

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocument7 pagesMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CeNo ratings yet

- MM74HC164 8-Bit Serial-in/Parallel-out Shift Register: General DescriptionDocument7 pagesMM74HC164 8-Bit Serial-in/Parallel-out Shift Register: General Descriptionmalirezazadeh5549No ratings yet

- 74HC573 Octal LatchDocument13 pages74HC573 Octal LatchWonzNo ratings yet

- 74 HC 4067Document15 pages74 HC 4067김경원No ratings yet

- Cmos Sram K6T1008C2E Family: Document TitleDocument11 pagesCmos Sram K6T1008C2E Family: Document TitleOmar LeonNo ratings yet

- HY6264A - (I) Series: 8kx8bit CMOS SRAMDocument9 pagesHY6264A - (I) Series: 8kx8bit CMOS SRAMLexuanhoa ProNo ratings yet

- TC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderDocument9 pagesTC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderAndrea DispoNo ratings yet

- MM 74 HCDocument6 pagesMM 74 HCdragon-red0816No ratings yet

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADocument6 pagesOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100No ratings yet

- Adc 0804 DatasheetDocument7 pagesAdc 0804 DatasheetPamela AricoNo ratings yet

- Document Title: GM76C256CDocument11 pagesDocument Title: GM76C256CFrenk EndyNo ratings yet

- SN 74 HCT 245Document22 pagesSN 74 HCT 245agiyafersyaNo ratings yet

- HCF 4099 BeDocument14 pagesHCF 4099 BeÁbel KatonaNo ratings yet

- CDP1802 DatasheetDocument28 pagesCDP1802 DatasheetDaveNo ratings yet

- 4536BDocument17 pages4536BpandaypiraNo ratings yet

- 74HC194N PDFDocument7 pages74HC194N PDFOsman KoçakNo ratings yet

- Datasheet SN74HC04 - Hex InversorDocument16 pagesDatasheet SN74HC04 - Hex InversorPablo CarvalhoNo ratings yet

- L293 Quadruple Half-H Driver: Description Logic SymbolDocument5 pagesL293 Quadruple Half-H Driver: Description Logic SymbolSiddhant YadavNo ratings yet

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoNo ratings yet

- 4511 IC StructureDocument15 pages4511 IC Structurenavneetgoel2222No ratings yet

- 74 HC 138Document5 pages74 HC 138dlbplbNo ratings yet

- 4008 Sumador 4 BitDocument14 pages4008 Sumador 4 Bitlucaxs09No ratings yet

- 74164Document4 pages74164milkyway69No ratings yet

- HCC4007UB HCF4007UB: Dual Complementary Pair Plus InverterDocument14 pagesHCC4007UB HCF4007UB: Dual Complementary Pair Plus InverterRendy WandarosanzaNo ratings yet

- SN 74 HCT 244Document22 pagesSN 74 HCT 244Filipe BrendlerNo ratings yet

- 8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsDocument11 pages8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsLưu TinhNo ratings yet

- CA3161EDocument4 pagesCA3161EAlejandro Borrego DominguezNo ratings yet

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601No ratings yet

- 40110Document11 pages40110Tutai LangtuNo ratings yet

- 000 0 Hy628100bllg 70Document9 pages000 0 Hy628100bllg 70Deepa DevarajNo ratings yet

- SN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsDocument7 pagesSN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsMadhukar PuliNo ratings yet

- 74AC161-Synchronous Presettable Binary CounterDocument11 pages74AC161-Synchronous Presettable Binary CounterbmmostefaNo ratings yet

- 74163Document12 pages74163Obenelia MartinezNo ratings yet

- MC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceiverDocument8 pagesMC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceivernandobnuNo ratings yet

- 74hc244 Tristate 8bitsDocument10 pages74hc244 Tristate 8bitshuvillamilNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- FBs PLC Catalog enDocument28 pagesFBs PLC Catalog enroozbehxoxNo ratings yet

- Eam-110 Gac To Cummins Qsx15 Interface ... - Huegli TechDocument3 pagesEam-110 Gac To Cummins Qsx15 Interface ... - Huegli TechroozbehxoxNo ratings yet

- H8S 2240Document818 pagesH8S 2240roozbehxoxNo ratings yet

- Leroy Somer ALTERNATORDocument18 pagesLeroy Somer ALTERNATORroozbehxoxNo ratings yet

- Capacitor AluminumDocument433 pagesCapacitor AluminumroozbehxoxNo ratings yet

- LS Inverter iG5A ManualDocument181 pagesLS Inverter iG5A ManualSusovit Dwa100% (10)

- BP12864CDocument1 pageBP12864CroozbehxoxNo ratings yet

- How To Use VNC FunctionDocument4 pagesHow To Use VNC FunctionroozbehxoxNo ratings yet

- 21823.0 Appendix RBC1100 - LX449 V1 - 0Document8 pages21823.0 Appendix RBC1100 - LX449 V1 - 0roozbehxoxNo ratings yet

- Description of Options: Description of Option Functional Description Parameter List Modbus CommunicationDocument13 pagesDescription of Options: Description of Option Functional Description Parameter List Modbus CommunicationroozbehxoxNo ratings yet

- 7640 7706 7708CatalogEDocument2 pages7640 7706 7708CatalogEroozbehxoxNo ratings yet

- Gps-211xx Series Dds Function GeneratorDocument8 pagesGps-211xx Series Dds Function GeneratorroozbehxoxNo ratings yet

- 709h Track DatasheetDocument3 pages709h Track DatasheetroozbehxoxNo ratings yet

- Gardner Denver PZ-11revF3Document66 pagesGardner Denver PZ-11revF3Luciano GarridoNo ratings yet

- Income Statement, Its Elements, Usefulness and LimitationsDocument5 pagesIncome Statement, Its Elements, Usefulness and LimitationsDipika tasfannum salamNo ratings yet

- The Electricity Act - 2003Document84 pagesThe Electricity Act - 2003Anshul PandeyNo ratings yet

- Agfa CR 85-X: Specification Fuji FCR Xg5000 Kodak CR 975Document3 pagesAgfa CR 85-X: Specification Fuji FCR Xg5000 Kodak CR 975Youness Ben TibariNo ratings yet

- As 60068.5.2-2003 Environmental Testing - Guide To Drafting of Test Methods - Terms and DefinitionsDocument8 pagesAs 60068.5.2-2003 Environmental Testing - Guide To Drafting of Test Methods - Terms and DefinitionsSAI Global - APACNo ratings yet

- Labstan 1Document2 pagesLabstan 1Samuel WalshNo ratings yet

- TSB 120Document7 pagesTSB 120patelpiyushbNo ratings yet

- Lab 6 PicoblazeDocument6 pagesLab 6 PicoblazeMadalin NeaguNo ratings yet

- Kaitlyn LabrecqueDocument15 pagesKaitlyn LabrecqueAmanda SimpsonNo ratings yet

- Ingles Avanzado 1 Trabajo FinalDocument4 pagesIngles Avanzado 1 Trabajo FinalFrancis GarciaNo ratings yet

- Check Fraud Running Rampant in 2023 Insights ArticleDocument4 pagesCheck Fraud Running Rampant in 2023 Insights ArticleJames Brown bitchNo ratings yet

- Separation PayDocument3 pagesSeparation PayMalen Roque Saludes100% (1)

- Continue: Rudolf Bultmann Theology of The New Testament PDFDocument3 pagesContinue: Rudolf Bultmann Theology of The New Testament PDFpishoi gerges0% (1)

- EnerconDocument7 pagesEnerconAlex MarquezNo ratings yet

- Building and Other Construction Workers Act 1996Document151 pagesBuilding and Other Construction Workers Act 1996Rajesh KodavatiNo ratings yet

- STM - Welding BookDocument5 pagesSTM - Welding BookAlvin MoollenNo ratings yet

- 2.1 Components and General Features of Financial Statements (3114AFE)Document19 pages2.1 Components and General Features of Financial Statements (3114AFE)WilsonNo ratings yet

- Functions of Commercial Banks: Primary and Secondary FunctionsDocument3 pagesFunctions of Commercial Banks: Primary and Secondary FunctionsPavan Kumar SuralaNo ratings yet

- Online Learning Interactions During The Level I Covid-19 Pandemic Community Activity Restriction: What Are The Important Determinants and Complaints?Document16 pagesOnline Learning Interactions During The Level I Covid-19 Pandemic Community Activity Restriction: What Are The Important Determinants and Complaints?Maulana Adhi Setyo NugrohoNo ratings yet

- Unit-5 Shell ProgrammingDocument11 pagesUnit-5 Shell ProgrammingLinda BrownNo ratings yet

- 23 Things You Should Know About Excel Pivot Tables - Exceljet PDFDocument21 pages23 Things You Should Know About Excel Pivot Tables - Exceljet PDFRishavKrishna0% (1)

- Pneumatic Fly Ash Conveying0 PDFDocument1 pagePneumatic Fly Ash Conveying0 PDFnjc6151No ratings yet

- Abu Hamza Al Masri Wolf Notice of Compliance With SAMs AffirmationDocument27 pagesAbu Hamza Al Masri Wolf Notice of Compliance With SAMs AffirmationPaulWolfNo ratings yet

- Droplet Precautions PatientsDocument1 pageDroplet Precautions PatientsMaga42No ratings yet

- 7 TariffDocument22 pages7 TariffParvathy SureshNo ratings yet

- Mid Term Exam 1Document2 pagesMid Term Exam 1Anh0% (1)

- Escario Vs NLRCDocument10 pagesEscario Vs NLRCnat_wmsu2010No ratings yet

- Catalog Celule Siemens 8DJHDocument80 pagesCatalog Celule Siemens 8DJHAlexandru HalauNo ratings yet

- Government of West Bengal Finance (Audit) Department: NABANNA', HOWRAH-711102 No. Dated, The 13 May, 2020Document2 pagesGovernment of West Bengal Finance (Audit) Department: NABANNA', HOWRAH-711102 No. Dated, The 13 May, 2020Satyaki Prasad MaitiNo ratings yet

- Javascript Applications Nodejs React MongodbDocument452 pagesJavascript Applications Nodejs React MongodbFrancisco Miguel Estrada PastorNo ratings yet