Professional Documents

Culture Documents

Analysis-And-evaluation of A Lossless Turn-On Snubber

Uploaded by

bmmostefaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analysis-And-evaluation of A Lossless Turn-On Snubber

Uploaded by

bmmostefaCopyright:

Available Formats

Analysis and Evaluation of a Lossless Turn-On Snubber

Hanan Levy, Isaac Zafrany, Gregory Ivensky and Sam Ben-Yaakov

*

Tel: +972-7-6461561; Fax: +972-7-6472949; Email: sby@bguee.bgu.ac.il

Power Electronics Laboratory

Department of Electrical and Computer Engineering

Ben-Gurion University of the Negev

P. O. Box 653, Beer-Sheva 84105, ISRAEL

Abs t r act - A l o s s l e s s turn-on snubber was studied

anal yt i cal l y, by si mul at i on and experi ment al l y.

Li mi t s were found for t he proper operat i on of t he

snubber and are expressed as permi s s i bl e duty c yc l e

as a f unct i on of i nput current. It was found that a

modi fi ed vers i on of t he snubber, whi ch i ncl udes a

tapped mai n i nductor, i mproves t he performance by

al l owi ng a wider operat i onal range. The

experi ment al resul t s conf i rm t he t heoret i cal

anal ysi s. A reduct i on of power l o s s e s of about 19W

was observed when t he snubber was i mpl ement ed i n

a 1kW Boost convert er.

I. INTRODUCTION

The recent technological strive toward smaller and lighter

systems imposes an ever increasing demand for the reduction

of size and weight of inverters and converters while keeping

down the overall power loss. This implies high switching

frequencies coupled with soft switching schemes to reduce

switching losses. Among the possible solutions for soft

switching are the dual switch approaches that apply an

auxiliary switch to help smooth the transitions of the main

switch [1,2]. While these solutions are effective in reducing

switching losses [3], they are too costly for many high

volume applications. The present relentless competition in

the power electronics industry calls for simple and

inexpensive solutions to make the design cost effective.

Among the possible approaches for soft switching is the

lossless snubber technology [4-6] which appears to be less

costly than the active snubbers. In this study we analyzed and

evaluated experimentally a turn-on lossless snubber that was

recently proposed [7]. The objective was to gain a better

understanding of the operational modes of the snubber, to

drive design guidelines and to verify the theory against

experimental results.

II. PRINCIPLE OF OPERATION

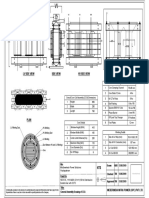

In one embodiment of the turn-on snubber (Fig. 1), it

comprises a series inductor (L

s

), a snubbing capacitor (C

s

)

and two bypass diodes D

1

and D

2

. The function of the

*

Corresponding author.

+

L

s

L

m

Driver

Controller

C

s

R

o

V

out

C

o

V

in

D

o

D

1

D

2

Q

-

+

-

I

in

C

s

V

Fig. 1. The lossless turn-on snubber (uncoupled inductors

version) implemented in a Boost converter.

inductor is to control the reverse recovery process of the main

diode (D

o

). C

s

and the bypass diodes are used to recover the

energy trapped in L

s

. Also, D

1

and D

2

clamp the switch

voltage to V

out

. The operation of the lossless snubber will

be discussed in relation to the waveforms of Fig. 2 that were

obtained by PSPICE (MicroSim Inc.) simulations.

The operation of the lossless snubber includes six stages

(Fig. 2):

1. The first interval commences when the main transistor Q

turns on. The current through D

o

and L

s

, which starts as I

in

,

decreases linearly to zero, changes polarity and then increases

(amplitude wise) linearly until it reaches its maximum

(negative) value I

rm

at time t

1

.

The duration of interval t

0

-t

1

is found to be:

t

0-1

I

in

L

s

V

out

+ t

rm

(1)

where t

rm

defined as the duration until the peak reverses

current is reached. The magnitude of the reverse recovery

current can be approximated by:

I

rm

=

V

out

t

rm

L

s

(2)

Hence

t

0-1

t

rm

a

1+a

(3)

2

where

a =

I

rm

I

in

(4)

2. Once the main diode D

o

is cut off, the inductor L

s

and

capacitor C

s

are free to resonate in the interval t

1

-t

2

.

I

D

1

V

C

s

I

D

o

I

D

2

I

L

s

t

0

t

1

t

2

t

3

t

4

t

5

t

6

t

0

=

0

0

4A

0

4A

-4A

20V

-20V

4A

-4A

4A

2

Control - Voltage

0

0

Fig. 2. Basic waveforms of the lossless snubber of Fig. 1.

The diode D

1

closes the path of the resonant current of L

s

C

s

and carries the cosinusoidal current that develops. The

magnitude of the resonant current and the capacitor C

s

voltage

can be expressed as:

i

Ls

(t) = I

rm

cos (

r

t) (5)

v

C

(t) =

I

rm

r

C

s

sin (

r

t) (6)

where:

r

=

1

L

s

C

s

(7)

t is time, accounted from the beginning of each interval.

The interval t

1

-t

2

ends when the current of D

1

reaches zero.

Consequently, the duration of interval t

1

-t

2

is found to be:

t

1-2

=

T

r

4

(8)

where T

r

=

2

r

is the resonant period. The voltage across the

capacitor C

s

at this instance is:

V

Cmax

= V

out

t

rm

r

(9)

3. During the interval t

2

-t

3

the main inductor (L

m

) charges,

diode D

1

is off and the voltage across the capacitor C

s

i s

equal to V

Cmax

(Fig. 2).

4. The interval t

3

-t

4

starts when Q turns 'off'. Diodes D

1

and

D

2

are immediately clamped to V

out

while carrying I

in

. The

resonant circuit L

s

C

s

is now shorted by the conducting D

1

and the current i

Ls

will increase under action of v

C

until it

will reach I

in

. The current of D

1

is now the difference

between i

Ls

and I

in

. The magnitude of the resonant current

and the capacitor C

s

voltage during this interval can be

expressed as:

i

Ls

(t) = I

rm

sin (

r

t) (10)

i

in

(t) = I

in pk

-

V

out

-V

in

L

m

t (11)

where in Boost topology:

I

in pk

= I

in av

+

V

in

DT

s

2L

m

(12)

I

in av

is the average input current, D is the duty cycle and T

s

is the switching

period.

This interval ends when i

Ls

(t

4

) = i

in

(t

4

) and the current of

D

1

smoothly reaches zero, turning it off. Approximately

t

3-4

=

1

r

sin

-1

,

_

I

i n pk

I

rm

(13)

The magnitude of the input current and the capacitor C

s

voltage at this moment can be expressed as:

i

in

(t

4

) = i

Ls

(t

4

) =

V

Cmax

L

s

C

s

sin(

r

t

4

) (14)

v

C

(t

4

) = V

Cmax

cos (

r

t

4

) (15)

5. In the interval t

4

-t

5

the input current i

in

flows through L

s

,

C

s

and D

2

until v

C

(t) reaches zero. In this moment (t

5

), D

o

will turn-on and D

2

will turn-off.

The duration of interval t

4

-

t

5

can be approximated by :

3

t

4-5

=

C

s

v

C

(t

4

)

I

i n pk

(16)

6. In the final operational stage t

5

-t

6

, L

s

and D

o

are

conducting while the auxiliary diodes are turned off. This

interval ends at t

6

(or t

0

)when the transistor turns-on.

Note that the operating conditions of the snubber described

above are for the case:

I

in pk

I

rm

(17)

If I

in pk

>I

rm

the conduction interval of D

1

is much longer

because the commutation process from the diode D

1

to the

inductor L

s

acts only under the influence of the on-voltage of

the diode after the voltage across the capacitor C

s

gets zero.

III. THE COUPLED INDUCTOR REALIZATION

A second, more desirable embodiment of the lossless

snubber is depicted in Fig. 3. In this case, the main inductor

is tapped, adding thereby a positive or negative voltage to

L

s

(Fig. 4).

V

out

C

s

V

+

L

1

Driver

Controller

C

s

R

o

C

o

D

o

D

1

D

2

Q

-

+

-

L

s

L

m

1: n I

in

V

in

Fig. 3. The lossless turn-on snubber (coupled inductors version)

implemented in a Boost converter.

L

s

C

s

V

cpl on

D

1

L

s

C

s

D

1

V

cpl off

+ +

(a) (b)

Fig. 4. Simplified equivalent circuits of the resonant elements

when the transistor is 'on' (a) and when the transistor is

'off' (b)

For a tap to main inductor turn ratio of n, the magnitude of

the added voltages can be estimated from:

V

cpl on

= nV

in

(18)

V

cpl off

= n (V

out

- V

in

) (19)

Consequently, the maximal reverse current of the main diode

(D

0

) will be in this case:

I

rm

=

(V

out

+V

cpl on

) t

rm

L

s

(20)

The duration of the interval t

0

-t

1

can be obtained as before by

(3).

The resonant inductor current L

s

and capacitor voltage C

s

at turn-on during the interval t

1

-t

2

will be:

i

Ls

(t)= I

rm

cos (

r

t) +

V

cpl on

L

s

C

s

sin (

r

t) (21)

v

C

(t) = I

rm

L

s

C

s

sin(

r

t) + V

cpl on

(1-cos(

r

t))(22)

This interval ends at t

2

when the current i

L

s

reaches zero.

Consequently, the duration of t

1

-t

2

interval will be:

t

1-2

=

1

]

1

1

1

tan

-1

_

-

I

rm

L

s

C

s

V

cpl on

+ (23)

The relationship (23) is depicted in Fig. 5 where

I

rm

*

= I

rm

L

s

C

s

V

out

(24)

V

cpl on

*

=

V

cpl on

V

out

(25)

We see that t

1-2

increases with rising V

cpl on

.

The capacitor's voltage v

C

(t) (eq. (22)) reaches its

maximum value V

Cmax

at the instance t

2

. The relationship

V

Cmax

*

=

V

Cmax

V

out

(26)

as a function on I

rm

*

and V

cpl on

*

is depicted in Fig. 6.

We see that due to the coupling, the voltage across the

capacitor gets somewhat larger.

The resonant inductor current L

s

and capacitor voltage C

s

during the interval t

3

-t

4

will be:

i

Ls

(t) =

V

C max

+ V

cpl off

L

s

C

s

sin (

r

t) (27)

v

C

(t) = (V

Cmax

+V

cpl off

)cos (

r

t) - V

cpl off

(28)

Two conditions must be checked for finding the end

moment t

4

of the interval t

3

-t

4

:

i

Ls

(t

4

') = I

in pk

(29)

4

v

C

(t

4

'') = 0 (30)

or applying (27) and (28)

t

4

'= L

s

C

s

sin

-1

_

I

i n pk

L

s

C

s

V

Cmax

+V

cpl off

(31)

80

90

100

110

120

130

140

150

160

0 0.2 0.4 0.6 0.8 1 1.2

I

rm

*

r

t

1-2

[deg]

V

cpl on

= 0

*

0.05

0.10

Fig. 5. Duration of the interval t

1-2

as a function of the peak

value of the normalized reverse current I

rm

*

for different

values of the normalized tap voltage V

cpl on

*

.

0

0.2

0.4

0.6

0.8

1

1.2

1.4

0 0.2 0.4 0.6 0.8 1 1.2

I

rm

*

0.10

V

Cmax

*

V

cpl on

= 0

*

0.05

Fig. 6. The peak of the capacitor's voltage V

Cmax

*

as a function

of the peak value of the reverse current I

rm

*

for different

values of normalized tap voltage V

cpl on

*

.

t

4

''= L

s

C

s

cos

-1

_

1

V

Cmax

V

cpl off

+1

(32)

t

4

assumes the value of t

4

' or t

4

'' whichever is smaller. t

4

is

equal to t

4

'' in the case

I

in pk

>

V

Cmax

+V

cpl off

L

s

C

s

(33)

when t

4

' does not exist.

In the case t

4

=t

4

', which is denoted as 'Mode 1', the

interval t

4

-t

5

is similar to the one described above for the

uncoupled snubber (eq. (16)).

Now we study the case t

4

=t

4

'' (Mode 2).

In the interval t

4

-t

5

in Mode 2 the current i

Ls

(t) is rising

linearly under action of V

cpl off

:

i

Ls

(t) = i

Ls

(t

4

'') +

V

cpl off

+V

D1(on)

L

s

t (34)

V

D1(on)

is the voltage drop on the conducting diode D

1

. Its

influence is practical insignificant when V

cpl off

>>V

D1(on)

,

but in the case V

cpl off

0 its action is very important

because without any voltage source in the network the current

i

Ls

(t) would not rise and therefore the diodes D

1

and D

2

would

not be turned off.

The duration of the interval t

4

-t

5

can be estimated by

assuming the condition i

Ls

(t

5

) = I

in

pk

:

t

4-5

=

[I

in pk

- i

Ls

(t

4

'')]L

s

V

cpl off

+V

D1(on)

(35)

The last equation clearly shows the benefit of coupling:

t

4-5

decreases when V

cpl off

is larger. This decreases the

minimum permissible value of the turn-off interval of the

switch (t

off min

) and therefore increases the maximum

acceptable value of the duty cycle for proper operation

D

max

= 1 -

t

off min

T

s

(36)

IV. LIMITATIONS

5

To insure complete discharge of C

s

before next 'turn-on',

the criteria below should be satisfied:

t

off

> t

3-4

+t

4-5

(37)

i. e. the minimum value of the turn-off interval of the switch

must conform to:

t

off min

= t

3-4

+ t

4-5

(37a)

We find t

off min

in Mode 1 under assumption:

V

cpl off

/V

out

= 0. The error due to this assumption is

practically insignificant because the duty cycle corresponding

to t

off min

is high and therefore V

in

V

out

,

V

cpl off

=n(V

out

-V

in

) 0. From (31), (16) and (28) we

obtain:

(

r

t

off min

)

M1

=sin

-1

_ I

in pk

*

V

Cmax

*

+

V

Cmax

*

I

in pk

*

cos(

r

t

4

)

(38)

where

I

in pk

*

= I

in pk

L

s

C

s

V

out

(39)

The relationship (38) is depicted in Fig. 7. We see that

(

r

t

off min

)

M1

decreases when

I

i n pk

*

V

Cmax

*

becomes higher.

Optimum values are when

I

i n pk

*

V

Cmax

*

> 0.7. Note that in

Mode 1 I

i n pk

*

/ V

Cmax

*

< 1.

We find t

off min

in Mode 2 in the case

I

in pk

*

> V

Cmax

*

+ V

cpl off

*

under the assumption: V

cpl off

<<V

Cmax

.

Applying (32), (35) and (27) we obtain:

(

r

t

off min

)

M2

=

2

-1 +

V

Cmax

*

V

cpl off

*

_ I

i n pk

*

V

Cmax

*

-1 (40)

The relationship (40) is depicted on Fig. 8. It shows that

(t

off min

)

M2

is increasing linearly with

I

i n pk

*

V

Cmax

*

. Optimal

ratios of

I

i n pk

*

V

Cmax

*

are near 1.0 when (t

off min

)

M2

is about 95-

100

o

.

The minimum admissible value of the turn on interval of

the switch is obtained from (3), (4) and (23):

t

on min

= t

0-1

+t

1-2

=

= t

rm

a

1+a

+

1

]

1

1

1

tan

-1

_

-

a I

in

L

s

C

s

V

cpl on

+ (41)

Analysis of (41) and Fig. 5 show that t

on min

increases

with rising V

cpl on

. Accordingly grows the minimum

admissible value of the duty cycle

D

min

=

t

on min

T

s

(42)

50

100

150

200

250

300

0.1 0.4 0.7 1

I

in pk

*

V

Cmax

*

(

r

t

off min

)

M1

[deg]

Fig. 7. The minimum acceptable value of the switch turn-off

interval in Mode 1. (

r

t

off min

)

M1

as a function of the

ratio I

i n pk

*

/V

Cmax

*

.

6

I

in pk

*

V

Cmax

*

(

r

t

off min

)

M2

[deg]

0.10

50

100

150

200

250

300

350

1 1.1 1.2 1.3

V

Cmax

*

V

cpl off

*

= 0.02

0.05

Fig. 8. The minimum acceptable value of the switch turn off

interval in Mode 2. (

r

t

off min

)

M2

as a function of the

ratio I

i n pk

*

/V

Cmax

*

by different values of V

cpl off

*

/V

Cmax

*

.

V. COMPONENT STRESSES

The current and voltage stresses of the components of the

snubber are given in Table I where

I

pk sn

= I

rm

+

V

cpl on

L

s

C

s

(43)

V

Cmax

= I

rm

L

s

C

s

+ 2V

cpl on

(44)

D =

t

on

T

s

(45)

D

off

=1 - D (46)

I

rm

- see eq. (20); V

cpl on

- (18); V

cpl off

- (19); t

3-4

- (31)

or (32); t

3-5

-

(38) or (40),

r

- (7).

I

pk

I

rms

I

av

V

max

L

s

I

pk sn I

in

D

off

C

s

I

pk sn

I

in

t

3-5

T

s

V

Cmax

D

1

I

pk sn

I

pk sn

2

s

+

I

in

(t

3-4

/T

s

)

V

Cmax

+V

cpl off

D

2

I

in

I

in

t

3-5

T

s

V

out

D

o

I

pk sn

I

in

D

off

V

Cmax

+ V

out

Q I

in

I

in

D

V

out

Table I. Current and voltage stresses of the snubber components.

VI. EXPERIMENTAL RESULTS

The proposed lossless turn-on snubber was tested

experimentally to examine its operation and to assess the

reduction in switching losses. The measured waveforms (Fig.

9) were found to be in excellent agreement with the simulated

ones.

The heat dissipation process of the experimental system

was calibrated by correlating the temperature rise of the heat

sink to the total power losses (Fig. 10). The parameters of

the Boost converter were as follows:

V

in

=200V; V

out

=400V; P

in

=1000W; C

s

=100nF; L

s

=3H;

f

s

= 100kHz; n=1/7; reverse recovery time of the main diode

t

rr

=60nS.

I

D1

Vgs

I

D

2

I

D

o

Fig. 9. Experimental waveforms. Compare to Fig. 2.

Temperature rise without snubber was measured to be

T=26

0

C which implies (Fig. 10) that total power

dissipation was about P

dissipated

=48.81W. Temperature rise

with the snubber was T=16

0

C which implies total losses of

P

dissipated

=29.21W. That is, by applying the proposed

lossless turn-on snubber, the power dissipation dropped by

19.6W.

7

0

0 30 4.54 16 26

6.75

29.21

48.81

60

P(W)

T( C)

0

estimated

conduction

losses

with

snubber

no

snubber

calibration

curve

Fig. 10. Calibration curve of temperature rise of heat sink

above ambient and experimental points.

VII. CONCLUSIONS

The lossless turn on snubber analyzed and evaluated in this

study appears to be a viable choice for practical designs. The

main disadvantage of the snubber is the limitation of the duty

cycle range. In active power factor corrector, maximum

current coincides with maximum input voltage, i.e.

minimum duty cycle. Consequently, the output voltage

should be adjusted such that even for the highest line voltage

expected, D

should be above D

min.

Otherwise L

s

will not

have sufficient time to discharge. This might lead to a failure.

Another point to be observed is the possibility of D

1

, D

2

conducting during the t

off

period. This will increase losses

and may cause hard switching at turn-on. The detailed analysis

presented here and the mathematical relationships derived,

provide a comprehensive information required for a reliable

design. The proposed snubber was implemented in a

commercial product and proved to increase the overall

efficiency by 1%-2% at power levels of 1.5KW. An extra

benefit of the snubber is the reduction of EMI associated with

the reverse recovery of the main diode.

APPENDIX

SIMPLIFIED DESIGN GUIDELINES

The following procedure is suggested for the practical

design of a turn-on lossless snubber implemented in a Boost

converter.

It is assumed that the following parameters are given:

maximum input (average) current of the converter (I

in max

),

minimum and maximum input voltage (V

in min

, V

in max

),

output voltage (V

out

), main inductance (L

m

) and reverse

recovery time (t

rr

) of the main diode D

0

.

1. Select the switching frequency f

s

according to the

converter's component values available.

2. Calculate the maximal and minimal values of the duty

cycle corresponding to V

in min

and V

in max

:

D

max

= 1 -

V

in min

V

out

; D

min

= 1 -

V

in max

V

out

3. Calculate minimal values of the turn on and turn off

intervals of the switch:

t

on min

=

D

min

f

s

;

t

off min

=

1

f

s

(1- D

max

)

4. Set (

r

t

off min

) 270

o

... 360

o

and calculate the

resonant frequency

r

using the value of t

off min

from

step 3.

5. Determine the magnitude of the reverse recovery current

of the diode D

o

:

I

rm

= a I

in max

.

It is recommended to choose a

= 1.3

, taking into account

the effect of a large input ripple current.

6. Calculate approximately L

s

neglecting the influence of

coupling and assuming that t

rm

=t

rr

:

L

s

=

V

out

t

rr

I

rm

7. Calculate capacitance C

s

using the data from steps 4 & 6:

C

s

=

1

r

2

L

s

8. Calculate the maximal peak value of the input current .

9. Set

I

i n pk

*

V

Cmax

*

0.9 ... 1.0 and using the data of steps 6-8

calculate the peak voltage across the capacitor:

V

Cmax

=

(I

in pk

)

max

L

s

C

s

_ I

in pk

*

V

Cmax

*

10. Calculate normalized peak values of the reverse recovery

current and of the voltage across the capacitor:

I

rm

*

= I

rm

L

s

C

s

V

out

; V

Cmax

*

=

V

Cmax

V

out

11. Find normalized value of the coupling voltage V

cpl on

*

using the plots (Fig. 6) and data of step 10. Note:

coupling is not necessary if the point corresponding to

the data of step 10 lies below the curve V

cpl on

*

on

Fig. 6.

12. Calculate the coupling voltage V

cpl on

=V

cpl on

*

.

V

out

and the necessary turns ratio n :

8

n =

V

cpl on

V

in

Note: steps 8-11 correspond to the case when the peak of

the input current has the highest value.

13. Calculate the minimal admissible value of the turn on

interval of the switch t

on min

putting (V

cpl on

)

Dmin

in

(41) and compare the result with the value of t

on min

from step 3. In the case (t

on min

)

step 13

>(t

on min

)

step3

we must repeat the design with lower resonant frequency

r

.

14. Calculate current and voltage stresses of all elements of

the snubber and choose these elements.

REFERENCES

[1] G. Ivensky, D. Sidi and S. Ben-Yaakov, "A soft switcher

optimized for IGBTs in PWM topologies", IEEE APEC

Record, 1995, pp. 900-906.

[2] S. Ben-Yaakov, G. Ivensky, O. Levitin and A. Treiner,

"Optimization of the auxiliary switch components in a

flying capacitor ZVS PWM converter," IEEE APEC

Record, 1995, pp. 503-509.

[3] K. M. Smith and K. M. Smedley, "A comparison of

voltage mode soft switching methods for PWM

converters," IEEE APEC Record, 1996, pp. 291-298.

[4] B. W. Williams, Power Electronics, McGraw-Hill Book

Company, New-York, 1992.

[5] M. S. Vilela, E. A. A. Coelho, J. B. Vieira Jr., L. C. de

Freitas, and V. J. Farias, "A family of PWM soft-

switching converters with low stresses of voltage and

current ," IEEE APEC Record, 1996, pp. 299-304.

[6] M. S. Vilela, E. A. A. Coelho, J. B. Vieira Jr., L. C. de

Freitas, and V. J. Farias, "PWM soft-switching

converters using a single active switch," IEEE APEC

Record, 1996, pp. 299-304.

[7] I. D. Jitaru, "Soft transitions power factor correction

circuit," Proceedings of HFPC, May 1993, pp. 202-208.

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Ac and DC ModuleDocument123 pagesAc and DC ModuleRaymark Flores EllamilNo ratings yet

- Shore To Ship Converter System For EnergyDocument6 pagesShore To Ship Converter System For EnergyDevi SamosirNo ratings yet

- QSC PowerLight 9.0 Service ManualDocument100 pagesQSC PowerLight 9.0 Service Manualjgerabm50% (2)

- Emission and Absorption SpectraDocument26 pagesEmission and Absorption SpectraRiriii67% (3)

- RETIE en InglesDocument214 pagesRETIE en InglesDiego MaestreNo ratings yet

- 70572-AN601-Unclamped Inductive Switching Rugged MOSFETs For Rugged EnvironmentsDocument8 pages70572-AN601-Unclamped Inductive Switching Rugged MOSFETs For Rugged EnvironmentsbmmostefaNo ratings yet

- A Design Methodology For Power ElecronicsDocument6 pagesA Design Methodology For Power ElecronicsbmmostefaNo ratings yet

- Data Sh01 - Transformer Selection Guide DS1 - InfineonDocument11 pagesData Sh01 - Transformer Selection Guide DS1 - InfineonbmmostefaNo ratings yet

- Sss6n70a-Advanced Power MosfetDocument7 pagesSss6n70a-Advanced Power MosfetbmmostefaNo ratings yet

- Thomson SemiconductorsDocument5 pagesThomson SemiconductorsbmmostefaNo ratings yet

- Input Filtering AnDocument6 pagesInput Filtering AnbmmostefaNo ratings yet

- 70575Document19 pages70575bmmostefaNo ratings yet

- AN1166Document16 pagesAN1166bmmostefaNo ratings yet

- NM27C256 262,144-Bit (32K X 8) High Performance CMOS EPROM: General DescriptionDocument12 pagesNM27C256 262,144-Bit (32K X 8) High Performance CMOS EPROM: General DescriptiondimkaleidoscopeNo ratings yet

- Irfbe20pbf Power MosfetDocument8 pagesIrfbe20pbf Power MosfetbmmostefaNo ratings yet

- Zeners 1N4370A - 1N4372A 1N746A - 1N759A: Absolute Maximum RatingsDocument5 pagesZeners 1N4370A - 1N4372A 1N746A - 1N759A: Absolute Maximum RatingsAxel JacobNo ratings yet

- MS-523-Fairchild Switch Family CharacteristicsDocument3 pagesMS-523-Fairchild Switch Family CharacteristicsbmmostefaNo ratings yet

- AB-8-Selection of MOSFETs in Switch ModeDocument4 pagesAB-8-Selection of MOSFETs in Switch ModebmmostefaNo ratings yet

- Irfbe20pbf Power MosfetDocument8 pagesIrfbe20pbf Power MosfetbmmostefaNo ratings yet

- 74AC161-Synchronous Presettable Binary CounterDocument11 pages74AC161-Synchronous Presettable Binary CounterbmmostefaNo ratings yet

- LM324 - Amp Op X4Document17 pagesLM324 - Amp Op X4huvillamilNo ratings yet

- Fqpf2n70 700v N Chanel MosfetDocument8 pagesFqpf2n70 700v N Chanel MosfetbmmostefaNo ratings yet

- Singer1992 - Canonical Modeling of PowerDocument7 pagesSinger1992 - Canonical Modeling of PowerbmmostefaNo ratings yet

- Siu97 - Analysis and Experimental Evaluation of Single-Switch Fast-Response SwitchingDocument7 pagesSiu97 - Analysis and Experimental Evaluation of Single-Switch Fast-Response SwitchingbmmostefaNo ratings yet

- Iris4007 Integrated SwitcherDocument6 pagesIris4007 Integrated SwitcherbmmostefaNo ratings yet

- Ref 37 - Pub56-Vlad Grigore-Institute of Intelligent Power Electronics Publications-ToPOLOGICAL ISSUES in SINGLE-PHASEDocument114 pagesRef 37 - Pub56-Vlad Grigore-Institute of Intelligent Power Electronics Publications-ToPOLOGICAL ISSUES in SINGLE-PHASEbmmostefaNo ratings yet

- 74HC14-Hix Inverting Schmitt TriggerDocument7 pages74HC14-Hix Inverting Schmitt TriggerbmmostefaNo ratings yet

- Hc11a1-Hcmos Microcontroller UnitDocument174 pagesHc11a1-Hcmos Microcontroller UnitbmmostefaNo ratings yet

- 4.1hoja de Datos Del CD40106 PDFDocument6 pages4.1hoja de Datos Del CD40106 PDFlookb64No ratings yet

- Integrated Magnetic P Esc 93Document7 pagesIntegrated Magnetic P Esc 93bmmostefaNo ratings yet

- A Mixed Signal AsicDocument6 pagesA Mixed Signal AsicbmmostefaNo ratings yet

- Ffmboo-D Maksimovie - FF PWM For Boost DC DC PWR CVDocument2 pagesFfmboo-D Maksimovie - FF PWM For Boost DC DC PWR CVbmmostefaNo ratings yet

- IEE94-RW Ericson - PWR Source Element and Its PropertiesDocument7 pagesIEE94-RW Ericson - PWR Source Element and Its PropertiesbmmostefaNo ratings yet

- Art96 MCH G - A New Control Strategy To Achieve Sinusoidal Line Current in A Cascade Buck-Boost Converter-IEEEDocument9 pagesArt96 MCH G - A New Control Strategy To Achieve Sinusoidal Line Current in A Cascade Buck-Boost Converter-IEEEbmmostefaNo ratings yet

- 10 1 1 8 3813Document6 pages10 1 1 8 3813yogendra12No ratings yet

- Reverse Power RelayDocument5 pagesReverse Power Relaysikta21No ratings yet

- The Electromechanical RelayDocument17 pagesThe Electromechanical Relaytata lorenNo ratings yet

- Chapter 1 - Semiconductor FundamentalsDocument26 pagesChapter 1 - Semiconductor FundamentalsSyarmiezi RodziNo ratings yet

- Manual Safepower EVODocument64 pagesManual Safepower EVOKenneth Cárdenas67% (3)

- Copa Express 1212Document130 pagesCopa Express 1212evoeletronicapfNo ratings yet

- Chapter2 - AC To DC ConvertersDocument36 pagesChapter2 - AC To DC ConvertersYee Yen AppleNo ratings yet

- Bhagvender Singh XII-A Physics Project PDFDocument15 pagesBhagvender Singh XII-A Physics Project PDFvoid50% (4)

- Sun Tracking Solar Panel Project Using MicrocontrollerDocument5 pagesSun Tracking Solar Panel Project Using MicrocontrollerVeeraPavanVasireddiNo ratings yet

- Kia324p KecDocument4 pagesKia324p KecR. Muhamad Ka RidwanNo ratings yet

- Karunya University: Division OF Electronics & Instrumentation EngineeringDocument325 pagesKarunya University: Division OF Electronics & Instrumentation EngineeringVishal NairNo ratings yet

- 07.06.21 - SR - Sankalp & ALL - WTM-5 Q.paper With Key & Sol'sDocument23 pages07.06.21 - SR - Sankalp & ALL - WTM-5 Q.paper With Key & Sol'sNishith Reddy 316No ratings yet

- KQ-330 Power Line Carrier Communication ModuleDocument3 pagesKQ-330 Power Line Carrier Communication Moduleservio2009No ratings yet

- Pioneer ct-400Document22 pagesPioneer ct-400VictorJulioLarcoLeónNo ratings yet

- Harman Kardon 3370Document105 pagesHarman Kardon 3370Rodrigo Cardenas MartinezNo ratings yet

- Expt 4 FWR LC FilterDocument6 pagesExpt 4 FWR LC FiltersamarthNo ratings yet

- Installation Instructions Panel Board NHPDocument12 pagesInstallation Instructions Panel Board NHPelectroplex56No ratings yet

- An-Introducing 32nm Technology in MicrowindDocument24 pagesAn-Introducing 32nm Technology in MicrowindAntonio LeonNo ratings yet

- PART IV. Instrument TransformersDocument30 pagesPART IV. Instrument TransformersuplbselesNo ratings yet

- Phy450 ReferencesDocument40 pagesPhy450 ReferencesGiovanni Andrew DaltonNo ratings yet

- Ild1, Ild2, Ild5, Ilq1, Ilq2: Vishay SemiconductorsDocument10 pagesIld1, Ild2, Ild5, Ilq1, Ilq2: Vishay SemiconductorsTan Hung LuuNo ratings yet

- 42MT New Starter - Product Details - Delco RemyDocument2 pages42MT New Starter - Product Details - Delco Remydandi zlkNo ratings yet

- Ixfk100n65x2 100a 650v N Kanal Mosfet To264 DatasheetDocument6 pagesIxfk100n65x2 100a 650v N Kanal Mosfet To264 Datasheetbasheer almetwakelNo ratings yet

- Apxvf18s C A20Document2 pagesApxvf18s C A20Francisco RevecoNo ratings yet

- WaveguidesDocument2 pagesWaveguidesRaweed UllahNo ratings yet

- 100KVA GA DrawingDocument1 page100KVA GA DrawingMahidhar TalapaneniNo ratings yet