Professional Documents

Culture Documents

Design Guide For Xilinx FPGA Power Management Systems

Uploaded by

bmmostefaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design Guide For Xilinx FPGA Power Management Systems

Uploaded by

bmmostefaCopyright:

Available Formats

Design Guide for Xilinx FPGA Power Management Systems

1 Introduction

Field Programmable Gate Arrays (FPGAs) are a class of programmable logic devices based on an array of logic cells surrounded by a periphery of input/output cells. These ICs can b e programmed in the field after manufacture in order to implement specific design functions. The advanced technologies and smaller geometries used to fabricate the devices require increasingly lower supply voltages for the core voltage (3.3, 2.5, 1.8, 1.5 and 1.2V are typical core voltages). While the core supply voltage is decreasing, these devices must continue to support both newer and legacy interfaces, potentially requiring an I/O supply voltage which is different from the core voltage. Typical Vccio voltages can range from 1.2V up to 3.6V. Legacy applications may require a 5V I/O supply. ST Microelectronics supports a complete power management solution for low and mixed-voltage FPGAs. This design guide serves to address the voltage and current requirements, including voltage sequencing, ramping, current limiting, and power estimation, for Xilinx FPGA families. The power requirements listed here are based on the most current information available. Designers should take care to consult Xilinxs application literature for the most up to date information.

2 Xilinx FPGA Requirements

2.1 Voltage Levels Xilinx FPGAs require a supply voltage of 3.3, 2.5, 1.8, 1.5 and 1.2V for the core, depending on the specific family of FPGAs. The I/O voltage requirement depends on which I/O standards the FPGA is supporting. These voltages can range from 3. 3V to 1.2V. The Virtex-II, Virtex-II Pro and the SpartanIII also require an auxiliary voltage of 3.3V, 2.5V and 2.5V respectively. The Xilinx core, auxiliary and I/O voltage requirements for each family are listed in the table below:

Xilinx FPGA Family Virtex-II Pro Virtex-II Virtex-E/EM Spartan-II Spartan-IIE Spartan-III

Core Voltage 1.5V 1.5V 1.8V 2.5V 1.8V 1.2V

Auxiliary Voltage 2.5V 3.3V N/A N/A N/A 2.5V

I/O Voltage 1.5 3.3V 1.5 3.3V 1.2 3.3V 1.5 3.3V 1.2 3.3V 1.2 3.3V

Version 1.2 October 04

1/11

Design Guide for Xilinx FPGA Power Management Systems

2.2 Power-On Requirements At power-up, a minimum level of core supply current must be provided to the Xilinx FPGAs in order to properly power-up and configure. In addition, the core voltage Vccint ramp time must be within a certain range, as specified in the datasheet for each family. The power supplies must also rise monotonically with a voltage droop less than 10mV/ms. The power-up current and ramp time specifications for each family are as follows:

Xilinx FPGA Family Virtex-II Pro Virtex-II Virtex-E Spartan-II Spartan-IIE Spartan-III

Min Power-Up Current (mA) 850 2550 350 1300 500 2000 250 2000 300 700 55 340

Ramp Time Specification 100us < T ccpo < 50ms 1ms < T ccpo < 50ms 2ms < T ccpo < 50ms Tccpo < 50ms 2ms < T ccpo < 50ms no limit<Min Tcco< 2ms

The following circuits address the power-on ramp up requirement, allowing for consistent and reliable power-up:

Vreg Vin

C2 R1

STT5NF20V

Vin

Vout GND

C3

Vout

C4

Vreg: LFxx KFxx L4931

Vin

Power up time: TS921 t=-(R1*C1)*log(1-Vout/Vin) C3=C4 C2,C3,C4 depend on the Vreg

C1

Fig 2.1- Power Up: Fixed output

The schematic in Figure 2.1 allows the designer to increase the output voltage slew rate of a fixed output Voltage Regulator. The MOSFET (STT5NF20V) acts as a pass element that is gradually switched on following the R1 and C1 charging time. t=-(R1*C1)*log(1-Vout/Vin) Note : For this solution, the delta Vin -Vout must be higher than the Q1 Vgs

2/11

Design Guide for Xilinx FPGA Power Management Systems

Vreg Vin

C1 R1

Vin Adj

Vout

C3

Vout

C1,C2= Depends on the Vreg Note: Vout starts from Vref

Vreg: LD108x LD1117 LD298x C2 R2

Vout=Vref+R2*Vref/R1(1-e-t/(R2*C2)) Vout=Vref * (R1+R2)/R1 Power up time: t=-(R2*C2)*log(1-((Vout-Vref)/Vin)*R1/R2)

Fig 2.2 - Power Up: Adjustable Output LDO Without GND pin

Using an adjustable Voltage regulator such as the LD1085 or the LD1117, it is easy to implement a controlled output voltage slew rate. A capacitor (C2) is placed in parallel to the low side of the bridge resistor (R2), which is used to set the output voltage level. Upon power up, the output of this circuit goes to the Vref (1.25V) then, from 1.25V to the set Vout Vout=Vref * (R1+R2)/R1 It will follow the R2* C2 charging time as follows: t=-(R2*C2)*log(1-((Vout-Vref)/Vin)*R1/R2)

Vin

C1 R1

LD29150 LD29300 Vin Vout Inh GND Adj

R3 C3

Vout

Vout=Vref * (R3+R4)/R4 D1 SO2222A On/Off R2 Q1 C2 R4 TS951 IC1 Q1=SO2222A IC1=TS921, TS951 D1= 1N4148 Power up time : t=-(R1*C2)*log(1-Vout/Vin)

Fig 2.3 - Power Up: Adjustable Output LDO With GND pin

The LD29xxx family offers the best solution to implement a controlled output voltage rise time. Due to the internal voltage reference, which is referred to GND, it is possible to let the output voltage go from 0V to the set value ( Vout=Vref * (R3+R4)/R4 ) according to the R1*C2 charging time. t=-(R1*C2)*log(1-Vout/Vin)

3/11

Design Guide for Xilinx FPGA Power Management Systems

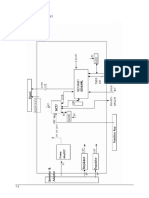

2.3 Power Sequencing The Virtex-II Pro family requires that the auxiliary power supply, Vccaux, power up before or at the same time as Vcco. For the Virtex-II, the power supplies can power up in any sequence, but if any Vcco bank powers up before V ccaux, then each bank will draw up to 300mA until the Vccaux supply powers up. (This does not harm the device.) Powering up the core supply voltage before the I/O supply voltage is generally recommended for most FPGA families. When power sequencing is needed, the following circuit will control the powerup and power-down sequence of the Vcc core and the V cco supply voltages.

Vin

R1 R4 C1 D1 IC1 74V1G14 C4 Inh GND Vin Vreg1 C6 Vreg2: LD108x LD1117 Vin Vreg2 C3 Adj R3 C5 Vout

Vcc I/O

Vreg1: LD29150 LD29300 LFxx KFxx L4931

Vout

Vcc Core

LD298x

C3,C4,C5 and C6= Depending on the Vreg Note: Vcc Core starts from Vref Vcc Core=Vref+R2*Vref/R1(1 -e-t/(R2*C2) )

R2 C2

Vcc Core=Vref * (R1+R2)/R1 D1= 1N4148

Fig 2.4 - Power Up Plus Power Sequencing With A Fixed Output LDO

Vreg2 powers-up the core with a slew rate controlled output voltage, due to R2 and C2 t=-(R2*C2)*log(1-((Vout-Vref)/Vin)*R3/R2) The I/O section is powered through Vreg1 , after a delay due to R1 and C1 t=-(R1*C1)*log(1-VtIC1/Vin)

Master

Vin

C2

Vin LD29150 Inh LD29300 R1 Q1 IC1a GND

Vout R3 Adj D1 R4 C4

Vcc I/O

On/Off R2 C1

Vin

Q1=SO2222A IC1=TS922, TS952 D1= 1N4148 Power up time : t=-(R1*C2)*log(1-Voutx /Vin) C3

Vin Inh LD29150 LD29300 Slave GND IC1b

Vout R5 C5 Adj R6 D1

Vcc Core

Fig 2.5 - Power Up Plus Power Sequencing With An Adj. Output LDO

This solution is suitable for those applications that require both a controlled slew rate on power up and power sequencing for the core and I/O voltages. Both outputs rise and fall with the same slew rate, set by R1 and C1. The different output voltage levels result in different power up times that create a power up sequence for the two supplies: t=-(R1*C2)*log(1-Vccx/Vin) Note : Vout Master must be higher than Vout Slave

4/11

Design Guide for Xilinx FPGA Power Management Systems

2.3 High Current Application Depending on the FPGA density and design, the current supply requirements can be higher that 3A . In those cases, and when a better efficiency is needed, the linear solution is no longer suitable. The following schematics are an example of a solution meeting high current requirements. a) This solution is suitable for those devices (such us SpartanIII and VirtexII) with: I. Core voltage range from 1.2V to 5V with a current capability up to 20A II. I/O voltage from 1.2V to 5V with a current capability up to 8A III. Auxiliary supply voltage form 1.2 V to 5V up to 800mA

VI C1 100 GNDI R1 C2 4.7 VC C3 100n GND SS C4 100n F R OSC EAREF C5 100n 1 5 7 R3 510 R OCSE 3 C6 1n BOOT 1 1 1 D1 1N414 C7 100n F UGAT PHAS LGAT PGND Q2 Q4 Q6 R5 4.7 K C11 47n F R7 open 14K 6.98K 4.66K 2.61K 1.74K 1.04 Vout 0.9 1.2 1.5 1.8 2.5 3.3 5.0 Q1 Q3 Q5 Q1 to Q6 STS11NF30L

VOUT= Vref(1+R5/R7)

L1 3H

VOUT Core

4 2 8

U1 L6910

1 1 3 6 5

D2 STPS3L25

C12 100F

1 VREF C8 100n F

9 PGOO

COMP

R4 2.7 C9 15n C10 1.5n

R6 1 K R7

Vcc Core 1.2V to 5V Up to 20A

C1 100

R3 510 OCSET

C6 1n BOOT 1 2

D1 1N414 8

C7 100n UGAT L1 3H PHAS LGAT PGN Q2 Q1 D2 STPS3L25 VOUT I/O

R1 C2 4.7

VCC 1 C3 100n GND SS 7 4 2 8

1 1

C4 100n

R 2

U2 L6910

1 1 9

C12

OSC EAREF

PGOOD R5 VFB R 6 C1 1

Vcc I/O 1.2V to 5V Up to 8A

FPGA

C5 100n

1 VREF C8 100n

C9 R4 15n 2.7 C10 1.5n

R 10K RUN Vcc C1 10uF Sync COM P C2 220pF 6 7 1 SW 5 R 500 3 PGOOD K VFB L 6.8u VOUT AUX

Vcc AUX 1.2V to 5V Up to 0.8mA

U3 8 L6926 2 3

4 GND

R2 200 R1 100

C4 47u F

Thanks to the programmable soft start (by C4) and the power good feature of the L6910, the above circuit can be adapted to meet all the requirements of power-up and power sequencing. If the Vaux section is not needed, the L6926 with its related circuitry can be omitted.

5/11

Design Guide for Xilinx FPGA Power Management Systems

b) This solution is good for medium power requirements: I. Core voltage range from 1.2V to 5V with a current capability up to 20A II. I/O voltage from 1.2V to 5V with a current capability up to 3.5A

VI C1 100 R3 510 OCSE R1 10R C2 4.7 VCC 1 C3 100n GND SS C4 100n R 2 OSC EAREF C5 100n 7 4 2 8 1 VREF C8 100n 9 3 C6 1n BOOT 1 1 1 1 U1 L6910 1 6 5 PGOOD C10 1.5n D1 1N414 C7 100n UGATE PHASE LGATE PGND VFB COMP C9 15n R4 2.7 R6 1 K R7 Q Q Q R5 4.7 Q 1 Q Q L1 3H D2 STPS3L25 Q1 to Q6 STS11NF30

VOUT= Vref(1+R5/R7)

GNDI

VOUT 1 C12 100F GNDOU

C11 47n R7 open 14K 6.98K 4.66K 2.61K 1.74K 1.04 Vout 0.9 1.2 1.5 1.8 2.5 3.3 5.0

Vcc Core 1.2V to 5V Up to 20A

R 10 VC C1 100 R2 20 K VCC OSC COMP C2 2.7n R1 9.1 C3 22n SS 7 8 1 1 1 4 1 0

INH 1 8

SYNC 9

BOOT C6 220n OUT OUT VFB L1 150 R

FPGA

U2 L4973

5 13 14

VOUT

2 3 1 1

REF C5 1

R4 4.7 D1 STPS5L4

C7 100

C4 470n

GND

Vcc I/O 1.2V to 5V Up to 3.5A

GND

The number of MOSFETs depends on the core current requirements. For current up to 10A, only one MOSFET pair is necessary.

6/11

Design Guide for Xilinx FPGA Power Management Systems

c) With a current lower than 4A the controller plus MOSFET solution can be replaced by a switching regulator, as showed on the schematic below I. Core Voltage range from 1.2V to 5V with a current capability up to 3.5A II. I/O voltage from 1.5V to 5V with a current capability up to 2A

INH VCC VIN 8 to 55 V C1 100F R2 20K VCC OSC C2 2.7nF R1 9.1K COMP SS 7 8 1 11 17 4 C4 470nF 5 6 10 18

SYNC 9 BOOT C6 220nF OUT OUT VFB 12 13 14 15 16 REF R4 4.7K L1 150H R3 C7 100F VOUT CORE 1.2 V to 5V 3.5A

L4973

2 3

C3 22nF

GND

C5 1F

D1 STPS5L40

FPGA

L VOUT I/O 1.5V t o 5 V 2A

VCC

OUT 8 1

C1 10uF 22nF C3 C2 220pF SYNC R3 4.7k COMP 4

L5973D

2 GND 7 3

VREF 6 5 FB INH D1 3.3V

33uH R1 5.6k C4 100uF R2 3.3k STPS340U

2.4 Current Limiting The Spartan-II and Spartan-IIE families require current limiting for situations where the circuit powered by the power supply exceeds a set current rating. During power-up, the Spartan-II and -IIE devices experience an in-rush current when the core voltage is between 0.6V and 0.8V. ST Microelectronics voltage regulators have internal current limiting features which limit the output of the devices once the output current has exceeded the limit. The output current limit can be found in the operating section of the ST Microelectronics voltage regulators datasheets.

2.5 Power Consumption Estimation The power consumption of an FPGA depends on a number of different factors and is highly dependent on the design. Accurate power estimation methods must be used to ensure that a power supply system meets the FPGAs requirements for a given design. Xilinx provides a Web Power Estimator, available on their website, specifically for this purpose. This calculator considers design resource usage, toggle rates, operating clock frequencies, I/O usage and many other factors to generate the power estimation.

7/11

Design Guide for Xilinx FPGA Power Management Systems

2.6 Suggested Xilinx FPGA Power Supply Solutions The following table lists the recommended linear and switching voltage regulators for each Xilinx FPGA: ST Microelectronics Voltage Regulators

Xilinx Part Number

Virtex-II Pro

XC2VP2 XC2VP4 XC2VP7 XC2VP20 XC2VP30 XC2VP40 XC2VP50 XC2VP70 XC2VP100 XC2VP125

LINEAR

Vccint

KF15 KF15 KF15 LD11172 LD1117 LD29150xx15 LD29150xx15 LD29300xx15 LD29300xx15 LD29300xx15

SWITCHING

Vcco

1

Vccaux

L4931ABD25x L4931ABD25x L4931ABD25x L4931ABD25x L4931ABD25x L4931ABD25x L4931ABD25x L4931ABD25x L4931ABD25x L4931ABD25x

Vccint

Vccaux

L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D

Vcco 1

LD29300 LD29300 LD29300 LD29300 LD29300 LD29300 LD29300 LD29300 LD29300 LD29300 L5972D L5972D L5973D L5973D L5973D

1

L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D

Virtex-II

XC2V40 XC2V80 XC2V250 XC2V500 XC2V1000 XC2V1500 XC2V2000 XCE2V3000 XCE2V4000 XCE2V6000 XCE2V8000

Vccint

L4931ABD15TR L4931ABD15TR L4931ABD15TR L4931ABD15TR L4931ABD15TR KF15 KF15 KF15 LD11172 LD1117 LD29150xx15

Vccaux

LD2981Cxx33 LD2981Cxx33 LD2981Cxx33 LD2981Cxx33 LD2981Cxx33 LD2981Cxx33 LD2981Cxx33 LD2981Cxx33 LD2981Cxx33 LD2981Cxx33 LD2981Cxx33

Vcco

Vccint

L4973 L6910 L4973 L6910 L4973 L6910 L4973 L6910 L4973 L6910 L4973 L6910 L4973 L6910 L4973 L6910 L4973 L6910 L4973 L6910 L4973 L6910

Vccaux

L6926D L6926D L6926D L6926D L6926D L6926D L6926D L6926D L6926D L6926D L6926D

Vcco 1

L4973 L4973 L4973 L4973 L4973 L4973 L4973 L4973 L4973 L4973 L4973

L4931 , LD29300 L4931 , LD29300 L4931 , LD29300 L4931 , LD29300 L4931 , LD29300 L4931 , LD29300 L4931 , LD29300 L4931 , LD29300 L4931 , LD29300 L4931 , LD29300 L4931 , LD29300

Virtex-EM and Virtex -E

XCV50E ( C ) XCV100E ( C ) XCV200E ( C ) XCV300E ( C ) XCV400E ( C ) XCV405E ( C ) XCV600E ( C ) XCV812E ( C ) XCV1000E ( C ) XCV1600E ( C ) XCV2000E ( C ) XCV2600E ( C ) XCV3200E ( C ) XCV50E ( I ) XCV100E ( I ) XCV200E ( I ) XCV300E ( I ) XCV400E ( I ) XCV405E ( I ) XCV600E ( I ) XCV812E ( I ) XCV1000E ( I ) XCV1600E ( I ) XCV2000E ( I ) XCV2600E ( I ) XCV3200E ( I )

Vccint

LF18Cxx LF18Cxx LF18Cxx LF18Cxx LF18Cxx LF18Cxx LF18Cxx LD1117Axx18 LD1117Axx18 LD1117Axx18 LD1117Axx18 LD1086xx18 LD1086xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18 LD1085xx18

Vccaux

-------------------------------------------------------------------------------

Vcco1

L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931

Vccint

Vccaux

L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D

Vcco 1

L5970D L5970D L5970D L5970D L5972D L5972D L5973D L5973D L5973D L5973D L5973D L5973D L5973D L5973D L5973D L5973D L5973D L5973D L5973D

The required I/O current will depend on several design specific factors, including I/O usage, loading, etc. Designers should use FPGA power estimator tools to determine the required Iccio current. 2 The adjustable version of the LD1117 regulator can be configured to supply 1.5V.

8/11

Design Guide for Xilinx FPGA Power Management Systems

ST Microelectronics Voltage Regulators

Xilinx Part Number Spartan II

XC2S15 (0 oC < Tj) XC2S30 (0 oC < Tj) XC2S50 (0 oC < Tj) XC2S100 (0oC < Tj) XC2S150 (0oC < Tj) XC2S15 (Tj <0oC) XC2S30 (Tj <0oC) XC2S50 (Tj <0oC) XC2S100 (Tj <0 oC) XC2S150 (Tj <0 oC)

LINEAR Vccint

KF25xx ---KF25xx ---KF25xx ---KF25xx ---KF25xx ---LD1085xx25 ---LD1085xx25 ---LD1085xx25 ---LD1085xx25 ---LD1085xx25 ----

SWITCHING Vcco 1

LFxx, KFxx LFxx, KFxx LFxx, KFxx LFxx, KFxx LFxx, KFxx

Vccint

L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973

Vcco 1

L6926D L6926D L6926D L6926D L6926D L6926D L6926D L6926D L6926D L6926D

/ LD29300xx25 / LD29300xx25 / LD29300xx25 / LD29300xx25 / LD29300xx25

LFxx, KFxx LFxx, KFxx LFxx, KFxx LFxx, KFxx LFxx, KFxx

Spartan - IIE

XC2S50E ( C ) XC2S100E ( C ) XC2S150E ( C ) XC2S200E ( C ) XC2S300E ( C ) XC2S400E ( C ) XC2S600E ( C ) XC2S50E ( I ) XC2S100E ( I ) XC2S150E ( I ) XC2S200E ( I ) XC2S300E ( I ) XC2S400E ( I ) XC2S600E ( I )

Vccint

LF18C , LD1086xx18, ---LF18C , LD1086xx18, ---LF18C , LD1086xx18, ---LF18C , LD10 86xx18, ---LF18C , LD1086xx18, ---LF18C , LD1086xx18, ---LF18C , LD1086xx18, ---LF18C , LD1086xx18, ---LF18C , ---LF18C , ---LF18C , ---LF18C , LD29150xx18 LD29150xx18 LD29150xx18 LD29150xx18 LD29150xx18 LD29150xx18 LD29150xx18 LD29150xx18

Vcco 1

L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931 L4931

Vccint

L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L5973D or L4973 L4973 L4973

Vcco 1

L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L 5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D L6926D or L5970D

LD1086xx18, LD29150xx18 LD1086xx18, LD29150xx18 LD1086xx18, LD29150xx18 LD1086xx18, LD29150xx18

LD1085xx18, LD29300xx18 LD1085xx18, LD29300xx18

Spartan III

XC3S50 XC3S200 XC3S400 XC3S1000 XC3S1500 XC3S200 0 XC3S4000 XC3S5000

Vccint

LD1117Axx12 LD1117Axx12 LD1117Axx12 LD1117Axx12 LD1117Axx12 LD1117Axx12 LD1117Axx12 LD1117Axx12

Vccaux

KF25xx KF25xx KF25xx KF25xx KF25xx KF25xx KF25xx KF25xx

Vcco1

LD29300 LD29300 LD29300 LD29300 LD29300 LD29300 LD29300 LD29300

Vccint

L4973 L4973 L4973 L4973, L6910 L4973, L6910 L4973, L6910 L4973, L6910 L4973, L6910

Vccaux

L692 6D L6926D L6926D L6926D L6926D L6926D L6926D L6926D

Vcco1

L4973 L4973 L4973 L4973 L4973 L4973 L4973, L6910 L4973, L6910

The required I/O current will depend on several design specific factors, including I/O usage, loading, etc. Designers should use FPGA power estimator tools to determine the required Iccio current.

9/11

Design Guide for Xilinx FPGA Power Management Systems

3 Summary

3.1 Supply Voltage Regulator Options Xilinx power supply requirements for the core, I/O, and auxiliary power supplies include voltage outputs ranging from 1.2V to 5V and current outputs from tens of milliamps to multiple amperes. Depending on the system requirements, a linear or a switching regulator may be used to supply power to the FPGA. ST Microelectronics makes both linear and switching regulators with a wide variety of output voltages and output current levels. In selecting a voltage regulator for use in a Xilinx FPGA power supply design, it is important to understand the tradeoffs between linear and switching regulators. Linear regulators are the best choice when board space is at a premium, low output noise is important or a fast response to inputs and transients is required. Linear regulators provide low to medium output currents with a simple desig n approach. An input capacitor is typically used to reduce the inductance and noise on the input to the LDO. The LDO also requires a capacitor on the output in order to handle system transients and to provide stability. ST Microelectronics offers voltage regulators (the LD298x and LD398x families) which allow low ESR ceramic capacitors to be used on the outputs, thereby reducing overall system cost. In addition, dual-output devices can be used to supply power for the core and I/O voltages in a single device. The ST2L05 offers fixed outputs in 1.5, 1.8, 2.5, 2.8, 3.0, 3.3V as well as an adjustable output option from 1.25V to 5.7V. Switching regulators are best used when design efficiency is critical and/or large output currents are required. Switching supplies are known for excellent efficiency, but the output is more susceptible to noise due to the switching nature of the regulator. Switching regulators require inductors and input and output capacitors for DC-DC conversion.

3.2 Conclusion The advancement of fabrication technologies and the shrinking of process geometries increase the complexity of the power management system required to supply the current generation of FPGAs. Todays FPGA designer must address the devices specific voltage and current requirements including voltage sequencing, ramping, current limiting and power estimation. Designers must also choose which type of voltage regulator is best suited to their application. Depending on the system requirements, a linear or a switching regulator may be the best choice for powering the FPGA. ST Microelectronics makes both linear and switching regulators with a wide variety of output voltages and output current levels to provide complete power management solutions for Xilinx FPGAs.

10/11

Design Guide for Xilinx FPGA Power Management Systems

Appendix A

The following table lists the output current for the recommended voltage regulators in this application note. Other regulators are also available, please consult your ST sales representative or the ST website, www.st.com, for the complete product portfolio.

ST Voltage Regulator Max Output Current Output Voltage Output Current 1.5 5.0V 1.25 12V 5V Adj. 3.3V 1.5V 1.8V 2.5V 1.2 5.0V, Adj Adj (0.6 - 5V) Adj (1.23 35V) 1.2 5V, Adj 1.5 12V, Adj 1.5 8V, Adj Adj Adj (1.235 35V ) Adj (1.235 35V ) 1.5 12V, Adj 1.5 9V, Adj Adj (0.5 50V) Adj (0.9 5V) 100mA 250mA 450mA 450mA 500mA 500mA 500mA 500mA 800mA 800mA 1A 1A 1.5A 1.5A 1.5A (switch current) 2A (switch current) 2.5A (switch current) 3A 3.0A 3.5A 20A

Part Number LD2981 L4931 ST730A ST750A ST763A KF15 LF18 KF25 LD1117 L6926D L5970 LD1117A LD1086 LD29150 MC34063 L5972D L5973 LD1085 LD29300 L4973 L6910

Input Voltage 3.3 - 20V 5.2 11V 4 11V 3.3 11V 2.5 20V 2.5 20V 2.5 20V 2.4 15V 2 5.5V 4.4 36V 2.5 -10V 4.1 - 30V 2.5 13V 3 40V 4.4 36V 4.4 36V 2.85 30V 2.5 13V 8 55V 5 12V

Topology Linear Linear Switching Switching Switching Linear Linear Linear Linear Switching Switching Linear Linear Linear Switching Switching Switching Linear Linear Switching Driver + STS9DNH3LL

(Vout+1V) 16V

11/11

You might also like

- Spartan-6 FPGA Data SheetDocument89 pagesSpartan-6 FPGA Data SheetfcikanNo ratings yet

- Ds 162Document89 pagesDs 162Erik TeichmannNo ratings yet

- Tps 65217 CDocument86 pagesTps 65217 CcosmicfundooNo ratings yet

- Voltage To Frequency ConverterDocument7 pagesVoltage To Frequency ConverterRodfer SorianoNo ratings yet

- Viper 100Document8 pagesViper 100SeanNo ratings yet

- Viper 100 ADocument31 pagesViper 100 AvasilesicoeNo ratings yet

- 7-2 Main Board Part: 7 Block DiagramsDocument14 pages7-2 Main Board Part: 7 Block DiagramsAlbert OstNo ratings yet

- LCD221SD Service ManualDocument41 pagesLCD221SD Service Manual1cvbnmNo ratings yet

- Datasheet - HK rt8110 7327105 PDFDocument14 pagesDatasheet - HK rt8110 7327105 PDFLuis CarlosNo ratings yet

- AM5888SDocument10 pagesAM5888SproctepNo ratings yet

- Iso 7816Document19 pagesIso 7816nalini veeraragaveluNo ratings yet

- DRV 8834Document30 pagesDRV 8834Anonymous 10cG5eRp8100% (1)

- SG6105 Datasheet, Pinout, Application Circuits Power Supply Supervisor Regulator PWMDocument13 pagesSG6105 Datasheet, Pinout, Application Circuits Power Supply Supervisor Regulator PWMBeatrizEstevesNo ratings yet

- LCT B85TDU22H Service ManualDocument59 pagesLCT B85TDU22H Service ManualCristina NistorNo ratings yet

- VT-pro 525-625 Service ManualDocument13 pagesVT-pro 525-625 Service ManualMuhammad ShoaibNo ratings yet

- CPWRAN10Document5 pagesCPWRAN10Vasco RodriguesNo ratings yet

- A 2918 SW Data SheetDocument8 pagesA 2918 SW Data SheetGustavo LunaNo ratings yet

- Delta PLC DVP SS ModelDocument4 pagesDelta PLC DVP SS ModelTarun SonwaneNo ratings yet

- 7 A H-Bridge for DC-Motor ApplicationsDocument29 pages7 A H-Bridge for DC-Motor ApplicationsJoão JoséNo ratings yet

- Up7706 DatasheetDocument12 pagesUp7706 DatasheetFernando DupuyNo ratings yet

- Atmel 9372 Smart RF Ata8520 DatasheetDocument23 pagesAtmel 9372 Smart RF Ata8520 Datasheetinuyasha62No ratings yet

- Uc 3845Document23 pagesUc 3845Bahram RN100% (1)

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesGiovanni Carrillo VillegasNo ratings yet

- AT17C65Document10 pagesAT17C65meroka2000No ratings yet

- LIN Transceiver: Automotive and IndustrialDocument19 pagesLIN Transceiver: Automotive and IndustrialRayan88No ratings yet

- Viper22a Equivalent PDFDocument16 pagesViper22a Equivalent PDFXande Nane Silveira0% (1)

- Single Synchronous Buck PWM DC-DC ControllerDocument16 pagesSingle Synchronous Buck PWM DC-DC Controllerbachet56No ratings yet

- Samsung Plasma Training ManualDocument57 pagesSamsung Plasma Training ManualDamiao100% (1)

- Samsung Plasma Training ManualDocument57 pagesSamsung Plasma Training ManualevaristoNo ratings yet

- 1-2-4-Bit Bidirectional Voltage-Level Translator With Automatic Direction Sensing and 15kV ESD ProtectionDocument1 page1-2-4-Bit Bidirectional Voltage-Level Translator With Automatic Direction Sensing and 15kV ESD ProtectionSabeur ShabouNo ratings yet

- EEPROM 24LC512 - 21754eDocument26 pagesEEPROM 24LC512 - 21754eMarcelo Azevedo BragaNo ratings yet

- P 7132 BGM en A5Document32 pagesP 7132 BGM en A5Orlando Jose Romero ReyesNo ratings yet

- PLC DVP28SV11TDocument20 pagesPLC DVP28SV11TSarah DoyleNo ratings yet

- DatasheetDocument13 pagesDatasheetkishore kumarNo ratings yet

- Skhi 22B DatasheetDocument9 pagesSkhi 22B DatasheetRakesh RoyNo ratings yet

- Samsung Sync Master 930bf Chassis Bi17ds Bi19ds Ls17 19bidks SMDocument74 pagesSamsung Sync Master 930bf Chassis Bi17ds Bi19ds Ls17 19bidks SMBradaric BrunoNo ratings yet

- TD - Datasheet TK400 NDDocument4 pagesTD - Datasheet TK400 NDSocaciu VioricaNo ratings yet

- Fx2n 2ad User S Guide 2ch IDocument8 pagesFx2n 2ad User S Guide 2ch InguyendaibkaNo ratings yet

- Ds191 XC7Z030 XC7Z045 Data SheetDocument67 pagesDs191 XC7Z030 XC7Z045 Data SheetApurv SinghNo ratings yet

- DVP20SX211RDocument8 pagesDVP20SX211RcurielvicNo ratings yet

- High-Efficiency Controllers for Notebook ComputersDocument28 pagesHigh-Efficiency Controllers for Notebook ComputerscNo ratings yet

- Trace Elliot Velocette 12r Schematic DiagramDocument9 pagesTrace Elliot Velocette 12r Schematic DiagramjonnycoolNo ratings yet

- MAX1858 Evaluation Kit: General Description FeaturesDocument7 pagesMAX1858 Evaluation Kit: General Description Features9183290782No ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- MC14017B Decade Counter: PDIP 16 P Suffix CASE 648Document9 pagesMC14017B Decade Counter: PDIP 16 P Suffix CASE 648JossuarmmNo ratings yet

- HP vs-15 (ET)Document46 pagesHP vs-15 (ET)Esmerisa GonzálezNo ratings yet

- Ibm Lenovo E420 COMPAL LA-1331Document83 pagesIbm Lenovo E420 COMPAL LA-1331Abubakar SidikNo ratings yet

- Reversible Motor Driver IC GuideDocument8 pagesReversible Motor Driver IC Guideeldel81No ratings yet

- IO Wiring DiagramsDocument172 pagesIO Wiring DiagramsNikola MilosevicNo ratings yet

- 1 - General DescriptionDocument9 pages1 - General DescriptiondazcornishNo ratings yet

- Cost-Effective, 2A Sink/Source Bus Termination Regulator: General Description FeaturesDocument13 pagesCost-Effective, 2A Sink/Source Bus Termination Regulator: General Description FeaturesMostapha BenaliNo ratings yet

- 24LC512Document26 pages24LC512tecpowerNo ratings yet

- High Efficiency Notebook Computer Main Power Supply ControllerDocument26 pagesHigh Efficiency Notebook Computer Main Power Supply Controllerpiron123No ratings yet

- RT8206A/B High-Efficiency Controllers for Notebook ComputersDocument26 pagesRT8206A/B High-Efficiency Controllers for Notebook ComputersJoseph BernardNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- 70575Document19 pages70575bmmostefaNo ratings yet

- 70572-AN601-Unclamped Inductive Switching Rugged MOSFETs For Rugged EnvironmentsDocument8 pages70572-AN601-Unclamped Inductive Switching Rugged MOSFETs For Rugged EnvironmentsbmmostefaNo ratings yet

- Input Filtering AnDocument6 pagesInput Filtering AnbmmostefaNo ratings yet

- AB-8-Selection of MOSFETs in Switch ModeDocument4 pagesAB-8-Selection of MOSFETs in Switch ModebmmostefaNo ratings yet

- Irfbe20pbf Power MosfetDocument8 pagesIrfbe20pbf Power MosfetbmmostefaNo ratings yet

- A Design Methodology For Power ElecronicsDocument6 pagesA Design Methodology For Power ElecronicsbmmostefaNo ratings yet

- Sss6n70a-Advanced Power MosfetDocument7 pagesSss6n70a-Advanced Power MosfetbmmostefaNo ratings yet

- Zeners 1N4370A - 1N4372A 1N746A - 1N759A: Absolute Maximum RatingsDocument5 pagesZeners 1N4370A - 1N4372A 1N746A - 1N759A: Absolute Maximum RatingsAxel JacobNo ratings yet

- Thomson SemiconductorsDocument5 pagesThomson SemiconductorsbmmostefaNo ratings yet

- Data Sh01 - Transformer Selection Guide DS1 - InfineonDocument11 pagesData Sh01 - Transformer Selection Guide DS1 - InfineonbmmostefaNo ratings yet

- AN1166Document16 pagesAN1166bmmostefaNo ratings yet

- NM27C256 262,144-Bit (32K X 8) High Performance CMOS EPROM: General DescriptionDocument12 pagesNM27C256 262,144-Bit (32K X 8) High Performance CMOS EPROM: General DescriptiondimkaleidoscopeNo ratings yet

- Ref 37 - Pub56-Vlad Grigore-Institute of Intelligent Power Electronics Publications-ToPOLOGICAL ISSUES in SINGLE-PHASEDocument114 pagesRef 37 - Pub56-Vlad Grigore-Institute of Intelligent Power Electronics Publications-ToPOLOGICAL ISSUES in SINGLE-PHASEbmmostefaNo ratings yet

- Irfbe20pbf Power MosfetDocument8 pagesIrfbe20pbf Power MosfetbmmostefaNo ratings yet

- MS-523-Fairchild Switch Family CharacteristicsDocument3 pagesMS-523-Fairchild Switch Family CharacteristicsbmmostefaNo ratings yet

- Ffmboo-D Maksimovie - FF PWM For Boost DC DC PWR CVDocument2 pagesFfmboo-D Maksimovie - FF PWM For Boost DC DC PWR CVbmmostefaNo ratings yet

- LM324 - Amp Op X4Document17 pagesLM324 - Amp Op X4huvillamilNo ratings yet

- Iris4007 Integrated SwitcherDocument6 pagesIris4007 Integrated SwitcherbmmostefaNo ratings yet

- Siu97 - Analysis and Experimental Evaluation of Single-Switch Fast-Response SwitchingDocument7 pagesSiu97 - Analysis and Experimental Evaluation of Single-Switch Fast-Response SwitchingbmmostefaNo ratings yet

- Singer1992 - Canonical Modeling of PowerDocument7 pagesSinger1992 - Canonical Modeling of PowerbmmostefaNo ratings yet

- Hc11a1-Hcmos Microcontroller UnitDocument174 pagesHc11a1-Hcmos Microcontroller UnitbmmostefaNo ratings yet

- Fqpf2n70 700v N Chanel MosfetDocument8 pagesFqpf2n70 700v N Chanel MosfetbmmostefaNo ratings yet

- 74AC161-Synchronous Presettable Binary CounterDocument11 pages74AC161-Synchronous Presettable Binary CounterbmmostefaNo ratings yet

- IEE94-RW Ericson - PWR Source Element and Its PropertiesDocument7 pagesIEE94-RW Ericson - PWR Source Element and Its PropertiesbmmostefaNo ratings yet

- 74HC14-Hix Inverting Schmitt TriggerDocument7 pages74HC14-Hix Inverting Schmitt TriggerbmmostefaNo ratings yet

- Art96 MCH G - A New Control Strategy To Achieve Sinusoidal Line Current in A Cascade Buck-Boost Converter-IEEEDocument9 pagesArt96 MCH G - A New Control Strategy To Achieve Sinusoidal Line Current in A Cascade Buck-Boost Converter-IEEEbmmostefaNo ratings yet

- CD40106 Hex Schmitt Trigger DatasheetDocument6 pagesCD40106 Hex Schmitt Trigger Datasheetlookb64No ratings yet

- A Mixed Signal AsicDocument6 pagesA Mixed Signal AsicbmmostefaNo ratings yet

- Integrated Magnetic P Esc 93Document7 pagesIntegrated Magnetic P Esc 93bmmostefaNo ratings yet

- 10 1 1 8 3813Document6 pages10 1 1 8 3813yogendra12No ratings yet

- An Experimental Comparative Review - PK NanavatiDocument9 pagesAn Experimental Comparative Review - PK NanavatiPurvesh NanavatiNo ratings yet

- UAE Visa Occupation ListDocument89 pagesUAE Visa Occupation ListSiddharth JaloriNo ratings yet

- Bernard D. Marquez Eduardo M. Axalan Engr. William A.L.T. NGDocument1 pageBernard D. Marquez Eduardo M. Axalan Engr. William A.L.T. NGRhon Nem KhoNo ratings yet

- GNB Absoltye IIPDocument18 pagesGNB Absoltye IIPFederico Tellez QNo ratings yet

- Max 223C Pipeline Welding InverterDocument2 pagesMax 223C Pipeline Welding InvertermtonellyNo ratings yet

- Pilot Valve Boxes SG110ADocument2 pagesPilot Valve Boxes SG110AVictor Ruiz FuentesNo ratings yet

- CVDocument3 pagesCVDhiraj Patra100% (1)

- Hands-On Exercise Oracle 10g PL SQL - v1 0Document24 pagesHands-On Exercise Oracle 10g PL SQL - v1 0pavanNo ratings yet

- Otis Relay Coils SpecificationsDocument1 pageOtis Relay Coils SpecificationsDamian Alberto EspositoNo ratings yet

- Zit 64 BVDocument12 pagesZit 64 BVVT86No ratings yet

- Loop Back DSP Audio AppDocument12 pagesLoop Back DSP Audio AppGytis BernotasNo ratings yet

- Machine Torch Parts: T100 ConsumablesDocument2 pagesMachine Torch Parts: T100 Consumablesبسام الاغبريNo ratings yet

- Root Cause AnalysisDocument1 pageRoot Cause AnalysisSick LoveNo ratings yet

- Stampingjournal20130102 DLDocument36 pagesStampingjournal20130102 DLWaqar MansoorNo ratings yet

- Reliable Ni-Cd batteries keep railroads running smoothlyDocument8 pagesReliable Ni-Cd batteries keep railroads running smoothlyJesus LandaetaNo ratings yet

- Bill of Quantities: Fifteen-Classrooms ADocument1 pageBill of Quantities: Fifteen-Classrooms AFritz NatividadNo ratings yet

- EC6302 - Digital ElectronicsDocument6 pagesEC6302 - Digital ElectronicsAdal ArasuNo ratings yet

- Soil Analysis Bitupan LastDocument25 pagesSoil Analysis Bitupan Lastbitupon boraNo ratings yet

- Volvo FMX: Product Guide - Euro 3-5Document24 pagesVolvo FMX: Product Guide - Euro 3-5HiT Dayat100% (2)

- HandRail Specsgf For CfvdrfsDocument3 pagesHandRail Specsgf For CfvdrfsTarek TarekNo ratings yet

- MEEN 364 Lecture 4 Examples on Sampling and Aliasing PhenomenaDocument5 pagesMEEN 364 Lecture 4 Examples on Sampling and Aliasing PhenomenaHiren MewadaNo ratings yet

- Masterful WiiFlow v4.2.3 Pack with Numerous UpdatesDocument4 pagesMasterful WiiFlow v4.2.3 Pack with Numerous UpdatesYulianNo ratings yet

- Terumo BCT Trima Accel Blood Collection System - Service ManualDocument340 pagesTerumo BCT Trima Accel Blood Collection System - Service Manualmorton1472No ratings yet

- PDF 256372311 Pec QC With Answerpdf DDDocument6 pagesPDF 256372311 Pec QC With Answerpdf DDLee Robert OlivarNo ratings yet

- Monopoles and Electricity: Lawrence J. Wippler Little Falls, MN United StatesDocument9 pagesMonopoles and Electricity: Lawrence J. Wippler Little Falls, MN United Stateswaqar mohsinNo ratings yet

- ABB 4 Pole Contactor, 230V, 40ADocument1 pageABB 4 Pole Contactor, 230V, 40ASEERALANNo ratings yet

- Cisco SD-WAN Intro SOLRST-2006 PDFDocument10 pagesCisco SD-WAN Intro SOLRST-2006 PDFffusaroNo ratings yet

- Trays and Packed TowersDocument71 pagesTrays and Packed TowersArt G. Enzi100% (1)

- Astm c243 Withdrawn.31346Document4 pagesAstm c243 Withdrawn.31346SilvioCarrilloNo ratings yet

- ME301 Mechanics of MachineryDocument2 pagesME301 Mechanics of MachineryVishnu Mohan M SNo ratings yet