Professional Documents

Culture Documents

Reporte Práctica 8

Uploaded by

Abimael SimbronOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Reporte Práctica 8

Uploaded by

Abimael SimbronCopyright:

Available Formats

INSTITUTO TECNOLGICO DE LZARO CRDENAS INGENIERA ELECTRNICA

PRACTICA NO.VIII CIRCUITO DE AMARRE DE FASE (PLL)

Alumnos:

Gamio Gonzlez Sergio Bonifacio. 09560689 Pineda Prez Rodrigo Edmundo. 09560630 Luna Paniagua Erick Paolo. 09560308

Docente:

Ing. Gmez Snchez Flix

Cd. Lzaro Crdenas Michoacn, a 15 de Noviembre del 2012.

Instituto Tecnolgico de Lzaro Crdenas

OBJETIVOS DE LA PRCTICA

Ajustar la frecuencia central de un PLL. Observar el intervalo de enganche, medir la frecuencia de captura mxima y mnima y medir el voltaje de cd a partir de la salida de FM.

MATERIAL Y EQUIPO

Fuente de alimentacin: fuente de alimentacin de 15 Vcd. Equipo: osciloscopio digital, generador de funciones. Resistores: 2 de 1 k, 1 de 4.7 k. Potencimetro: 1 de 5 k Circuito integrado: LM 565. Capacitores: 1 de 0.01 F, 1 de 0.047 F, 2 de 0.1 F, 1 de 1 F. Otros: Protoboard y alambre para conexiones.

Instituto Tecnolgico de Lzaro Crdenas

MARCO TEORICO

El circuito PLL (Phase Locked-Loop) es un sistema retroalimentado cuyo objetivo principal consiste en la generacin de una seal de salida con amplitud fija y frecuencia coincidente con la de entrada, dentro de un margen determinado. Los componentes bsicos de un PLL son: 1. El detector de fase (PD, siglas en ingles) 2. EL filtro pasa-bajas (LPF, siglas en ingles) 3. EL oscilador de controlado por voltaje (VCO, siglas en ingles) Un detector de fase es un mezclador optimizado para usarse con frecuencias de entrada iguales. ste se denomina detector de fase (o comparador de fase) dado que la cantidad de voltaje de cd depende del ngulo de fase entre las seales de entrada. A medida que el ngulo de fase cambia lo mismo ocurre con el voltaje de cd.

Un oscilador controlado por tensin o VCO (Voltage-controlled oscillator) es un dispositivo electrnico que usa amplificacin, realimentacin y circuitos resonantes que da a su salida una seal elctrica de frecuencia proporcional a la tensin de entrada. Tpicamente esa salida es una seal sinusoidal, aunque en VCOs digitales es una seal cuadrada. El PLL corrige de manera automtica la frecuencia del VCO y el ngulo de fase.

El intervalo de enganche, BC, es el intervalo de frecuencias que el VCO puede producir, y est dado por:

Donde fmx y fmn son las frecuencias mximas y mnimas del VCO.

Instituto Tecnolgico de Lzaro Crdenas

Modo de funcionamiento libre Si la seal de entrada se desconecta, el VCO oscila en modo de funcionamiento libre a una frecuencia que determinan las componentes del circuito. Captura y enganche Suponga que el PLL est en funcionamiento libre o desenganchado. El PLL se puede enganchar a la frecuencia de entrada si sta cae dentro del intervalo de captura, una banda de frecuencias centradas alrededor de la frecuencia de funcionamiento libre. La frmula para el intervalo de captura es:

PLL con el LM 565 Un resistor de temporizacin externo se conecta a la terminal 8 y el capacitor de temporizacin externo a la terminal 9. Estos dos componentes determinan la frecuencia de funcionamiento libre del VCO.

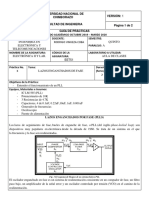

Figura 8.1 Diagrama interno de un LM565

Instituto Tecnolgico de Lzaro Crdenas

METODOLOGA

+9 V

4.7k

5k 50% 10 2 1uF 1k 8 4 5 Salida enganchada

565

3 9 1k CT 10nF 1 CF 7 Salida de FM

-9 V

Figura 8.2.-Circuito de amarre de fase con LM 565

Frecuencia de funcionamiento libre 1. Si el generador de la seal de ca de la Figura 8.1 se desconecta, el 565 est en operacin de funcionamiento libre. Cul es la frecuencia del VCO si el cursor del potencimetro est en la parte superior? Registre las frecuencias calculadas en la Tabla 8.1. Para cuando el potencimetro est arriba

Para cuando el potencimetro est abajo

2. Conecte el circuito de la Figura 8.2 con un CF de 0.2 F (use dos capacitores de 0.1 F en paralelo).

4

Instituto Tecnolgico de Lzaro Crdenas

3. Desconecte de manera temporal el generador de seal de ca para obtener la operacin de funcionamiento libre.

4. Observe con un osciloscopio la salida del VCO (terminal 4). Use una sensibilidad vertical de 5 V/cm y una base de tiempo de 0.1 ms/cm. Vare el potencimetro y observe como cambia la frecuencia.

5. Mida la frecuencia mxima y mnima de funcionamiento libre. Registre las frecuencias medidas en la Tabla 8.1.

6. Ajuste el potencimetro para obtener un a frecuencia central de unos 5 kHz.

Tabla 8.1.- Mediciones del PLL en funcionamiento libre

Cursor Arriba Abajo 3.09 kHz 6.38 kHz 3.32 kHz 6.4 kHz

Intervalo de enganche 7. Reconecte el generador de seal de ca. Observe la seal en la terminal 2. Ajuste el generador para obtener 0.5 V pp a 5 kHz.

8. Observe la salida (terminal 4). Vare la frecuencia del generador de 4 a 6 khz. Observe como la salida del PLL se engancha con la seal de entrada.

9. Mida las frecuencias de enganche mxima y mnima. Registre estos valores en la Tabla 8.2.

Instituto Tecnolgico de Lzaro Crdenas

Tabla 8.2.- Mediciones del PLL en intervalo de enganche

9.54 kHz

4.032 kHz

Intervalo de captura 10. Calcule las frecuencias de corte del filtro pasa bajas para los valores de CF en la Tabla 8.3. Anote los resultados. Para

Para

Para

11. Mida y anote en la Tabla 8.3 las frecuencias de captura mxima y mnima. Calcule y registre el intervalo de captura, .

12. Repita el paso 11 para los dems valores de CF en la Tabla 8.3.

Tabla 8.3.- Mediciones del PLL en intervalo de captura

0.2 0.1 0.047

0.221 0.442 0.940

4.75 5.3 5.35

2.8 2.8 2.8

1.95 2.5 2.55

Instituto Tecnolgico de Lzaro Crdenas

Salida de FM 13. Mida el voltaje de cd (con multmetro digital si es posible) en la salida de FM (terminal 7) para una frecuencia de entrada de 4 kHz. Registre el voltaje de cd en la Tabla 8.4.

Tabla 8.4.- Mediciones del PLL, salida de FM

Frecuencia, kHz 4 5 6 9.13 8.32 9.10 9.13 8.32 9.10 9.04 8.88 9

CUESTIONARIO

1. Cul es el intervalo de captura para CF = 0.2 F? El intervalo es de 2.1 kHz.

2. Cul es el efecto del capacitor del filtro en el intervalo de captura? Mientras ms pequeo sea el capacitor mayor ser el intervalo de captura e inversamente. 3. Los datos de la Tabla 8.4 prueban que un PLL puede producir una salida de FM demodulada. Explique por qu. En los resultados se noto que la frecuencia cambiaba pero la amplitud se mantena aproximadamente igual. Si hubiera cambiado la amplitud y la frecuencia se mantiene constante sera AM.

Instituto Tecnolgico de Lzaro Crdenas

4. Qu cambio hara para obtener una frecuencia de funcionamiento libre de 50 kHz? Cambiara el valor de CT. Suponiendo que el potencimetro este en su valor mximo se ocupara el capacitor siguiente:

CONCLUSION

Se comprob el funcionamiento del circuito de amarre de fase (PLL). Fue fcil de construir el PLL mediante el uso del circuito integrado LM 565. Al estar en funcionamiento libre, el PLL presenta a la salida una seal cuadrada constante, como se muestra en la Figura 8.1.

Figura 8.1.- Frecuencia en funcionamiento libre el PLL

Instituto Tecnolgico de Lzaro Crdenas

Mientras que en el intervalo de enganche a ciertas frecuencias mnima y mxima, la seal de salida sigue a la seal de entrada, durante este intervalo la seal de salida muestra estabilidad (Figura 8.2). El nico problema que se presento en la prctica, fue al obtener el intervalo de captura, en la pantalla de osciloscopio se observaba una gran variacin de la seal de salida, era difcil obtener este resultado; al final se obtuvo el intervalo entre 2.8 kHz a 4.7 kHz aproximadamente para los tres capacitores que se utilizaron, fue tedioso porque se tenia que aumentar la frecuencia de entrada poco a poco para determinar las frecuencias mnima y mxima de captura.

Figura 8.2.- Intervalo de enganche

You might also like

- Armónicas en Sistemas Eléctricos IndustrialesFrom EverandArmónicas en Sistemas Eléctricos IndustrialesRating: 4.5 out of 5 stars4.5/5 (12)

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiFrom EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiRating: 5 out of 5 stars5/5 (1)

- Informe de Laboratorio - PLLDocument12 pagesInforme de Laboratorio - PLLJuan David Cardenas AcostaNo ratings yet

- Modulador y Demodulador FSKDocument23 pagesModulador y Demodulador FSKJose Patricio Rubio OrozcoNo ratings yet

- Demodulador y Modulador FSK Con 555 y lm565 875Document5 pagesDemodulador y Modulador FSK Con 555 y lm565 875Bani Villarreal Munguia0% (1)

- Laboratorio 4Document5 pagesLaboratorio 4enrique salazarNo ratings yet

- Guia5 6-PLL DemodulacionFSKDocument7 pagesGuia5 6-PLL DemodulacionFSKRamiro Alonso Bruz SilvaNo ratings yet

- Guía de Prácticas PLL-1Document11 pagesGuía de Prácticas PLL-1Jamil NinaNo ratings yet

- 8 Demodulador FMDocument15 pages8 Demodulador FMErick PonceNo ratings yet

- Lazo Amarrado Por FaseDocument5 pagesLazo Amarrado Por FaseJulian Prieto RiverosNo ratings yet

- PLL y VcoDocument10 pagesPLL y VcoDavid LemaNo ratings yet

- Guia 2 de Electronica de Comunicaciones 2018 - PDFDocument3 pagesGuia 2 de Electronica de Comunicaciones 2018 - PDFFernando VargasNo ratings yet

- Practica PLLDocument6 pagesPractica PLLJairo González MorenoNo ratings yet

- Laboratorio 4 Grupo 1Document9 pagesLaboratorio 4 Grupo 1Carlos Carrillo ZapataNo ratings yet

- Practica 7Document16 pagesPractica 7nevermind57No ratings yet

- Práctica 4Document5 pagesPráctica 4David Soler DelgadoNo ratings yet

- Informe PLLDocument10 pagesInforme PLLRubenCalleSanchezNo ratings yet

- Informe PLLDocument4 pagesInforme PLLAndrey LealNo ratings yet

- OsciladoresDocument11 pagesOsciladoresJordanG.NoriegaNo ratings yet

- Laboratorio FMDocument6 pagesLaboratorio FMArvei Galvis Castrillon50% (2)

- 5 Practica9 PLL 4046Document8 pages5 Practica9 PLL 4046Silva Mejia Victor Miguel100% (1)

- PLL 4046Document6 pagesPLL 4046Carlos RamosNo ratings yet

- Circuitos Integrados Lineales - Humphries PDFDocument16 pagesCircuitos Integrados Lineales - Humphries PDFADRB1804No ratings yet

- LAB1Document3 pagesLAB1Juan Felipe GomezNo ratings yet

- Semiconductores Laboratorio NDocument8 pagesSemiconductores Laboratorio NJackCastroNo ratings yet

- INCBDocument10 pagesINCBJoséNo ratings yet

- It264lab3 PLL 2013Document6 pagesIt264lab3 PLL 2013shonn10No ratings yet

- Demodulador FSK Mediante PLLDocument5 pagesDemodulador FSK Mediante PLLCarlos RubioNo ratings yet

- Manual de Laboratorio Electrónica II - (04-09-2023)Document21 pagesManual de Laboratorio Electrónica II - (04-09-2023)Gabriel FernandezNo ratings yet

- Aplicaciones PLLDocument12 pagesAplicaciones PLLEduardo RomeroNo ratings yet

- RadiocomunicacionesDocument6 pagesRadiocomunicacionesQuicaño PradoNo ratings yet

- EnsayoDocument2 pagesEnsayoNikina Calvo CNo ratings yet

- Unidad 6. Aplicación de Proyecto de ControlDocument60 pagesUnidad 6. Aplicación de Proyecto de ControlJORGESOLANOIEM100% (1)

- Guardado Con Autorrecuperación de IEEE-FSK-Navidad - AsdDocument9 pagesGuardado Con Autorrecuperación de IEEE-FSK-Navidad - AsdDaniel CavaNo ratings yet

- Practica 2 Demodulacion en AmplitudDocument6 pagesPractica 2 Demodulacion en AmplitudBryan PaucarNo ratings yet

- Guia 5 Ctos IIIDocument4 pagesGuia 5 Ctos IIIFernando Gutierrez OportoNo ratings yet

- Modulador FM Con Oscilador ClappDocument29 pagesModulador FM Con Oscilador Clappalejo_1994244644No ratings yet

- Modulador AMDocument11 pagesModulador AMDiego HernándezNo ratings yet

- CD4046Document15 pagesCD4046Victor SanchezNo ratings yet

- Aprenda Acerca Del PLL y Diseño Con EllosDocument8 pagesAprenda Acerca Del PLL y Diseño Con EllosArmando CajahuaringaNo ratings yet

- FescDocument5 pagesFescAndyGomezNo ratings yet

- Practica 8 ElectronicaDocument2 pagesPractica 8 ElectronicaJosele ZarzaNo ratings yet

- Mallas de Fase EncadenadaDocument11 pagesMallas de Fase EncadenadaCars SandovalNo ratings yet

- Lazo Cerrado de Fase (PLL)Document5 pagesLazo Cerrado de Fase (PLL)Erick Africano MejiaNo ratings yet

- Informe PLLDocument7 pagesInforme PLLDaniel Mesa100% (1)

- Practica 4Document8 pagesPractica 4Porta Perez Garcia100% (1)

- Lab 3Document8 pagesLab 3MORALES BENITES JUAN FABIANNo ratings yet

- Informe de Laboratorio (Ask)Document4 pagesInforme de Laboratorio (Ask)Giovanni QCNo ratings yet

- Informe 2 Electronica BasicaDocument7 pagesInforme 2 Electronica BasicaManuNo ratings yet

- PWM PotenciaDocument8 pagesPWM PotenciaRicardo Sanchez HernandezNo ratings yet

- Como Funciona El Circuito Integrado 555Document28 pagesComo Funciona El Circuito Integrado 555cesarNo ratings yet

- Lab#6Document6 pagesLab#6Ader Hariel Treminio MontoyaNo ratings yet

- Laboratorio 3 EC1Document29 pagesLaboratorio 3 EC1Ivar JmNo ratings yet

- Informe Final 06Document22 pagesInforme Final 06RENZO PLASENCIA CELESTINONo ratings yet

- TL 494Document8 pagesTL 494SOPHIE PCJONNo ratings yet

- Programación Del Riego Según La Relación Agua Suelo Caña de Azúcar Clima. O Castro. CENGICAÑA. Guatemala.Document8 pagesProgramación Del Riego Según La Relación Agua Suelo Caña de Azúcar Clima. O Castro. CENGICAÑA. Guatemala.Nayeli GonzalezNo ratings yet

- Párrafos y Oraciones-30 de NoviembreDocument2 pagesPárrafos y Oraciones-30 de NoviembreFlor CorreaNo ratings yet

- Curso BombasDocument15 pagesCurso BombasAlfredo MarengoNo ratings yet

- El Yo Social (Tutoria)Document33 pagesEl Yo Social (Tutoria)Liliana Carrillo Lopez100% (2)

- 1ra Clase, El Derecho en El Estado ModernoDocument16 pages1ra Clase, El Derecho en El Estado ModernodleonchiNo ratings yet

- ISO 45001 - SGSST - Nuevo EstándarDocument97 pagesISO 45001 - SGSST - Nuevo Estándardanielito_xxxNo ratings yet

- Fabrica Tu Propio MicroscopioDocument2 pagesFabrica Tu Propio MicroscopioJose Luis70% (33)

- G&G DiaclasasDocument4 pagesG&G DiaclasasDiego IriarteNo ratings yet

- 12 de Julio. RESTAMOS FRACCIONES HETEROGÉNEASDocument4 pages12 de Julio. RESTAMOS FRACCIONES HETEROGÉNEASSulay ormesinda Llatas oliveraNo ratings yet

- Universidad Cesar Vallejo: Escuela Profesional Ing - CivilDocument34 pagesUniversidad Cesar Vallejo: Escuela Profesional Ing - CivilYesi NuñezNo ratings yet

- Tarea Preparatoria Primer Parcial 2S2019 PDFDocument2 pagesTarea Preparatoria Primer Parcial 2S2019 PDFjorge cernaNo ratings yet

- d5 - Guía Práctica - Aprendizaje y Desarrollo de La PersonalidadDocument5 pagesd5 - Guía Práctica - Aprendizaje y Desarrollo de La PersonalidadNancyNo ratings yet

- Delta Del Orinoco-San JuanDocument6 pagesDelta Del Orinoco-San JuanAngelica YsaccisNo ratings yet

- Krishnamurti - El Reino de La FeliciDocument27 pagesKrishnamurti - El Reino de La FeliciLuis E DiazNo ratings yet

- GisDocument19 pagesGisAnonymous YQkftDNzrjNo ratings yet

- Mary Jo Hatch Cap 2Document47 pagesMary Jo Hatch Cap 2hatrickmario0% (1)

- Creg - 065-2012Document34 pagesCreg - 065-2012sergio castellanosNo ratings yet

- Pintura de Baba de NopalDocument2 pagesPintura de Baba de NopalLeonardo HernándezNo ratings yet

- Extracción de Códigos OBD1 Toyota y DescripcionDocument4 pagesExtracción de Códigos OBD1 Toyota y DescripcionGerardo Navarro Sánchez100% (1)

- Software de Cómputo NuméricoDocument3 pagesSoftware de Cómputo NuméricoRedes Computadores Sena TunjaNo ratings yet

- Fito Páez LetrasDocument110 pagesFito Páez LetrasMauricio BarriosNo ratings yet

- Ejercicios CDocument74 pagesEjercicios CHector TrianaNo ratings yet

- Cuenca de ChanchasDocument88 pagesCuenca de ChanchasRussell Peñaloza Yauri100% (1)

- Manual Unidad 2 - Psicología - Social - y - ComunitariaDocument50 pagesManual Unidad 2 - Psicología - Social - y - ComunitariaMARISOL NOA MENDOZANo ratings yet

- 0143 2024 Inia BasesDocument14 pages0143 2024 Inia Basesleonelak2No ratings yet

- Nivelacion Compuesta Mapa ConceptualDocument1 pageNivelacion Compuesta Mapa ConceptualRodrigo Isidro TrebejoNo ratings yet

- Informática EducativaDocument7 pagesInformática Educativasteven judgeNo ratings yet

- Fee 4856Document1 pageFee 4856liliana muñozNo ratings yet

- Resumen - Corina Yturbe (2005)Document4 pagesResumen - Corina Yturbe (2005)ReySalmon100% (2)

- Diseño en Ingeniería ACOFIDocument20 pagesDiseño en Ingeniería ACOFIRobert Castilla ToroNo ratings yet