Professional Documents

Culture Documents

Low Power Vlsi Question Paper

Uploaded by

ustadkrishnaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Low Power Vlsi Question Paper

Uploaded by

ustadkrishnaCopyright:

Available Formats

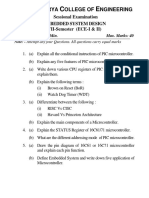

Reg. No.

M.E. DEGREE EXAMINATION, NOVEMBER/DECEMBER 2010 Elective VLSI Design

VL 9252 LOW POWER VLSI DESIGN (Common to M.E. Applied Electronics) (Regulation 2009) Time : Three hours Answer ALL questions

PART A (10 2 = 20 Marks) 1. 2. 3. 4. 5. 6. 7. 8. 9. Define subthreshold swing. What is body effect?

Define intrinsic delay.

Draw a 6 transistor SRAM cell.

Compare NOR type row decoder and NAND type row decoder in memories. What is reconfigurable computing? Implement function AX 2 + BX + C using two multipliers and two adders. Define signal activity. Write down an algorithm to compute signal probabilities.

10.

What is meant by transistor reordering?

4

Maximum : 100 Marks

Question Paper Code : 98081

PART B (5 16 = 80 Marks) 11. (a) (i) (ii) Derive an expression for short circuit power dissipation of a CMOS inverter. (10) Write a short note on drain induced barrier lowering. Or (b) (i) (ii) 12. (a) (i) (ii) Explain basic principles of low power design. (6)

Discuss the various sources of power consumption in CMOS devices. (8) Discuss the various features of technology mapping.

Explain the circuit level techniques for minimization of power dissipation. (8) Or

(b)

(i) (ii)

Explain the concept of state assignment for finite state machine to reduce power dissipation with example. (10) Factoring out a common sub-expression can achieve power saving. Justify. (6)

(ii)

Differentiate MTCMOS from DTCMOS.

1

2

13.

(a)

(i)

How can power be reduced in write driver circuits and sense amplifier circuits? Explain. (10) (6)

(b)

(i) (ii)

Explain the working of DCVS voltage level converter. Design a full adder using Adiabatic logic.

0

Or Or Or

(ii)

Discuss methods of estimating average power in combinational circuits. (8)

(b) 15. (a)

Explain in detail about Monte Carlo method for estimating glitch power. (i) (ii) Elaborate on the use of pipelining and parallelism for low power. (8) Discuss the principle of pre-computation logic for reducing power with a suitable example. (8)

(b)

Explain the various methods to minimize power based on software power optimization.

14.

(a)

(i)

How do you compute signal probability using binary decision diagrams? Discuss. (8)

0

(8) (8) (10) (6)

98081

You might also like

- Microprocessor and Microcontroller Anna University Question PapersDocument3 pagesMicroprocessor and Microcontroller Anna University Question PapersthennishaNo ratings yet

- MUltimedia Compression Techniques Question PaperDocument2 pagesMUltimedia Compression Techniques Question PaperPurush Jayaraman100% (1)

- M.E./M.Tech. Degree Examinations Question Paper on Advanced Wireless NetworksDocument2 pagesM.E./M.Tech. Degree Examinations Question Paper on Advanced Wireless Networksmethila100% (1)

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)Val GinNo ratings yet

- Cad For Vlsi Circuits 2 PDFDocument2 pagesCad For Vlsi Circuits 2 PDFrajasekarkpr100% (1)

- Question Bank-1913104-Design of Embedded SystemsDocument12 pagesQuestion Bank-1913104-Design of Embedded SystemsHasib Al-ariki100% (1)

- IoT Data Management Concept and DiagramDocument7 pagesIoT Data Management Concept and DiagramVIDYA PNo ratings yet

- IOT Question Bank - M1 - 2 - 3Document3 pagesIOT Question Bank - M1 - 2 - 3Shilpa ShridharNo ratings yet

- Ap5191 Embedded System DesignDocument3 pagesAp5191 Embedded System DesignHasib Al-ariki100% (1)

- Cs9251 Mobile Computing Question BankDocument16 pagesCs9251 Mobile Computing Question BankNivithaNo ratings yet

- Microprocessor and Microcontroller Question PaperDocument2 pagesMicroprocessor and Microcontroller Question PaperUmesh Harihara sudan0% (1)

- LPC2148 DacDocument14 pagesLPC2148 DacSmruti Pore100% (1)

- Ec2051 QBDocument3 pagesEc2051 QBBalajee Kowshik0% (1)

- EI2403 - VLSI Design 2 Marks With AnswersDocument23 pagesEI2403 - VLSI Design 2 Marks With AnswersAnand GvphNo ratings yet

- UNIT-3 Gate Level Design NotesDocument22 pagesUNIT-3 Gate Level Design NotesPallavi Ch100% (2)

- Electronic Devices Model Question PapersDocument2 pagesElectronic Devices Model Question Papersk_kunarajNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)rajkumarsac100% (1)

- Embedded Syatem Question Paper.Document1 pageEmbedded Syatem Question Paper.Saurabh SinghNo ratings yet

- EC6202 Electronic Devices and Circuits Question Paper May 2016Document16 pagesEC6202 Electronic Devices and Circuits Question Paper May 2016Senthil IlangovanNo ratings yet

- Microcontroller and Embedded Systems Question BankDocument4 pagesMicrocontroller and Embedded Systems Question BankGanaraj KaruvajeNo ratings yet

- Microprocessor and Interfacing Questions for UCET ExamDocument4 pagesMicroprocessor and Interfacing Questions for UCET ExamDarshan SharmaNo ratings yet

- CS3691 Embedded Systems and IotDocument2 pagesCS3691 Embedded Systems and IotSelva PriyaNo ratings yet

- Question Bank - Lowpower VLSI Circuits - JNTUADocument3 pagesQuestion Bank - Lowpower VLSI Circuits - JNTUArajasekarkpr100% (5)

- Low Power VLSI Circuits QuestionsDocument31 pagesLow Power VLSI Circuits QuestionsPallavi Ch71% (7)

- IOT Question PaperDocument2 pagesIOT Question PaperAatithya VoraNo ratings yet

- EC8791 Embedded and Real Time SystemsDocument78 pagesEC8791 Embedded and Real Time SystemsSivagami ManiNo ratings yet

- Xilinx XC4000Document24 pagesXilinx XC4000jeevitha100% (3)

- RTL Simulation and Synthesis With PLDs QP Mid-1Document1 pageRTL Simulation and Synthesis With PLDs QP Mid-1baburao_kodavati0% (1)

- CU5291-Advanced Wireless Communications SystemDocument11 pagesCU5291-Advanced Wireless Communications SystemS.J Angelin PraveenaNo ratings yet

- Optical Networks QUESTION BANKDocument11 pagesOptical Networks QUESTION BANKS.J Angelin Praveena0% (1)

- WSN Question Bank For Mid 1Document6 pagesWSN Question Bank For Mid 1praneetha ChowdaryNo ratings yet

- Iot Question BankDocument2 pagesIot Question BankAjay100% (3)

- IoT Question Bank Covers Key ConceptsDocument2 pagesIoT Question Bank Covers Key ConceptspriyaNo ratings yet

- RFIC Imp QuestionsDocument4 pagesRFIC Imp QuestionsSai SreejaNo ratings yet

- Ap92s12 Advanced Digital System DesignDocument2 pagesAp92s12 Advanced Digital System Designsridhar_omalur67% (3)

- PIC QuestionsDocument4 pagesPIC Questionsgopikrishnarao100% (1)

- Question Bank Advanced ProcessorsDocument2 pagesQuestion Bank Advanced ProcessorsManish Narkhede67% (3)

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)Ponraj Park100% (4)

- Twin Tub ProcessDocument11 pagesTwin Tub Processvmspraneeth33% (3)

- Embedded Systems University Questions Marks 16Document2 pagesEmbedded Systems University Questions Marks 16g3v5No ratings yet

- Vlsi Design Question Bank EEC 703Document10 pagesVlsi Design Question Bank EEC 703selvi0412No ratings yet

- Study Microwind Tool and Lambda RulesDocument54 pagesStudy Microwind Tool and Lambda RulesyayavaramNo ratings yet

- 15ecl48-VTU-raghudathesh-BJT MIXER PDFDocument2 pages15ecl48-VTU-raghudathesh-BJT MIXER PDFraghudatheshgp100% (1)

- RMK Group A4 PPT - MPMC - Ec8691 - Unit 1Document127 pagesRMK Group A4 PPT - MPMC - Ec8691 - Unit 1Gowtham Reddy Rekkala100% (1)

- Introduction to DSP Processors ArchitectureDocument45 pagesIntroduction to DSP Processors ArchitectureLavanya KattaNo ratings yet

- ML Important questions on machine learning algorithms and applicationsDocument2 pagesML Important questions on machine learning algorithms and applicationsprashanth kumarNo ratings yet

- CU7202-MIC and RF System DesignDocument16 pagesCU7202-MIC and RF System DesignSaadNo ratings yet

- VLSI Testing Techniques and ApplicationsDocument93 pagesVLSI Testing Techniques and ApplicationsDr Ravi Kumar A.V100% (1)

- UNIT-V Realization of State MachinesDocument29 pagesUNIT-V Realization of State MachinesNarasimha Murthy Yayavaram100% (20)

- Cp5191 MLT Unit IIDocument27 pagesCp5191 MLT Unit IIbala_07123No ratings yet

- EE6602 2 Marks With Answer KeyDocument20 pagesEE6602 2 Marks With Answer KeyLogesh50% (2)

- Features of The LPC214X FamilyDocument13 pagesFeatures of The LPC214X FamilyramyaNo ratings yet

- MPMC Model Questions R-20Document3 pagesMPMC Model Questions R-20Jaswanth KadaNo ratings yet

- Question Paper Code:: ElectiveDocument2 pagesQuestion Paper Code:: ElectiveShanmugapriya AnandanNo ratings yet

- Low Power VLSI Design TechniquesDocument2 pagesLow Power VLSI Design TechniquesShanmugapriya AnandanNo ratings yet

- EVL562 ECL523 Digital IC Design Dec2020Document3 pagesEVL562 ECL523 Digital IC Design Dec2020akash rawatNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- M.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Document9 pagesM.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Manu SeaNo ratings yet

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANo ratings yet

- Question BankDocument9 pagesQuestion BankNiyas AhamedNo ratings yet

- Embedded System - J7607Document2 pagesEmbedded System - J7607ustadkrishnaNo ratings yet

- Embedded SystemsDocument3 pagesEmbedded SystemsJeeva PriyaNo ratings yet

- Embedded SystemsDocument3 pagesEmbedded SystemsJeeva PriyaNo ratings yet

- Cad Question Paper PDFDocument3 pagesCad Question Paper PDFrajasekarkprNo ratings yet

- Cad Question Paper-116982331Document2 pagesCad Question Paper-116982331ustadkrishnaNo ratings yet

- ECEN 454: Digital Integrated Circuit DesignDocument36 pagesECEN 454: Digital Integrated Circuit DesignJoe KingNo ratings yet

- Service Manual: Split Type Room Air Conditioner Ae-X9Ghr AE-X12GHR Ay-Xp9Ghr Ay-Xp12GhrDocument11 pagesService Manual: Split Type Room Air Conditioner Ae-X9Ghr AE-X12GHR Ay-Xp9Ghr Ay-Xp12GhrMuhamad PriyatnaNo ratings yet

- HD465-7 PresentationDocument28 pagesHD465-7 PresentationYopi100% (1)

- Twin Vs SingleDocument7 pagesTwin Vs SingleDoug GouldNo ratings yet

- REF - NO.PSE/P 2603-2 List: HBL Power Systems LTDDocument22 pagesREF - NO.PSE/P 2603-2 List: HBL Power Systems LTDmukesh_kht1No ratings yet

- 10.1 Climate Control System OverviewDocument9 pages10.1 Climate Control System OverviewIgorIlnickijNo ratings yet

- Oi Series Diagnostics For All AlarmsDocument2 pagesOi Series Diagnostics For All Alarmsrattan singhNo ratings yet

- Parts Catalogue: CD DeluxeDocument52 pagesParts Catalogue: CD DeluxeJonathan FiquitivaNo ratings yet

- Thumm 4.506.13 e 506H 4 G1 2Document1 pageThumm 4.506.13 e 506H 4 G1 2luc sherdNo ratings yet

- Sony Sat A55p Sat b55pDocument124 pagesSony Sat A55p Sat b55pAbdulraouf DefnanyNo ratings yet

- Document - Onl Motor Mercedes Benz Om501 Om502 em InglesDocument123 pagesDocument - Onl Motor Mercedes Benz Om501 Om502 em InglesEdison HaroNo ratings yet

- 4.5 Cargo DischargingDocument2 pages4.5 Cargo DischargingHasan Cosalev100% (1)

- Table of Gauges: Inch MM Inch MM Inch MM Inch MM Inch MM Inch MM No. S.W.G B.W.G B.G B.S U.S.G M.S.GDocument1 pageTable of Gauges: Inch MM Inch MM Inch MM Inch MM Inch MM Inch MM No. S.W.G B.W.G B.G B.S U.S.G M.S.GSamiul IslamNo ratings yet

- Color Imagerunner C1030/C1022 Series: Service ManualDocument534 pagesColor Imagerunner C1030/C1022 Series: Service ManualCornel SusanuNo ratings yet

- Simosec Ha41 21 2003 enDocument44 pagesSimosec Ha41 21 2003 enJosue Espinoza YachachinNo ratings yet

- 19191.6101.01.000 LF MCC Single Line DiagramDocument5 pages19191.6101.01.000 LF MCC Single Line DiagramSOUMENNo ratings yet

- 06 - 0010 LED Anti-Collision Lighting System A320Document12 pages06 - 0010 LED Anti-Collision Lighting System A320premica100% (1)

- PM5X4Document2 pagesPM5X4Sergio Sosa NavaNo ratings yet

- Nema Hybrid Stepper SolutionsDocument62 pagesNema Hybrid Stepper SolutionsTamas RaduNo ratings yet

- Specifications: Horn LocationDocument14 pagesSpecifications: Horn LocationCarlos VelázquezNo ratings yet

- BFR 226 EN 3 Black Flow Regulator G 3 - 4Document2 pagesBFR 226 EN 3 Black Flow Regulator G 3 - 4Shinya Takeda(武田 慎也)No ratings yet

- Ina - Permaglide - InformationsDocument3 pagesIna - Permaglide - Informationsnunesalessandro1975No ratings yet

- Nfpa 12 2018 12Document1 pageNfpa 12 2018 12Sundar RzNo ratings yet

- High Current Megamos Fet: Ixtk 120N25 V 250 V I 120 A 20 MDocument6 pagesHigh Current Megamos Fet: Ixtk 120N25 V 250 V I 120 A 20 MMohamed belhasanNo ratings yet

- Power Transformer Reactor ComponentsDocument17 pagesPower Transformer Reactor ComponentsLokesh KapoorNo ratings yet

- Ac Machines Lab ManualDocument102 pagesAc Machines Lab ManualAshwin Gopinath100% (3)

- Operation and Maintenance of A 220 132KV SubstationDocument59 pagesOperation and Maintenance of A 220 132KV Substationanup kumarNo ratings yet

- Calculating Conductor Impedance for a 3-Phase Pole ConfigurationDocument12 pagesCalculating Conductor Impedance for a 3-Phase Pole ConfigurationJonatan Lopez RodriguezNo ratings yet

- Especificaciones TRAMAC 125Document44 pagesEspecificaciones TRAMAC 125Alberto de la cruzNo ratings yet

- Columbia Maintenance Manual Models: CL112 CL120Document137 pagesColumbia Maintenance Manual Models: CL112 CL120atsa03No ratings yet