Professional Documents

Culture Documents

An 133 F

Uploaded by

marquitos550bOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

An 133 F

Uploaded by

marquitos550bCopyright:

Available Formats

Application Note 133 October 2011 A Closed-Loop, Wideband, 100A Active Load

Brute Force Marries Controlled Speed Jim Williams Introduction Digital systems, particularly microprocessors, furnish transient loads in the 100A range that a voltage regulator must service. Ideally, regulator output is invariant during a load transient. In practice, some variation is encountered and becomes problematic if allowable operating voltage tolerances are exceeded. 100A load steps, characteristic of microprocessors, exacerbate this issue, necessitating testing the regulator and associated components under such transient loading conditions. To meet this need, a closed-loop, 500kHz bandwidth, linearly responding, 100A capacity active load is described below. Study of this approach is prefixed by a brief review of conventional test load types and noting their shortcomings1. Basic Load Transient Generator Figure 1 diagrams a conceptual load transient generator. The regulator under test drives DC and switched resistive loads, which may be variable. The switched current and output voltage are monitored, permitting comparison of the nominally stable output voltage versus load current under static and dynamic conditions. The switched current is either on or off; there is no controllable linear region. Figure 2 develops the concept by including electronic load switch control. Operation is straightforward. The input

INPUT PULSE GATE DRIVE STAGE 0.001

AN133 F02

pulse switches the FET via a drive stage, generating a transient load current out of the regulator and its output capacitors. The size, composition and location of these capacitors has a pronounced effect on transient response and must be quite carefully considered. Although the electronic control facilitates high speed switching, the architecture cannot emulate loads between the minimum

Note 1: See Reference 1, from which the immediately following material partially derives, for details and descriptions of very wideband load transient generators, albeit at much lower currents.

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

REGULATOR UNDER TEST, INCLUDING OUTPUT CAPACITORS

DC LOAD

RSWITCHED LOAD

REGULATOR VOLTAGE MONITOR

ISWITCHED MONITOR

Figure 2. Conceptual FET Based Load Tester Permits Input Pulse Controlled Step Loading. As Before, Switched Current Is Either On or Off; There Is No Controllable Linear Region

+EREGULATOR REGULATOR INPUT SUPPLY REGULATOR UNDER TEST CURRENT MONITOR DC LOAD RSWITCHED LOAD LOAD SWITCH ISWITCHED = EREGULATOR RSWITCHED LOAD

AN133 F01

VOLTAGE MONITOR

Figure 1. Conceptual Regulator Load Tester Includes Switched and DC Loads and Voltage/Current Monitors. Resistor Values Set DC and Switched Load Currents. Switched Current Is Either On or Off; There Is No Controllable Linear Region

an133f

AN133-1

Application Note 133

and maximum currents. Additionally, FET switching speed is uncontrolled, introducing wideband harmonic into the measurement, potentially corrupting the oscilloscope display. Closed-Loop Load Transient Generator Placing Q1 within a feedback loop allows true, linear control of the load tester. Figure 3s conceptual closed-loop load transient generator linearly controls Q1s gate voltage to set instantaneous transient current at any desired point,

100A REGULATOR UNDER TEST, INCLUDING OUTPUT CAPACITORS

+

INPUT PULSE (NEGATIVE) A1 Q1

REGULATOR OUTPUT VOLTAGE MONITOR

allowing simulation of nearly any load profile. Feedback from Q1s source to the A1 control amplifier closes a loop around Q1, stabilizing its operating point. Q1s current assumes a value dependent on the instantaneous input control voltage and the current sense resistor over a very wide bandwidth. Note that once A1 is biased to Q1s conduction threshold (by the DC Load Set), small variations in A1s output result in large Q1 channel current changes. As such, large output excursions are not required from A1; its small signal bandwidth is the fundamental speed limitation. Within this restriction, Q1s current waveform is identically shaped to A1s input control voltage, allowing linear control of load current. This versatile capability permits a wide variety of simulated loads. Figure 4 further develops Figure 3, adding new elements. A gate drive stage isolates the control amplifier from Q1s gate capacitance, maintaining amplifier phase margin and providing low delay, linear current gain. An X10 differential amplifier provides high resolution sensing across the 1m current shunt. The dissipation limiter, acting on the averaged input value and Q1 temperature, shuts down gate drive to preclude excessive FET heating and subsequent destruction. Amplifier associated capacitors tailor bandwidth and optimize loop response.

0.001

AN133 F03

V BASELINE/DC LOAD SET ISWITCHED AND DC LOAD MONITOR

Figure 3. Feedback Controlled Load Step Tester Allows Continuous FET Conductivity Control. Input Accommodates Separate DC and Pulsed Loading Instructions

INPUT AVG

DISSIPATION LIMITER

FET TEMP

REGULATOR UNDER TEST, INCLUDING OUTPUT CAPACITORS

TEMP SENSE INPUT PULSE (NEGATIVE)

+

A1

SHUTDOWN GATE DRIVE STAGE Q1

+

X10 0.001

V BASELINE/DC LOAD SET

AN133 F04

Figure 4. Developed Form of Figure 3. Differential Amplifier Provides High Resolution Sensing Across Milliohm Shunt. Dissipation Limiter, Acting on Average Input Value and FET Temperature, Shuts Down Gate Drive, Precluding Excessive FET Heating. Amplifier Associated Capacitors Tailor Bandwidth, Optimize Loop Response

an133f

AN133-2

Application Note 133

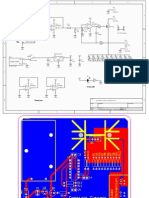

Detailed Circuitry Discussion Figure 5s detailed schematic of the 100A capacity load tester follows Figure 4s outline. A1, responding to DC and pulse inputs and current indicating feedback from A3, sets Q1s conductivity via the actively biased Q4-Q5 gate drive stage. A2 determines stage bias under all conditions by comparing Q5s averaged collector voltage to a reference and controlling Q3s conduction, closing a loop. C1, instructed by the average input value, shuts down FET gate drive via Q2 under harmful conditions2. SW1, sensing heat sink temperature, contributes thermally activated Q1 shutdown. Q6 and the Zener prevent Q1 turn-on if the

15V DISSIPATION LIMITER 15V POWER LIMIT 100k 0.01 2.2k GATE DRIVE 15V

15V supply is not present by diverting Q4 bias. A1s 1k resistor precludes A1 damage due to 15V supply loss. Trims optimize dynamic response, determine loop DC baseline idle current, set dissipation limit and control gate drive stage bias. The DC trims are self-explanatory. The loop compensation and FET response AC trims at A1 are more subtle. They are adjusted for the best compromise between loop stability, edge rate and pulse purity. A1s loop compensation trim sets roll-off for maximum

Note 2: The protection scheme is patterned after techniques utilized in high power pulse generators. See Reference 2 and 3.

+

C1 LT1011

10F

200 Q2 TP-0610L 7pF TO 45pF LOOP COMPENSATION

1k

13k Q6 2N3904 Q4 2N3904 3

0.1

DISSIPATION 2k LIMIT ADJUST 100k 470k 5 5V

0V

INPUT 1V 1.5k* 51 300pF 50k 20pF 1.5k* 3.01k*

0V TO 1V = 0A TO 100A

FET RESPONSE COMPENSATION

Figure 5. Detailed Circuitry Follows Figure 4s Concept. A1, Responding to DC and Pulsed Inputs, Sets Q1 Conductivity via Actively Biased Gate Drive Stage. A3, Sensing Q1 Current, Closes A1s Feedback Loop. C1, Instructed by Average Input Value, Shuts Down Q1 Gate Drive Under Harmful Conditions. Q6 Guards Against Lost 15V Supply. SW1 Adds Thermal Limiting. Trims Optimize Dynamic Response, Determine Loop Baseline Idle Current, Set Dissipation Limit and Control Gate Drive Stage Bias

an133f

33k

5 BASELINE 1M CURRENT

TO LOAD POINT OF SUPPLY UNDER TEST Q1 HEAT SINK GAIN 100 HIGH CURRENT CRITICAL PATH MINIMIZE INDUCTANCE

1N754 6.8V

SW1 OPENS 70C

10k 20pF

100k

A1

FET CURRENT SINK 432* 3

+ LT1220

1k CONTROL AMPLIFIER Q3 VN2222L IQ 10mA

4.5k*

+

A3 LT1193 F 0.001

Q5 2N3906 5V 1k 15V 1

5V X10 CURRENT SENSE CURRENT MONITOR 1V = 100A 5V REGULATORS, + = LT1121, = LT1175 SW1 MOUNTED ON Q1 HEAT SINK SW1 = CANTHERM F20A07005ACFA06E * = 1% FILM RESISTOR Q1 = INFINEON IPB015N04LG = 1N4148

AN133 F05

SUPPLY UNDER TEST RETURN POINT

10k 0.02 LT1004 2.5V IQ ADJUST 1k 150k 10k FEEDBACK

+

A2 LT1006

15V 10k GATE DRIVE BIAS CONTROL 1F

A1, A2, C1 = 15V POWERED BYPASSING NOT SHOWN 0.001 = TEPRO-TPSM3

AN133-3

Application Note 133

bandwidth while accommodating phase shift introduced by Q1s gate capacitance and, to a lesser extent, by A3. The FET response adjustment partially compensates Q1s inherent nonlinear gain characteristic, improving front and rear pulse corner fidelity3. Circuit Testing The circuit is initially tested using a fixture equipped with massive, low loss, wideband bypassing shown in Figure6. Additionally, the importance of exceptionally low inductance layout in the high current path cannot be overstated. Every attempt must be made to minimize inductance in the 100A path; such current density at high speed demands low inductance if waveform purity is desirable. Figure 7 shows results with the circuit properly trimmed and a minimized inductance high current path. The 100A amplitude, high speed waveform is exceptionally pure with just discernible top-front and bottom-rear corner infidelities4. AC trim effects on waveform presentation are studied by deliberate mis-adjustment. Figure 8s overdamped response is typical of excess A1 feedback capacitance. The current pulse is well controlled but edge rate is slow. Figure 9s inadequate A1 feedback capacitance decreases transition time but

Note 3: The trimming procedure is not described here in order to maintain text flow and focus. For detailed trimming information see Appendix B, Trimming Procedure. Note 4: See Appendices A, Verifying Current Measurement and C, Instrumentation Considerations for guidance on obtaining Figure 7s performance level.

DC POWER SUPPLY

10,000F COMBINATION OF OS-CON, FILM AND CERAMIC CAPACITORS

MINIMIZE INDUCTANCE

Q1 FIGURE 5s CIRCUIT

MINIMIZE INDUCTANCE

AN133 F06

Figure 6. Fixturing Tests Figure 5s Dynamic Response. Massive, Broadband Bypassing Combined with Low Inductance Layout Provides Low Loss, High Current Power to Q1

20A/DIV

HORIZ = 2s/DIV

AN133 F07

Figure 7. Optimized Dynamic Response Trims Yield Exceptionally Pure, 100A Q1 Current Pulse. Residual Top-Front and Bottom-Rear Corner Infidelities Are Just Discernable

an133f

AN133-4

Application Note 133

20A/DIV 20A/DIV

HORIZ = 2s/DIV HORIZ = 2s/DIV

AN133 F08

AN133 F10

Figure 8. Overdamped Response Characteristic of Excessive A1 Feedback Capacitor Value

Figure 10. Corner Peaking Due to Overstated FET Response Compensation

20A/DIV

20A/DIV

HORIZ = 2s/DIV

AN133 F09

HORIZ = 500ns/DIV

AN133 F11

Figure 9. Inadequate A1 Feedback Capacitor Decreases Transition Time But Promotes Instability. Further Capacitor Reduction Causes Oscillation

Figure 11. Optimized Dynamic Trims Allow 650 Nanosecond Rise Time, Corresponding to 540kHz Bandwidth

promotes instability. Further capacitance reduction will cause loop oscillation because loop phase shift becomes a significant feedback lag5. Figure 10s corner peaking is due to overstated FET response compensation. If the AC trims are restored to nominal values, Figure 11s leading edge indicates 650 nanosecond rise time, equivalent to 540kHz bandwidth. The trailing edge (Figure 12), taken under the same conditions as the previous figure, is somewhat faster at 500 nanosecond fall time.

Note 5: Sorry, no photo available. Uncontrolled 100 Ampere amplitude loop oscillation is too thrilling for documenting.

20A/DIV

HORIZ = 500ns/DIV

AN133 F12

Figure 12. Same Conditions as Figure 11 Show 500 Nanosecond Fall Time

an133f

AN133-5

Application Note 133

Layout Effects None of the previous responses, even the mis-compensated examples, can be remotely approached if parasitic inductance is present in the high current path. Figure 13 deliberately places only 20nH parasitic inductance in Q1s drain path. Figure 14a displays enormous waveshape degradation deriving from the inductance and the loops subsequent response. A monstrous error dominates the leading edge before recovery occurs at the pulse middle-top. Additional aberration is evident in the falling edge turn-off. It is especially noteworthy that the photos horizontal scale is 5 slower than Figure 7s optimized response, repeated here for emphasis as Figure 14b. The lesson is clear. High speed 100A excursions do not tolerate inductance.

DC POWER SUPPLY

MINIMIZE INDUCTANCE 10,000F COMBINATION OF OS-CON, FILM AND CERAMIC CAPACITORS DELIBERATLY INTRODUCED 20nH PARASITIC INDUCTANCE Q1 FIGURE 5s CIRCUIT

MINIMIZE INDUCTANCE

AN133 F13

Figure 13. Deliberately Introduced Parasitic 20nH Inductance Tests Figure 5s Layout Sensitivity

20A/DIV

20A/DIV

HORIZ = 10s/DIV

HORIZ = 2s/DIV

AN133 F14

(14a)

(14b)

Figure 14. 1.5" of 0.075" (20nH) Flat Copper Braided Wire Completely Distorts (Figure 14a) Text Figure 7s (Shown Here as Figure 14b) Response. Note 5 Horizontal Scale Change

an133f

AN133-6

Application Note 133

Regulator Testing Regulator testing is possible after the above compensation and layout issues have been addressed. Figure 15 describes a test arrangement for an LTC3829 based, 6-phase, 120A buck regulator6. Trace A, Figure 16 shows the 100A load pulse. Trace Bs regulator response is well controlled on both edges.

INPUT 7V TO 14V

The active loads true linear response and high bandwidth permit wide ranging load waveform characteristics. While the step load pulse shown above is the commonly desired

Note 6: This regulator is conveniently incarnated as LTC demonstration board 1675A.

LTC3829 BASED 6-PHASE, 1.5V, 120A POWER SUPPLY

MINIMIZE INDUCTANCE

FIGURE 5s CIRCUIT

AN133 F15

Figure 15. Test Arrangement for LTC3829 Based 6-Phase, 120A Buck Regulator Emphasizes Low Impedance Connections to Figure 5s Circuit

A = 100A/DIV

B = 0.1V/DIV AC-COUPLED

HORIZ = 10s/DIV

AN133 F16

Figure 16. Figure 5s Circuit Subjects Figure 15s Regulator to 100A Pulsed Load (Trace A). Response (Trace B) Is Well Controlled on Both Edges

an133f

AN133-7

Application Note 133

test, essentially any load profile is easily generated. Figure 17s burst of 100A, 100kHz sinewaves is an example. Response is crisp, with no untoward dynamics despite the high speed and current involved. In Figure18, an 80 microsecond burst of 100A peak-peak noise forms the load. Figure 19 summarizes active load characteristics.

50A/DIV

HORIZ = 10s/DIV

AN133 F17

Figure 17. Figure 5 Supplies 100kHz, 100A Sinewave Load Transient Profile. Circuits Wide Bandwidth and Linear Operation Permit Wide Ranging Load Waveform Characteristics

50A/DIV

HORIZ = 20s/DIV

AN133 F18

Figure 18. Active Load Circuit Sinks 100A Peak-Peak in Response to Gated Random Noise Input

Active Load Characteristics

CURRENT ACCURACY (REFERRED TO INPUT) TEMPERATURE DRIFT CURRENT REGULATION vs SUPPLY BANDWIDTH 1% FS 100ppm/C OF READING + 20mA/C >60dB PSRR 540kHz AT 100A (tRISE = 650ns) 435kHz AT 10A (tRISE = 800ns) COMPLIANCE VOLTAGES FOR FULL OUTPUT CURRENT 0.95V MIN (SEE PLOT) MAX SET BY 70C Q1 THERMAL DISSIPATION LIMITER AMPERES 4% LEADING EDGE OVERSHOOT

100 90 80 70 60 50 40 30 20 10 0 0

NO OVERSHOOT

0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 1.1 1.2 MINIMUM Q1 DRAIN VOLTS

AN133 F19

Minimum Compliance Voltage vs Load Current

Figure 19. Active Load Tabular Characteristics. Current Accuracy/Regulation Errors Are Small, Bandwidth Mildly Retards at Low Current. Compliance Voltage Is Below 1V at 100A with 4% Leading Edge Overshoot, 1.1V with No Overshoot

an133f

AN133-8

Application Note 133

REFERENCES 1. Williams, Jim, Load Transient Response Testing For Voltage Regulators, Linear Technology Corporation, Application Note 104, October 2006. 2. Hewlett-Packard Company, HP-214A Pulse Generator Operating and Service Manual, Overload Adjust, Figure 5-13. See also, Overload Relay Adjust, pg. 5-9. Hewlett-Packard Company, 1964. 3. Hewlett-Packard Company, HP-214B Pulse Generator Operating and Service Manual, Overload Detection/ Overload Switch , pg. 8-29. Hewlett-Packard Company, March, 1980. APPENDIX A Verifying Current Measurement Theoretically, Figure 5s Q1 source and drain current are equal. Practically, questions center on potential effects of residual inductances and the huge (28000pF!) gate capacitance of the 1.5m FET specified. If these or other terms impact drain-source current equivalence at speed A3s indicated instantaneous current could be erroneous. Verification is necessary and Figure A1 diagrams a method. An added top-side 1m shunt and its attendant X10 differential amplifier duplicate the circuits resident bottomside current sensing section. Figure A2s results happily eliminate concern over dynamic Q1 current differences. The two 100A pulse outputs are identical in amplitude and shape, promoting confidence in circuit operation.

TO FIGURE 6s CAPACITOR BANK AND DC SUPPLY

+

0.001 F LT1193

Q1 TO FIGURE 5s CIRCUIT 4.5k* 432* 0.001 100 GAIN

+

LT1193 F

BOTTOM-SIDE CURRENT 4.5k* * = 1% FILM RESISTOR 432* 100 GAIN

TOP-SIDE CURRENT

AN133 FA01

Figure A1. Arrangement For Observing Q1s Top and Bottom Dynamic Currents

A = 50A/DIV

B = 50A/DIV

HORIZ = 2s/DIV

AN133 FA02

Figure A2. Q1 Top (Trace A) and Bottom (Trace B) Currents Show Identical Characteristics Despite High Speed Operation

an133f

AN133-9

Application Note 133

APPENDIX B Trimming Procedure Trimming Figure 5s circuit is a 7-step procedure which should be performed in the numerical order listed below. Out-of-sequence adjustments are permissible assuming the dissipation limiter circuitry is working and adjusted. 1. Set all adjustments to mid-range except A1s feedback capacitor, which should be at full capacity. 2. Apply no input, bias Q1s drain from a 1V DC supply, turn on power and trim Base Line Current for 0.5A through Q1. Monitor this current with an ammeter in Q1s drain line. 3. Turn power off. Lift Q2s source lead and let it float. This disables the dissipation limit circuitry, leaving Q1 vulnerable to damage from inappropriate inputs. Follow the remainder of this step in strict accordance with the instructions given. Turn power on, bias Q1s drain from a 1V supply and apply a 0.1000V DC input while monitoring Q1s drain current with an ammeter. Trim the Gain adjustment for a 10.50A meter reading1. Make this adjustment fairly quickly as Q1 is dissipating 10 Watts. Turn power off and reconnect Q2s source lead2. 4. Turn power on with no input applied and Q1s drain unbiased. Trim the IQ adjustment for +10mV at A2s positive input measured with respect to the 15V rail. Turn off power. 5. Bias and bypass Q1s drain in accordance with text Figure 6. Set the drain DC power supply for 1.5V output and turn on power. Apply a 1kHz, 1V amplitude, 5s wide pulse. Slowly increase pulse width until C1 trips, shutting down circuit output and illuminating the Power Limit LED. Tripping should occur at about 12s to15s pulse width. If it does not, adjust the Dissipation Limit potentiometer to bring the trip point within these limits. This sets allowable full-amplitude (100A) duty cycle at about 1.5% . 6. Under the same operating conditions as Step 5, set input pulse width at 10s and adjust A1s capacitive trim for the fastest positive going edge obtainable at A3s output without introducing pulse distortion. Pulse clarity should approach text Figure 7 with somewhat degraded top-front and bottom-rear corner rounding. 7. Adjust FET Response Compensation to correct the corner rounding noted in Step 6. Some interaction may occur with Step 6s adjustment. Repeat Step 6 and 7 until A3s output waveform looks like text Figure 7.

Note 1: The tight trim targets are mandated by trimming gain at only 10% of scale. This is certainly undesirable but less painful than trimming at 100% of scale which would force astronomical (and brief) dissipation in Q1 and the milliohm shunt. Note 2: It is worth mention that the primary uncertainty necessitating gain trimming is the sense lines mechanical placement at the milliohm shunt.

an133f

AN133-10

Application Note 133

APPENDIX C Instrumentation Considerations The pulse edge rates discussed in the text are not particularly fast, but high fidelity response requires some diligence. In particular, the input pulse must be cleanly defined and devoid of parasitics which would unfairly make circuit output pulse shape look bad. The pulse generators preshoot, rise time and pulse-transition aberrations are well out of band and filtered by A1s 2.1MHz (tRISE = 167ns) input RC network. These terms are not a concern; almost all general purpose pulse generators should perform well. A potential offender is excessive tailing after transitions. Meaningful dynamic testing requires a rectangular pulse shape, flat on top and bottom within 1% to 2%. The circuits input band shaping filter removes the aforementioned high speed transition related errors but will not eliminate lengthy tailing in the pulse flats. The pulse generator should be checked for this with a well compensated probe at the circuit input. The oscilloscope should register the desired flat top/bottom waveform characteristics. In making this measurement, if high speed transition related events are bothersome, the probe can be moved to the band limiting 300pF capacitor. This is defensible practice because the waveform at this point determines A1s input signal bandwidth. Some pulse generator output stages produce low level DC offset when their output is nominally at its zero volt state. The active load circuit will process such DC potentials as legitimate signal, resulting in DC load baseline current shift. The active loads input scale factor of 1V = 100A means that a 10mV zero state error produces 1A of DC baseline current shift. A simple way to check a pulse generator for this error is to place it in external trigger mode and read its output with a DVM. If offset is present it can be accounted for, nullified with the circuits baseline current trim or another pulse generator can be selected. Parasitic effects due to probe grounding and instrument interconnection should be kept in mind. At pulsed 100A levels parasitic current is easily induced into grounds and interconnections, distorting displayed waveforms. Probes should be coaxially grounded, particularly at A3s output current monitor and preferably anywhere else. Additionally, it is convenient and common practice to externally trigger the oscilloscope from the pulse generators trigger output. There is nothing wrong with this, in fact it is recommended to insure a stable trigger as probes are moved between points. This practice does, however, potentially introduce ground loops due to multiple paths between the pulse generator, the circuit and the oscilloscope. This can falsely cause apparent distortion in displayed waveforms. This effect is avoidable by using a trigger isolator at the oscilloscope external trigger input. This simple coaxial component typically consists of isolated ground and signal paths, often coupled to a pulse transformer to provide a galvanically isolated trigger event. Commercial examples include the Deerfield Labs 185 and the Hewlett-Packard 11356A. Alternately, a trigger isolator is easily constructed in a small BNC equipped enclosure as shown in Figure C1.

COAXIAL METAL ENCLOSURE 300pF OUTPUT TO OSCILLOSCOPE EXTERNAL TRIGGER INPUT

1k INPUT FROM PULSE GENERATOR TRIGGER OUTPUT INSULATED SHELL BNC 50

T1

t

1k

AN133 FC01

T1 = ALMOST ANY SMALL PULSE TRANSFORMER 1k AND 300pF VALUES ARE TYPICAL

Figure C1. Trigger Isolator Floats Input BNC Ground Using Insulated Shell BNC Connector. Capacitively Coupled Pulse Transformer Avoids Loading Input, Maintains Isolation, Delivers Trigger to Output. T1 Secondary Resistor Terminates Ringing

an133f

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

AN133-11

Application Note 133

an133f

AN133-12

Linear Technology Corporation

(408) 432-1900 FAX: (408) 434-0507

LT 1011 PRINTED IN USA

1630 McCarthy Blvd., Milpitas, CA 95035-7417

www.linear.com

LINEAR TECHNOLOGY CORPORATION 2011

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Memoria de Samsung K9GAG08U0EDocument55 pagesMemoria de Samsung K9GAG08U0ERodrigo CiezaNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Illustrated Assembly Manual k8015 Rev2Document16 pagesIllustrated Assembly Manual k8015 Rev2marquitos550bNo ratings yet

- UbifsDocument47 pagesUbifsSanel KoncarNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Ups Lyonn RackeableDocument2 pagesUps Lyonn RackeableMijael MontañoNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Samsung Un32 40d5500rfDocument80 pagesSamsung Un32 40d5500rfmarquitos550bNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- AKZ 431 Service ManualDocument5 pagesAKZ 431 Service Manualmarquitos550bNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- 20097841222Document2 pages20097841222marquitos550bNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Sony HBD Tz130Document28 pagesSony HBD Tz130marquitos550bNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- SN75176 RS-485 CommunicationDocument7 pagesSN75176 RS-485 Communicationmarquitos550bNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Aotf11s60 PDFDocument6 pagesAotf11s60 PDFmarquitos550bNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- 13 NM 60 NDocument21 pages13 NM 60 Nmarquitos550bNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- AN2492 Application Note: Wide Range 400W L6599-Based HB LLC Resonant Converter For PDP ApplicationDocument35 pagesAN2492 Application Note: Wide Range 400W L6599-Based HB LLC Resonant Converter For PDP Applicationmarquitos550bNo ratings yet

- Currentload Rev2Document2 pagesCurrentload Rev2nvkjayanthNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- 60W 18 1Document20 pages60W 18 1marquitos550bNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Carga Inductiva Con TriacDocument11 pagesCarga Inductiva Con Triacanon_274509247No ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Planos Tableta Cpu Rk2928 Puerto Usb Pequeno Board Tr738 SCH v10 Moveontechnology ComDocument6 pagesPlanos Tableta Cpu Rk2928 Puerto Usb Pequeno Board Tr738 SCH v10 Moveontechnology Comoryad100% (1)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- 30V Dual N-Channel MOSFET With Schottky Diode: General Description Product SummaryDocument9 pages30V Dual N-Channel MOSFET With Schottky Diode: General Description Product SummaryRafael HurtadoNo ratings yet

- SCR Guide PDFDocument16 pagesSCR Guide PDFmarquitos550bNo ratings yet

- Power MOSFET BasicsDocument10 pagesPower MOSFET BasicsBob ProebstelNo ratings yet

- LG Flat TV 32LG40 Manual de EntrenamientoDocument87 pagesLG Flat TV 32LG40 Manual de EntrenamientoMiguel Gabriel TunNo ratings yet

- Carga Inductiva Con TriacDocument11 pagesCarga Inductiva Con Triacanon_274509247No ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- D13N03LTDocument12 pagesD13N03LTmarquitos550bNo ratings yet

- SCR Guide PDFDocument16 pagesSCR Guide PDFmarquitos550bNo ratings yet

- Lattice WP Flash CorruptionDocument8 pagesLattice WP Flash Corruptionmarquitos550bNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- APPCON Technologies: APC220NDocument6 pagesAPPCON Technologies: APC220Nmarquitos550bNo ratings yet

- Nand 01 GW 3 B 2 N 6Document64 pagesNand 01 GW 3 B 2 N 6marquitos550bNo ratings yet

- Ohaus TS200sDocument77 pagesOhaus TS200smarquitos550bNo ratings yet

- Max 4614Document12 pagesMax 4614marquitos550bNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Trimble Lassen SQDocument196 pagesTrimble Lassen SQmarquitos550bNo ratings yet

- 651Document26 pages651riskraj1984No ratings yet

- Pioneer pdp-424mv Pdp-42mve1 (ET)Document122 pagesPioneer pdp-424mv Pdp-42mve1 (ET)Manuel PeraltaNo ratings yet

- Sheet 3Document5 pagesSheet 3Yasmin RedaNo ratings yet

- Test Certificates Stainless SteelDocument4 pagesTest Certificates Stainless SteelSurajPandey33% (3)

- S2N Gyro Interface ManualDocument20 pagesS2N Gyro Interface ManualAfrizal Setiawan100% (1)

- Calculation Surfaces (Results Overview) : Philips HRODocument4 pagesCalculation Surfaces (Results Overview) : Philips HROsanaNo ratings yet

- Installation InstructionsDocument3 pagesInstallation InstructionsRosaLovaNo ratings yet

- C ElanchezhianDocument8 pagesC ElanchezhiankeshavuvceNo ratings yet

- ABB SWBD VD4 Brochure PDFDocument6 pagesABB SWBD VD4 Brochure PDFanand_girgaonkarNo ratings yet

- T8000 Type2 USER MANUAL - 47501358-A0 EN 2016-6-1Document10 pagesT8000 Type2 USER MANUAL - 47501358-A0 EN 2016-6-1AerdiaNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Sao Paulo Brand BookDocument104 pagesSao Paulo Brand Booknicoagudelo82No ratings yet

- Generic TWS600S Service ManualDocument113 pagesGeneric TWS600S Service ManualWise So100% (2)

- VLSI Design FlowDocument20 pagesVLSI Design FlowPranav DarganNo ratings yet

- Civil Engineering Interview QuestionsDocument12 pagesCivil Engineering Interview Questionsjadgug100% (1)

- 4wd SystemDocument31 pages4wd SystemManuales Transmisiones AutomaticasNo ratings yet

- Thinker Thought Sara HendrenDocument1 pageThinker Thought Sara HendrenNathaniel RiversNo ratings yet

- Ingrid Olderock La Mujer de Los Perros by Nancy GuzmnDocument14 pagesIngrid Olderock La Mujer de Los Perros by Nancy GuzmnYuki Hotaru0% (3)

- Telecommunication Switching Systems and Networks by Thiagarajan Viswanathan Manav Bhatnagar B00tqoystkDocument5 pagesTelecommunication Switching Systems and Networks by Thiagarajan Viswanathan Manav Bhatnagar B00tqoystkKittu KumarNo ratings yet

- Manual de Partes LDW1003 (6B01E0)Document54 pagesManual de Partes LDW1003 (6B01E0)Enrique AssmannNo ratings yet

- Vulnerability Management PolicyDocument6 pagesVulnerability Management PolicySerdar AktaşNo ratings yet

- Reduced Vertical Separation Minimum - RVSM: IVAO HQ Training DepartmentDocument4 pagesReduced Vertical Separation Minimum - RVSM: IVAO HQ Training DepartmentjesusNo ratings yet

- PowerMaxExpress V17 Eng User Guide D-303974 PDFDocument38 pagesPowerMaxExpress V17 Eng User Guide D-303974 PDFSretenNo ratings yet

- Manual Yamaha Clavinova P100Document69 pagesManual Yamaha Clavinova P100Nelon Rocha100% (1)

- APL APOLLO - Chaukhat - Catalogue A4 English - 04 03 2022 - Low ResDocument48 pagesAPL APOLLO - Chaukhat - Catalogue A4 English - 04 03 2022 - Low ResarrsshaNo ratings yet

- Supervisory Setpoint Control (SSC) : I/A Series SystemDocument46 pagesSupervisory Setpoint Control (SSC) : I/A Series SystemMiguel Angel GiménezNo ratings yet

- Company Profile Metro GoldrichDocument29 pagesCompany Profile Metro GoldrichBids and Awards CommitteeNo ratings yet

- Software: Measurlink Is An Easy-To-Use, Windows-Based Family of Quality Data Management Software ApplicationsDocument8 pagesSoftware: Measurlink Is An Easy-To-Use, Windows-Based Family of Quality Data Management Software ApplicationsBrandi DaleNo ratings yet

- Full Marks: 50 Duration: 3 HoursDocument2 pagesFull Marks: 50 Duration: 3 HoursK JaiswalNo ratings yet

- Vatufeku Longman Writing Academic English Xufex PDFDocument4 pagesVatufeku Longman Writing Academic English Xufex PDFNZAR AREFNo ratings yet

- TIBCO Hawk Rulebase Standard GuidelinesDocument9 pagesTIBCO Hawk Rulebase Standard GuidelinesAshish ShrivastavaNo ratings yet