Professional Documents

Culture Documents

VLSI Lab VHDL Simulation & FPGA Implementation

Uploaded by

Karthikeyan JhkOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI Lab VHDL Simulation & FPGA Implementation

Uploaded by

Karthikeyan JhkCopyright:

Available Formats

VLSI Laboratory "L" Scheme - Sub Code: 24057 1.

SIMULATION OF VHDL CODE FOR COMBINATIONAL CIRCUIT Optimize a 4 variable combinational function (SOP or POS), describe it in VHDL code and simulate it. Example: F= ( 0,5,8,9,12) in sop or pos 2. SIMULATION OF VHDL CODE FOR ARITHMETIC CIRCUITS Design and Develop the circuit for the following arithmetic function in VHDL Codes and simulate it. Addition, Subtraction Multiplication (4 x 4 bits) 3. SIMULATION OF VHDL CODE FOR MULTIPLEXER Design and develop a 2 bit multiplexer and port map the same for developing up to 8 bit multiplexer. 4. SIMULATION OF VHDL CODE FOR DEMULTIPLEXER Design and develop an 8 output demultiplexer. Simulate the same code in the software 5. VHDL IMPLEMENTATION OF MULTIPLEXER Describe the code for a multiplexer and implement it in FPGA kit in which switches are connected for select input and for data inputs a LED is connected to the output. 6. VHDL IMPLEMENTATION OF DEMULTIPLEXER Switches are connected for select inputs and a data input, Eight LEDs are connected to the output of the circuit. 7. VHDL IMPLEMENTATION OF 7 SEGMENT DECODER Develop Boolean expression for 4 input variables and 7 output variables. Design and develop a seven segment decoder in VHDL for 7 equations. A seven segment display is connected to the output of the circuit. Four switches are connected to the input. The 4 bit input is decoded to 7 segment equivalent. 8. VHDL IMPLEMENTATION OF 7 SEGMENT DECODER BY LUT Develop a 7 segment decoder using Look up table. Describe the seven segment decoder in VHDL using developed Look up table. A seven segment display is connected to the output of the circuit. Four switches are connected to the input. The 4 bit input is decoded into 7 segment equivalent. 9. VHDL IMPLEMENTATION OF ENCODER Design and develop HDL code for decimal (Octal) to BCD encoder. There will be10 input switches (or 8 switches) and 4 LEDs in the FPGA kit. The input given from switches and it is noted that any one of the switch is active. The binary equivalent for the corresponding input switch will be glowing in the LED as output. 10. SIMULATION OF VHDL CODE FOR DELAY Develop a VHDL code for making a delayed output for 1second or 2 seconds by assuming clock frequency provided in the FPGA Kit. 11. VHDL IMPLEMENTATION FOR BLINKING A LED Develop a VHDL Code for delay and verify by simulating it. This delay output is connected to LED. Delay is adjusted such away LED blinks for every 1 or 2 seconds. 12. SIMULATE A VHDL TEST BENCH CODE FOR TESTING A GATE Develop a VHDL test bench code for testing any one of the simple gate. Simulate the test bench code in the HDL software. 13. VHDL IMPLEMENTATION FOR BLINKING A ARRAY OF LEDS Design and develop a VHDL Code for 4 bit binary up counter. Four LEDs are connected at the output of the counter. The counter should up for every one seconds. 14. VHDL IMPLEMENTATION OF A SPELLER WITH AN ARRAY OF LEDS Design and develop VHDL Code for a 5 bit Johnson ring counter 4 bit The LEDs are connected at the output of the counter. The speller should work for every one seconds. 15. VHDL IMPLEMENTATION OF 7 SEGMENT DISPLAY Design and develop a seven segment decoder in VHDL. Design and develop a 4 bit BCD counter, the output of the counter is given to seven segment decoder. A seven segment display is connected to the output of the decoder. The display shows 0, 1, 2... 9 for every one second

You might also like

- Exploring Arduino: Tools and Techniques for Engineering WizardryFrom EverandExploring Arduino: Tools and Techniques for Engineering WizardryRating: 4.5 out of 5 stars4.5/5 (5)

- C Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingFrom EverandC Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingNo ratings yet

- Viva QuestionsDocument19 pagesViva QuestionskslnNo ratings yet

- BCD To 7 SegmentDocument6 pagesBCD To 7 SegmentAndhe PraveedNo ratings yet

- Design and build gray code and BCD convertersDocument3 pagesDesign and build gray code and BCD convertersmarkjesterNo ratings yet

- BCD To 7 SegmentDocument7 pagesBCD To 7 SegmentAnonymous VMgblZLbVUNo ratings yet

- VHDL code for BCD to 7-segment displayDocument4 pagesVHDL code for BCD to 7-segment displayDevdatta Supnekar100% (2)

- BCD To 7 Segment LED Display Decoder CircuitDocument6 pagesBCD To 7 Segment LED Display Decoder CircuitMarx Lennin CabalticanNo ratings yet

- Introduction For 7 Segment DisplayDocument3 pagesIntroduction For 7 Segment DisplayDennis DomingoNo ratings yet

- VLSI Lab Experiment ListDocument2 pagesVLSI Lab Experiment ListShivam SanwariaNo ratings yet

- Codd Lab ManualDocument86 pagesCodd Lab ManualShreyaank RaoNo ratings yet

- List of ExperimentsDocument58 pagesList of ExperimentsPraveen KumarNo ratings yet

- Lab ManualDocument78 pagesLab Manualgurusandhya11No ratings yet

- VHDL Coding Tips and Tricks - VHDL Code For BCD To 7-Segment Display ConverterDocument4 pagesVHDL Coding Tips and Tricks - VHDL Code For BCD To 7-Segment Display Convertermrithyunjaysiv100% (1)

- Circuit Board 7 SegmentDocument6 pagesCircuit Board 7 SegmentDany SetyawanNo ratings yet

- Name: P.Aswin Bharathi Date: 24-02-2021 Reg - Num: 9519005303 Experiment Number: 1 Study of Embedded Soc in Fpga AimDocument13 pagesName: P.Aswin Bharathi Date: 24-02-2021 Reg - Num: 9519005303 Experiment Number: 1 Study of Embedded Soc in Fpga AimbalaNo ratings yet

- VLSI Design AssignmentDocument3 pagesVLSI Design Assignmentabhijit_jamdadeNo ratings yet

- ECE 2003 ManualDocument79 pagesECE 2003 Manualannambaka satishNo ratings yet

- BCD To 7 Segment DecoderDocument39 pagesBCD To 7 Segment DecoderEljon Reaño De OcampoNo ratings yet

- Subject Code HDL 2003Document45 pagesSubject Code HDL 2003Suguna ShivannaNo ratings yet

- Display LCDDocument4 pagesDisplay LCDwilliams missael100% (2)

- HDL Lab Manual Final 2017Document65 pagesHDL Lab Manual Final 2017eshwar_worldNo ratings yet

- Raana Semicondutors PVT LTD: ARM 7-LPC2148 Development BoardDocument107 pagesRaana Semicondutors PVT LTD: ARM 7-LPC2148 Development BoardVimal RajNo ratings yet

- Programmable Electronic AssignmentDocument2 pagesProgrammable Electronic Assignmentnazir143No ratings yet

- I2c 2004 LCDDocument26 pagesI2c 2004 LCDizaqui bernardoNo ratings yet

- Experiment No. 3Document6 pagesExperiment No. 3John FarandisNo ratings yet

- List of Lab Exercises For VHDL LabDocument3 pagesList of Lab Exercises For VHDL LabDivyanshu ShekharNo ratings yet

- Avionics - Decoders & EncodersDocument5 pagesAvionics - Decoders & EncoderskrishnamurthyVishNo ratings yet

- Lab - 8, Implementation of Combinational Circuits Using VHDL Design EntryDocument18 pagesLab - 8, Implementation of Combinational Circuits Using VHDL Design EntrySeif-El-Islam BayNo ratings yet

- Hello WorlvvvvvdDocument8 pagesHello WorlvvvvvdbrodryuNo ratings yet

- 7-Segment Display DecoderDocument5 pages7-Segment Display DecodernamsabeerNo ratings yet

- Implementing a 7-Segment DisplayDocument3 pagesImplementing a 7-Segment DisplayDeepam AsnaniNo ratings yet

- DSD Importanat Question Unit Wise Unit 1Document2 pagesDSD Importanat Question Unit Wise Unit 1siddharthgrgNo ratings yet

- Integral University, Lucknow Department of Electronics &communication EngineeringDocument1 pageIntegral University, Lucknow Department of Electronics &communication EngineeringArshadNo ratings yet

- Verilog Basic ExperimentsDocument62 pagesVerilog Basic ExperimentsGaurav Soni0% (1)

- HDL LAB EXPERIMENTS AND CODESDocument76 pagesHDL LAB EXPERIMENTS AND CODESvijaykannamallaNo ratings yet

- Arduino - LiquidCrystalDocument5 pagesArduino - LiquidCrystalIonutm100% (1)

- CH 08Document82 pagesCH 08Luis Eduardo García QuesadaNo ratings yet

- BCD To 7 Segment LED Display Decoder Circuit Diagram and WorkingDocument19 pagesBCD To 7 Segment LED Display Decoder Circuit Diagram and WorkingAashish KumarNo ratings yet

- EC8711 Embedded Lab Manual FinalDocument258 pagesEC8711 Embedded Lab Manual FinalbloomeceNo ratings yet

- Pic 18 F 4520Document51 pagesPic 18 F 4520sitizarina78100% (1)

- Carry Save Adder VHDL CodeDocument16 pagesCarry Save Adder VHDL CodeAnónimo AnónimoNo ratings yet

- Digital Electronics On Seven Segment Display DecoderDocument18 pagesDigital Electronics On Seven Segment Display DecodernikhilmalagiNo ratings yet

- Pic Lab ManualDocument29 pagesPic Lab ManualK T7No ratings yet

- DLD 7-1Document4 pagesDLD 7-1lalatendu9938No ratings yet

- Embedded System Lab - Blinking LED, Seven Segment Display and LCD Interfacing Projects Using PIC MicrocontrollerDocument62 pagesEmbedded System Lab - Blinking LED, Seven Segment Display and LCD Interfacing Projects Using PIC Microcontrollerfatima100% (1)

- BCD To Seven Segment Decoder PresentationDocument12 pagesBCD To Seven Segment Decoder PresentationIoT Library100% (1)

- VLSIDocument5 pagesVLSIAnurag MishraNo ratings yet

- Indian Institute of Technology Goa EE 232 Digtial Circuits and Lab Assignment VII : Seven Segment DisplayDocument2 pagesIndian Institute of Technology Goa EE 232 Digtial Circuits and Lab Assignment VII : Seven Segment DisplayNeeleswarNo ratings yet

- 8051 Second Programming ExcerciseDocument4 pages8051 Second Programming Excercisev.kinnarNo ratings yet

- DECODERSDocument14 pagesDECODERSSarangNo ratings yet

- ESP-32 Dev Kit C V4 - ENDocument31 pagesESP-32 Dev Kit C V4 - ENsl2976818No ratings yet

- HDL Lab Manual: Anandanagar, Bangalore-24Document81 pagesHDL Lab Manual: Anandanagar, Bangalore-24Abinet ArbaNo ratings yet

- Esp32 Iot Development KitDocument66 pagesEsp32 Iot Development KitElada MohamedNo ratings yet

- Cpe523 Tutorial QuestionsDocument1 pageCpe523 Tutorial QuestionsKolawole JosephNo ratings yet

- PIC LAB ManualDocument13 pagesPIC LAB ManualxyzzyzNo ratings yet

- Interfacing LCD To ArduinoDocument5 pagesInterfacing LCD To ArduinoShahrim Mohd100% (2)

- Design Recipes for FPGAs: Using Verilog and VHDLFrom EverandDesign Recipes for FPGAs: Using Verilog and VHDLRating: 2 out of 5 stars2/5 (1)

- CS6412Document1 pageCS6412Karthikeyan JhkNo ratings yet

- Circuit Simulation LabDocument18 pagesCircuit Simulation LabKarthikeyan Jhk100% (1)

- 2008 Anna University SyllabusDocument30 pages2008 Anna University SyllabusKarthikeyan JhkNo ratings yet

- 2008 Anna University SyllabusDocument30 pages2008 Anna University SyllabusKarthikeyan JhkNo ratings yet

- Dear Student,: MBA Degree Program Details of Bharathiar UniversityDocument6 pagesDear Student,: MBA Degree Program Details of Bharathiar UniversityKarthikeyan JhkNo ratings yet

- Ec2405 Ece Lab ManualDocument10 pagesEc2405 Ece Lab ManualKarthikeyan JhkNo ratings yet

- XR2206Document16 pagesXR2206Himma FirdausNo ratings yet

- 8086 OpcodesDocument2 pages8086 OpcodesKarthikeyan JhkNo ratings yet

- LPC 2148Document62 pagesLPC 2148Karthikeyan JhkNo ratings yet

- Boeing 777 High Lift Control System: IEEE Aerospace and Electronic Systems Magazine September 1993Document8 pagesBoeing 777 High Lift Control System: IEEE Aerospace and Electronic Systems Magazine September 1993Manuel HervasNo ratings yet

- Dji Robomaster Ai Challenge Technical ReportDocument10 pagesDji Robomaster Ai Challenge Technical ReportSaad khalilNo ratings yet

- What are the cousins of the compilerDocument6 pagesWhat are the cousins of the compilerManinblack ManNo ratings yet

- User Manual For PileGroupDocument120 pagesUser Manual For PileGroupmyplaxisNo ratings yet

- Structure of MatplotlibDocument32 pagesStructure of Matplotlibshyam krishnan sNo ratings yet

- DMOS Microstepping Driver With Translator: Description Features and BenefitsDocument12 pagesDMOS Microstepping Driver With Translator: Description Features and BenefitsAhmad SaeedNo ratings yet

- 1000 Ways To Pack The Bin PDFDocument50 pages1000 Ways To Pack The Bin PDFafsarNo ratings yet

- Mobicrowd: Mobile Crowdsourcing On Location-Based Social NetworksDocument9 pagesMobicrowd: Mobile Crowdsourcing On Location-Based Social NetworksjasonwNo ratings yet

- IS7910 BioGraph Infiniti System Known IssuesDocument5 pagesIS7910 BioGraph Infiniti System Known IssuesDiego Eduardo Mora GarcíaNo ratings yet

- T REC G.984.4 201007 I!Amd3!PDF EDocument10 pagesT REC G.984.4 201007 I!Amd3!PDF ERoberto CardosoNo ratings yet

- Chapter 05: Animation: Part 1: Key Team QuizDocument6 pagesChapter 05: Animation: Part 1: Key Team QuizHồng NhungNo ratings yet

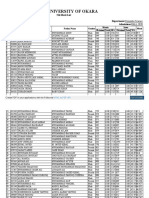

- University of Okara: 5th Merit List Department:Computer Science Admissions:FALL 2020Document5 pagesUniversity of Okara: 5th Merit List Department:Computer Science Admissions:FALL 2020Saghar Asi AwanNo ratings yet

- What Is New in PTV Vissim/Viswalk 11Document20 pagesWhat Is New in PTV Vissim/Viswalk 11Billy BrosNo ratings yet

- ARM Processor RoadmapDocument23 pagesARM Processor RoadmapKi Ki100% (1)

- Time Calculation Rule Fast Formula Reference GuideDocument58 pagesTime Calculation Rule Fast Formula Reference GuideMohammed Nadeem Ulla SNo ratings yet

- Yogesh Meena (BCA-M15 4th SEM) CONM CCEDocument10 pagesYogesh Meena (BCA-M15 4th SEM) CONM CCEYogesh MeenaNo ratings yet

- Create Endless Running Game in UnityDocument37 pagesCreate Endless Running Game in UnityChikeluba ObioraezeNo ratings yet

- Dell Se2717h Monitor - User's Guide - en UsDocument51 pagesDell Se2717h Monitor - User's Guide - en UseruizalvaradoNo ratings yet

- Pentest Lab Setup: WWW - Uat.eduDocument8 pagesPentest Lab Setup: WWW - Uat.eduapi-549068032No ratings yet

- Railway Management SystemDocument50 pagesRailway Management SystemSukanya Devi100% (2)

- Upload 1 Document To Download: YALE (A910) GLC25VX LIFT TRUCK Service Repair Manual PDFDocument3 pagesUpload 1 Document To Download: YALE (A910) GLC25VX LIFT TRUCK Service Repair Manual PDFddsdsNo ratings yet

- Imageprograf Ipf780 SM Rev3 022717Document320 pagesImageprograf Ipf780 SM Rev3 022717Rick_IngersollNo ratings yet

- Install Linux On A Chromebook and Unlock Its Full PotentialDocument9 pagesInstall Linux On A Chromebook and Unlock Its Full PotentialAshvin AppadooNo ratings yet

- Technical Manual Storage Electric Water Heaters - VLSDocument18 pagesTechnical Manual Storage Electric Water Heaters - VLSdim-elNo ratings yet

- User Experience Design Internship: Sahil KundalDocument15 pagesUser Experience Design Internship: Sahil KundalSahil KundalNo ratings yet

- Is 1501 Part 1Document114 pagesIs 1501 Part 1Mohit DhimaanNo ratings yet

- Azure Cost Optimization: A Complete Guide ToDocument16 pagesAzure Cost Optimization: A Complete Guide ToShanmuganathan Ramanathan100% (1)

- Technical Marketing Information (TMI) : Shane GillesDocument28 pagesTechnical Marketing Information (TMI) : Shane Gillesdon cargaNo ratings yet

- Nintendo 3dsDocument29 pagesNintendo 3dsAnthony PerezNo ratings yet

- Arid Agriculture University, Rawalpindi: NstructionsDocument10 pagesArid Agriculture University, Rawalpindi: NstructionsArsal Javed ButtNo ratings yet