Professional Documents

Culture Documents

A Seamless Mode Transfer Maximum Power Point Tracking Controller For Thermoelectric Generator Applications

Uploaded by

sumiths32Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Seamless Mode Transfer Maximum Power Point Tracking Controller For Thermoelectric Generator Applications

Uploaded by

sumiths32Copyright:

Available Formats

Novel High Step-Up DC-DC Converter with

Coupled-Inductor and Switched-Capacitor

Techniques

Yi-Ping Hsieh, Jiann-Fuh Chen, Tsorng-Juu Liang, and Lung-Sheng Yang

Department of Electrical Engineering, National Cheng Kung University, Taiwan

Abstract A novel high step-up DC-DC converter with

coupled-inductor and switched-capacitor techniques is proposed

in this paper. The capacitors are charged in parallel and are

discharged in series by the coupled inductor, stacking on the

output capacitor. Thus, the proposed converter can achieve high

step-up voltage gain with appropriate duty ratio. Besides, the

voltage spike on the main switch can be clamped. Therefore, low

ON-state resistance R

DS(ON)

of the main switch can be adopted to

reduce the conduction loss. The efficiency can be improved. The

operating principle and steady-state analyses are discussed in

detail. Finally, a prototype circuit with 24-V input voltage, 400-V

output voltage, and 200-W output power is implemented in the

laboratory. Experiment results confirm the analysis and

advantages of the proposed converter.

Index Terms High step-up voltage gain, coupled-inductor,

switched capacitor

I. INTRODUCTION

Renewable energy systems are more and more widely

used to provide electric energy. However, the fuel cells,

photovoltaic arrays source are low-voltage source, needing

step-up DC-DC converter as the front-stage to boost low

voltage to high voltage for inverter to feed AC utility.

Although the PV solar cell can connect in series to get high

voltage for grid-connected, the voltage might effect by shadow

effect. Also, the broken of one of the PV array leads to shut

down the system. By using the high step-up converters,

modules can worked independently to generated power as

microgrid and avoid the effect [1]-[3]. Theoretically, Boost

and buck-boost converters can provide high step-up voltage

gain with extremely high duty ratio. In practice, the voltage

gain is limited by the effect of power switch, rectifier diode,

and equivalent series resistance (ESR) of inductor and

capacitor. Also, the extreme high duty-ratio operation may

result in serious reverse-recovery problem, low efficiency and

the electromagnetic interference (EMI) problem [4].

Copyright (c) 2009 IEEE. Personal use of this material is permitted.

However, permission to use this material for any other purposes must be

obtained from the IEEE by sending a request to pubs-permissions@ieee.org

This work made use of Shared Facilities supported by the Research

Center of Ocean Environment and Technology, and Ocean Energy Research

Center

Yi-Ping Hsieh is with Department of Electrical Engineering, National

Cheng Kung University (NCKU), Tainan City, Taiwan, R.O.C. (e-mail:

kyo124718@yahoo.com.tw).

L.-S. Yang is with the Department of Electrical Engineering, Far East

University, Tainan, Taiwan. (e-mail: yanglungsheng@yahoo.com.tw).

Generally speaking, high step-up converter is used for

these applications which required to have high voltage gain,

and high efficiency [5], [6]. To achieve high step-up voltage

gain, many converters have been proposed. The means on the

literature can be discussed in two sections: capacitor means

and magnetic means.

Capacitor means include cascade technique, switched-

capacitor technique and voltage-lift technique. Two cascade

boost converter can achieve high step-up voltage gain but it

has energy-two-processing structure [7]. Thus, the efficiency is

low and needs two switches. The voltage-lift technique and

switched-capacitor can achieve high step-up voltage gain [8]-

[12]. However, the main switch suffers high transient current,

the conduction loss is increased.

Magnetic means include coupled-inductor technique. The

switched coupled-inductor technique is proposed. The

converters can achieve high step-up voltage gain by adjusting

the turns ratio of coupled inductor [13]. Although the leakage

energy can send to the output directly, the voltage stress of

switch is equal to output voltage. It is difficult to chose low

R

ds(on)

switch. Thus, the converter is proposed [14]. The third

winding is added and the voltage stress of main switch is

reduced. Low R

ds(on)

switch can be chose to reduce conduction

loss. The switched coupled-inductor technique is a very good

method to achieve high step-up voltage gain. This technique

can apply in many converters and achieve a good performance

[15]. However, once the voltage of secondary-side is build, the

current-flowing path of leakage inductor is cut. If the energy of

leakage inductor cannot release to output totally, some energy

may dissipation on switch. The passive clamp circuit for

coupled inductor converter is proposed which can recycle the

energy of leakage inductor totally [16]. Also, the converters

using a coupled inductor with an active clamp circuit have

been proposed, but the cost increases due to the extra power

switch and high-side driver [17], [18]. An integrated boost-

flyback converter is proposed. The coupled-inductor is used as

a transformer in flyback converter and the converter uses

output-voltage stacking to achieve high step-up voltage gain.

Besides, the energy of leakage inductor is recycled into the

output capacitor directly. Thus, the voltage spike of the main

switch is limited. [19], [20]. To have large high step-up

voltage gain, some converters have been proposed which use

the coupled-inductor as a transformer in flyback and forward

converter. The utilization of core is added [21]-[23].

Additionally, many converters using three-output-voltage

The proposed converter operating in continuous

conduction mode (CCM) and discontinuous conduction mode

(DCM) are analyzed as follows.

stacking to increase voltage gain are proposed [24]-[26]. The

boost-sepic converter with the coupled-inductor and output

stacking techniques has been proposed [27]. The high step-up

boost converter uses multiple coupled-inductor of output

stacking is proposed [28], [29]. To increase the voltage gain,

the converters add the number of turns ratio and extra

additional winding stages. The complexity is added.

This paper proposes a novel high step-up voltage gain

converter. The proposed converter uses the coupled-inductor

and switched-capacitor techniques. The coupled inductor is

operated as transformer in flyback and forward converters.

Thus, the capacitors on the output-stacking are charged in

parallel and are discharged in series to achieve high step-up

gain. Also, the voltage spike of the main switch is limited and

voltage stress can be adjusted by the turns ratio of the coupled-

inductor. Therefore, low ON-state resistance R

DS(ON)

of the

main switch can be adopted to reduce the conduction loss. Fig. 1 Circuit configuration of the proposed converter

II. OPERATING PRINCIPLE OF THE PROPOSED CONVERTER

(A) CCM Operation

Based on the above assumptions, fig. 2 illustrates the

typical waveforms and fig. 3 shows the topological stages of

the proposed converter. The operating modes are described as

follows:

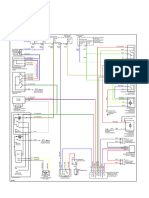

Fig. 1 shows the circuit topology of the proposed

converter. The equivalent circuit model of the coupled

inductor includes the magnetizing inductor L

m

, leakage

inductor L

k

and an ideal transformer. This converter consists of

one power switch, six diodes and six capacitors. The leakage-

inductor energy of the coupled inductor is recycled to the

capacitor C

1

, and thus the voltage across the switch S can be

clamped. Also, the voltages across the capacitors C

2

, C

3

, C

4

and C

5

can be adjusted by the turns ratio of the coupled

inductor. The voltage level of the switch is reduced

significantly and low conducting resistance R

ds(on)

of the switch

can be used. Thus, the efficiency of the proposed converter can

be increased and high step-up voltage gain can be achieved.

1) Mode I [t

0

, t

1

]: During this time interval, S is turned on.

Diodes D

1

, D

2

, and D

5

are turned off, and D

3

, D

4

and D

6

are

turned on. The current-flow path is shown in fig. 3(a). The

voltage of primary-side is V

in

= v

Lk

+V

L1

. Thus, leakage

inductor L

k

and magnetic inductor L

m

is charged by DC-

source V

in

. The primary current i

Lk

increases linearly. Due

to leakage inductor L

k

, the secondary-side current i

s

decreases linearly. Secondary-side voltage V

L2

, V

c2

and V

c5

are connected in series to charge output capacitor C

6

and to

provide the energy to load R. Because i

s

decreases linearly,

the reverse-recovery problem of the diode is alleviated.

When current i

s

becomes zero at t = t

1

, this operating mode

is ended.

When switch S is turned on, DC source V

in

charges

leakage inductor L

k

, magnetic inductor L

m

and the coupled

inductor induced voltage V

L2

on the secondary-side. Voltages

V

L2

and V

c4

connected in series to charge capacitor C

5

.

Meanwhile, Voltages V

L2

and V

c3

connected in series to charge

capacitor C

2

. Thus, two capacitors C

2

and C

5

are charge in

parallel. When switch S is turned off, the energy of leakage

inductor L

k

is released to output capacitor C

1

directly and

magnetic energy of L

m

released by the coupled inductor. The

induced voltage V

L2

on the secondary-side of coupled inductor

charges capacitors C

3

and C

4

in parallel. Also, voltages V

L2

, V

c2

and V

c5

are connected in series to charge output capacitor C

6

.

The output voltage is stacked by capacitors C

1

and C

6

. The

high step-up voltage gain is achieved. The energy of leakage

inductor is sent to output. The voltage stress of main switch is

clamped.

2) Mode II [t

1

, t

2

]: During this time interval, S is still turned on.

Diodes D

1

, D

3

, D

4

and D

6

are turned off, and D

2

and D

5

are

turned on. The current-flow path is shown in fig. 3(b). The

magnetizing inductor L

m

is charged by DC-source V

in

. The

coupled inductor induces voltage V

L2

on the secondary-side.

Voltage V

L2

which is connecting V

C3

in series and

connecting V

C4

in series charge C

2

and C

5

in parallel. A

part of the energy of DC-source V

in

is transferred to

capacitors C

2

and C

5

via the coupled inductor. Also, the

energies of C

3

and C

4

are transferred to capacitors C

2

and

C

5

together. Meanwhile, voltages V

c2

and V

c5

are

approximately equal to nV

in

+V

c3

. The output capacitor and

C

1

and C

6

provides its energy to load R. This operating

mode is ended when switch S is turned off at t = t

2

. To simplify the circuit analysis, the following conditions are

assumed: 3) Mode III [t

2

, t

3

]: During this time interval, S is turned off.

Diodes D

1

, D

3

, D

4

and D

6

are turned off, and D

2

and D

5

are

turned on. The current-flow path is shown in fig. 3(c). The

energies of leakage inductor L

k

and magnetizing inductor

L

m

are released to the parasitic capacitor C

ds

of switch S.

Capacitors C

2

and C

5

are charged by DC-source V

in

. Output

capacitors C

1

and C

6

provide energy to load R. When the

capacitor voltage V

c1

is equal to V

in

+V

ds

at t = t

3

, diode D

1

is conducted and this operating mode is ended.

1) Capacitors C

1

-C

6

are large enough. Thus, V

c1

-V

c6

are

considered as constant in one switching period.

2) The power devices are ideal, but the parasitic capacitor

of the power switch is considered.

3) The coupling-coefficient of the coupled-inductor k is

equal to L

m

/(L

m

+L

k

) and the turns ratio of the

coupled-inductor n is equal to N

s

/N

p

.

4) Mode IV [t

3

, t

4

]: During this time interval, S is turned off.

Diodes D

1

, D

2

, and D

5

are turned on, and D

3

, D

4

, and D

6

are turned off. The current-flow path is shown in fig. 3(d).

The energies of leakage inductor L

k

and magnetizing

inductor L

m

is released to capacitor C

1

. Thus, the voltage

across the switch is clamped at V

c1

. The current i

Lk

decreases quickly. The secondary-side voltage of the

coupled inductor V

L2

charges capacitors C

2

and C

5

in

parallel until the secondary-side current i

s

equals zero.

Thus, diodes D

2

and D

5

are cut off at t = t

4

. This operating

mode is ended.

5) Mode V [t

4

, t

5

]: During this time interval, S is turned off.

Diodes D

1

, D

3

, D

4

and D

6

are turned on, and D

2

and D

5

are

turned off. The current-flow path is shown in fig. 3(e). The

energies of leakage inductor L

k

and magnetizing inductor

L

m

is released to capacitor C

1

. Capacitors C

3

and C

4

are

charged in parallel by the magnetizing-inductor energy via

coupled inductor. Simultaneously, secondary-side voltage

V

L2

is connected with V

c2

and V

c5

in series and charges

output capacitor C

6

. This operating mode is ended when

capacitor C

1

starts to discharge at t = t

5

.

6) Mode VI [t

5

, t

6

]: During this time interval, S is still turned

off. Diodes D

3

, D

4

and D

6

are turned on, and D

1

, D

2

and D

5

are turned off. The current-flow path is shown in fig. 3(f).

The magnetizing energy of L

m

is transferred to capacitors

C

3

and C

4

by coupled inductor

.

Thus, two capacitors are

charged in parallel. Also, V

L2

, V

c2

and V

c5

are connected in

series and charge capacitor C

6

. This mode is ended at t = t

6

when S is turned on at the beginning of the next switching

period.

Fig. 2 Some typical waveforms of the proposed converter at CCM operation.

(a) Mode I

(b) Mode II

Vo

Vin

S

Np

D2

C1

R

Ns

Lk

D5

C2

C5

Lm D1

C4 C3

D4

D3

D6

C6

(c) Mode III

(d) Mode IV

(e) Mode V

(f) Mode VI

Fig. 3 Current-flow path of operating modes during one switching period at

CCM operation. (a) Mode I. (b) Mode II. (c) Mode III. (d) Mode IV. (e) Mode

V. (f) Mode VI.

(B) DCM Operation

To simplify the analysis of DCM operation, the leakage

inductor L

k

of the coupled-inductor is neglected. Fig. 4 shows

typical waveforms of the proposed converter operated in DCM.

Fig. 5 shows the operating stages of each mode. The operating

modes are described as follows:

1) Mode I [t

0

, t

1

]: During this time interval, S is turned on. The

current-flow path is shown in fig. 5(a). The energy of DC-

source V

in

charges magnetizing inductor L

m

. Thus, i

Lm

is

increased linearly. Also, the secondary side of the coupled

inductor is connected series with capacitor C

3

or C

4

and

releases their energies to charge capacitors C

2

and C

5

in

parallel. Output capacitors C

1

and C

6

provide energy to

load R. This mode is ended when S is turned off at t = t

1

.

2) Mode II [t

1

, t

2

]: During this time interval, S is turned off.

The current-flow path is shown in fig. 5(b). The energies of

DC source V

in

and magnetizing inductor L

m

are transferred

to capacitors C

1

and load R. Similarly, capacitors C

2

and C

5

are discharged in series with DC source V

in

and

magnetizing inductor L

m

to capacitor C

6

and load R.

Meanwhile, the energy of magnetizing inductor L

m

is

transferred to capacitors C

3

and C

4

by coil N

s

. This mode is

ended when the energy stored in L

m

is empty at t = t

2

.

3) Mode III [t

2

, t

3

]: During this time interval, S is turned off.

The current-flow path is shown in fig. 5(c). Since the

energy stored in L

m

is empty, the energy stored in C

1

and

C

6

are discharged to load R. This mode is ended when S is

turned on at t = t

3

.

0

i

D2

, i

D5

t

0

0 t

t

DT

s

D

L

T

s

T

s

i

Lm

v

gs

0

i

D6

t

t

0 t

1 t

3

t

2

ModeI ModeII ModeIII

0 t

i

s

I

Lmp

0

i

c6

t

I

Lmp

/3n+1

-I

o

I

Lmp

/3n+1 - I

o

i

D3

, i

D4

0 t

I

Lmp

/3n+1

Fig. 4 Some typical waveforms of the proposed converter at DCM operation.

(a) Mode I

(b) Mode II

(c) Mode III

Fig. 5 Current-flow path of operating modes during one switching period at

DCM operation. (a) Mode I. (b) Mode II. (c) Mode III.

III. STEADY-STATE ANALYSIS OF THE PROPOSED CONVERTER

(A) CCM Operation

At modes IV and V, the energy of the leakage inductor L

k

is released to capacitor C

1

. According to Ref. [16], the energy

released duty cycle D

c1

can be expressed as

1

1

2(1 )

,

1

c

c

s

t D

D

T n

= =

+

(1)

where t

c1

is the time interval from modes IV to V which is

shown in fig. 2.

Since the time durations of modes I, III, and IV are

significantly short, only modes II, V, and VI are considered at

CCM operation for the steady-state analysis.

The voltage equation of mode II can be written based on

fig. 3(b).

(1 ) ,

II

Lk

v k =

in

V

(2)

1

,

II m

L in in

m k

L

v V

L L

= =

+

kV

(3)

2 1

.

II II

L L

v nv nkV = =

in

3

4

(4)

Also, the voltage across capacitors C

2

and C

5

can be written as

2 2

+

II

c L c

V v V = .

(5)

Vo

Vin

S

Np

D2

C1

R

Ns

D5

C2

C

5

Lm D1

C4 C3

D4

D3

D6

C6

5 2

+

II

c L c

V v V = .

(6)

During the time duration of modes V and VI, the following

voltage equations can be derived based on fig. 3(f).

1 1 1

= = .

V VI VI

L L in Lk c

v v V V V

(7)

2 2 3 4 2 5 6

= = = = +

V VI

.

L L c c c c c

v v V V V V V

(8)

2

=

V V

1

.

L L

v nv

(9)

By applying the volt-second balance principle on N

p

and N

s

,

the following equation is given

1

( )

1 1

0

0.

s c s

s

DT D D T

II VI

L L

DT

v dt v dt

+

+

} }

=

=

(10)

2 2

0

0.

s s

s

DT T

II VI

L L

DT

v dt v dt +

} }

(11)

Substituting (1), (3) and (7) into (10), the voltage of capacitors

C

1

is obtained as

1

1 (1 )( 1)

( + ) = .

(12)

1 2(1 )

c in ds

D k n

V V v

D D

=

Fig. 6 Voltage-gain versus duty-ratio at CCM operation under n = 3 and

various k.

And substituting (4) and (8) into (11), the voltage across

capacitors C

3

and C

4

can expressed as

3 4

= .

(13)

1

c c in

Dnk

V V V

D

=

In fig. 7, the curve shows the voltage gain versus the

duty ratio of the proposed converter, and other converters in

[23] and [24] at CCM operation under k =1 and n =3. As two

winding of coupled inductor is used, the voltage gain of

proposed converter is higher than other converters in [23] and

[24]. The proposed converter can using less turns ratio to

achieve the same voltage gain.

Substituting (4) and (13) into (5) and (6) the voltage of

capacitors C

2

and C

5

are obtained as

2 5

= ( ) .

(14)

1

c c in

Dnk

V V nk V

D

= +

And substituting (4), (8) and (12) into (11), the voltage of

capacitor C6 is obtained as

0.5 1

M

CCM

0 0.1 0.2 0.3 0.4 0.6 0.7 0.8 0.9

0

5

10

15

20

25

30

35

40

45

50

D

Proposed Converter

Converter in [24]

Converter in [23]

6

3

(2 ) .

1

c

Dnk

V nk V

D

= +

in

6

(15)

Also, the output voltage can be expressed as

1

+

o c c

V V V =

(16)

Substituting (12) and (15) into (16), the voltage gain is

obtained as

| | ( +1) (1 ) 1+2

= = .

(17)

1 2(1 )

o

CCM

in

D n k k V nk

M

V D D

+

Fig. 7 Voltage-gain versus duty-ratio of the proposed converter, the

converters in [23] and [24] at CCM operation under n = 3 and k =1.

The voltage-gain versus the duty-ratio under various coupling-

coefficients of the coupled-inductor is shown in fig. 6. It

shows that the coupling coefficient results the voltage gain

decline. However, voltage gain is less sensitive to the

coupling-coefficient. When k = 1, the ideal voltage gain is

rewritten as

According to the analysis of the operating modes, the

voltage stresses on main switch S and diodes D

1

-D

6

are given

as

1

,

1 1

o in

ds in

V nV

v V

D n

= =

+

(19)

1 2

1

CCM

n nD

M

D

+ +

=

(18)

1

1

,

1 1

o in

D in

V nV

V V

D n

= =

+

(20)

2 3 4 5 5

= ( )

1 1

.

D D D D D in o in

n n

V V V V V nV

D n

= = = = =

+

V V

(21)

Equations (19), (20) and (21) mean that under the same

voltage gain, the voltage stresses of the proposed converter on

main switch and diodes can be adjusted by the turns ratio.

(B) DCM Operation

6

3

(2 ) ,

c

L

nD

V n V

D

= +

in

(36)

In DCM operation, the typical waveforms are shown in

fig. 4. In the time duration of mode I, switch S is turned on.

Thus, the following equations can be formulated based on fig.

5(a)

Also, the voltage gain is expressed as

1 6

+ (3 1) (2 1) .

o c c in

L

D

V V V n n V

D

(

= = + + +

1

,

I

L in

v V =

(22)

2

.

I

L in

v nV =

(23)

The peak value of the magnetizing-inductor current is given

as

.

in

Lmp s

m

V

I DT

L

=

(24)

Furthermore, the voltage across capacitors C

2

and C

5

can be

written as

(25)

2 2

+

I

c L c

V v V =

3

,

4

1

.

(26)

5 2

+

I

c L c

V v V =

In the time interval of mode II, the following equations can be

expressed based on fig. 5(b):

1

,

II

L in c

v V V =

(27)

2 3 4 2 5 6

+

II

,

L c c c c c

v V V V V V = = =

(28)

2

.

1

II II

L L

v nv =

(29)

During the time interval of mode III, the following equation

can be derived from Fig. 5(c).

1 2

0.

III III

L L

v v = =

(30)

By applying the voltage-second balance principle on coupled

inductor, the following equations are given as

( )

1 1 1

0 (

0.

s L s s

s L s

DT D D T T

I II III

L L L

DT D D T

v dt v dt v dt

+

+

+ +

} } }

+

)

=

)

=

(31)

( )

2 2 2

0 (

0.

s L s s

s L s

DT D D T T

I II III

L L L

DT D D T

v dt v dt v dt

+

+ +

} } }

(32)

Substituting (22) and (27) into (31), the voltage is obtained as

1

(1+ ) ,

c

L

D

V

D

=

in

V

(33)

Similarly, substituting (23) and (28) into (32), the voltage

across capacitors C

2

, C

3

, C

4

, C

5

and C

6

are derived as

3 4

,

c c in

L

nD

V V V

D

= =

(34)

2 5

( ) ,

(35)

c c in

L

nD

V V n V

D

= = +

(

(37)

According to (37), the duty cycle D

L

can be derived as

(1 3 )

.

(1 2 )

in

L

o i

n DV

D

V n

n

V

+

=

+

(38)

From fig. 4, the average value of i

c6

is computed as

6

1

.

2 3 1

Lmp

c L

I

o

I D

n

I =

+

(39)

Since I

c6

is equal to zero under steady state, equations (24),

(38), and I

c6

= 0 can be substituted to (39). Thus, equations

(39) can be rewritten as follows:

| |

2 2

.

2 (1 2 )

in s o

o in m

D V T V

V n V L

=

+ R

(40)

Then, the normalized magnetizing-inductor time constant is

defined as

,

m m s

Lm

s

L L f

RT R

t =

(41)

where f

s

is the switching frequency.

Substituting (41) into (40), the voltage gain is given by

2 2

1 2 (1 2 )

.

2 4 2

o

DCM

in Lm

V n n

M

V

D

t

+ +

= = + +

(42)

The curve of the voltage gain is showed in fig. 8 which

illustrates the voltage-gain versus the duty-ratio under various

Lm

.

(C) Boundary Operating Condition between CCM and DCM

If the proposed converter is operated in boundary

condition mode, the voltage gain of CCM operation is equal

to the voltage gain of DCM operation. The boundary

normalized magnetizing-inductor time constant

LmB

can be

derived from (18) and (42) as

2

(1 )

.

2(1 3 )(1 2 )

LmB

D D

n n nD

t

=

+ + +

(43)

Fig. 9 shows the curve of

LmB

. If

Lm

is larger than

LmB

, the

proposed converter is operated in CCM.

V

o

/ V

in

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

0

5

10

15

20

25

30

35

40

45

50

D

DCM (under Lm = 0.0005)

CCM

DCM (under Lm = 0.0006)

DCM (under Lm = 0.0007)

Fig. 8 Voltage-gain versus duty-ratio at DCM operation under various

Lm

and

at CCM operation under n = 3 and k = 1.

CCM

DCM

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

0

0.0004

0.0008

0.0012

0.0016

0.0020

D

LmB

t

Fig. 9 Boundary condition of the proposed converter under n = 3.

IV. EXPERIMENTAL RESULTS OF THE PROPOSED CONVERTER

A prototype circuit is implemented in the laboratory to

demonstrate the practicability of the proposed converter. The

specifications are as follows:

1) input DC voltage V

in

: 24 V

2) output DC voltage V

o

: 400 V

3) maximum output power: 200 W

4) switching frequency: 50 kHz

5) MOSFET S: IRL83036

6) Diodes D

1

: MBRF20200CT, D

2

/D

3

/D

4

/D

5

/D

6

:

DESP29

7) Coupled inductor: ETD-59, core pc40, N

p

: N

s

= 1 : 3

L

m

= 30 H; L

k

= 0.12 H

8) Capacitors C

2

/C

3

/C

4

/C

5

: 22 F/ 200 V, C

1

: 47F/ 160

V, C

6

: 47 F/ 400 V

Fig. 10 shows the measured waveforms for full-load P

o

= 200 W and V

in

= 24 V. The proposed converter is operated

in CCM under full-load condition. In the measured

waveforms, the peak value of V

ds

is 60.04 V. The duty cycle is

51% and the voltage stress is clamped at appropriately 49 V

during the switch-off period. The waveforms demonstrate that

the steady-state analysis is corresponded. Therefore, the low-

voltage rated switch can be adopted to achieve high efficiency

for the proposed converter.

The waveform of secondary-side current i

s

in fig. 10(a)

shows that the proposed converter is operated in CCM

because the current is not equal to zero when the switch is

turned on. In fig. 10(b), the waveforms of i

D2

and i

D4

show

that capacitors C

2

and C

4

are charged in the different time

durations. Fig. 10(c) shows that the energy of leakage

inductor L

k

is released to capacitor C

1

through diode D

1

. Fig.

10(d) reveals that V

c1

, V

c2

and V

c4

satisfy equations (33), (34)

and (35). In addition, output voltage V

o

is consistent with

Equation (37). Fig. 10(e) shows the voltage stress of main

switch and diodes, and demonstrates the consistency of

Equations (19), (20) and (21). Fig. 11 shows the proposed

converter under the output power variation between light-load

20 W and full-load 200 W.

Fig. 12 shows the experimental conversion efficiency of

the proposed converter. Maximum efficiency is around

95.31% at P

o

= 80 W and V

in

= 24 V. The full-load efficiency

is appropriately 94.06 % at P

o

= 200 W, V

in

= 24 V, and V

out

=

400 V. Compared to other converter, the efficiency is

improved about 2%.

(a)

(b)

Fig. 11 Load variation between light-load P

o

= 20 W and full-load P

o

= 200 W. (c)

Fig. 12 Experimental conversion efficiency.

(d)

V. CONCLUSIONS

This paper has proposed a novel, high efficiency, and

high step-up DC-DC converter with the coupled inductor and

switched capacitors techniques. The proposed converter adds

passive components without extra winding stage, and uses

capacitors charged in parallel and discharged in series with a

coupled-inductor to achieve high step-up voltage gain. The

steady-state analyses of voltage gain and boundary operating

condition are discussed. Finally, a prototype circuit of the

proposed converter is implemented in the laboratory.

Experimental results verify that high efficiency and high step-

up voltage gain can be achieved. The efficiency is 95.31%.

The voltage stress on the main switches is 60 V, thus low

voltage ratings and low on-state resistance levels R

DS(ON)

switch can be selected. (e)

Fig. 10 Experiment results under full-load P

o

= 200 W.

REFERENCES

[1] V. Scarpa, S. Buso, G. Spiazzi, Low-complexity MPPT technique

exploiting the PV module MPP locus characterization, IEEE Trans. Ind.

Electron., vol. 56, no. 5, pp. 1531-1538, 2009

[2] C. L. Chen, Y. W, J. S. Lai, Y.S. Lee, and D. Martin, Design of parallel

inverters for smooth mode transfer microgrid applications, IEEE Trans.

Power Electron., vol. 25, no. 1, pp. 6-15, Jan. 2010

[3] A. Timbus, M. Liserre, R. Teodorescu, P. Rodriguez, and F. Blaabjerg,

Evaluation of current controllers for distributed power generation

systems, IEEE Trans. Power Electron., vol. 24, no. 3, pp. 654-664, Mar.

2009.

[4] R. J. Wai, C. Y. Lin, C. Y. Lin, R. Y. Duan, and Y. R. Chang, High-

efficiency power conversion system for kilowatt-level stand-alone

generation unit with low input voltage, IEEE Trans. Ind. Electron., vol.

55, no. 10, pp. 3702-3714, Oct. 2008.

[5] B. Axelrod, Y. Berkovich, and A. Ioinovici, Transformerless DC-DC

converters with a very high DC line-to-load voltage ratio, Proc. IEEE

ISCAS, pp. III435-III438, 2003.

[6] L. S. Yang, T. J. Liang, and J. F. Chen, Transformer-less DC-DC

converter with high voltage gain, IEEE Trans. Ind. Electron., vol. 56, no.

8, pp. 3144-3152, Aug. 2009.

[7] F. L. Luo and H. Ye, Positive output cascade boost converters, in Proc.

IEEE Electric Power Applications, vol. 151, no. 5, pp. 590-606, Sep. 2004.

[8] F. L. Luo, Six self-lift DCDC converters, voltage lift technique, IEEE

Trans. Ind. Electron., vol. 48, no. 6, pp. 1268-1272, Dec. 2001.

[9] F. L. Luo and H. Ye, Positive output super-lift converters, IEEE Trans.

Power Electron., vol. 18, no. 1, pp. 105-113, Jan. 2003.

[10] F. L. Luo and H. Ye, Positive output multiple-lift pushpull switched-

capacitor Luo-converters, IEEE Trans. Ind. Electron., vol. 51, no. 3, pp.

594-602, Jun. 2004.

[11] Chen Jun and A. Ioinovici, Switching-mode DC-DC converter with

switched capacitor based resonant circuit, IEEE Trans. Circuits and

Systems I, vol. 43, no. 11, pp. 933-938, 1996.

[12] B. Axelrod, Y. Berkovich, and A. Ioinovici, Switched-capacitor/

switched-inductor structures for getting transformerless hybrid DC-DC

PWM converters, IEEE Trans. Circuits and Systems I, vol. 55, no. 2, pp.

687-696, Mar. 2008.

[13] B. Axelrod, Y. Berkovich, and A. Ioinovici, Switched coupled-inductor

cell for DC-DC converters with very large conversion ratio, in Proc.

IEEE IECON Conf., pp. 2366-2371, 2006.

[14] B. Axelrod, Y. Berkovich, S. Tapuchi, and A. Ioinovici, Improved

circuit of the switched coupled-inductor cell for dc-dc converters with

very large conversion ratio, in Proc. IEEE PEA Conf., pp.1-10, Sep.

2009.

[15] B. Axelrod, Y. Berkovich, S. Tapuchi, A. Ioinovici, Steep conversion

ration uk, Zeta, and sepic converters based on a switched coupled-

inductor cell, in Proc. IEEE PES Conf., pp.3009-3014, Jun. 2008.

[16] Q. Zhao and F. C. Lee, High-efficiency, high step-up dc-dc converters,

IEEE Trans. Power Electron., vol. 18, no. 1, pp. 65-73, Jan. 2003.

[17] B. R. Lin and F. Y. Hsieh, Soft-switching zetaflyback converter with a

buckboost type of active clamp, IEEE Trans. Ind. Electron., vol. 54, no.

5, pp. 2813-2822, Oct. 2007.

[18] T. F. Wu, Y. S. Lai, J. C. Hung, and Y. M. Chen, Boost converter with

coupled inductors and buckboost type of active clamp, IEEE Trans. Ind.

Electron., vol. 55, no. 1, pp. 154-162, Jan. 2008.

[19] K. C. Tseng and T. J. Liang, Novel high-efficiency step-up converter,

IEE Proc. Inst. Elect. Eng.-Electric Power Applications, vol. 151, no. 2,

pp. 182-190, Mar. 2004.

[20] K. C. Tseng and T. J. Liang, Analysis of intergrated boost-flyback step-

up converter, IEE Proc. Inst. Elect. Eng.-Electric Power Applications,

vol. 152, no. 2, pp. 217-225, 2005.

[21] R. J. Wai and R. Y. Duan, High-efficiency DC/DC converter with high

voltage gain, IEE Proc. Inst. Elect. Eng.-Electric Power Applications,

vol. 152, no.4, pp. 793-802, Jul. 2005.

[22] R. J. Wai and R. Y. Duan, High step-up converter with coupled-

inductor, IEEE Trans. Power Electron., vol. 20, no. 5, pp. 1025-1035,

Sep. 2005.

[23] R. J. Wai, L. W. Liu, and R. Y. Duan, High-efficiency voltage-clamped

DCDC converter with reduced reverse-recovery current and switch-

voltage stress, IEEE Trans. Ind. Electron., vol. 53, no. 1, pp. 272-280,

Feb. 2005.

[24] J. W. Baek, M. H. Ryoo, T. J. Kim, D. W. Yoo, and J. S. Kim, High

boost converter using voltage multiplier, in Proc. IEEE IECON, pp.

567-572, 2005.

[25] G. V. T. Bascope, R. P. T. Bascope, D. S. Oliveira Jr., S. A. Vasconcelos,

F. L. M. Antunes, and C. G. C. Branco, A high step-up DC-DC converter

based on three-state switching cell, in Proc. IEEE ISIE, pp. 998-1003,

2006.

[26] S. V. Araujo, R. P. Torrico-Bascope, G. V. Torrico-Bascope, Highly

efficient high step-up converter for fuel-cell power processing based on

three-state commutation cell, IEEE Trans. Ind. Electron., vol. 57, no. 6,

pp. 1987-1997, Jun. 2010.

[27] K. B. Park, H. W. Seong, H. S. Kim, G. W. Moon, and M. J. Youn,

Integrated boost-sepic converter for high step-up applications, in Proc.

Power Electronics Specialists Conf., Rohode, Greece, pp. 944-950, 2008.

[28] Y. J. A. Alcazar, R. T. Bascope, D. S. de Oliveira, E. H. P. Andrade, and

W. G. Cardenas, High voltage gain boost converter based on three-state

switching cell and voltage multipliers, in Proc. IEEE IECON, pp. 2346-

2352, 2008.

[29] S. K. Changchien, T. J. Liang, J. F. Chen, L. S. Yang, Novel high step-

up DC-DC converter for fuel cell energy conversion system, IEEE

Trans. Ind. Electron., vol. 57, no. 6, pp. 2007-2017, 2010.

Yi-Ping Hsieh was born in Tainan, Taiwan, in

1986. He received the B.S. degree and the M.S.

degree in electrical engineering from national

Cheng-Kung University (NCKU), Taiwan, in 2008

and 2010, respectively. He is currently pursuing a

Ph.D. degree at NCKU, Taiwan. His research

interests are power factor correction, DC/DC power

converter, DC/AC inverter, renewable energy

conversion, LED lighting and electronic ballast.

Jiann-Fuh Chen (S79M80) was born in Chung-

Hua, Taiwan, in 1955. He received his B.S., M.S. and

Ph.D. degrees in electrical engineering from NCKU

in 1978, 1980 and 1985, respectively.

Since 1980, he has been with the department of

Electrical Engineering at NCKU, where he is

currently a professor. His research interests are power

electronics and energy conversion.

Tsorng-Juu (Peter) Liang (M93-SM10) was born

in Kaohsiung, Taiwan. He received his B.S. degree

in Electrophysics from National Chiao-Tung

University, Hsinchu, Taiwan, in 1985. He received

his M.S. and Ph.D. degrees in Electrical Engineering

from the University of Missouri, Columbia, USA, in

1990 and 1993, respectively.

He is currently a Professor of Electrical

Engineering and Director of Green Energy

Electronics Research Center (GEERC), National

Cheng-Kung University (NCKU), Tainan, Taiwan. Currently, he is the

Associate Editor of IEEE Trans. on Power Electronics, the Associate Editor of

IEEE Trans. on Circuits and Systems-I, and the Technical Committee Chair of

IEEE CAS Systems Power and Energy Circuits and Systems Technical

Committee. He is also on the Board of Directors for Compucase Enterprise

Co., Ltd and Catcher Technology Co., Ltd.

Dr. Liang has authored or coauthored 50 journal and more than 100

conference papers. He was the Director of Electrical Laboratories at NCKU

from 2001-2004. In 2008, he received Outstanding Engineer, The Chinese

Institute of Electrical Engineering, Kaohsiung Chapter and Outstanding

Professor Award, Taiwan Power Electronics Conference. In 2010, he received

Teaching Excellence Award, National Cheng Kung University and

Outstanding Engineers Professor Award, The Chinese Institute of Electrical

Engineering, Kaohsiung Branch. He is a member of the IEEE Societies of

power electronics, industrial electronics, circuits and system, and industrial

applications. His research interests include high efficiency power converters,

high efficiency lighting systems, renewable energy conversion, and power ICs

design.

Lung-Sheng Yang was born in Tainan, Taiwan,

R.O.C., in 1967. He received the B.S. degree in

electrical engineering from National Taiwan

Institute of Technology, Taiwan, the M.S. degree

in electrical engineering from National Tsing-Hua

University, Taiwan, and the Ph.D degree in

electrical engineering from National Cheng-Kung

University in 1990, 1992, and 2007 respectively.

He is currently with the Department of Electrical

Engineering, Far East University, Tainan, where

he is an assistant professor. His research interests

are power factor correction, dcdc converters, renewable energy conversion,

and electronic ballasts.

You might also like

- Drivers Environment and Electrical SystemDocument59 pagesDrivers Environment and Electrical SystemHalil karaNo ratings yet

- Donaldson India - Engine Aftermarket Price List - FY13Document412 pagesDonaldson India - Engine Aftermarket Price List - FY13B Sathish Babu100% (1)

- Dr. Assad Abu-Jasser, ECE-iugaza: Electrical Machines (EELE 4350)Document37 pagesDr. Assad Abu-Jasser, ECE-iugaza: Electrical Machines (EELE 4350)MohammedSaadaniHassani67% (6)

- Power Systems Protection Course: Al-Balqa Applied UniversityDocument36 pagesPower Systems Protection Course: Al-Balqa Applied UniversityAayush PatidarNo ratings yet

- 8FBE Spec SheetDocument12 pages8FBE Spec SheetToni SiquibacheNo ratings yet

- Ac Machines Lab ManualDocument102 pagesAc Machines Lab ManualAshwin Gopinath100% (3)

- Electric Spring For Voltage Stability and Power Factor CorrectionDocument3 pagesElectric Spring For Voltage Stability and Power Factor CorrectionAmalu PhilipNo ratings yet

- Passive Damping Filter Design and Application For Three-Phase PV Grid-Connected InverterDocument3 pagesPassive Damping Filter Design and Application For Three-Phase PV Grid-Connected InverterEditor IJTSRDNo ratings yet

- Preparing Group 1 RS2000 Rally CarsDocument6 pagesPreparing Group 1 RS2000 Rally CarsPhilip RiddlesNo ratings yet

- Buck-boost converter project reportDocument3 pagesBuck-boost converter project reportArnoldo ZereceroNo ratings yet

- High Voltage Engineering: Chapter 4 Generation of High VoltagesDocument75 pagesHigh Voltage Engineering: Chapter 4 Generation of High VoltagesSunny ModiNo ratings yet

- PV BoostDocument6 pagesPV BoostlestherroqueNo ratings yet

- LCL FilterDocument10 pagesLCL Filtersumiths32No ratings yet

- LCL FilterDocument10 pagesLCL Filtersumiths32No ratings yet

- A Modified SEPIC Converter For High Power Factor Rectifier and Universal Input Voltage ApplicationsDocument12 pagesA Modified SEPIC Converter For High Power Factor Rectifier and Universal Input Voltage ApplicationsBritto TigerNo ratings yet

- Low Power Boost Converter For Portable Applications by Eddy Wells and Mark JordanDocument9 pagesLow Power Boost Converter For Portable Applications by Eddy Wells and Mark JordanberbouNo ratings yet

- SpeedAC NXT - Bagging - Operating Manual - Revision 1 11Document150 pagesSpeedAC NXT - Bagging - Operating Manual - Revision 1 11Nijam Jabbar100% (7)

- Slup 129Document11 pagesSlup 129Sameer NandanNo ratings yet

- AC DC AcDocument3 pagesAC DC AcPhani KumarNo ratings yet

- Buck ReportDocument9 pagesBuck ReportNaeem GulNo ratings yet

- Electronic Devices Experiment 4Document13 pagesElectronic Devices Experiment 4ArvinALNo ratings yet

- TP 1800 DC-DC Converter For Hybrid Electric Vehicle and EV ArrowTimesDocument7 pagesTP 1800 DC-DC Converter For Hybrid Electric Vehicle and EV ArrowTimespapipapii100% (1)

- High Efficiency Single Input Multiple Output DC DC ConverterDocument35 pagesHigh Efficiency Single Input Multiple Output DC DC ConverterArjunSasiNo ratings yet

- Double Frequency Buck ConverterDocument36 pagesDouble Frequency Buck ConverterSanthosh Guduru100% (1)

- DC Link CurrentDocument8 pagesDC Link CurrentsubbannaNo ratings yet

- A Zero-Voltage Switching Full-Bridge DC - DC ConverterDocument8 pagesA Zero-Voltage Switching Full-Bridge DC - DC Convertersuresh100% (1)

- Advanced HVDC TechnologiesDocument14 pagesAdvanced HVDC TechnologiesS Bharadwaj Reddy100% (1)

- Recent Advances in HVDC SystemsDocument4 pagesRecent Advances in HVDC SystemsvivekNo ratings yet

- Generalized Average Modeling of Dual ActiveDocument7 pagesGeneralized Average Modeling of Dual ActiveHarsh ChittoraNo ratings yet

- Bidirectional DC-DC Converter With Full-Bridge / Push-Pull Circuit For Automobile Electric Power SystemsDocument5 pagesBidirectional DC-DC Converter With Full-Bridge / Push-Pull Circuit For Automobile Electric Power SystemsPaulo UchihaNo ratings yet

- Report of Project 18pulseDocument6 pagesReport of Project 18pulsedhaval2430100% (1)

- A Network Theorem Dual to Miller's TheoremDocument5 pagesA Network Theorem Dual to Miller's TheoremSiddhant Jain0% (1)

- Multi LVL DC DC BoostDocument9 pagesMulti LVL DC DC BoostDurga PrathibhaNo ratings yet

- Full Wave Rectifier Guide: Circuit, Theory & UsesDocument7 pagesFull Wave Rectifier Guide: Circuit, Theory & UsesArun PratapNo ratings yet

- Solar Energy AbstractDocument2 pagesSolar Energy Abstractnikhil_mathur10No ratings yet

- SEPIC ConverterDocument16 pagesSEPIC ConverterDina GaranNo ratings yet

- Microwave Devices and Circuits Question BankDocument3 pagesMicrowave Devices and Circuits Question BankanupvasuNo ratings yet

- What Are The Advantages and Disadvantages of A Bi-Directional DC To A DC Converter?Document14 pagesWhat Are The Advantages and Disadvantages of A Bi-Directional DC To A DC Converter?BALAJINo ratings yet

- Lab 5 Diode As Rectifier BBN 10205 (Done)Document10 pagesLab 5 Diode As Rectifier BBN 10205 (Done)Zhamir ZhakwanNo ratings yet

- 04 0800 HVDC Plenary RashwanDocument24 pages04 0800 HVDC Plenary RashwanDante FilhoNo ratings yet

- Design and Simulate Sample and Hold CircuitDocument8 pagesDesign and Simulate Sample and Hold CircuitRen BurnettNo ratings yet

- A Six-Switch Seven-Level Triple-Boost InverterDocument6 pagesA Six-Switch Seven-Level Triple-Boost InverterKarthi KeyanNo ratings yet

- Modeling of DC DC Converter PDFDocument6 pagesModeling of DC DC Converter PDFVishal AryaNo ratings yet

- Photodiode vs Phototransistor: Key Differences (39Document5 pagesPhotodiode vs Phototransistor: Key Differences (39CladyNo ratings yet

- Ee460 Lab Manual 2006Document80 pagesEe460 Lab Manual 2006F0x123No ratings yet

- The Phase Control Circuit The TC787Document10 pagesThe Phase Control Circuit The TC787nansusanNo ratings yet

- A - Generalized - High - Gain - Multilevel - Inverter - For - Small - Scale - Solar - Photovoltaic - ApplicationsDocument15 pagesA - Generalized - High - Gain - Multilevel - Inverter - For - Small - Scale - Solar - Photovoltaic - ApplicationsJamal KhyatNo ratings yet

- Zig Zag Ipst05 - Paper044Document6 pagesZig Zag Ipst05 - Paper044brutusNo ratings yet

- Lab 5: Design Single Stage and Telescopic Differential AmplifiersDocument13 pagesLab 5: Design Single Stage and Telescopic Differential AmplifiersTamilinbaaNo ratings yet

- Boost ConverterDocument8 pagesBoost Converterhamza abdo mohamoudNo ratings yet

- Lab 6 LCS 078Document13 pagesLab 6 LCS 078Asad saeedNo ratings yet

- Study and Design, Simulation of PWM Based Buck Converter For Low Power ApplicationDocument17 pagesStudy and Design, Simulation of PWM Based Buck Converter For Low Power ApplicationIOSRjournalNo ratings yet

- EE309 Notes 07 PDFDocument4 pagesEE309 Notes 07 PDFbals123456100% (1)

- Eca Lab ManualDocument78 pagesEca Lab ManualNageswariah.MNo ratings yet

- Two Reaction Theory of Salient Pole Synchronous AlternatorDocument4 pagesTwo Reaction Theory of Salient Pole Synchronous AlternatorAngel Mae AlsuaNo ratings yet

- Translational System Transfer FunctionsDocument30 pagesTranslational System Transfer FunctionsRhizhailNo ratings yet

- Electrical Engineering Report on Substation TrainingDocument43 pagesElectrical Engineering Report on Substation TrainingALL IS WELLNo ratings yet

- Lab 4 Half Wave and Full WaveDocument8 pagesLab 4 Half Wave and Full WaveRashid Rind Rashid Rind100% (1)

- AC POWER WIRELESSLY BY HFDocument3 pagesAC POWER WIRELESSLY BY HFa d100% (1)

- Transient of R.C. CircuitDocument9 pagesTransient of R.C. CircuitArinder SinghNo ratings yet

- Power Electronic Module - Chapter 5Document36 pagesPower Electronic Module - Chapter 5jayxcellNo ratings yet

- Novel High Step-Up DC-DC Converter With Coupled-Inductor and Switched-Capacitor Technique For Sustainable Energy SystemDocument10 pagesNovel High Step-Up DC-DC Converter With Coupled-Inductor and Switched-Capacitor Technique For Sustainable Energy SystemAnonymous TIKXqq8Fa7No ratings yet

- Tugas BiohidrogenDocument6 pagesTugas BiohidrogenlestariNo ratings yet

- Ultra Step-Up DC-DC Converter Based On Three Windings Coupled InductorDocument6 pagesUltra Step-Up DC-DC Converter Based On Three Windings Coupled Inductorseyed mohsen SalehiNo ratings yet

- 9.eee Ijeee Two Phase Interleaved DC SumalathaDocument16 pages9.eee Ijeee Two Phase Interleaved DC Sumalathaiaset123No ratings yet

- Journal Jpe 19-3 1305793780Document11 pagesJournal Jpe 19-3 1305793780Ade safitraNo ratings yet

- Essence OF Indian Knoweldge BookDocument186 pagesEssence OF Indian Knoweldge BooknongdambaNo ratings yet

- HanDicrafts in IndiaDocument16 pagesHanDicrafts in Indiasumiths32No ratings yet

- Entrepreneurship and StartupDocument20 pagesEntrepreneurship and Startupsumiths32No ratings yet

- 10.25.14BASIC ELECTRICITY Part 1-Volts, Amps, Watts, Series, ParallelDocument24 pages10.25.14BASIC ELECTRICITY Part 1-Volts, Amps, Watts, Series, Parallelsumiths32No ratings yet

- 35 Handicrafts in IndiaDocument8 pages35 Handicrafts in Indiasumiths32No ratings yet

- D1 S1B - IKS For Human Culture - Civilisation Aug 17Document18 pagesD1 S1B - IKS For Human Culture - Civilisation Aug 17padmaNo ratings yet

- HanDicrafts in IndiaDocument16 pagesHanDicrafts in Indiasumiths32No ratings yet

- FULLTEXT01Document104 pagesFULLTEXT01tkcow519No ratings yet

- Saedi Et Al. - 2012 - Power Quality Enhancement in Autonomous Microgrid Operation Using Particle Swarm Optimization194 SynopsisDocument12 pagesSaedi Et Al. - 2012 - Power Quality Enhancement in Autonomous Microgrid Operation Using Particle Swarm Optimization194 Synopsissumiths32No ratings yet

- ProformaDocument1 pageProformasumiths32No ratings yet

- PSIM and MATLAB Based Simulation of PV Array For Enhance The Performance by Using MPPT AlgorithmDocument4 pagesPSIM and MATLAB Based Simulation of PV Array For Enhance The Performance by Using MPPT Algorithmsumiths32No ratings yet

- Sensorless Current Mode ControlDocument6 pagesSensorless Current Mode Controlsumiths32No ratings yet

- Connected Inverters With LCL FiltersDocument16 pagesConnected Inverters With LCL Filterssumiths32No ratings yet

- Survey of CascadeDocument10 pagesSurvey of Cascadesumiths32No ratings yet

- Saedi Et Al. - 2012 - Power Quality Enhancement in Autonomous Microgrid Operation Using Particle Swarm Optimization194 SynopsisDocument12 pagesSaedi Et Al. - 2012 - Power Quality Enhancement in Autonomous Microgrid Operation Using Particle Swarm Optimization194 Synopsissumiths32No ratings yet

- Dual-Buck Full-Bridge Inverter With Hysteresis Current Control (Journal)Document8 pagesDual-Buck Full-Bridge Inverter With Hysteresis Current Control (Journal)Minh LuanNo ratings yet

- Basic For PIC Microcontrollers PDFDocument172 pagesBasic For PIC Microcontrollers PDFMohammed Ahmad OsamaNo ratings yet

- A New Control Structure For Grid-Connected LCLDocument9 pagesA New Control Structure For Grid-Connected LCLsumiths32No ratings yet

- Mosfet Gate Driving CircuitDocument37 pagesMosfet Gate Driving Circuitkannanrk1984No ratings yet

- 01302341Document10 pages01302341sumiths32No ratings yet

- Sectional Views 1Document28 pagesSectional Views 1sumiths32No ratings yet

- A New Control Structure For Grid-Connected LCLDocument12 pagesA New Control Structure For Grid-Connected LCLsumiths32No ratings yet

- A Voltage-Controlled PFC Cuk Converter-BasedDocument7 pagesA Voltage-Controlled PFC Cuk Converter-BasedAthiesh KumarNo ratings yet

- CMP0193 SynopsisDocument6 pagesCMP0193 Synopsissumiths32No ratings yet

- A New Control Structure For Grid-Connected LCLDocument9 pagesA New Control Structure For Grid-Connected LCLsumiths32No ratings yet

- Wiring Diagram: 5-1. LayoutDocument7 pagesWiring Diagram: 5-1. LayoutLuisMiguelCalvoNo ratings yet

- Maintenance Manual LH 350 Flight Helmet: Confidential IndustryDocument18 pagesMaintenance Manual LH 350 Flight Helmet: Confidential Industrynelson vasquezNo ratings yet

- APC RS-600 UPS ManualDocument2 pagesAPC RS-600 UPS Manualsubir150% (2)

- Experiment No. 7 SensorsDocument8 pagesExperiment No. 7 SensorsJonelNo ratings yet

- Motor DeutzDocument80 pagesMotor DeutzJose vargasNo ratings yet

- TH-A35 TH-A32: DVD Digital Theater SystemDocument65 pagesTH-A35 TH-A32: DVD Digital Theater SystemEl Tio Del TamborNo ratings yet

- RT310i FULL MANUAL UK V005-Revied-1 PDFDocument23 pagesRT310i FULL MANUAL UK V005-Revied-1 PDFsekula_zrNo ratings yet

- Manual Pulidora 9 Milwaukee Serial B43CD15010643Document36 pagesManual Pulidora 9 Milwaukee Serial B43CD15010643M Vega Vega Mahecha0% (1)

- Catalogue 2016Document68 pagesCatalogue 2016Abenezer BirhanuNo ratings yet

- 8086 Instruction Sets ExplainedDocument4 pages8086 Instruction Sets ExplainedYaqeen MatheamNo ratings yet

- Overland ConveyorDocument4 pagesOverland ConveyorRAUL PEREZ NEGREIROSNo ratings yet

- Calculating Conductor Impedance for a 3-Phase Pole ConfigurationDocument12 pagesCalculating Conductor Impedance for a 3-Phase Pole ConfigurationJonatan Lopez RodriguezNo ratings yet

- Design and Analysis of Threaded Fasteners and JointsDocument41 pagesDesign and Analysis of Threaded Fasteners and JointsRa Balamurugan67% (3)

- 53D - Abvolt - Digital Micro-Ohm MeterDocument6 pages53D - Abvolt - Digital Micro-Ohm Meterilesh shahNo ratings yet

- Panasonic Blueray DMP BDT100Document48 pagesPanasonic Blueray DMP BDT100gepetordi2No ratings yet

- 2.4 Precaution of Usage For Anti Backlash Spur GearsDocument2 pages2.4 Precaution of Usage For Anti Backlash Spur Gearsnay hlaing SoeNo ratings yet

- DC circuit supplementary protectors guideDocument4 pagesDC circuit supplementary protectors guideovidiupatruNo ratings yet

- Duoscreedgb 4vanaf1 10 2010Document16 pagesDuoscreedgb 4vanaf1 10 2010Sandeep YadavNo ratings yet

- 48 50tj-2wDocument64 pages48 50tj-2wsclstc89No ratings yet

- Driving Controls Guide for FamiliarisationDocument175 pagesDriving Controls Guide for FamiliarisationpetarstarNo ratings yet

- HSD DoorhanDocument48 pagesHSD DoorhanJokerNo ratings yet

- MTRL MasterDocument386 pagesMTRL MasterSourav MaitraNo ratings yet

- All Wiring Diagrams For Nissan Sentra CA 2002Document63 pagesAll Wiring Diagrams For Nissan Sentra CA 2002tellossaposNo ratings yet