Professional Documents

Culture Documents

Smart Antennas-Beamforming

Uploaded by

SriramOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Smart Antennas-Beamforming

Uploaded by

SriramCopyright:

Available Formats

Smart AntennasBeamforming There is an ever-increasing demand on mobile wireless operators to provide voice and high-speed data services.

At the same time, these operators want to support more users per basestation to reduce overall network costs and make the services affordable to subscribers. As a result, wireless systems that enable higher data rates and higher capacities are a pressing need. Interference Limited Systems Unfortunately, because the available broadcast spectrum is limited, attempts to increase traffic within a fixed bandwidth create more interference in the system and degrade the signal quality. In particular, when omni-directional antennas (see Figure 1) are used at the basestation, the transmission/reception of each users signal becomes a source of interference to other users located in the same cell, making the overall system interference limited. An effective way to reduce this type of interference is to split up the cell into multiple sectors and use sectorized antennas, as shown in Figure 1. Figure 1. Non-Smart Antennas System

Smart Antenna TechnologyBeamforming Smart antenna technology offers a significantly improved solution to reduce interference levels and improve the system capacity. With this technology, each users signal is transmitted and received by the basestation only in the direction of that particular user. This drastically reduces the overall interference in the system. A smart antenna system, as shown in Figure 2, consists of an array of antennas that together direct different transmission/reception beams toward each user in the system. This method of transmission and reception is called beamforming and is made possible through smart (advanced) signal processing at the baseband. Figure 2. Smart Antenna SystemBeamforming

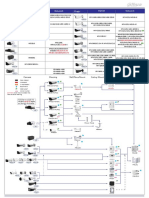

In beamforming, each users signal is multiplied with complex weights that adjust the magnitude and phase of the signal to and from each antenna. This causes the output from the array of antennas to form a transmit/receive beam in the desired direction and minimizes the output in other directions. Switched and Adaptive Beamforming If the complex weights are selected from a library of weights that form beams in specific, predetermined directions, the process is called switched beamforming. Here, the basestation basically switches between the different beams based on the received signal strength measurements. On the other hand, if the weights are computed and adaptively updated in real time, the process is called adaptive beamforming. Through adaptive beamforming, the basestation can form narrower beams towards the desired user and nulls towards interfering users, considerably improving the signal-to-interference-plus-noise ratio. Altera Adaptive Beamforming Implementation The high-performance digital signal processing (DSP) blocks, embedded Nios II processors, and logic elements (LEs) of Alteras Stratix series FPGAs make them ideal for adaptive beamforming applications. This section describes the Altera implementation of a Rake-Beamformer (also known as two-dimensional Rake) structure that performs joint space-time processing. As illustrated in Figure 3, the signal from each receive antenna is first down converted to baseband, processed by the matched filtermultipath estimator, and accordingly assigned to different Rake fingers. Figure 3. Adaptive Beamforming with Alteras Stratix Series FPGAs

Notes: 1. DDC: digital down converter 2. MRC: maximal ratio combining 3. CORDIC: coordinate rotation digital computer

4. QRD: QR decomposition The beamforming unit on each Rake finger then calculates the corresponding beamformer weights and channel estimate using the pilot symbols that have been transmitted through the dedicated physical control channel (DPCCH). The QRD-based recursive least squares (RLS) algorithm is selected as the weight update algorithm for its fast convergence and good numerical properties. The updated beamformer weights are then used for multiplication with the data that has been transmitted through the dedicated physical data channel (DPDCH). Maximal ratio combining (MRC) of the signals from all fingers is then performed to yield the final soft estimate of the DPDCH data. The beamforming unit implementation on each Rake finger is further elaborated below. DSP Blocks for Complex Weight Multiplication The application of complex weights to the signals from different antennas involves complex multiplications that map well onto the embedded DSP blocks available in Stratix series FPGAs. Each DSP block has a number of multipliers, followed by adder/subtractor/accumulators, in addition to registers for pipelining. With these features, Stratix series FPGAs can efficiently implement complex multiplications and reduce the amount of overall logic and routing required in beamforming designs. CORDIC-Based QR Decomposition The QRD-RLS weights update algorithm involves decomposing the input signal matrix Y into QR, where Q is a unitary matrix and R is an upper triangular matrix. This is achieved using a triangular systolic array of CORDIC blocks, as shown in Figure 4. Each CORDIC block operates in either vectoring or rotating modes and performs a series of micro rotations through simple shift and add/subtract operations and can run at speeds of 300 MHz. Figure 4. Triangular Systolic Array Example for CORDIC-Based QRD-RLS

The R matrix and u vector (transformed reference signal vector d) are recursively updated for every new row of inputs entering the triangular array. The triangular systolic array can be further mapped into a

linear array with reduced number of time-shared CORDIC blocksas illustrated in Figure 4providing a tradeoff between resource consumption and throughput. Back Substitution for Weights Using Nios II Processors The final beamformer weights vector w is related to the R and u outputs of the triangular array as Rw=u. Because R is an upper triangular matrix, w can be solved using a procedure called back substitution that can be implemented in software on the flexible embedded Nios II processor. The Nios II soft processor can also utilize custom instructions for hardware acceleration of program code. For an example eight antennas system, the beamformer weights for a Rake finger can be solved via back substitution in approximately 0.2 ms using the Nios II processor operating at 100 MHz. The computation time can be lowered to 3 s by implementing the back substitution on a hardware peripheral controlled by the Nios II processor. Moreover, the Nios II processor offers a flexible platform to implement other adaptive weight update algorithms such as least mean squares (LMS) and normalized LMS. The Altera Advantage for Beamforming Processing Speed Smart antenna technology requires high processing bandwidth, with computational speeds approaching several billion multiply and accumulate (MAC) operations per second. Such computationally demanding applications quickly exhaust the processing capabilities of digital signal processors. Altera FPGAs, with enhanced DSP blocks and TriMatrix memory, provide throughputs in excess of 50 GMACs, offering a high-performance platform for beamforming applications. Flexibility There are a number of beamforming architectures and adaptive algorithms that provide good performance under different scenarios such as transmit-receive adaptive beamforming and transmit-receive switched beamforming. With embedded Nios II processors and easy-to-use development tools such as DSP Builder and SOPC Builder, Altera FPGAs offer a high degree of flexibility in implementing various adaptive signal processing algorithms. Lower Risk The standards for next-generation networks are continuously evolving, and this creates an element of risk for beamforming ASIC implementation. Transmit beamforming, for example, utilizes the feedback from the mobile terminals. The number of bits provided for feedback in the standards can determine the beamforming algorithm that is used at the basestation. Moreover, future basestations are likely to support transmit diversity including space-time coding and multiple-input multiple-output (MIMO) technology. Because Altera FPGAs are remotely upgradeable, they reduce the risk involved with designing for evolving industry standards while providing the option for the gradual deployment of additional transmit diversity schemes. Cost Reduction Path Mobile wireless service providers would likely deploy smart antennas technology initially at certain hot spots such as densely populated urban areaswhere there is more demand for high-speed wireless

data services. The high NRE costs and long development cycles associated with ASICs cannot be justified for such low volume requirements. Along with a significant time-to-market advantage over ASICs, Altera's HardCopy ASICs offer a seamless migration process that supports the high-density Stratix series FPGAs and can offer up to 70 percent cost reduction for relatively low minimum order quantities (MOQs).

You might also like

- Circuit Theory 2014 - Apr MayDocument6 pagesCircuit Theory 2014 - Apr MaySriramNo ratings yet

- Wireless Communication - EC 2401 - I - Answer KeyDocument9 pagesWireless Communication - EC 2401 - I - Answer KeySriramNo ratings yet

- EC8661 VLSI Design LaboratoryDocument53 pagesEC8661 VLSI Design LaboratorySriram100% (4)

- MeasurementsDocument12 pagesMeasurementsSriramNo ratings yet

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- What Determines The Color of An LED?: SemiconductingDocument1 pageWhat Determines The Color of An LED?: SemiconductingSriramNo ratings yet

- EC6612 - VLSI Design Laboratory ManualDocument39 pagesEC6612 - VLSI Design Laboratory ManualSriramNo ratings yet

- 2014 - Apr May PDFDocument4 pages2014 - Apr May PDFSriramNo ratings yet

- VLSI Design Lab EC-6612-nDocument58 pagesVLSI Design Lab EC-6612-nSriramNo ratings yet

- EC6702Document2 pagesEC6702SriramNo ratings yet

- Design Entry and Simulation of Sequential CircuitsDocument7 pagesDesign Entry and Simulation of Sequential CircuitsSriramNo ratings yet

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- Data Path Circuits - EC6601Document10 pagesData Path Circuits - EC6601SriramNo ratings yet

- Principles of Management: Lesson PlanDocument23 pagesPrinciples of Management: Lesson PlanSriram100% (1)

- Sensors: SL - N o Application Sensor Example PriceDocument6 pagesSensors: SL - N o Application Sensor Example PriceSriramNo ratings yet

- Ec 6501Document1 pageEc 6501SriramNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- DSP WorkshopDocument2 pagesDSP WorkshopSriramNo ratings yet

- SEMESTER Requirements Lab EquipmentDocument29 pagesSEMESTER Requirements Lab EquipmentSriramNo ratings yet

- Ec2357 - Vlsi Design LaboratoryDocument45 pagesEc2357 - Vlsi Design LaboratorySriramNo ratings yet

- Concept MapDocument18 pagesConcept MapSriramNo ratings yet

- ECE Department Course DetailsDocument151 pagesECE Department Course DetailsSriramNo ratings yet

- Verilog Course ManualDocument60 pagesVerilog Course ManualSriramNo ratings yet

- Ece 2013Document14 pagesEce 2013SriramNo ratings yet

- VerilogDocument12 pagesVerilogSriramNo ratings yet

- Ece 2008Document27 pagesEce 2008SriramNo ratings yet

- Analog DesignDocument4 pagesAnalog DesignSriramNo ratings yet

- Verilog Lab ProgramsDocument25 pagesVerilog Lab ProgramsSriramNo ratings yet

- Kalasalingam University ECE302 Analog Communication Question BankDocument6 pagesKalasalingam University ECE302 Analog Communication Question BankSriramNo ratings yet

- VerilogDocument12 pagesVerilogSriramNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- How Does Marijuana Affect The BrainDocument3 pagesHow Does Marijuana Affect The BrainWanNurAtikahNo ratings yet

- Absence Makes The Heart Grow FonderDocument27 pagesAbsence Makes The Heart Grow FondereljhunNo ratings yet

- Director's Report Highlights Record Wheat Production in IndiaDocument80 pagesDirector's Report Highlights Record Wheat Production in Indiakamlesh tiwariNo ratings yet

- Jual Sokkia SET 350X Total Station - Harga, Spesifikasi Dan ReviewDocument5 pagesJual Sokkia SET 350X Total Station - Harga, Spesifikasi Dan Reviewbramsalwa2676No ratings yet

- Maya Keyboard ShortcutsDocument0 pagesMaya Keyboard ShortcutsDaryl Gomez TimatimNo ratings yet

- Animal Names in English and IndonesianDocument7 pagesAnimal Names in English and IndonesianAndi KurniawanNo ratings yet

- YOKOGAWADocument16 pagesYOKOGAWADavide ContiNo ratings yet

- Celiac DiseaseDocument14 pagesCeliac Diseaseapi-355698448100% (1)

- Indian Oil Corporation Limited: Bhubaneswar Divisional OfficeDocument3 pagesIndian Oil Corporation Limited: Bhubaneswar Divisional OfficeBinay SahooNo ratings yet

- Elements of Plane and Spherical Trigonometry With Numerous Practical Problems - Horatio N. RobinsonDocument228 pagesElements of Plane and Spherical Trigonometry With Numerous Practical Problems - Horatio N. RobinsonjorgeNo ratings yet

- Kingspan Spectrum™: Premium Organic Coating SystemDocument4 pagesKingspan Spectrum™: Premium Organic Coating SystemNikolaNo ratings yet

- Ford 1982 3.8L V6Document22 pagesFord 1982 3.8L V6sc100% (1)

- Belden CatalogDocument24 pagesBelden CatalogMani MaranNo ratings yet

- Chapter 4 Cost MinimizationDocument6 pagesChapter 4 Cost MinimizationXavier Hetsel Ortega BarraganNo ratings yet

- GT ĐỀ 04Document39 pagesGT ĐỀ 04Cao Đức HuyNo ratings yet

- PDLAMMPS - made easy: An introductionDocument8 pagesPDLAMMPS - made easy: An introductionSaeed AbdNo ratings yet

- CE 581 Reinforced Concrete Structures: Lecture 4: Axial LoadingDocument36 pagesCE 581 Reinforced Concrete Structures: Lecture 4: Axial LoadingCelil OrakNo ratings yet

- Lesson 1 - Simple StressDocument5 pagesLesson 1 - Simple StressJohn Philip NadalNo ratings yet

- Overlord - Volume 01 - The Undead KingDocument223 pagesOverlord - Volume 01 - The Undead KingPaulo FordheinzNo ratings yet

- NitrocelluloseDocument7 pagesNitrocellulosejumpupdnbdjNo ratings yet

- Configuration & Options List: 30Xw0452 1752 Water Cooled Liquid ChillerDocument22 pagesConfiguration & Options List: 30Xw0452 1752 Water Cooled Liquid ChillerOctavio Farid Rossi YumhaNo ratings yet

- Unit 4.2Document45 pagesUnit 4.2Gundrathi Narendra GoudNo ratings yet

- Dahua Pfa130 e Korisnicko Uputstvo EngleskiDocument5 pagesDahua Pfa130 e Korisnicko Uputstvo EngleskiSaša CucakNo ratings yet

- G 26 Building Using ETABS 1673077361Document68 pagesG 26 Building Using ETABS 1673077361md hussainNo ratings yet

- Screenshot 2023-01-03 at 9.25.34 AM PDFDocument109 pagesScreenshot 2023-01-03 at 9.25.34 AM PDFAzri ZakwanNo ratings yet

- Mfz-Odv065r15j DS 1-0-0 PDFDocument1 pageMfz-Odv065r15j DS 1-0-0 PDFelxsoonNo ratings yet

- Gene Regulation: Made By: Diana Alhazzaa Massah AlhazzaaDocument17 pagesGene Regulation: Made By: Diana Alhazzaa Massah AlhazzaaAmora HZzNo ratings yet

- Three Bucket Method & Food ServiceDocument4 pagesThree Bucket Method & Food Servicerose zandrea demasisNo ratings yet

- Mahle KFWA MAIN Data SheetDocument4 pagesMahle KFWA MAIN Data SheetRudnikNo ratings yet

- CV1000 CV2000 CV3000 Ice Cube Machines SpecsDocument12 pagesCV1000 CV2000 CV3000 Ice Cube Machines SpecsAriel Godoy100% (1)