Professional Documents

Culture Documents

1840

Uploaded by

Deepa DevarajCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1840

Uploaded by

Deepa DevarajCopyright:

Available Formats

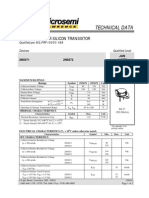

HS-1840ARH

Data Sheet August 1999 File Number 4355.1

Rad-Hard 16 Channel CMOS Analog Multiplexer with High-Z Analog Input Protection

The HS-1840ARH is a radiation hardened, monolithic 16 channel multiplexer constructed with the Intersil Rad-Hard Silicon Gate, bonded wafer, Dielectric Isolation process. It is designed to provide a high input impedance to the analog source if device power fails (open), or the analog signal voltage inadvertently exceeds the supply by up to 35V, regardless of whether the device is powered on or off. Excellent for use in redundant applications, since the secondary device can be operated in a standby unpowered mode affording no additional power drain. More significantly, a very high impedance exists between the active and inactive devices preventing any interaction. One of sixteen channel selection is controlled by a 4-bit binary address plus an Enable-Inhibit input which conveniently controls the ON/OFF operation of several multiplexers in a system. All inputs have electrostatic discharge protection. The HS-1840ARH is processed and screened in full compliance with MIL-PRF-38535 and QML standards. The device is available in a 28 lead SBDIP and a 28 lead Ceramic Flatpack. Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed here must be used when ordering. Detailed Electrical Specifications for these devices are contained in SMD 5962-95630. A hot-link is provided on our homepage for downloading. http://www.intersil.com/spacedefense/space.htm

Features

Electrically Screened to SMD # 5962-95630 QML Qualified per MIL-PRF-38535 Requirements Pin-to-Pin for Intersils HS-1840RH and HS-1840/883S Improved Radiation Performance - Gamma Dose () 3 x 105RAD(Si) Improved rDS(ON) Linearity Improved Access Time 1.5s (Max) Over Temp and Post Rad High Analog Input Impedance 500M During Power Loss (Open) 35V Input Over Voltage Protection (Power On or Off) Dielectrically Isolated Device Islands Excellent in Hi-Rel Redundant Systems Break-Before-Make Switching No Latch-Up

Ordering Information

ORDERING NUMBER 5962F9563002QXC 5962F9563002QYC 5962F9563002V9A 5962F9563002VXC 5962F9563002VYC INTERNAL MKT. NUMBER HS1-1840ARH-8 HS9-1840ARH-8 HS0-1840ARH-Q HS1-1840ARH-Q HS9-1840ARH-Q TEMP. RANGE (oC) -55 to 125 -55 to 125 25 -55 to 125 -55 to 125 -55 to 125 -55 to 125

HS1-1840ARH/PROTO HS1-1840ARH/PROTO HS9-1840ARH/PROTO HS9-1840ARH/PROTO

Pinouts

HS1-1840ARH (SBDIP) CDIP2-T28 TOP VIEW

+VS 1 NC 2 NC 3 IN 16 4 IN 15 5 IN 14 6 IN 13 7 IN 12 8 IN 11 9 IN 10 10 IN 9 11 GND 12 (+5VS) VREF 13 ADDR A3 14 28 OUT 27 -VS 26 IN 8 25 IN 7 24 IN 6 23 IN 5 22 IN 4 21 IN 3 20 IN 2 19 IN 1 18 ENABLE 17 ADDR A0 16 ADDR A1 15 ADDR A2 +VS NC NC IN 16 IN 15 IN 14 IN 13 IN 12 IN 11 IN 10 IN 9 GND (+5VS) VREF ADDR A3

HS9-1840ARH (FLATPACK) CDFP3-F28 TOP VIEW

1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 OUT -VS IN 8 IN 7 IN 6 IN 5 IN 4 IN 3 IN 2 IN 1 ENABLE ADDR A0 ADDR A1 ADDR A2

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2002. All Rights Reserved

HS-1840ARH Functional Diagram

IN 1 1 P

A0

A1 DIGITAL ADDRESS A2 OUT

A3

EN

16

P IN 16

ADDRESS INPUT BUFFER AND LEVEL SHIFTER

DECODERS

MULTIPLEX SWITCHES

TRUTH TABLE A3 X L L L L L L L L H H H H H H H H A2 X L L L L H H H H L L L L H H H H A1 X L L H H L L H H L L H H L L H H A0 X L H L H L H L H L H L H L H L H EN H L L L L L L L L L L L L L L L L ON CHANNEL None 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

HS-1840ARH Burn-In/Life Test Circuits

R +VS R 1 2 3 4 5 6 7 8 9 10 GND F4 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 F3 F1 F2 F5 GND VR R -VS

+VS R

1 2 3 4 5 6 7 8 9 10 11 12 13 14

28 27 26 25 24 23 22 21 20 19 18 17 16 15

R -VS R

NOTES: VS+ = +15.5V 0.5V, VS- = -15.5V 0.5V. R = 1k 5%. C1 = C2 = 0.01F 10%, 1 each per socket, minimum. D1 = D2 = 1N4002, 1 each per board, minimum. Input Signals: square wave, 50% duty cycle, 0V to 15V peak 10%. F1 = 100kHz; F2 = F1/2; F3 = F1/4; F4 = F1/8; F5 = F1/16. FIGURE 1. DYNAMIC BURN-IN AND LIFE TEST CIRCUIT NOTES: 1. The above test circuits are utilized for all package types. 2. The Dynamic Test Circuit is utilized for all life testing.

NOTES: R = 1k 5%, 1/4W. C1 = C2 = 0.01F minimum, 1 each per socket, minimum. VS+ = 15.5V 0.5V, VS- = -15.5V 0.5V, VR = 15.5 0.5V. FIGURE 2. STATIC BURN-IN TEST CIRCUIT

Irradiation Circuit

HS-1840ARH

+15V NC NC +1V

1 2 3 4 5 6 7 8 9 10 11 12 13 14

28 27 26 25 24 23 22 21 20 19 18 17 16 15 -15V 1k

+5V

NOTE: 3. All irradiation testing is performed in the 28 lead CERDIP package.

HS-1840ARH Die Characteristics

DIE DIMENSIONS: (2820m x 4080m x 483m 25.4m) 111 mils x 161 mils x 19 mils 1 mil INTERFACE MATERIALS: Glassivation: Type: PSG (Phosphorus Silicon Glass) Thickness: 8.0k 1k Top Metallization: Type: AlSiCu Thickness: 16.0k 2k Backside Finish: Silicon ASSEMBLY RELATED INFORMATION: Substrate Potential: Unbiased (DI) ADDITIONAL INFORMATION: Worst Case Current Density: Modified SEM Transistor Count: 407 Process: Radiation Hardened Silicon Gate, Bonded Wafer, Dielectric Isolation

Metallization Mask Layout

HS-1840ARH

IN7 IN6 IN5 IN4 IN3 IN2 IN1

IN8 ENABLE

A0 -V

A1

OUT

A2

+V

A3

VREF IN16 GND

IN15

IN14

IN13

IN12

IN11

IN10

IN9

This datasheet has been download from: www.datasheetcatalog.com Datasheets for electronics components.

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Spec - Dappro 16Mb SRAM - 5V - QFP68Document23 pagesSpec - Dappro 16Mb SRAM - 5V - QFP68Deepa DevarajNo ratings yet

- 2N5672Document4 pages2N5672Deepa DevarajNo ratings yet

- Support Component List: Components For Spacecraft ElectronicsDocument22 pagesSupport Component List: Components For Spacecraft ElectronicsDeepa DevarajNo ratings yet

- Spacewire PCBDocument1 pageSpacewire PCBDeepa DevarajNo ratings yet

- 2N5672Document13 pages2N5672Deepa DevarajNo ratings yet

- Vehicle Rto Exam FaqDocument1 pageVehicle Rto Exam FaqDeepa DevarajNo ratings yet

- EC Announces Dates For Polls in Five StatesDocument3 pagesEC Announces Dates For Polls in Five StatesDeepa DevarajNo ratings yet

- Standard Wire Gauge ListDocument3 pagesStandard Wire Gauge ListDeepa DevarajNo ratings yet

- Recipes From Mum's Kitchen - Mutton BiryaniDocument3 pagesRecipes From Mum's Kitchen - Mutton BiryaniDeepa DevarajNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDeepa DevarajNo ratings yet

- Systems Advantages of 1553Document8 pagesSystems Advantages of 1553Deepa DevarajNo ratings yet

- NPN 2N5671 - 2N5672: H I G H C U R R e N T F A S T S W I T C H I N G A P P L I C A T I o N SDocument0 pagesNPN 2N5671 - 2N5672: H I G H C U R R e N T F A S T S W I T C H I N G A P P L I C A T I o N SDeepa DevarajNo ratings yet

- Results PO 2013Document22 pagesResults PO 2013Deepa DevarajNo ratings yet

- Tina Ti Spice ModelsDocument17 pagesTina Ti Spice Modelsdragos_bondNo ratings yet

- 2n7389 Irhf9130Document8 pages2n7389 Irhf9130Deepa DevarajNo ratings yet

- 2N6849 LP PMOS IR For Neg SupplyDocument7 pages2N6849 LP PMOS IR For Neg SupplyDeepa DevarajNo ratings yet

- 2N3792Document4 pages2N3792Deepa DevarajNo ratings yet

- 2N6849Document2 pages2N6849Deepa DevarajNo ratings yet

- 2N3700UBDocument0 pages2N3700UBDeepa DevarajNo ratings yet

- Technical Data: PNP High Power Silicon TransistorDocument3 pagesTechnical Data: PNP High Power Silicon TransistorDeepa DevarajNo ratings yet

- 2 N 5153Document3 pages2 N 5153Deepa DevarajNo ratings yet

- Technical Data: NPN High Power Silicon TransistorDocument2 pagesTechnical Data: NPN High Power Silicon TransistorDeepa DevarajNo ratings yet

- 2N3792Document4 pages2N3792Deepa DevarajNo ratings yet

- 2N3637Document0 pages2N3637Deepa DevarajNo ratings yet

- 1 N 5822Document3 pages1 N 5822Deepa DevarajNo ratings yet

- 2N3019Document0 pages2N3019Deepa DevarajNo ratings yet

- 1 N 5822Document3 pages1 N 5822Deepa DevarajNo ratings yet

- Description Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDocument0 pagesDescription Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDeepa DevarajNo ratings yet

- Diodo Shotky 1n5817-5819Document9 pagesDiodo Shotky 1n5817-5819Alejandro Esteban VilaNo ratings yet

- Description Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDocument0 pagesDescription Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDeepa DevarajNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Digital Letter Box Project ReportDocument7 pagesDigital Letter Box Project ReportMoyammir HaiderNo ratings yet

- LCA Lab Report 12Document12 pagesLCA Lab Report 12ayleeNo ratings yet

- AD8232Document28 pagesAD8232محمد نNo ratings yet

- Basics of Electrical Engineering Assignment SolutionsDocument5 pagesBasics of Electrical Engineering Assignment SolutionsKishuxyzNo ratings yet

- Power Filter Options For The FPD-Link Interfaces in TRAVEO™ T2G FamilyDocument15 pagesPower Filter Options For The FPD-Link Interfaces in TRAVEO™ T2G Familygshgeje hehjwjeNo ratings yet

- A Spice Model For The Ideal TransformerDocument2 pagesA Spice Model For The Ideal TransformerCristian LiviuNo ratings yet

- Vlsi Modeling and Design: Dr. Mohammed M. FaragDocument27 pagesVlsi Modeling and Design: Dr. Mohammed M. FaragAshar AsifNo ratings yet

- MixedDocument173 pagesMixedJean BookNo ratings yet

- System On Chip Architecture Design Lecture6Document16 pagesSystem On Chip Architecture Design Lecture6Thi NguyenNo ratings yet

- Pojacalo ManualDocument4 pagesPojacalo ManualServis ChipoNo ratings yet

- Power Dissipation ExamplesDocument4 pagesPower Dissipation ExamplesEhab ZaghloolNo ratings yet

- Load Line and Q-PointDocument3 pagesLoad Line and Q-PointRavi Kanth M NNo ratings yet

- Courses in Electrical Engineering: Digital Electronics Chapter Six: Combinatory LogicDocument29 pagesCourses in Electrical Engineering: Digital Electronics Chapter Six: Combinatory LogicNGOUNENo ratings yet

- Digital Voltmeters (DVMS) : 2Nd Slide 1Document13 pagesDigital Voltmeters (DVMS) : 2Nd Slide 1Simbiex AwpNo ratings yet

- ELEXDocument14 pagesELEXHazel Grace del MonteNo ratings yet

- Section C - Digital MCQ3Document3 pagesSection C - Digital MCQ3viki awsacNo ratings yet

- Logic Gates - Make Decisions with Electronic CircuitsDocument13 pagesLogic Gates - Make Decisions with Electronic CircuitsbanaliaNo ratings yet

- Service Manual 800RBDocument21 pagesService Manual 800RBCodinasound CaNo ratings yet

- LJ & Le DS6258BC-03Document24 pagesLJ & Le DS6258BC-03DevendraSharmaNo ratings yet

- 2 MarksDocument25 pages2 MarksAnnapurna CheruvuNo ratings yet

- HIP4082IBZ A Half-Bridge FET Gate DriveDocument5 pagesHIP4082IBZ A Half-Bridge FET Gate DrivejackNo ratings yet

- DNSD 339 FDocument2 pagesDNSD 339 FrajeshdaveNo ratings yet

- KTMICRODocument28 pagesKTMICROthiago garofaloNo ratings yet

- CO-PO Analog ElectronicsDocument3 pagesCO-PO Analog ElectronicsPrabhu KumarNo ratings yet

- Memories CompleteDocument51 pagesMemories Completeyeswanth chowdary nidamanuriNo ratings yet

- SFH551 1-1vDocument6 pagesSFH551 1-1v1earthling2No ratings yet

- Ci Control Velocidad LavadoraDocument12 pagesCi Control Velocidad LavadorailoalNo ratings yet

- Amplifier Design DocumentDocument38 pagesAmplifier Design DocumentMrToedeNo ratings yet

- Designing With Xc9500 CPLDS: Interconnect Within Function BlocksDocument8 pagesDesigning With Xc9500 CPLDS: Interconnect Within Function BlocksvenkateshNo ratings yet

- Introduction of Logic Gates PDFDocument4 pagesIntroduction of Logic Gates PDFcompiler&automataNo ratings yet