Professional Documents

Culture Documents

8085 Microprocessor Architecture, Pin Diagram

Uploaded by

Sachin JaysenanOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8085 Microprocessor Architecture, Pin Diagram

Uploaded by

Sachin JaysenanCopyright:

Available Formats

2.

8085 Architecture, Pin diagram & Features

18 July 2013

Module 1

Basics of 8085

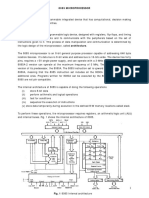

Basic 8085 microprocessor architecture and its functional blocks. 8085 microprocessor IC pin outs and signals, address, data and control buses. 8085 features

Prepared By AJIT SARAF

Working of small organization

INTA INTR

RST 6.5 TRAP RST 5.5 RST 7.5

SID

SOD

Interrupt control

Serial I/O control

8-Bit internal data bus

(8) (8) (8) (8) (8) (8)

Accumulator

Temporary register

Flag register

Instruction register

Instruction Decoder And Machine Cycle encoder

W Reg Z Reg B Reg C Reg D Reg E Reg H Reg L Reg

Stack pointer (16) Program Counter (16) Incrementer/ Decrementer Address latch

Arithmetic Logic Unit (ALU)

POWER SUPPLY

+5V GND

X1

CLK IN

Simple microprocessor based system

X2

Timing and Control

CLK

GEN

CONTROL

STATUS

DMA

RESET

CLK OUT READY

RD WR

ALE S0

S1 IO/M

HOLD

Address buffer

A15 A8 Address bus

Address/Data buffer

AD7 AD0 Data / Address bus

RESETIN HLDA RESET OUT

Architecture of 8085

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

Functional blocks of 8085

Registers Arithmetic and Logic Unit Instruction decoder and machine cycle encoder Address buffer Address / Data buffer. Incrementer / Decrementer Address Latch. Timing and control circuitry. Interrupt control. Serial I/O control.

Registers

General Purpose Registers (Scratchpad registers) ( B, C, D, E, H, L ) Temporary Registers. 1) Temporary data register. 2) W and Z registers Special Purpose Registers. 1) Accumulator (A) 2) Flag registers. 3) Instruction register. 4) Program Counter (PC). 5) Stack Pointer (SP).

General Purpose Registers

B, C, D, E, H, L 8-bit general purpose registers. Used as a separate 8-bit or 16-bit registers as BC, DE or HL pair. Scratchpad registers used to store data. To store and read data from these registers bus access is not required. It is an internal operation. It provides an efficient way to store intermediate results.

Temporary Registers

1) Temporary data register. One of the Input of ALU. Not accessible for user. Internally used for execution of most of the arithmetic and logical instructions. 2) W and Z registers Used to hold 8-bit data during execution of some instructions. Not available for programmer. 8085 uses them internally. Used in CALL and XCHG instructions.

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

Accumulator

8-bit Special Purpose Register. It is a multipurpose register. Accumulate the result. One of the input to the ALU. Extensively used in arithmetic, logical, load and store as well as input/output operations. It holds operands & result of ALU operations.

Flag Register

Flag is nothing but group of flipflops. 8-bit Register. It provides status of the result to the user. User can access this register. Flag get affected only when operation is to be performed in ALU.

Flag Register

D7 D6 D5 D4 D3 D2 D1 D0 S Z AC P CY

Instruction Register

Used to hold operation code of the current instruction. User can read content of Instruction register. The instruction register is loaded during the opcode fetch cycle. This register is only activated when instruction code or opcode is available for programmer use.

S-Sign Flag. Z-Zero Flag. AC-Auxiliary Carry Flag. P-Parity Flag. CY-Carry Flag.

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

Program Counter

16-bit register used for execution of program. Program is a series of instructions stored in the memory. These instructions must be executed in a proper order to get the correct result. This sequence of instruction execution is monitored by the program counter. It stores address of the next instruction to be fetched and executed. This register always points to address of program memory where the next instruction is to be fetched and executed so it acts as a memory pointer. When reset is activated PC is set to the location 0000H (Starting location of ROM).

Stack Pointer

Stack is a reserved are of the memory in the RAM. Before going to the subroutine program next instruction location (Return address) is stored in stack. The memory address of the stack area is given by a special register called the stack pointer. 16-bit register used to define the stack starting address. It points to the current stack location. It always points to the top of the stack. Usually stack operations are 2 byte operations. Stack operates in LIFO (Last In First Out).

Arithmetic Logic Unit (ALU)

It is multi-operation combinational logic circuit.. It performs arithmetic and logical operations. It is not available to the user. It has 2 inputs, Accumulator & Temp. register. The ALUs single output is connected to the internal data bus. Operation to be performed on the 2 inputs is selected by control logic. ALU can perform : Addition, Subtraction, AND, OR, XOR, Complement, Shift right, Shift left, Increment and Decrement.

Instruction Decoder

It accepts bit pattern from instruction register decodes it and sends decoded information to the timing and control circuit. It is 8:256 Decoder.

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

Address Buffer

8-bit unidirectional buffer. It is used to drive external high order address bus (A15 - A8). Used to tri-state the high order address bus under certain conditions such as reset, hold, halt and when address lines are not in use.

Address/Data Buffer

8-bit bi-directional buffer. It is used to drive multiplexed address/data bus, i.e. low order address bus (A7 A0) and data bus (D7 D0). Used to tri-state the multiplexed address/data bus under certain conditions such as reset, hold, halt and when address lines are not in use

Incrementer/Decrementer Address Latch

16-bit register used to increment or decrement the contents of program counter or stack pointer.

Interrupt Control

The occurrence of special condition is referred to as interrupt. This block has five interrupt request inputs such as TRAP, RST7.5, RST6.5, RST5.5, INTR and one acknowledge signal INTA.

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

Serial I/O Control

For data transmission over long distance and communication with cassette tapes or a CRT terminal, serial data transmission is used to reduce the cost of cabling. For serial data transmission SID and SOD pins are used.

Timing and Control Circuitry

Control circuitry is responsible for all the operations, so it controls all the blocks of 8085. Control circuitry and hence the operations in 8085 are synchronized with the help of clock signal. Along with the control of fetching and decoding operations and generating appropriate signals for instruction execution, control circuitry also generates signals required to interface external devices to the processor.

The Signals of 8085

Power supply and frequency signals. Data bus and address bus. Control bus. Interrupt signals. Serial I/O signals. DMA signals Reset signals.

X1

VCC HOLD HLDA CLK(OUT) RESETIN READY

Pin Definitions 0f 8085

Power supply and frequency signals. Data bus and address bus. Control and Status signals Interrupt signals. Serial I/O signals. DMA signals Reset signals.

X2 RESET OUT SOD SID TRAP RST 7.5 RST 6.5 RST 5.5 INTR INTA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 Vss

8 0 8 5

IO/M S1 RD WR ALE S0 A15 A14 A13 A12 A11 A10 A9 A8

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

Power Supply and Frequency Signals

Vcc:- It requires a single +5V power supply. Vss:- Ground reference. X1 & X2:- A tuned circuit like LC, RC or crystal is connected at these 2 pins. The internal clock generator divides oscillator frequency by 2. CLK OUT:- Used as a system clock for other devices. Its frequency is half of the oscillator frequency.

Data Bus and Address Bus

AD0 to AD7:8-bit data bus (D0 D7) is multiplexed with the lower half of address bus (A0 A7). During first part of the machine cycle (T1) lower 8 bits of memory address or I/O address appear on the bus. During remaining part of the machine cycle (T2 and T3) these lines are used as a bi-directional data bus. A8 to A15 :Upper half of the 16 bit address appears on the address lines A8 to A15. These lines are used for the most significant 8 bits of the 16 bit address

Control and Status Signals

ALE (Address Latch Enable): Address latch enable is an output signal. It goes high when operation is started by processor. AD0 to AD7 lines are multiplexed and the lower half of the address (A0 A7) is available only during T1 of the machine cycle. This lower half of address is also necessary during T2 and T3 of machine cycle to access specific location in memory or I/O port. Lower half of an address must be latched in T1 of the machine cycle, so that it is available throughout the machine cycle. The latching of lower half of an address is done by using external latch and ALE signal from 8085.

Control and Status Signals

RD: Read is active low input signal used to read data from I/O device or memory. WR: Write is an active low output signal used write data on memory or an I/O device. IO/M: This is output pin or signal used to indicate whether 8085 is working in I/O mode(IO/M=1) or Memory mode(IO/M=0 ).

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

Control and Status Signals

S0 and S1: These are the status signals used to indicate type of machine cycle in progress. READY: It is used by the microprocessor to sense whether a peripheral is ready or not for data transfer. This an input signal used to check the status of output device. If it is low, P will WAIT until it is high. It is used to synchronize slower peripherals to the microprocessor.

Interrupt Signals

TRAP: It is an Edge & Level triggered highest priority, non mask able interrupt. After TRAP, restart occurs and execution starts from address 0024H. RST 7.5, 6.5, 5.5: These are maskable interrupts and have low priority than TRAP. INTR & INTA: INTR is a interrupt request signal after which P generates INTA or interrupt acknowledge signal.

Serial I/O Signals

SID (Serial I/P Data): Serial input data is input pin used to accept serial 1 bit data. SOD (Serial O/P Data): Serial output data is input pin used to send serial 1 bit data.

DMA Signals

HOLD & HLDA: HOLD is an input signal. When P receives HOLD signal it completes current machine cycle and stops executing next instruction. In response to HOLD P generates HLDA that is HOLD Acknowledge signal.

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

Reset Signals

RESETIN: This is input signal. When RESETIN is low p restarts and starts executing from location 0000H. RESETOUT: Used to reset connecting peripherals.

Features of 8085

It is an 8-bit microprocessor. It is a single chip N-MOS device with 40 pins. It works on 5 Volt dc power supply. It operates on a clock cycle with 50% duty cycle. It has on chip clock generator. The maximum clock frequency is 3 MHz while minimum frequency is 500kHz. It has multiplexed address and data bus.(AD0-AD7) to reduce number of external pins. It provides 74 instructions with 5 different addressing.

Features of 8085

It generates 8 bit I/O address so it can access 2^8 = 256 I/O ports. It provides 16 address lines so it can access 2^16 = 64Kbytes of memory. It provides Acc, one flag register, 6 general purpose registers and two special purpose registers (SP,PC). It provides 5 hardware interrupts, TRAP, RST 5.5, RST 6.5, RST 7.5,INTR. It provides serial lines SID, SOD. So serial peripherals can be interfaced with 8085 directly.

Features of 8085

It provides control signals (IO/M, RD, WR) to control the bus cycles, and hence external bus controller is not required.

Prepared by AJIT SARAF

2. 8085 Architecture, Pin diagram & Features

18 July 2013

University Questions (ELECTRONICS)

May-2011 1) Explain generation of control signals for 8085 microprocessor. (05 Marks) May-2013 2) Explain following signals of 8085 1) ALE 2) READY

University Questions (EXTC)

May-2012 1) With the help of a diagram explain the architecture of 8085microprocessor. (08 Marks) 2) Write short note on 8085 flags and their usage. (05 Marks) May-2013 3) Draw and explain microprocessor.

(05 Marks) 3) INTR

architecture

of 8085 (10 Marks)

Prepared by AJIT SARAF

10

You might also like

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- C5 - Intro To 8085 - Hardware PDFDocument39 pagesC5 - Intro To 8085 - Hardware PDFsiti hajarNo ratings yet

- EE6502 MPMC Two Marks With AnswerDocument10 pagesEE6502 MPMC Two Marks With Answervlsimani9110100% (1)

- MicroprocessorsDocument24 pagesMicroprocessorsarokiarajNo ratings yet

- 8085 Up NotesDocument44 pages8085 Up NotesAbhijit Chakrabarty100% (2)

- Assignment MPDocument10 pagesAssignment MPrajaNo ratings yet

- Microcontroller 8051Document76 pagesMicrocontroller 8051Anand GharuNo ratings yet

- 8051 MicrocontrollerDocument32 pages8051 MicrocontrollerRachit Sharma91% (11)

- 8085 Lab ManualDocument58 pages8085 Lab ManualShah JainamNo ratings yet

- Experiments On 8085 MicroprocessorDocument18 pagesExperiments On 8085 MicroprocessorSaumya Mohan100% (1)

- 8085Document56 pages8085Kunal MeherNo ratings yet

- Timing Diagrams For 1 Byte Instructions: 1. Adc MDocument21 pagesTiming Diagrams For 1 Byte Instructions: 1. Adc MChitra Belwal75% (4)

- Microprocessor8085 BestDocument145 pagesMicroprocessor8085 BestDebashis TaraiNo ratings yet

- First Term Assignment CSC 471 Summer-2018: Rihab Rahman, 16103327, CSC 471, Sec-F, MAHDocument40 pagesFirst Term Assignment CSC 471 Summer-2018: Rihab Rahman, 16103327, CSC 471, Sec-F, MAHAbdur RazzakNo ratings yet

- BE-II/IV-Sem-IV Computer Organization Lab Viva Questions With Answers-Osmania UniversityDocument15 pagesBE-II/IV-Sem-IV Computer Organization Lab Viva Questions With Answers-Osmania UniversitySirisha VamsiNo ratings yet

- Adc Interfacing With 8051Document2 pagesAdc Interfacing With 8051Sumukha Kumar0% (1)

- Block Diagram of 8085Document32 pagesBlock Diagram of 8085Shabd ShashankNo ratings yet

- 8085Document47 pages8085Govind GuptaNo ratings yet

- Introduction To 8085 Microprocessor - Dr.P.YogeshDocument48 pagesIntroduction To 8085 Microprocessor - Dr.P.Yogeshmailmeasdd100% (1)

- Microprocessors and Microcontrollers Module 1 - 5Document260 pagesMicroprocessors and Microcontrollers Module 1 - 5ncecentral0% (1)

- Microprocessor Lab Manual - FinalDocument157 pagesMicroprocessor Lab Manual - FinalDr. N.Shanmugasundaram100% (6)

- 8085 Instruction Addressing Modes ImppDocument87 pages8085 Instruction Addressing Modes ImppRohan VaidyaNo ratings yet

- Question Paper 8051 Microcontroller and ApplicationsDocument1 pageQuestion Paper 8051 Microcontroller and Applicationsveeramaniks408No ratings yet

- Timing Diagram 8085 FinalDocument29 pagesTiming Diagram 8085 FinalgokulchandruNo ratings yet

- 8051 MicrocontrollerDocument31 pages8051 MicrocontrollerRadha RaniNo ratings yet

- Block Diagram of Intel 8086Document5 pagesBlock Diagram of Intel 8086Ritesh SinghNo ratings yet

- Pic16f877a Phpapp02Document35 pagesPic16f877a Phpapp02firdaus_n9No ratings yet

- 8085 Instruction SetDocument122 pages8085 Instruction Setgokulchandru100% (1)

- Memory InterfacingDocument14 pagesMemory InterfacingSusmita Sau100% (3)

- Microprocessor Question BankDocument4 pagesMicroprocessor Question BankDarshan SharmaNo ratings yet

- 8255 NewDocument13 pages8255 Newmohit mishraNo ratings yet

- MPMC PDFDocument210 pagesMPMC PDFAnonymous TxxI4MTTNo ratings yet

- Microprocessors Jto Lice Study Material SampleDocument16 pagesMicroprocessors Jto Lice Study Material SamplePrabha KaruppuchamyNo ratings yet

- Microcontroller and Embedded SystemsDocument2 pagesMicrocontroller and Embedded SystemsIndranilNo ratings yet

- 8085 Instruction SetDocument27 pages8085 Instruction Setbostanci100% (1)

- Interfacing Programs For 8085Document37 pagesInterfacing Programs For 8085archankumarturagaNo ratings yet

- Microcontrollers and Embedded SystemsDocument35 pagesMicrocontrollers and Embedded SystemsTarek BarhoumNo ratings yet

- Chapter 4 Programmable Peripheral InterfaceDocument49 pagesChapter 4 Programmable Peripheral InterfacetesfayebbNo ratings yet

- Microprocessor Question BankDocument3 pagesMicroprocessor Question Bankstudy knowledge sumanjayNo ratings yet

- Question Bank-Microprocessor and ApplicaionDocument38 pagesQuestion Bank-Microprocessor and Applicaionchandrasekar100% (5)

- Cs1304 Q&A MWDocument35 pagesCs1304 Q&A MWksrajasekarNo ratings yet

- The 8085 Microprocessor ArchitectureDocument30 pagesThe 8085 Microprocessor Architectureabhisheksharma12392% (13)

- DSP - Mod 6 PPT 1Document37 pagesDSP - Mod 6 PPT 1oxygen oxygenNo ratings yet

- MICROPORCESSOR 8085 Lab ManualDocument53 pagesMICROPORCESSOR 8085 Lab ManualAjay PatilNo ratings yet

- Timers in 8051Document5 pagesTimers in 8051Karan AroraNo ratings yet

- Assignment Microprocessor 8085Document2 pagesAssignment Microprocessor 8085Dhaval Shukla100% (1)

- Program For Interfacing 8279: 1. 8085 Microprocessor Kit 2. 8279 Interfacing Module 3. Power SupplyDocument21 pagesProgram For Interfacing 8279: 1. 8085 Microprocessor Kit 2. 8279 Interfacing Module 3. Power SupplySubhashini MurugesanNo ratings yet

- Advanced RISC Machine-ARM Notes BhurchandiDocument8 pagesAdvanced RISC Machine-ARM Notes BhurchandiVipin TiwariNo ratings yet

- Reference: The 8051 Microcontroller: Architecture, Programming & Applications by Kenneth J. AyalaDocument27 pagesReference: The 8051 Microcontroller: Architecture, Programming & Applications by Kenneth J. Ayalasachin rawatNo ratings yet

- 8086 MicroprocessorDocument24 pages8086 Microprocessorsamrat kumar100% (1)

- MPDocument34 pagesMPAbhinandan JainNo ratings yet

- Notes For StudentsDocument29 pagesNotes For StudentsAnif Ilham IsmailNo ratings yet

- MPMC Eee Unit - I 8085 ProcessorDocument35 pagesMPMC Eee Unit - I 8085 ProcessorAnonymous zaMNkL100% (1)

- 8085 Features, Signal DescriptionDocument13 pages8085 Features, Signal DescriptionRakesh Kumar DNo ratings yet

- Ece 8085 MicroprocessorDocument26 pagesEce 8085 Microprocessorgourav VermaNo ratings yet

- Lecture1423722820 PDFDocument101 pagesLecture1423722820 PDFdavNo ratings yet

- Unit 1Document78 pagesUnit 1Vasunthara DNo ratings yet

- 8085 MaterialDocument12 pages8085 MaterialsameerNo ratings yet

- 8085 MicroprocessorDocument25 pages8085 Microprocessorprofessor2062No ratings yet

- Memory Interfacing With ExampleDocument6 pagesMemory Interfacing With ExampleSachin Jaysenan0% (3)

- IO Data Transfer TechniquesDocument5 pagesIO Data Transfer TechniquesSachin JaysenanNo ratings yet

- Supporting Hardware For 8085Document2 pagesSupporting Hardware For 8085Sachin JaysenanNo ratings yet

- Harvest Moon Friends of Mineral Town GuideDocument59 pagesHarvest Moon Friends of Mineral Town GuideSachin JaysenanNo ratings yet

- Binomial TheoremDocument17 pagesBinomial TheoremSachin JaysenanNo ratings yet

- Data Structures: Socs, Upes DehradunDocument99 pagesData Structures: Socs, Upes DehradunAnushka SharmaNo ratings yet

- Xii SC Practical AssignmentDocument20 pagesXii SC Practical AssignmentSakhyam BhoiNo ratings yet

- InterviewDocument60 pagesInterviewsalugu.janakimanoj2020No ratings yet

- (Lab 9 Manual) CS 204 DSA StackDocument4 pages(Lab 9 Manual) CS 204 DSA StackAbdullah AtiqNo ratings yet

- Java RecordDocument78 pagesJava RecordJ Nikle ReddyNo ratings yet

- 8085 Microprocessor ArchitectureDocument46 pages8085 Microprocessor ArchitectureJuhil H Patel100% (1)

- Cs6212 Programming and Data Structure LabDocument82 pagesCs6212 Programming and Data Structure LabPinky SaranNo ratings yet

- Arithmetic and Logic InstructionsDocument83 pagesArithmetic and Logic InstructionsAkash PandaNo ratings yet

- Java RecordDocument81 pagesJava RecordNaveen KumarNo ratings yet

- CBSE 2015 Question Papers For Class 12 Computer Science OutsideDocument55 pagesCBSE 2015 Question Papers For Class 12 Computer Science OutsideAyush MukhopadhyayNo ratings yet

- Ds Study QsDocument38 pagesDs Study QsAbhijeet PanwarNo ratings yet

- Basics of Computer ArchitecturesDocument24 pagesBasics of Computer ArchitecturesArvind KumarNo ratings yet

- Data Structure & AlgorithmDocument36 pagesData Structure & AlgorithmRubab AnamNo ratings yet

- AlgorithmsDocument23 pagesAlgorithmsUsman MalikNo ratings yet

- C Classes and Data Structures CompressDocument417 pagesC Classes and Data Structures CompressAisha AhmedNo ratings yet

- Plugin Aggregate Manual v075 PDFDocument33 pagesPlugin Aggregate Manual v075 PDFFiliyal FahriNo ratings yet

- Programming and Data Structures - Lecture Notes, Study Material and Important Questions, AnswersDocument7 pagesProgramming and Data Structures - Lecture Notes, Study Material and Important Questions, AnswersM.V. TVNo ratings yet

- 23 Tree ImplementationDocument5 pages23 Tree ImplementationVinay Kumar BollineniNo ratings yet

- PArkash DAta StructureDocument118 pagesPArkash DAta StructureRaishaNo ratings yet

- Basics of Electrical MeasurementDocument98 pagesBasics of Electrical MeasurementAshesh B VigneshNo ratings yet

- Viva Questions Class 12Document28 pagesViva Questions Class 12aryabhumika946No ratings yet

- I Fundamentals 1Document593 pagesI Fundamentals 1Joy BagdiNo ratings yet

- Chap2 - Data StructureDocument70 pagesChap2 - Data StructureAman PrajapatiNo ratings yet

- 3.CS6456 Oops PDFDocument155 pages3.CS6456 Oops PDFP.M.K anthNo ratings yet

- Data Structure DSDocument6 pagesData Structure DSgwcet2022 itdepartmentNo ratings yet

- Tia Micro1 09 FC FBDocument24 pagesTia Micro1 09 FC FBgsrNo ratings yet

- Cs301 Supreme File For Mid by HaCkeRzZzDocument55 pagesCs301 Supreme File For Mid by HaCkeRzZzSpread The Islam Every PlaceNo ratings yet

- Xii CS PB1Document10 pagesXii CS PB1lalita nagarNo ratings yet

- Os Galvinsilberschatz SolDocument134 pagesOs Galvinsilberschatz SolAakash DuggalNo ratings yet

- Three Improvements To The Reduceron: Matthew Naylor and Colin Runciman University of YorkDocument50 pagesThree Improvements To The Reduceron: Matthew Naylor and Colin Runciman University of YorkaldeghaidyNo ratings yet