Professional Documents

Culture Documents

Atmel 11207 SAMA5D3x Schematic Checklist Application Note

Uploaded by

suduku007Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Atmel 11207 SAMA5D3x Schematic Checklist Application Note

Uploaded by

suduku007Copyright:

Available Formats

Application Note

SAMA5D3x Microcontroller Schematic Checklist

AT91SAM ARM-based Embedded MPU

1.

Introduction

This application note is a schematic review checklist for systems embedding the Atmel AT91SAM ARM-based SAMA5D3x Embedded MPU. It gives requirements concerning the different pin connections that must be considered before starting any new board design and describes the minimum hardware resources required to quickly develop an application with the SAMA5D3x. It does not consider PCB layout constraints. It also gives advice regarding low-power design constraints to minimize power consumption. This application note is not intended to be exhaustive. Its objective is to cover as many configurations of use as possible. The Checklist table has a column reserved for reviewing designers to verify the line item that has been checked.

11207AATARM30-Jan-13

2.

Associated Documentation

Before going further into this application note, it is strongly recommended to check the latest documents for the SAMA5D3x Microcontroller on Atmels Web site. Table 2-1 gives the associated documentation needed to support full understanding of this application note.

Table 2-1.

Associated Documentation Information Document Title

User Manual Electrical/Mechanical Characteristics Ordering Information Errata Internal Architecture of Processor ARM/Thumb Instruction Sets Embedded In-circuit Emulator Evaluation Kit User Guide SAMA5D3x-EK User Guide (literature number 11180) Cortex-A5 Technical Reference Manual SAMA5D3x Datasheet (literature number 11121)

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

3.

Schematic Checklist

CAUTION: The AT91SAM Board design must comply with power-up and power down sequence guidelines provided in the datasheet to guarantee reliable operation of the device.

1.2V, 1.8V, 2.5V, 3.3V Power Supplies Schematic Example(1)

VDDOSC 1R 100nF 4.7F LDO Converter 10H GNDOSC VDDANA 3.3V 1R 100nF 4.7F GNDANA VDDBU 100nF GNDBU VDDIOP0,1 100nF GNDIOP VDDUTMII 100nF GNDUTMI VDDIOM 100nF LDO Converter GNDIOM VDDFUSE 2.5V DC/DC Converter 100nF GNDFUSE

VDDIODDR 1.8V DC/DC Converter 100nF GNDIODDR VDDCORE 1.2V LDO Converter 10H

VDDPLLA

100nF GNDCORE

1.2V

1R 100nF 4.7F GNDPLL VDDUTMIC 2.2F 100nF

GNDUTMI

(1)

These values are given only as a typical example

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

Signal Name

Recommended Pin Connection

Description Powers the device.

VDDCORE

1.2V Decoupling capacitor (100 nF)

(1)(2)

Decoupling/filtering capacitors must be added to improve start-up stability and reduce source voltage drop. Supply ripple must not exceed 20 mVrms.

1.8V VDDIODDR 1.2V Decoupling capacitor (100 nF)(1)(2)

Powers the DDR2/LPDDR Interface I/O lines. Powers the LPDDR2 Interface I/O lines. Decoupling/filtering capacitors must be added to improve start-up stability and reduce source voltage drop. Powers the External Memory Interface I/O lines. Dual voltage range is supported.

3.0V to 3.6V VDDIOM Decoupling capacitor (100 nF)

(1)(2)

The I/O drives are selected by programming the EBI_DRIVE field in the CCFG_EBICSA register. At power-up, the high drive mode for 3.3V memories is selected. Decoupling/filtering capacitors must be added to improve start-up stability and reduce source voltage drop.

VDDIOP0 VDDIOP1

1.65V to 3.6V Decoupling/filtering capacitors (100 nF)(1)(2)

Powers the peripherals I/O lines. Decoupling/filtering capacitors must be added to improve start-up stability and reduce source voltage drop. Powers the Backup unit.

VDDBU

1.8V to 3.6V Decoupling capacitor (100 nF)(1)(2)

(Slow Clock Oscillator, On-chip RC and a part of the System Controller). Supply ripple must not exceed 30 mVrms.

1.2V VDDUTMIC Decoupling/filtering capacitors (100 nF and 2.2 F)(1)(2)

Powers the USB device and host UTMI+ core. Decoupling/filtering capacitors must be added to improve start-up stability and reduce source voltage drop. Powers the USB device and host UTMI+ interface.

VDDUTMII

3.0V to 3.6V Decoupling capacitor (100 nF)(1)(2) Decoupling/filtering capacitors must be added to improve start-up stability and reduce source voltage drop.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

Signal Name

Recommended Pin Connection

Description Powers the PLLA cell. The VDDPLLA power supply pin draws small current, but it is noise sensitive. Care must be taken in VDDPLLA power supply routing, decoupling and also on bypass capacitors. Supply ripple must not exceed 10 mVrms. Powers the main oscillator cells. The VDDOSC power supply pin draws small current, but it is noise sensitive. Care must be taken in VDDOSC power supply routing, decoupling and also on bypass capacitors. Supply ripple must not exceed 30 mVrms.

VDDPLLA

1.2V Decoupling/filtering RLC circuit(1)

VDDOSC

1.65V to 3.6V Decoupling/filtering RLC circuit(1)

3.0V to 3.6V VDDANA Decoupling/filtering RLC circuit(1) Application dependent VDDFUSE 2.25V to 2.75V Powers the fuse box for Programming. It can be tied to ground with a 100 resistor for fuse reading only. GNDCORE pins are common to VDDCORE pins. GNDCORE Core Chip ground DDR/LPDDR/LPDDR2 interface I/O lines ground NAND and SMC Interface I/O lines ground Peripherals and ISI I/O lines ground GNDCORE pins should be connected as shortly as possible to the system ground plane. GNDIODDR pins should be connected as shortly as possible to the system ground plane. GNDIOM pins should be connected as shortly as possible to the system ground plane. GNDIOP pins are common to VDDIOP0, VDDIOP1 pins. GNDIOP GNDIOP pins should be connected as shortly as possible to the system ground plane. GNDBU pin is provided for VDDBU pins. GNDBU Backup ground GNDBU pin should be connected as shortly as possible to the system ground plane. GNDUTMI pins are common to VDDUTMII and VDDUTMIC pins. GNDUTMI pins should be connected as shortly as possible to the system ground plane. GNDPLL pin is provided for VDDPLLA pin. GNDPLL pin should be connected as shortly as possible to the system ground plane. Powers the Analog to Digital Converter (ADC).

GNDIODDR

GNDIOM

GNDUTMI

UDPHS and UHPHS UTMI+ Core and interface ground

GNDPLL

PLLA cell ground

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

Signal Name GNDOSC

Recommended Pin Connection PLLA, PLLUTMI and Oscillator ground

Description GNDOSC pin is provided for VDDOSC, VDDPLLA pins. GNDOSC pin should be connected as shortly as possible to the system ground plane. GNDANA pins are common to VDDANA pins.

GNDANA

Analog ground

GNDANA pins should be connected as shortly as possible to the system ground plane. GNDFUSE pins are common to VDDFUSE pins.

GNDFUSE

Fuse box ground

GNDFUSE pins should be connected as shortly as possible to the system ground plane.

Note:

For more information please refer to the Core Power Supply POR Characteristics section of the SAMA5D3x Datasheet.

Signal Name

Recommended Pin Connection Clock, Oscillator and PLL

Description

Crystal Load Capacitance to check (CCRYSTAL).

SAMA5D3x

XIN XOUT GNDOSC

Crystals between 8 and 16 MHz XIN XOUT 12 MHz Main Oscillator in Normal Mode USB High Speed (not Full Speed) Host and Device peripherals need a 12 MHz clock. Capacitors on XIN and XOUT (Crystal Load Capacitance dependent)

CCRYSTAL

CLEXT

CLEXT

Example: for a 12 MHz crystal with a load capacitance of CCRYSTAL = 15 pF, external capacitors are required: CLEXT = 20 pF. Refer to the electrical specifications of the SAMA5D3x Datasheet. XIN XOUT 12 MHz Main Oscillator in Bypass Mode XIN: external clock source XOUT: can be left unconnected USB High speed (not Full Speed) Host and Device peripherals need a 12 MHz clock. VDDOSC square wave signal External clock source up to 50 MHz Duty Cycle: 40 to 60% Refer to the electrical specifications of the SAMA5D3x Datasheet.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

Signal Name XIN XOUT 12 MHz Main Oscillator Disabled

Recommended Pin Connection XIN: can be left unconnected XOUT: can be left unconnected USB High Speed (not Full Speed) Host and Device peripherals need a 12 MHz clock.

Description Typical nominal frequency 12 MHz (Internal 12 MHz RC Oscillator) Duty Cycle: 45 to 55% Refer to the electrical specifications of the SAMA5D3x Datasheet. Crystal Load Capacitance to check (CCRYSTAL32).

SAMA5D3x

XIN32 XOUT32 GNDBU

XIN32 XOUT32

32.768 kHz Crystal

C CRYSTAL32

Capacitors on XIN32 and XOUT32 Slow Clock Oscillator (Crystal Load Capacitance dependent)

CLEXT32 CLEXT32

Example: for a 32.768 kHz crystal with a load capacitance of CCRYSTAL32 = 12.5 pF, external capacitors are required: CLEXT32 = 19 pF. Refer to the electrical specifications of the SAMA5D3x Datasheet. XIN32 XOUT32 XIN32: external clock source Slow Clock Oscillator in Bypass Mode XIN32 XOUT32 XIN32: can be left unconnected Slow Clock Oscillator Disabled XOUT32: can be left unconnected Typical nominal frequency 32 kHz (Internal 32 kHz RC Oscillator) Duty Cycle: 45 to 55% Refer to the electrical specifications of the SAMA5D3x Datasheet. XOUT32: can be left unconnected VDDBU square wave signal External clock source up to 44 kHz Duty Cycle: 40 to 60% Refer to the electrical specifications of the SAMA5D3x Datasheet.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

Signal Name

Recommended Pin Connection

Description Bias Voltage Reference for USB To reduce as much as possible the noise on VBG pin please check the Layout consideration below: - VBG path as short as possible - ground connection to GNDUTMI

VBG

0.9 - 1.1V(5)

5K62 1% VBG 10 pF GNDUTMI

Refer to the Signal Description of the SAMA5D3x Datasheet. ICE and JTAG(3) TCK Pull-up (100 kOhm)(1) Pull-up (100 kOhm)(1) This pin is a Schmitt trigger input. No internal pull-up resistor. This pin is a Schmitt trigger input. No internal pull-up resistor.

TMS

TDI

Pull-up (100 kOhm)(1)

This pin is a Schmitt trigger input. No internal pull-up resistor.

TDO

Floating

Output driven at up to VVDDIOP0

NTRST

Please refer to the Pin Description of the SAMA5D3x Datasheet.

This pin is a Schmitt trigger input. Internal pull-up resistor to VVDDIOP0 (100 kOhm).

JTAGSEL

In harsh environments(4), it is strongly recommended to tie this pin to GNDBU if not used or to add an external low-value resistor (such as 1 kOhm).

Internal pull-down resistor to GNDBU (15 kOhm). Must be tied to VVDDBU to enter JTAG Boundary Scan.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

Signal Name

Recommended Pin Connection Reset/Test

Description

NRST is a bidirectional pin (Schmitt trigger input). It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low externally to reset the microcontroller. By default, the User Reset is enabled after a General Reset so that it is possible for a component to assert low and reset the microcontroller. An internal pull-up resistor to VVDDIOP0 (100 kOhm) is available for User Reset and External Reset control. In harsh environments(4), it is strongly recommended to tie this pin to GNDBU if not used or to add an external low-value resistor (such as 10 kOhm).

Application dependent. NRST Can be connected to a push button for hardware reset.

TST

This pin is a Schmitt trigger input. Internal pull-down resistor to GNDBU (15 kOhm).

Must be tied to VVDDIOP0 to boot from Embedded ROM. BMS Application dependent. Must be tied to GNDIOP to boot from external memory (EBI Chip Select 0). Shutdown/Wake-up Logic Application dependent. SHDN A typical application connects the pin SHDN to the shutdown input of the DC/DC Converter providing the main power supplies. This pin is a push-pull output. SHDN pin is driven low to GNDBU by the Shutdown Controller (SHDWC).

WKUP

0V to VVDDBU

This pin is an input-only. WKUP behavior can be configured through the Shutdown Controller (SHDWC).

PIO All PIOs are pulled-up inputs (100 kOhm) at reset except those which are multiplexed with the Address Bus signals that require to be enabled as peripherals: PAx PBx PCx PDx PEx To reduce power consumption if not used, the concerned PIO can be configured as an output, driven at 0 with internal pull-up disabled. ADC Application dependent. Schmitt Trigger on All Inputs. Refer to the column Reset State of the Pin Description table in the 324-ball LFBGA Package Pinout section of the SAMA5D3x Datasheet.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

Signal Name

Recommended Pin Connection 3.3V to VDDANA

Description ADVERF is a pure analog input. To reduce power consumption, if ADC is not used: connect ADVREF to GNDANA.

TSADVREF

Decoupling/filtering capacitors Application dependent. EBI

D0 - D15

Application dependent.

Data Bus (D0 to D15) All data lines are pull-up inputs to VVDDIOM at reset. Address Bus (A0 to A25) All address lines are driven to 0 at reset.

A0 - A25

Application dependent.

HSMC - DDR2/LPDDR/LPDDR2 Controller - NAND Flash Support See EBI and DDR2/LPDDR/LPDDR2 Hardware Interface on page 12. USB High Speed Host (UHPHS)/USB High Speed Device (UDPHS) HHSDPA/DHSDP HHSDMA/DHSDM HHSDPB/HHSDMB HHSDPC/HHSDMC Application dependent(5). Application dependent(5). Application dependent .

(5)

Pull-down output at reset. Pull-down output at reset. Pull-down output at reset.

Notes: 1. These values are given only as a typical example. 2. Decoupling capacitors must be connected as close as possible to the microcontroller and on each concerned pin.

100nF VDDCORE 100nF VDDCORE 100nF VDDCORE GND

3. It is recommended to establish accessibility to a JTAG connector for debug in any case. 4. In a well-shielded environment subject to low magnetic and electric field interference, the pin may be left unconnected. In noisy environments, a connection to ground is recommended. 5. Example of USB High Speed Host connection: More details are in the USB Host High Speed Port (UHPHS) section of the SAMA5D3x Datasheet.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

10

(1) The values shown on the 22 k and 15 k resistors are only valid with 3.3V supplied PIOs. (2) R = 5K62. 6. Typical USB High Speed Device connection: More details are in the USB High Speed Device Port (UDPHS) section of the SAMA5D3x Datasheet.

(1) The values shown on the 22 k and 15 k resistors are only valid with 3.3V supplied PIOs. (2) R = 5K62.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

11

4.

EBI and DDR2/LPDDR/LPDDR2 Hardware Interface

These tables detail the connections to be applied between the EBI/DDR2 pins and the external devices for each Memory Controller.

Table 4-1. EBI Pins and External Static Devices Connections Pins of the Interfaced Device Signals: EBI_ Controller D0 - D7 D8 - D15 A0/NBS0 A1 A2-A22 A23-A25 NCS0 NCS1 NCS2 NCS3/NANDCS NRD/NANDOE NWE/NWR0/NANDWE NWR1/NBS1 D0 - D7 A0 A1 A[2:22] A[23:25] CS CS CS CS OE WE 8-bit Static Device 2 x 8-bit Static Devices SMC D0 - D7 D8 - D15 A0 A[1:21] A[22:24] CS CS CS CS OE WE WE

(1) (1)

16-bit Static Device

D0 - D7 D8 - D15 NLB A0 A[1:21] A[22:24] CS CS CS CS OE WE NUB

Notes: 1.

NWR0 enables lower byte writes. NWR1 enables upper byte writes.

Table 4-2.

EBI/DDR2 Pins and External Devices Connections Pins of the Interfaced Device

Signals: EBI_/DDR2_ Controller DDR_CALP DDR_CALN DDR_VREF DDR_A[6..0] DDR_A[13..7] DDR_D[15..0] DDR_D[31..16] DDR_DQM[1..0] DDR_DQM[3..2] DDR_DQS[1..0] DDR_DQS[3..2]

DDR2/LPDDR 2 x 16-bit MPDDRC VREF A[6..0] A[13..7] D[15..0] D[15..0] DM[1..0] DM[1..0] DQS[1..0] DQS[1..0]

LPDDR2 2 x 16-bit NAND Flash NFC VREF CA[9..3] DQ[15..0] DQ[15..0] DM[1..0] DM[1..0] DQS[1..0] DQS[1..0]

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

12

Table 4-2.

EBI/DDR2 Pins and External Devices Connections Pins of the Interfaced Device

Signals: EBI_/DDR2_ Controller DDR_DQSN[1..0] DDR_DQSN[3..2] DDR_CS DDR_CLK DDR_CLKN DDR_CKE DDR_RAS DDR_CAS DDR_WE DDR_BA[2..0] D0 - D15 A21/NANDALE A22/NANDCLE NRD/NANDOE NWE/NWR0/NANDWE NCS3/NANDCS NANDRDY A0/NBS0 A1 - A20 A23 - A25 NWR1/NBS1 NCS0 NCS1 NCS2 NWAIT Pxx(1) Pxx

(1)

DDR2/LPDDR 2 x 16-bit MPDDRC DDR_VREF DDR_VREF CS CK CK# CKE RAS CAS WE BA[2..0]

LPDDR2 2 x 16-bit NAND Flash NFC DQS#[1..0] DQS#[1..0] CS CK CK# CKE CA0 CA1 CA2 BA[2..0] NFD0-NFD15 ALE CLE RE WE CE R/B# CE RDY

Notes: 1.

Any PIO line.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

13

5.

AT91SAM Boot Program Hardware Constraints

See the Boot Strategies section of the SAMA5D3x Datasheet for more details on the boot program.

5.1

AT91SAM Boot Program Supported Crystals (MHz)

A 12 MHz Crystal or external clock (in bypass mode) is mandatory in order to generate USB and PLL clocks correctly for the following boots.

5.2

NAND Flash Boot

Boot is possible if the first page contains a valid header or if it is ONFI compliant. For more details please check the section Nand Flash Boot of the SAMA5D3x Datasheet.

Table 5-1. Peripheral EBI CS3 SMC EBI CS3 SMC EBI CS3 SMC EBI CS3 SMC EBI CS3 SMC EBI CS3 SMC Pins Driven during NAND Flash Boot Program Execution Pin NANDOE NANDWE NANDCS NAND ALE NAND CLE Cmd/Addr/Data PIO Line

5.3

SD Card Boot

SD Card Boot supports all SD Card memories compliant with SD Memory Card Specification V2.0. This includes SDHC cards.

Table 5-2. Peripheral MCI0 MCI0 MCI0 MCI0 MCI0 Pins Driven During SD Card Boot Program Execution Pin MCI0_CK MCI0_D0 MCI0_D1 MCI0_D2 MCI0_D3 PIO Line PD9 PD1 PD2 PD3 PD4

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

14

5.4

Serial and DataFlash Boot

Two kinds of SPI Flash are supported: SPI Serial Flash and SPI DataFlash. The SPI Flash bootloader tries to boot on SPI0 Chip Select 0, first looking for SPI Serial Flash, and then for SPI DataFlash. The SPI Flash Boot program supports:

z z

All SPI Serial Flash devices All DataFlash devices

Pins Driven During Serial or DataFlash Boot Program Execution Pin MOSI MISO SPCK NPCS0 PIO Line PD11 PD10 PD12 PD13

Table 5-3. Peripheral SPI0 SPI0 SPI0 SPI0

5.5

TWI EEPROM Boot

The TWI EEPROM Flash Boot program searches for a valid application in an EEPROM memory. TWI EEPROM Boot supports all I2C-compatible EEPROM memories using 7-bit device (Address 0x50).

Table 5-4. Peripheral TWI0 TWI0 Pins Driven During TWI EEPROM Boot Program Execution Pin TWD0 TWCK0 PIO Line PA30 PA31

5.6

SAM-BA Boot

The SAM-BA Boot Assistant supports serial communication via the DBGU or the USB Device Port.

Table 5-5. Peripheral DBGU DBGU Pins Driven During SAM-BA Boot Program Execution Pin DRXD DTXD PIO Line PB30 PB31

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

15

6.

Revision History

Doc. Rev 11207A

Comments First issue.

Change Request Ref.

SAMA5D3x Microcontroller Schematic Checklist [APPLICATION NOTE]

11207AATARM30-Jan-13

16

Atmel Corporation 1600 Technology Drive San Jose, CA 95110 USA Tel: (+1) (408) 441-0311 Fax: (+1) (408) 487-2600 www.atmel.com

Atmel Asia Limited Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

Atmel Japan G.K. 16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku Tokyo 141-0032 JAPAN Tel: (+81) (3) 6417-0300 Fax: (+81) (3) 6417-0370

2013 Atmel Corporation. All rights reserved. / Rev.: 11207AATARM30-Jan-13 Atmel, Atmel logo and combinations thereof, Enabling Unlimited Possibilities, SAM-BA and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM, ARMPowered logo and others are registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- An0002 Efm32 Hardware Design ConsiderationsDocument16 pagesAn0002 Efm32 Hardware Design ConsiderationsRam SakthiNo ratings yet

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- Dual Full Bridge PWM Motor Driver: FeaturesDocument31 pagesDual Full Bridge PWM Motor Driver: FeaturesTiếnMốcNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- AT91RM9200 Microcontroller Schematic Check List: At91Sam ARM-based Embedded MPU Application NoteDocument17 pagesAT91RM9200 Microcontroller Schematic Check List: At91Sam ARM-based Embedded MPU Application NoteThienNo ratings yet

- Led Driver 12 PinDocument39 pagesLed Driver 12 PinМихаил НестеровNo ratings yet

- NCP 43080Document36 pagesNCP 43080TestronicpartsNo ratings yet

- Application Note 2034 LM3445 - 120VAC, 8W Isolated Flyback LED DriverDocument20 pagesApplication Note 2034 LM3445 - 120VAC, 8W Isolated Flyback LED DriverEduardoNo ratings yet

- AMIS-39101 Octal High Side Driver With Protection: General DescriptionDocument12 pagesAMIS-39101 Octal High Side Driver With Protection: General Descriptionblackmesa82No ratings yet

- LM 2623Document21 pagesLM 2623alejo0091No ratings yet

- AN-2061 LM3445 A19 Edison Retrofit Evaluation Board: User's GuideDocument11 pagesAN-2061 LM3445 A19 Edison Retrofit Evaluation Board: User's GuideVanessaDDMNo ratings yet

- Microchip TC962 DatasheetDocument13 pagesMicrochip TC962 DatasheetCale McColloughNo ratings yet

- 12 Volt Smps Circuit DiagramDocument7 pages12 Volt Smps Circuit DiagramAnura MaddumageNo ratings yet

- AN98080 - Devices Based in HTRC110Document58 pagesAN98080 - Devices Based in HTRC110recursos2009No ratings yet

- LM2852 Synchronous BuckDocument14 pagesLM2852 Synchronous BuckAndrew CavanaughNo ratings yet

- Bootstrap Diode: ExplanationDocument6 pagesBootstrap Diode: ExplanationKidus DawitNo ratings yet

- Dual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Document16 pagesDual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Benny RoyNo ratings yet

- High-performance offline controller delivers lowest total cost solution in compact packagesDocument9 pagesHigh-performance offline controller delivers lowest total cost solution in compact packagesRICHIHOTS2No ratings yet

- Tps 65217 CDocument86 pagesTps 65217 CcosmicfundooNo ratings yet

- Viper22a Equivalent PDFDocument16 pagesViper22a Equivalent PDFXande Nane Silveira0% (1)

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- 5051 AppDocument37 pages5051 AppawemetalNo ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- La 4108Document12 pagesLa 4108andrzej_w_k100% (3)

- Line Regulator Controller: Features General DescriptionDocument16 pagesLine Regulator Controller: Features General DescriptionfuzulibabaNo ratings yet

- Ads 7870Document43 pagesAds 7870Moorthy VenkatachalamNo ratings yet

- STR-A6251 AND STR-A6252 UNIVERSAL-INPUT REGULATORSDocument7 pagesSTR-A6251 AND STR-A6252 UNIVERSAL-INPUT REGULATORSGiovanni Carrillo VillegasNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- IC-ON-LINE - CN dm0365r 44840Document20 pagesIC-ON-LINE - CN dm0365r 44840MoscandoNo ratings yet

- Sbs 1.1-Compliant Gas Gauge Enabled With Impedancetrack™ Technology For Use With The Bq29312Document62 pagesSbs 1.1-Compliant Gas Gauge Enabled With Impedancetrack™ Technology For Use With The Bq29312João FranciscoNo ratings yet

- Low-Capacitance 2-Channel 15-Kv Esd-Protection Array For High-Speed Data InterfacesDocument21 pagesLow-Capacitance 2-Channel 15-Kv Esd-Protection Array For High-Speed Data InterfacesLeslie StewartNo ratings yet

- drv8805 PDFDocument19 pagesdrv8805 PDFAdithya ChandrasekaranNo ratings yet

- 300mA LDO REGULATOR RP114x SERIES DATA SHEETDocument28 pages300mA LDO REGULATOR RP114x SERIES DATA SHEETSol De GabrielNo ratings yet

- Contactor - SchniderDocument28 pagesContactor - SchniderPramod DixitNo ratings yet

- 7805 Regulator DescriptionDocument4 pages7805 Regulator DescriptionyeateshwarriorNo ratings yet

- DRV 8811Document22 pagesDRV 8811nelson_loboNo ratings yet

- 2SD10617Document12 pages2SD10617info5280No ratings yet

- Cad 32Document10 pagesCad 32Nikos GerakasNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- Manual Ad Rcsn422Document7 pagesManual Ad Rcsn422schatten_3No ratings yet

- DRV 8432Document34 pagesDRV 8432Van Thanh TranNo ratings yet

- Datasheet LM3429Document34 pagesDatasheet LM3429Bagus KrisviandikNo ratings yet

- BQ 24726Document38 pagesBQ 247268ctanoNo ratings yet

- TC427CPADocument5 pagesTC427CPASherif OkdaNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- Cost-Effective, 2A Sink/Source Bus Termination Regulator: General Description FeaturesDocument13 pagesCost-Effective, 2A Sink/Source Bus Termination Regulator: General Description FeaturesMostapha BenaliNo ratings yet

- LM48555 Ceramic Speaker Driver: General Description Key SpecificationsDocument14 pagesLM48555 Ceramic Speaker Driver: General Description Key SpecificationsSai SudhaNo ratings yet

- ADPLL PresentationDocument28 pagesADPLL PresentationSaiHarshithaNo ratings yet

- DM74123 Dual Retriggerable One-Shot With Clear and Complementary OutputsDocument5 pagesDM74123 Dual Retriggerable One-Shot With Clear and Complementary OutputsDiego HenriqueNo ratings yet

- 10gigabit XFP Optical ReceiverDocument6 pages10gigabit XFP Optical ReceivermichelNo ratings yet

- BQ 24725Document40 pagesBQ 24725nameless2061No ratings yet

- Oz9938 PDFDocument12 pagesOz9938 PDFCarlosNo ratings yet

- AN74 ZXLD1374 For Solar Street Lighting PDFDocument11 pagesAN74 ZXLD1374 For Solar Street Lighting PDFkishordaNo ratings yet

- PVI-3.8/4.6-I-OUTD 3.8 To 4.6 KW: ABB String InvertersDocument4 pagesPVI-3.8/4.6-I-OUTD 3.8 To 4.6 KW: ABB String InvertersRicho DeepNo ratings yet

- MC14017B Decade Counter: PDIP 16 P Suffix CASE 648Document9 pagesMC14017B Decade Counter: PDIP 16 P Suffix CASE 648JossuarmmNo ratings yet

- IC-ON-LINE - CN dm0465r 44841Document20 pagesIC-ON-LINE - CN dm0465r 44841ubhagavanNo ratings yet

- Ds92Lv16: Ds92Lv16 16-Bit Bus Lvds Serializer/Deserializer - 25 - 80 MHZDocument21 pagesDs92Lv16: Ds92Lv16 16-Bit Bus Lvds Serializer/Deserializer - 25 - 80 MHZlur46No ratings yet

- SN74CBTS16211 24-Bit Fet Bus Switch With Schottky Diode ClampingDocument11 pagesSN74CBTS16211 24-Bit Fet Bus Switch With Schottky Diode ClampingBa DuyNo ratings yet

- ADC08831/ADC08832 8-Bit Serial I/O CMOS A/D Converters With Multiplexer and Sample/Hold FunctionDocument24 pagesADC08831/ADC08832 8-Bit Serial I/O CMOS A/D Converters With Multiplexer and Sample/Hold Functionrudra_1No ratings yet

- Broucher SVSGOI WorkshopDocument2 pagesBroucher SVSGOI Workshopsuduku007No ratings yet

- Broucher SVSGOI WorkshopDocument2 pagesBroucher SVSGOI Workshopsuduku007No ratings yet

- Multivariate Analysis Techniques for Market SegmentationDocument57 pagesMultivariate Analysis Techniques for Market Segmentationsuduku007100% (1)

- Application Design Patterns: State Machines: TutorialDocument4 pagesApplication Design Patterns: State Machines: Tutorialsuduku007No ratings yet

- Generating A Schematic Symbol For Orcad Capture: September 2006 Application Note An8075Document7 pagesGenerating A Schematic Symbol For Orcad Capture: September 2006 Application Note An8075suduku007No ratings yet

- Assignment 3Document2 pagesAssignment 3suduku007No ratings yet

- LabVIEW Core 1 v2012 Release NotesDocument2 pagesLabVIEW Core 1 v2012 Release Notessuduku007No ratings yet

- 2011-9 Reliability and Fault ToleranceDocument49 pages2011-9 Reliability and Fault Tolerancesuduku007No ratings yet

- Schematic Guidelines For The MMPF0100: Application NoteDocument8 pagesSchematic Guidelines For The MMPF0100: Application Notesuduku007No ratings yet

- LabVIEW Core 2 v2012 Release NotesDocument2 pagesLabVIEW Core 2 v2012 Release Notessuduku007No ratings yet

- 6 Tips and Tricks To Increase Labview Performance: Document Type Ni Supported Publish DateDocument2 pages6 Tips and Tricks To Increase Labview Performance: Document Type Ni Supported Publish Datesuduku007No ratings yet

- Environmental Stress Screening TutorialDocument30 pagesEnvironmental Stress Screening TutorialMariut Elena LarisaNo ratings yet

- Seq Traffic LightDocument4 pagesSeq Traffic Lightsuduku007No ratings yet

- Evolve Treadmill Rev.1.3Document24 pagesEvolve Treadmill Rev.1.3suduku007No ratings yet

- Computer Organization Hamacher Instructor Manual Solution - Chapter 4Document13 pagesComputer Organization Hamacher Instructor Manual Solution - Chapter 4suduku007No ratings yet

- Practice Problems 12Document32 pagesPractice Problems 12suduku007No ratings yet

- Programming The Basic ComputerDocument22 pagesProgramming The Basic Computermanishbhardwaj8131No ratings yet

- Amanda Sallander Research Paper Back Pain PDFDocument11 pagesAmanda Sallander Research Paper Back Pain PDFjacobineiroNo ratings yet

- AN4603Document46 pagesAN4603suduku007No ratings yet

- AN3278Document16 pagesAN3278suduku007No ratings yet

- MS QualityManagementDocument1 pageMS QualityManagementsuduku007No ratings yet

- EC-GATE-2011 (1) .PDF SolutionDocument28 pagesEC-GATE-2011 (1) .PDF SolutionMudit MittalNo ratings yet

- Post-Silicon Validation Opportunities, Challenges and Recent AdvancesDocument6 pagesPost-Silicon Validation Opportunities, Challenges and Recent Advancessuduku007No ratings yet

- Electrical Paper IDocument28 pagesElectrical Paper ISai KrishnaNo ratings yet

- Kids Activity Book 2007Document27 pagesKids Activity Book 2007honormae14No ratings yet

- Vimal Patel Offer Letter PatniDocument5 pagesVimal Patel Offer Letter Patnisuduku007No ratings yet

- MS Software Systems ChartDocument1 pageMS Software Systems ChartVinay GowdaNo ratings yet

- Ec 1251 Electronics Circuits IIDocument17 pagesEc 1251 Electronics Circuits IIainugiri100% (1)

- Collis EMV Personal Is at Ion Validation ToolDocument4 pagesCollis EMV Personal Is at Ion Validation Toolsuduku007No ratings yet

- VT6050 VT6010 QuickGuide ENDocument19 pagesVT6050 VT6010 QuickGuide ENPriyank KumarNo ratings yet

- Smart Grid Standards GuideDocument11 pagesSmart Grid Standards GuideKeyboardMan19600% (1)

- TutorialDocument324 pagesTutorialLuisAguilarNo ratings yet

- Sap ThufingteDocument10 pagesSap ThufingtehangsinfNo ratings yet

- JK Paper Q4FY11 Earnings Call TranscriptDocument10 pagesJK Paper Q4FY11 Earnings Call TranscriptkallllllooooNo ratings yet

- Steam Turbines: ASME PTC 6-2004Document6 pagesSteam Turbines: ASME PTC 6-2004Dena Adi KurniaNo ratings yet

- Who will buy electric vehicles Segmenting the young Indian buyers using cluster analysisDocument12 pagesWho will buy electric vehicles Segmenting the young Indian buyers using cluster analysisbhasker sharmaNo ratings yet

- Conjoint Analysis Basic PrincipleDocument16 pagesConjoint Analysis Basic PrinciplePAglu JohnNo ratings yet

- Air Arms S400 EXPDocument3 pagesAir Arms S400 EXPapi-3695814No ratings yet

- Helmitin R 14030Document3 pagesHelmitin R 14030katie.snapeNo ratings yet

- Oral Nutrition Support NotesDocument28 pagesOral Nutrition Support Notesleemon.mary.alipao8695No ratings yet

- SRS Design Guidelines PDFDocument46 pagesSRS Design Guidelines PDFLia FernandaNo ratings yet

- Air Wellness QRSDocument2 pagesAir Wellness QRSapi-3743459No ratings yet

- Chemistry Implementation: Name: Rasheed Campbell School: Kingston College Candidate #.: Centre #: 100057Document12 pagesChemistry Implementation: Name: Rasheed Campbell School: Kingston College Candidate #.: Centre #: 100057john brownNo ratings yet

- 7890 Parts-Guide APDocument4 pages7890 Parts-Guide APZia HaqNo ratings yet

- Progibb LV Plus PGR - Low Voc FormulationDocument2 pagesProgibb LV Plus PGR - Low Voc FormulationDodik Novie PurwantoNo ratings yet

- GIS AccidentsDocument5 pagesGIS Accidentsali110011No ratings yet

- T9001 T9002 T9003 T9004: Tecn# Originator Title Aging Status of TecnDocument2 pagesT9001 T9002 T9003 T9004: Tecn# Originator Title Aging Status of TecnThanalachmy GopiNo ratings yet

- Tetracyclines: Dr. Md. Rageeb Md. Usman Associate Professor Department of PharmacognosyDocument21 pagesTetracyclines: Dr. Md. Rageeb Md. Usman Associate Professor Department of PharmacognosyAnonymous TCbZigVqNo ratings yet

- Math 202: Di Fferential Equations: Course DescriptionDocument2 pagesMath 202: Di Fferential Equations: Course DescriptionNyannue FlomoNo ratings yet

- Traffic Violation Monitoring with RFIDDocument59 pagesTraffic Violation Monitoring with RFIDShrëyãs NàtrájNo ratings yet

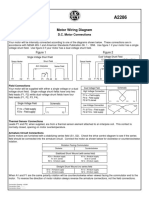

- Motor Wiring Diagram: D.C. Motor ConnectionsDocument1 pageMotor Wiring Diagram: D.C. Motor Connectionsczds6594No ratings yet

- Soil LiquefactionDocument12 pagesSoil LiquefactionKikin Kikin PelukaNo ratings yet

- Daftar Spesifikasi Teknis Pembangunan Gedung Kantor BPN BojonegoroDocument6 pagesDaftar Spesifikasi Teknis Pembangunan Gedung Kantor BPN BojonegoroIrwin DarmansyahNo ratings yet

- Metal Framing SystemDocument56 pagesMetal Framing SystemNal MénNo ratings yet

- Basic First AidDocument31 pagesBasic First AidMark Anthony MaquilingNo ratings yet

- Chemistry of FormazanDocument36 pagesChemistry of FormazanEsteban ArayaNo ratings yet

- What Is DSP BuilderDocument3 pagesWhat Is DSP BuilderĐỗ ToànNo ratings yet

- Baseline Program Rev 3A Presentation 25 July 2020Document24 pagesBaseline Program Rev 3A Presentation 25 July 2020Shakti Sourava RautrayaNo ratings yet

- Fraktur Dentoalevolar (Yayun)Document22 pagesFraktur Dentoalevolar (Yayun)Gea RahmatNo ratings yet