Professional Documents

Culture Documents

Tema 19

Uploaded by

Rupesito RI0 ratings0% found this document useful (0 votes)

6 views0 pagesOriginal Title

Tema19

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views0 pagesTema 19

Uploaded by

Rupesito RICopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 0

PREPARACION Y CARACTERIZACION DE

RECUBRIMIENTOS Y LAMINAS DELGADAS

TEMA 18

APLICACIONES DE LAS LAMINAS

DELGADAS EN

MICROELECTRONICA

DR. J.M. ALBELLA

APLICACIONES DE LAS LMINAS DELGADAS

EN MICROELECTRONICA

Indice:

1. INTRODUCCION: PAPEL DE LAS CAPAS DELGADAS EN LOS

CIRCUITOS INTEGRADOS MONOLITICOS.

2. ESTRUCTURA DE LAS CAPAS DE UN CIRCUITO

INTEGRADO:

3. TECNOLOGIA PLANAR: FOTOLITOGRAFIA.

4. PREPARACION DEL SUBSTRATO.

5. CRECIMIENTO Y DEPOSICION DE CAPAS AISLANTES.

6. IMPLANTACIN DE DOPANTES.

7. DEPOSICION DE CAPAS CONDUCTORAS.

8. RESUMEN Y CONCLUSIONES

1. INTRODUCCION: PAPEL DE LAS CAPAS DELGADAS EN LOS

CIRCUITOS INTEGRADOS MONOLITICOS.

Transistores y circuitos: Evolucin de la tecnologa de fabricacin

desde el primer transistor (fig. 1) hasta los modernos circuitos

integrados

Ao TECNOLOGA Ao TECNOLOGA

1947 Transistor de punta de contac. 1960 Fotolitografa

1948 Transistor de unin 1960 Transistor MOS

1950 Crecimiento monocristal 1968 Implantacin inica

1954 Transistor de unin de Si 1970 Memoria en circuito integrado

1956 Proceso de difusin doble 1971 Microprocesador

1959 Circuito integrado 1970-80 Litografa de elecr. y Rayos X

1960 Proceso planar 1990-00 CI de ULSI

1960 Proceso epitaxial >2000

Puntos Cunticos, Redes

Neuron., Interconex. ptica, etc

Tendencia actual de integracin: Ley de Moore:

El no. de componentes por chip se duplica

cada 18 meses La reduccin progresiva

del tamao de los componentes impone

exigencias muy estrictas en cuanto a la calidad

de las capas depositadas

1. INTRODUCCION: PAPEL DE LAS CAPAS DELGADAS EN LOS CIRCUITOS INTEGRADOS MONOLITICOS

(CONTN).

Aos 1947: Primer transistor de

silicio, junto con la de los

descubridores en los laboratorios

Bell: Schokley, Bardeen, Brittain

50 aos despus....

Circuito integrado

10 aos despus: IBM Ramac 305

(5MB, 50x24 , 1000kg, 50,000$)

2. ESTRUCTURA DE LAS CAPAS DE UN CIRCUITO

INTEGRADO:

Esquema de la estructura de un circuito integrado tpico de Si

Transistor MOS (ver fig. 2).

Notar diferentes niveles:

Substrato Si Soporte de la capa activa (epitaxial)

Capa activa Areas con dopaje diferente (p, i, n) y por tanto

con props elctricas diferentes. Permite la integracin de

diversos componentes.

Interconexiones y capas intermedias de separacin

Diferentes tipos de capas: aislantes, conductoras, barrera,

pasivantes, contactos, separacin de nivel, mscaras de

difusin, etc.

Diferentes tecnologas: CVD, PVD, Implantacin, ataque qumico,

etc

Materiales mas comunes: Si-epi, Poli-Si, SiO

2

(trmico y

depositado), Si

3

N

4

, TiSi

2

, Al, W, etc.

Fig. 2

Fuente

Puerta

Drenador

P-Si

Metal 2 (aleacin Al)

Metal 1

SiO

2

SiO

2

Si- epi

W

W

Siliciuro

3. TECNOLOGIA PLANAR: FOTOLITOGRAFIA

Esquema de la integracin sobre la superficie de una oblea de

diferentes componentes (resistencia, diodo, transistor, etc.) de un

circuito integrado hipottico

Esquema: Integracin de circuitos repetidos (chip) en una oblea de Si

2

1

3

4

5

resistencia

diodo

transistor

condensador

Metal inter-

conexin

p p p

p

n n n n

p

+

n

+

n

1 2 3

4

5

Capa

epitaxial

SiO

2

Oblea de Si

resistencia diodo

transistor condens.

3. TECNOLOGIA PLANAR: FOTOLITOGRAFIA (CONTN).

Fundamento de la tecnologa planar: Delimitacin de reas

(ventanas) en la superficie de la oblea de Si para llevar a cabo en

esa rea el proceso requerido (deposicin de contactos, o aislantes,

dopaje por implantacin (o difusin), etc.

Esquema del proceso de delineacin de ventanas con formas

definidas en una capa aislante depositada sobre la capa epitaxial de

la oblea de silicio usando mscaras positivas (fotolitografa):

Mscara de vidrio

a) Deposicin fotoresina

b) Revelado fotoresina

Si

SiO

2

SiO

2

fotoresina

c) Ataque fotoresina

expuesta

d) Ataque SiO

2

SiO

2

e) Eliminacin fotoresina:

SiO

2

delineado

Si

Si

Si

Si

Luz ultravioleta

3. TECNOLOGIA PLANAR: FOTOLITOGRAFIA (CONTN).

Integracin a pequea escala:

Utilizacin de mscaras de tamao nanomtrico mediante

reduccin fotogrfica.

Repeticin de motivos para cubrir toda la superficie de la oblea

Proyeccin de la mscara sobre la superficie de toda la oblea para

proceso de fotolitografa

Equipo ptico de delineacin de estructuras por fotolitografa:

3. TECNOLOGIA PLANAR: FOTOLITOGRAFIA (CONTN)

Etapas de preparacin de la capa de resina (resist) mediante el

mtodo de rotacin (spinner)

oblea

mesa

giratoria

resina

1. Sujecin de la oblea 2. Depsito de la resina

3. Rotacin de la oblea y

distribucin de la resina

4. Oblea recubierta con la

capa de resina

3. TECNOLOGIA PLANAR: FOTOLITOGRAFIA (CONTN)

Problemas asociados al ataque de la capa aislante (SiO

2

) depositada

debajo de la resina. Tcnicas empleadas:

Ataque qumico (isotrpico) baja resolucin en la delineacin de

la ventana (fig. 6a)

Ataque inico mediante tcnicas de plasma (anisotrpico)

Formacin de paredes verticales (fig. 6b)

Notar: Influencia en la resolucin en la delineacin del circuito

Uso de iluminacin de longitud de onda corta para aumentar la

resolucin (radiacin UV, rayos X, haz de e

-

).

Delineacin sobre capa de SiO

2

Ataque hmedo (sol. HF)

Resina

SiO

2

Ataque seco con plasma (iones F

-

)

Si

a) Ataque isotrpico b) Ataque anisotrpico

Esquema de las tcnicas de ataque empleadas en

fotolitografa para la delineacin de ventanas en

las capas de aislantes

4. PREPARACION DEL SUBSTRATO.

Fabricacin de silicio monocristalino:

Diferentes tcnicas para la cristalizacin del silicio. La ms

utilizada es la de Czochralski

Esquema de la tcnica de Czochralski para el crecimiento de

Si monocristalino

Descripcin del mtodo de crecimiento: En el interior de un horno

de alta la temperatura se hace girar un cristal-semilla de silicio, que

est en contacto con silicio calentado hasta la temperatura de

fusin. Lentamente, se extrae el cristal semilla desplazndolo

verticalmente hacia arriba de forma que el silicio lquido se enfre y

quede pegado en la semilla. El silicio enfriado cristaliza como

cristal nico (monocristal).

Sistema de giro y

desplazamiento

vertical

Horno de alta

temperatura

Silicio fundido

Tubo de cuarzo

Cristal semilla

Si mono-

cristalino

Crisol

3. PREPARACION DEL SUBSTRATO (CONTN).

Crecimiento de la capa epitaxial de silicio:

Se utiliza la tcnica de CVD a partir de la descomposicin de

SiCl

4

a alta temperatura.

Esquema de la tcnica:

Notar la inclinacin del soporte de las obleas, que tiene por

objeto compensar la perdida de gases debido al consumo a la

entrada al reactor.

Esquema de un sistema de deposicin de capas

epitaxiales de Si

Gases de reaccin:

HCL, H

2

, SiCl

4

,

dopante, purga, etc.

Sistema

de vaco

Horno

Obleas de silicio

Soporte

5. CRECIMIENTO Y DEPOSICIN DE CAPAS AISLANTES

Crecimiento de capas de SiO

2

por oxidacin trmica para aplicacin

como aislante de puerta de circuitos MOS y para xido de campo:

Reaccin : Si (sol) + O

2

(gas) SiO

2

(sol).

Calidad del xido de silicio trmico: La ausencia de defectos en el

interior de la capa y en la interfase SiO

2

/Si hace que este material

tenga unas propiedades elctricas ptimas

Micrografa obtenida por HRTEM de la interfase SiO

2

/Si

(Ntese el grado de perfeccin de la interfase)

T 900-1100 C

5. CRECIMIENTO Y DEPOSICION DE CAPAS AISLANTES (CONTN).

Aplicacin: Aislante de puerta y de delimitacin del rea de circuitos

en transistores MOS

Tcnica de oxidacin selectiva (LOCOS) a travs de una mscara de

Si

3

N

4

utilizando tcnicas de fotolitografa para formar el xido de

puerta en un circuito MOS. Notar el efecto de la penetracin del

xido por debajo de la mscara formado el denominado pico de

pjaro en la regin del borde, que limita la resolucin en la

delineacin del rea del xido.

Tcnica de oxidacin local del silicio (LOCOS) para formar el

aislante de puerta:

a) deposicin de mscaras de Si

3

N

4

, y delineacin de la

ventana mediante tcnicas de fotolitografa

b) oxidacin trmica,

c) disolucin de la mscara

Mscara de

Si

3

N

4

Si

SiO

2

a)

b)

c)

SiO

2

Si

Si

SiO

2 Efecto de pico

de pjaro

5. CRECIMIENTO Y DEPOSICION DE CAPAS AISLANTES (CONTN).

Deposicin de capas aislantes mediante tcnicas de CVD:

Mtodos tpicos de deposicin del SiO

2

:

Temperaturas bajas (300-500 C):

SiH

4

+ O

2

SiO

2

+ 2 H

2

(APCVD y LPCVD)

SiH

4

+ 2 N

2

O SiO

2

+ 2 N

2

+H

2

4 PH

3

+ 5 O

2

2 P

2

O

5

+ 6 H

2

Temperaturas intermedias (500-800 C):

Descomposicin piroltica del TEOS

Si(OC

2

H

5

)

4

SiO

2

+ subproductos (PECVD)

Temperaturas altas ( 900 C):

SiCl

2

H

2

+ 2 N

2

O SiO

2

+ 2N

2

+ 2 HCl (LPCVD)

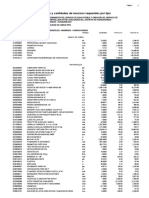

Datos comparativos:

parmetro ox. trmico

(1000 C)

SiH

4

+ O

2

(450 C)

TEOS

(700 C)

SiCl

2

H

2

+ 2N

2

O

(900 C)

Composicin SiO

2

SiO

x

H

y

SiO

2

SiO

x

Cl

y

Densidad 2.2 2.1 2.2 2.2

Indice Refraccin 1.46 1.44 1.46 1.46

Rupt. Dielctrica

(10

6

V/m)

>10 8 10 10

Vel. Ataque HF

(A/min)

440 1200 450 450

Recubr. escalones

(A/min)

- no conforme conforme conforme

adiccin

de dopante

6. IMPLANTACIN DE DOPANTES

Esquema de un implantador de impurezas en

semiconductores

Proceso de implantacin de dopantes en una regin delimitada por

una ventana de SiO

2

, delineada mediante fotolitografa

Haz de iones As

+

(100 keV)

a) Implantacin del dopante (As)

b) Tratamiento trmico a 950-1050 C para la re-

distribucin hacia el interior

Si

SiO

2

SiO

2

Regin implantada

Si

7. DEPOSICION DE CONTACTOS Y CAPAS CONDUCTORAS.

Materiales tpicos empleados:

Al y Cu para interconexiones,

poli-Si (silicio policristalino) y Siliciuros (Ti

2

Si, Co

2

Si) para contacto

de puerta en circuitos MOS

TiN como barrera antidifusin de contactos entre Si y Al

W para rellenar agujeros pasantes (vas) para contactos inter-nivel.

Problemas asociados al uso del Al como material de contacto con

Si:

Formacin de spikes debido a la disolucin del Si en el Al lo cual

da lugar a corto circuitos en uniones metal/Si(n).

Se evita utilizando la aleacin Al-Si (1%) para el metal de contacto

Electromigracin Sustitucin por otros metales (Cu).

n

+

n

+

Aguja de Al

Aluminio

Oxido de Silicio

Silicio tipo p

Formacin de spikes en contactos de aluminio (en una unin

n

+

- p) debido a la difusin del Si y del Al en direcciones

opuestas

5. DEPOSICION DE CONTACTOS Y CAPAS CONDUCTORAS (CONTN)

Tcnicas de deposicin: Bombardeo catdico y deposicin qumica

en fase vapor (CVD).

Ventaja de bombardeo catdico: T deposicin baja.

Ventaja de CVD: Recubrimiento de escalones Importante para

llenar agujeros pasantes (vas) en la interconexin de una capa

metlica con otra de nivel superior. Ejemplo: capas de

tungsteno (W):

2 WF

6

(gas) + 3 Si (substr.) 2 W (depos.) + 3 SiF

4

(gas)

(inicial)

WF

6

+ 3H2 W + 6 HF (capas posteriores)

Problemas asociados al recubrimiento de escalones Necesidad

de llevar a cabo una planarizacin mediante el empleo de capas de

SiO

2

dopadas con B P (vidrios BPSG), con punto de fusin bajo,

capaces de fluir a temperaturas moderadas y suavizar escalones.

SiO

2

sin dopar

SiO

2

dopado con

P B (BPSG)

Si Si

Efecto de la adiccin de dopantes a las capas de SiO

2

en el

recubrimiento de escalones en la superficie del Si: a) sin

dopante, b) con dopantes de P o B, (despus de un

tratamiento trmico para hacer fluir el vidrio sobre la

superficie).

a)

b)

5. DEPOSICION DE CONTACTOS Y CAPAS CONDUCTORAS (CONTN).

Tendencia actual: Uso de multi-cmaras (cluster tools) conectadas

entre s a travs de una cmara central de distribucin para llevar a

cabo las diferentes etapas del procesado sin exponer las obleas al

aire. Ventajas: Posibilidad de robotizacin y ahorro de superficie

de Sala limpia.

Fotografa de una multicmara, mostrando en un

lateral una de las cmaras con una oblea en

proceso de ser tratada

8. RESUMEN Y CONCLUSIONES

Las capas delgadas son un componente esencial en la preparacin

de circuitos integrados, cumpliendo diferentes misiones: capa

activa de integracin de los componentes electrnicos, contactos e

interconexiones, aislante de puerta y de campo en los circuitos

MOS, aislante de inter-nivel, mscaras de difusin, capas

pasivantes, etc.

Cada una de estas misiones exige a su vez caractersticas

especificas: p.e., el SiO

2

cuando acta como aislante de puerta es de

espesor muy pequeo y debe tener ruptura dielctrica elevada y

densidad de estados muy baja, mientras que como aislante de inter-

nivel es de mucho mayor espesor y puede contener un mayor

nmero de defectos.

En cualquier caso, el aumento del nivel de integracin y la

consiguiente reduccin de tamao de los circuitos electrnicos ha

obligado a resolver numerosos problemas asociados con la calidad,

ausencia de defectos y compatibilidad de las capas depositadas

sobre la oblea de silicio.

Las tcnicas ms comunes utilizadas en la tecnologa de micro-

electrnica del Si estn basadas en las de CVD para materiales

aislantes (generalmente basadas en plasma) y en las de bombardeo

catdico para materiales conductores. Las tcnicas de plasma

tambin se utilizan para el ataque qumico en los procesos de

fotolitografa.

El grado de desarrollo que han alcanzado estas tcnicas as como el

de los materiales utilizados en la microelectrnica est siendo

aprovechado para su aplicacin en otros campos: sensores,

dispositivos optoelectrnicos, recubrimientos cermicos, etc.

You might also like

- Diagramas de Transformación Isotérmica Gerardo HuertaDocument7 pagesDiagramas de Transformación Isotérmica Gerardo HuertaGerardo HuertaNo ratings yet

- Reactivo de Cloro Libre DPDDocument14 pagesReactivo de Cloro Libre DPDgnoguera780No ratings yet

- Repaso QuimicaDocument13 pagesRepaso QuimicaPAULO GUERRERONo ratings yet

- Ensayo DesengrasanteDocument8 pagesEnsayo DesengrasanteCesar SalazarNo ratings yet

- Practica Nº2Document4 pagesPractica Nº2Anibar Yamil Solamayo VediaNo ratings yet

- C 11 Dif. MagmaticaDocument35 pagesC 11 Dif. MagmaticaAlbani NietoNo ratings yet

- Diapositiva de DestilacionDocument25 pagesDiapositiva de DestilacionMiguel Reynaldo CabreraNo ratings yet

- Ejercicos DanteDocument4 pagesEjercicos DanteJaime Antonio Martinez HernandezNo ratings yet

- Cuestionario Elaboración de PapelDocument5 pagesCuestionario Elaboración de PapelDayana B. Villena100% (2)

- Plantilla APADocument16 pagesPlantilla APAneyer coca clarosNo ratings yet

- Abs. Practica 1 ESIQIEDocument15 pagesAbs. Practica 1 ESIQIERoberto Ramirez Trinidad100% (1)

- Taller Dilatación Térmica ActualizadoDocument5 pagesTaller Dilatación Térmica Actualizadojuan sebastian garciaNo ratings yet

- Bonba de Agua y SoldadoDocument2 pagesBonba de Agua y SoldadoMihai BouwmeesterNo ratings yet

- Informe #001-PreliquidacionDocument16 pagesInforme #001-PreliquidacionYESI Y LA DULCE REVELACIONNo ratings yet

- CLASESDocument122 pagesCLASESFidelOrtizMhNo ratings yet

- Hornos 2Document5 pagesHornos 2Smith Valderrama ParedesNo ratings yet

- INSUMOS1Document3 pagesINSUMOS1Steven Torres QuinchoNo ratings yet

- Prueba de Refuerzo de Fisica 100Document5 pagesPrueba de Refuerzo de Fisica 100Blanca Lidia GarciaNo ratings yet

- Ejercítate 1 La Tabla Periódica-1Document6 pagesEjercítate 1 La Tabla Periódica-1John OliverNo ratings yet

- Experimentos de Ciencia A Conciencia Efecto de La Lluvia Ácida PDFDocument1 pageExperimentos de Ciencia A Conciencia Efecto de La Lluvia Ácida PDFFabiola GutierrezNo ratings yet

- Clasificacion AfirmadoDocument14 pagesClasificacion AfirmadoJuanDiegoCcanchiNo ratings yet

- CSNRI PS SP DiamondWrap 05nov19Document2 pagesCSNRI PS SP DiamondWrap 05nov19Williams SmailliwNo ratings yet

- Milagro Planilla Computo 60m2Document2 pagesMilagro Planilla Computo 60m2GabrielaGarcíaNo ratings yet

- Agentes MetalurgicosDocument31 pagesAgentes MetalurgicosGiseeTaricoNo ratings yet

- Estado Gaseoso - Lab 4Document22 pagesEstado Gaseoso - Lab 4Juan Marcelo Tenorio Barboza75% (8)

- Práctica de Combustión de Exámenes Pasados PDFDocument3 pagesPráctica de Combustión de Exámenes Pasados PDFJuan Esteban Cordova AliNo ratings yet

- Certificado de Estudios #000013-2023-Umragt-Figmmg-UnmsmDocument4 pagesCertificado de Estudios #000013-2023-Umragt-Figmmg-UnmsmMARCOS ORLANDO CALLA CONDORINo ratings yet

- TermocuplasDocument13 pagesTermocuplasdavidrafaelbastardopiamoNo ratings yet

- NITROGENODocument3 pagesNITROGENOYeshua FonsecaNo ratings yet

- Anexo De-9 Catalogo de Conceptos Proteccion InteriorDocument8 pagesAnexo De-9 Catalogo de Conceptos Proteccion InteriorBalderas Rosas WilibaldoNo ratings yet