Professional Documents

Culture Documents

Safe Driving Using Mobile Phones

Uploaded by

Jagadeesh KumarCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Safe Driving Using Mobile Phones

Uploaded by

Jagadeesh KumarCopyright:

Available Formats

Safe Driving Using Mobile Phones

CHAPTER-1 INTRODUCTION

1.1 MOTIVATION

Driving is complex and challenging. A simple way to make driving safer is to reduce the number of non-driving and distracting activities you undertake while driving. Research shows that dialing and talking on a mobile phone while driving can lead to

Riskier decision making Deciding when it is safe to turn in traffic is a complex task. Using a mobile phone while driving affects judgment and concentration and you may fail to choose a safe gap. When making a decision to turn across oncoming traffic, you also tend not to consider the environmental conditions such as, when it is raining or the roads are slippery. If you dont make safe turns you could crash.

Slower reactions You generally react slower when using a mobile phone, particularly when youre deep in conversation. You may take longer to respond to traffic signals or completely miss them.

Slower and less controlled braking During a mobile phone call your brake reaction time is slower, and you break with more force and less control which results in shorter stopping distances available between yourself and the car in front.

Wandering out of your lane Youre more likely to wander out of your lane when youre using a mobile phone, even on a straight road with little traffic.

DEPARTMENT OF ECE Page 1 VYCET

Safe Driving Using Mobile Phones

Not being alert to your surroundings When using a mobile phone, you tend to spend less time checking your mirrors and whats going on around you. This affects your ability to monitor and negotiate traffic safely.

1.2 PROBLEM DEFINITION

In the fast-paced society of today, we are focused on arriving at our destination as quickly as possible. However, with this lifestyle, we are not always aware of all the dangerous conditions that are experienced while operating an automobile. Factors such as sudden vehicle maneuvers and hazardous road conditions, which often contribute to accidents, are not always apparent to the person behind the wheel. In recent years, there has been tremendous growth in smart phones embedded with numerous sensors such as accelerometers, Global Positioning Systems (GPSs), magnetometers, multiple microphones, and even cameras. The scope of sensor networks has expanded into many application domains such as intelligent transportation systems that can provide users with new functionalities previously unheard of Experimental automobiles in the past have included certain sensors to record data preceding test crashes, After analysis, crash scenarios are stored and analyzed with real-time driving data to potentially recognize a future crash and actually prevent it. With more than 10 million car accidents reported in the United States each year, car manufacturers have shifted their focus of a passive approach, e.g., airbags, seat belts, and antilock brakes, to more active by adding features associated with advanced driverassistance systems (ADASs), e.g., lane departure warning system and collision avoidance systems. However, vehicles manufactured with these sensors are hard to find in lower priced economical vehicles as ADAS packages are not cheap add-ons. In addition, older vehicles might only have passive safety features since manufacturers only recently began to introduce an effective driver assist. Since sensors ultimately add onto the cost of a vehicle initially and

DEPARTMENT OF ECE Page 2 VYCET

Safe Driving Using Mobile Phones

cannot be affordably upgraded, we target a mobile Smartphone as an alternative device for ADASs that can assist the driver and compliment any existing active safety features. Given its accessibility and portability, the Smartphone can bring a driver assist to any vehicle without regard for on-vehicle communication system requirements.

1.3 OBJECTIVE OF THE PROJECT

In this chapter introduction of the SAFE DRIVING USINGMOBILE

PHONES are discussed. It gives overall view of the project design and the related

literature and the environment to be considered. Chapter wise organization of the thesis and the appendices is given at the end of this chapter. At first we discuss the main processing done using ARM7TDMI-S and then what is the process that can be automated which is within the scope of the work. Then we discuss the implementation aspects.

1.4 LIMITATION OF PROJECT

The driver has to place the mobile at the same place when he enters the car. The driver has to lift the call manually. In this we are not stopping the car we are just reducing the speed to the car to 10-20 rpm.

DEPARTMENT OF ECE

Page 3

VYCET

Safe Driving Using Mobile Phones

CHAPTER-2 LITERATURE SURVEY

2.1 EXISTING SYSTEM

Muting Mobile.

Voice Mail Converter No information to caller

2.2 DISADVANTAGES OF EXISTING SYSTEM

Keep some data on existing points

2.3 PROPOSED SYSTEM

Automatic attend of the call. Gives information about the Driver. Only Emergency Call will connect to the User.

2.4 CONCLUSION

The former section consists of Ignition Starter; the microcontroller gives the signal to the mobile. When the signal is received by the mobile it immediately changes in to Driving Mode. In driving mode, if someone is calling it automatically attends the call and gives response only for the emergency call.

DEPARTMENT OF ECE

Page 4

VYCET

Safe Driving Using Mobile Phones

CHAPTER-3 SYSTEM ENVIRONMENT

3.1. INTRODUCTION

The flat form for this project is based on Embedded System. An Embedded system is a special-purpose system in which the computer is completely encapsulated by the device it controls. Unlike a general-purpose computer, such as a personal computer, an embedded system performs one or a few pre-defined tasks, usually with very specific requirements. Since the system is dedicated to specific tasks, design engineers can optimize it, reducing the size and cost of the product. Embedded systems are often mass-produced, so the cost savings may be multiplied by millions of items. An embedded system is a special-purpose computer system designed to perform a dedicated function. Unlike a general-purpose computer, such as a personal computer, an embedded system performs one or a few pre-defined tasks, usually with very specific requirements. Since the system is dedicated to specific tasks, design engineers can optimize it, reducing the size and cost of the product. Embedded system comprises of both hardware and software. Embedded system is fast growing technology in various fields like industrial automation, home appliances, automobiles, aeronautics etc. Embedded technology is implemented to perform a specified task and the programming is done using assembly language programming or embedded C. Ours being a developing country the power consumption is increasing on large scale to meet the growing need of the people. Power generation is widely based on the non-renewable sources and these sources being depleting some means have to be found for power saving.

DEPARTMENT OF ECE

Page 5

VYCET

Safe Driving Using Mobile Phones

3.2. DESIGN OF EMBEDDED SYSTEMS

Intelligent, programmable and computing electronic device designed to perform specific tasks based on a fixed time frame. An embedded system is a combination of hardware and software, perhaps with some mechanical and other components designed to perform a specific task.

Figure 3.1 Embedded System Design. Electronics usually uses either a microprocessor or a microcontroller. Some large or old systems use general-purpose mainframes computers or minicomputers.

3.3. CHARACTERISTICS OF EMBEDDED SYSTEM

o o It is very reactive and real time constrained. Increasingly high performance.

Page 6

DEPARTMENT OF ECE

VYCET

Safe Driving Using Mobile Phones

o o Application specific processor design can be significant component of embedded system. It acts as a single function not used as general purpose.

3.4. REQUIREMENTS OF EMBEDDED SYSTEM

Functional Requirement o o o o o o o o o o o o Direct digital control Data collection Man-machine interaction

Temporal Requirement Tasks may have dead lines Minimal error detection latency Timing requirement Human-interface requirements.

Dependability Requirement Reliability Safety Availability Maintainability Security

Basic Block diagram of Embedded System

ASICs ANALOG I/Os

PROCESSOR

MEMORY

Figure 3.2 Basic Block diagram of Embedded System

DEPARTMENT OF ECE

Page 7

VYCET

Safe Driving Using Mobile Phones

Processor Processor is a digital circuit designed to perform computational tasks. An Embedded system consists of single purpose processor rather than general purpose processor. Single purpose processor better then general-purpose processor.

ASICs (Application Specific ICs) It is the silicon chip with an array of unconnected transistors. It includes gate arrays and standard cell ICs. Memory A fixed size volatile memory such as DRAM or SRAM & non-volatile memory such as EPROM or Flash, connected to microcontroller/processor is used. Peripherals According to the block diagram analog I/O consists of the several peripherals according to the requirement or the application. Some of the peripherals are listed below

o Timer, counter o UART o Pulse Width Modulators o LCD controller o DMA controller o Keypad controller o Stepper motor controller o ADC converter o Real Time clock

DEPARTMENT OF ECE

Page 8

VYCET

Safe Driving Using Mobile Phones

CHAPTER-4 HARDWARE IMPLEMENTATION OF THE PROJECT

4.1. INTRODUCTION

This chapter briefly explains about the Hardware Implementation of the project. It discusses the design and working of the design with the help of block diagram and circuit diagram and explanation of circuit diagram in detail. It explains the features, timer programming, serial communication, interrupts of LPC2148 microcontroller. It also explains the various modules used in this project.

POWER SUPPLY

EYE BLINK

MOTOR

RELAY

MEMS ARM LCD BUZZER

RF tx/txsection

GSM

SWITCH

Figure 4.1 Block Diagram of Safe Driving Using Mobile Phones

DEPARTMENT OF ECE

Page 9

VYCET

Safe Driving Using Mobile Phones

This project is implemented in an effective way to improve the safety. When the driver enters the car the mobile automatically goes into the driving mode. When the driver is getting call for the first time the arm microcontroller detect and gives a pre-recorded voice (the person you are calling is in driving mode). If again the caller is calling for the second time the rf transmitter (TWS-434) in the mobile section send the signal to the rf section

(RWS-434)that is placed on the dashboard and the buzzer gets activated . if the driver attends the call the rf section on the dash board sends a signal to the mobile section using the MAX232 and the arm controller activate the relay and decreases the speed of the car. The other way of accidents causes by drunken driving or sleepy driving. We are also using eye blink sensors. The driver has to wear the eye glasses , if the driver closes his eyes arm receives the signal if the person doesnt open his eyes more 3seconds the buzzer gets activated and the seep of the vehicle gets reduced. This project mainly consists of two sections which are the mobile section and the dash board section. The mobile section consists arm Micro Controller (ARM7) FAMILY, gsm mobile, relays, rf transmitter and eye blink sensor. The second section dashboard section consists of RF Reciver, LPC2148 MICROCONTROLLER. In this section all the devices are connected to the arm microcontroller. The arm controller receives the signal from the sensors, gsm module, and RF section and controls the devices that are connected. When the RF section receives the signal it sends to the Micro controller and its acts according to the signal.

POWER SUPPLY

RF SECTION

MCU

DRIVER UNIT

MOTOR

Figure 4.2 Dash board section

DEPARTMENT OF ECE Page 10 VYCET

Safe Driving Using Mobile Phones

CHAPTER-5 PROJECT DESCRIPTION

5.1 HARDWARE SPECIFICATIONS

The following hardware components are used in building the entire system

5.1.1 ARM BASED LPC2148 5.1.1.1 INTRODUCTION

The LPC2148 microcontrollers are based on a 32/16 bit ARM7TDMI-S CPU with real-time emulation and embedded trace support, that combines the microcontroller with embedded high speed flash memory ranging from 32 Kbytes to 512 Kbytes. A 128-bit wide memory interface and unique accelerator architecture enable 32-bit code execution at the maximum clock rate. For critical code size applications, the alternative 16-bit Thumb mode reduces code by more than 30 % with minimal performance penalty. Due to their tiny size and low power consumption, LPC2141/2/4/6/8 are ideal for applications where miniaturization is a key requirement, such as access control and point-ofsale. A blend of serial communications interfaces ranging from a USB 2.0 Full Speed device, multiple UARTS, SPI, SSP to I2Cs and on-chip SRAM of 8 Kbytes up to 40 Kbytes, make these devices very well suited for communication gateways and protocol converters, soft modems, voice recognition and low end imaging, providing both large buffer size and high processing power. Various 32-bit timers, single or dual 10-bit ADC(s), 10-bit DAC, PWM channels and 45 fast GPIO lines with up to nine edge or level sensitive external interrupt pins make these microcontrollers particularly suitable for industrial control and medical systems.

5.1.1.2 FEATURES

o 16/32-bit ARM7TDMI-S microcontroller in a tiny LQFP64 package.

DEPARTMENT OF ECE

Page 11

VYCET

Safe Driving Using Mobile Phones

o 8 to 40 kB of on-chip static RAM and 32 to 512 kB of on-chip flash program memory. o 128 bit wide interface/accelerator enables high speed 60 MHz operation. o In-System/In-Application Programming (ISP/IAP) via on-chip boot-loader software. o Single flash sector or full chip erase in 400 ms and programming of 256 bytes in 1 msec. o Embedded ICE RT and Embedded Trace interfaces offer real-time debugging with the on-chip Real Monitor software and high speed tracing of instruction execution. o USB 2.0 Full Speed compliant Device Controller with 2 kB of endpoint RAM. In addition, the LPC2146/8 provides 8 kB of on-chip RAM accessible to USB by DMA. o One or two (LPC2141/2 vs. LPC2144/6/8) 10-bit A/D converters provide a total of 6/14 analog inputs, with conversion times as low as 2.44 sec per channel. o Single 10-bit D/A converter provide variable analog output. o Two 32-bit timers/external event counters (with four capture and four compare channels each), PWM unit (six outputs) and watchdog. o Low power real-time clock with independent power and dedicated 32 kHz clock input. o Multiple serial interfaces including two UARTs (16C550), two Fast I2C-bus (400 Kbit/s), SPI and SSP with buffering and variable data length capabilities. o Vectored interrupt controller with conFigureurable priorities and vector addresses. o Up to 45 of 5 V tolerant fast general purpose I/O pins in a tiny LQFP64 package. o Up to nine edge or level sensitive external interrupt pins available. o 60 MHz maximum CPU clock available from programmable on-chip PLL with settling time of 100 sec.

DEPARTMENT OF ECE

Page 12

VYCET

Safe Driving Using Mobile Phones

o On-chip integrated oscillator operates with an external crystal in range from 1 MHz to 30 MHz and with an external oscillator up to 50 MHz o Power saving modes include idle and Power-down. o Individual enable/disable of peripheral functions as well as peripheral clock scaling for additional power optimization. o Processor wake-up from Power-down mode via external interrupt, USB, Brown-Out. o Single power supply chip with Power-On Reset (POR) and BOD circuits CPU operating voltage range of 3.0 V to 3.6 V (3.3 V 10 %) with 5 V tolerant I/O Pads.

5.1.1.3 APPLICATIONS

o Industrial control o Medical systems o Access control o Point-of-sale

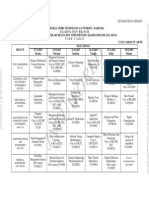

Device Number of pin LPC 2141 LPC 2142 LPC 2144 LPC 2146 64 32KB+8KB On-chip SRAM Endpoint USB RAM 64 8KB 2KB 32KB On chip FLASH Number of 10 bit ADC channels 6 Number of 10 bit DAC channels Note

64

16KB

2KB

64KB

UART with full modem

64

16KB

2KB

128KB

14

2KB

256KB

14

interface Uart1 with full modem interface

DEPARTMENT OF ECE

Page 13

VYCET

Safe Driving Using Mobile Phones

LPC 2148 Uart1 with full 64 32KB+8KB 2KB 512KB 14 1 modem interface

Table 5.1 Device information

5.1.1.4 ARCHITECTURAL OVERVIEW

The LPC2148 consists of an ARM7TDMI-S CPU with emulation support, the ARM7 Local Bus for interface to on-chip memory controllers, the AMBA Advanced Highperformance Bus (AHB) for interface to the interrupt controller, and the VLSI Peripheral Bus (VPB, a compatible superset of ARMs AMBA Advanced Peripheral Bus) for connection to on-chip peripheral functions. The LPC2148 conFigures the ARM7TDMI-S processor in little-endian byte order. AHB peripherals are allocated a 2 megabyte range of addresses at the very top of the 4 gigabyte ARM memory space. Each AHB peripheral is allocated a 16 kB address space within the AHB address space. LPC2148 peripheral functions (other than the interrupt controller) are connected to the VPB bus. The AHB to VPB Bridge interfaces the VPB bus to the AHB bus. VPB peripherals are also allocated a 2 megabyte range of addresses, beginning at the 3.5 gigabyte address point. Each VPB peripheral is allocated a 16 kB address space within the VPB address space. The connection of on-chip peripherals to device pins is controlled by a Pin Connect Block. This must be conFigured by software to fit to specific application requirements for the use of peripheral functions and pins.

5.1.1.5 ARM7TDMI-S PROCESSOR

The ARM7TDMI-S is a general purpose 32-bit microprocessor, which offers high performance and very low power consumption. The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler than those of micro programmed Complex Instruction Set Computers.

DEPARTMENT OF ECE

Page 14

VYCET

Safe Driving Using Mobile Phones

This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective processor core. The main block diagram of ARM7TDMI-S processor is shown below. Pipeline techniques are employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory. The ARM7TDMI-S processor also employs a unique architectural strategy known as THUMB, which makes it ideally suited to high-volume applications with memory restrictions, or applications where code density is an issue. The key idea behind THUMB is that of a super-reduced instruction set. Essentially, the ARM7TDMI-S processor has two instruction sets o The standard 32-bit ARM instruction set. o A 16-bit THUMB instruction set. The THUMB sets 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARMs performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because THUMB code operates on the same 32-bit register set as ARM code. The THUMB code is able to provide up to 65% of the code size of ARM, and 160% of the performance of an equivalent ARM processor connected to a 16-bit memory system.

5.1.1.6 ON-CHIP FLASH MEMORY SYSTEM

The LPC2141/2/4/6/8 incorporates a 32 kB, 64 kB, 128 kB, 256 kB, and 512 kB Flash memory system respectively. This memory may be used for both code and data storage. Programming of the Flash memory may be accomplished in several ways over the serial built-in JTAG interface, using In System Programming (ISP) and UART0, or by means of In Application Programming (IAP) capabilities.

DEPARTMENT OF ECE Page 15 VYCET

Safe Driving Using Mobile Phones

The application program, using the IAP functions, may also erase and/or program the Flash while the application is running, allowing a great degree of flexibility for data storage field firmware upgrades, etc. When the LPC2148 on-chip boot loader is used, 32 kB, 64 kB, 128 kB, 256 kB, and 500 kB of Flash memory is available for user code. The LPC2148 Flash memory provides minimum of 100,000 erase/write cycles and 20 years of data-retention.

Figure 5.1. Block diagram of LPC2148

DEPARTMENT OF ECE Page 16 VYCET

Safe Driving Using Mobile Phones

5.1.1.7 ON-CHIP STATIC RAMS (SRAM)

On-chip Static RAM (SRAM) may be used for code and/or data storage. The on-chip SRAM may be accessed as 8-bits, 16-bits, and 32-bits. The LPC2148 provide 8/16/32 kB of static RAM respectively. The LPC2148 SRAM is designed to be accessed as a byteaddressed memory. Word and half word accesses to the memory ignore the alignment of the address and access the naturally-aligned value that is addressed (so a memory access ignores address bits 0 and 1 for word accesses, and ignores bit 0 for half word accesses).Therefore valid reads and writes require data accessed as half words to originate from addresses with address line 0 being 0 and data accessed as words to originate from addresses with address lines 0 and 1 being 0 (addresses ending with 0, 4, 8, and C in hexadecimal notation). This rule applies to both off and on-chip memory usage. The SRAM controller incorporates a write-back buffer in order to prevent CPU stalls during back-to-back writes. The write-back buffer always holds the last data sent by software to the SRAM. This data is only written to the SRAM when another write is requested by Software (the data is only written to the SRAM when software does another write).If a chip reset occurs, actual SRAM contents will not reflect the most recent write request (i.e. after a "warm" chip reset, the SRAM does not reflect the last write operation).

5.1.1.8 MEMORY MAPS

The LPC2141/2/4/6/8 incorporates several distinct memory regions, shown in the following Figurers.

5.1.1.9 LPC2148 memory re-mapping and boot block Memory map concepts and operating modes

The basic concept on the LPC2141/2/4/6/8 is that each memory area has a "natural" location in the memory map. This is the address range for which code residing in that area is written. The bulk of each memory space remains permanently fixed in the same location, eliminating the need to have portions of the code designed to run in different address ranges.

DEPARTMENT OF ECE Page 17 VYCET

Safe Driving Using Mobile Phones

Figure 5.2 system memory map Because of the location of the interrupt vectors on the ARM7 processor, a small portion of the Boot Block and SRAM spaces need to be re-mapped in order to allow alternative uses of interrupts in the different operating modes described in Figure 5.2.

DEPARTMENT OF ECE

Page 18

VYCET

Safe Driving Using Mobile Phones

Address 0x0000 0000 0x0000 0004 0x0000 0008 0x0000 000C 0x0000 0010 0x0000 0014 0x0000 0018 0x0000 001C Exception Reset Undefined Instruction Software Interrupt Pre fetch Abort Data Abort Reserved IRQ FIQ

Table 5.2 ARM exception memory locations Mode Activation Usage The boot loader always executes after any Boot loader Hardware activation mode by any reset reset. The boot block interrupt vectors are mapped to the bottom of memory to allow handling exceptions and using interrupts during the boot loading Activated process. by boot loader when a valid user program signature is recognized in memory and boot leader operation is not User RAM mode Software activation by boot code forced. Interrupt vectors are not re Activated by a user program as desired . mapped and are found in the bottom Interrupt vectors are re mapped tp theof

User flash mode

Software activation by boot code

the flash memory bottom of the static RAM. Table 5.3 LPC 2148 memory mapping modes

5.1.1.10 MEMORY RE-MAPPING

In order to allow for compatibility with future derivatives, the entire Boot Block is mapped to the top of the on-chip memory space. In this manner, the use of larger or smaller flash modules will not require changing the location of the Boot Block (which would require changing the Boot Loader code itself) or changing the mapping of the Boot Block interrupt vectors.

DEPARTMENT OF ECE Page 19 VYCET

Safe Driving Using Mobile Phones

Memory spaces other than the interrupt vectors remain in fixed locations. The portion of memory that is re-mapped to allow interrupt processing in different modes includes the interrupt vector area (32 bytes) and an additional 32 bytes, for a total of 64 bytes. The re-mapped code locations overlay addresses 0x0000 0000 through 0x0000 003F. A typical user program in the Flash memory can place the entire FIQ handler at address 0x0000 001C without any need to consider memory boundaries. The vector contained in the SRAM, external memory, and Boot Block must contain branches to the actual interrupt handlers, or to other instructions that accomplish the branch to the interrupt handlers. There are three reasons this configuration was chosen o To give the FIQ handler in the Flash memory the advantage of not having to take a memory boundary caused by the remapping into account. o Minimize the need to for the SRAM and Boot Block vectors to deal with arbitrary boundaries in the middle of code space. o To provide space to store constants for jumping beyond the range of single word branch instructions. o Re-mapped memory areas, including the Boot Block and interrupt vectors, continue to appear in their original location in addition to the re-mapped address. o Minimize the need to for the SRAM and Boot Block vectors to deal with arbitrary boundaries in the middle of code space. o To provide space to store constants for jumping beyond the range of single word branch instructions. Re-mapped memory areas, including the Boot Block and interrupt vectors, continue to appear in their original location in addition to the re-mapped address.

5.1.1.11. GENERAL PURPOSE I/O

FEATURES 1. GPIO will give the direction control (whether the selected pin is used as input pin or output pin) of individual bits. It can be achieved by IODIR.

DEPARTMENT OF ECE Page 20 VYCET

Safe Driving Using Mobile Phones

2. We can set the values of register by writing one, produces high at the corresponding port pins, whereas writing zero will have no effect. It can be done by using IOSET. Whenever we use i.e. when we set any value we have to clear those bit using IOCLR. IOCLR will clear the particular bits we have selected. 3. After reset, by default all the I/O will act as input pins. PIN DESCRIPTION

Pin Name

Type

Description

P0.0 P0.31 P1.16 P1.31

Input/ Output

General purpose input/output. The number of GPIOs available depends on the use of functions.

Table 5.4 GPIO PIN Description. TheLPC2148 processor has totally four ports. 1. Port0 has 32 pins and all can be used as input/output. All pins of this port can be used as general purpose input/output. The number of pins available for input/output operation will depends on the use of alternate functions i.e. if we use less alternate functions more are the available input/outputs .Port Pins P0.24,P0.26,P0.27 are not available.

DEPARTMENT OF ECE

Page 21

VYCET

Safe Driving Using Mobile Phones

Figure 5.3 Pin diagram of LPC 2148 REGISTER DESCRIPTION As we seen in the above table it is clear that LPC2148 has two 32-bit general purpose input/output ports. For Port0 29 pins (24, 26, 27 are not available) out of 32 pins are available for GPIO functions and for port1 only 16 (0-15pins are not available) out of 32 are available for GPIO functions. Port0 and port1 are controlled by two groups of four registers (IOPIN, IOSET, IODIR and IOCLR) which are explained in detail below. There are four registers associated with the GPIO and are shown below

DEPARTMENT OF ECE

Page 22

VYCET

Safe Driving Using Mobile Phones

Gener ic Name Description Access Reset Value PORT0Address & Name PORT1Add ress & Name 0xE0028010 IO1PIN

IOPIN

GPIO Port Pin Value Register. The current status of the GPIO conFigured port Read pins can always be read from Only this register, regardless of pin direction and mode. GPIO Port Output Set Register. This register controls the state of output pins along with the IOCLR Read/ register. Writing 1 produces highs at the corresponding Write port pins. Writing zeros has no effect. GPIO Port Direction Control Read/ Register. This register is used to control the direction Write of each port pin. GPIO Port Output Clear Register. This register is used to control the state of output pins. Writing ones Write produces lows at the Only corresponding port pins and clears the corresponding bits in the IOSET register. Writing zeros has no effect.

NA

0xE0028000 IO0PIN

0x0000 0000

0xE0028004 IO0PIN

0xE0028014 IO1SET

IOSET

0x0000 0000

0xE0028008 IO0DIR

0xE0028018 IO1DIR

IODIR

0x0000 0000

0xE0028008 IO0DIR

0xE0028014 IO1SET

IOCL R

Table 5.5 GPIO Register Description. GPIO Port Pin Value Register This is a 32 bit register. In our project we are not using this register as we are selecting the particular port pins as outputs. Here we know the output pins. This register is used when we would like to know whether the particular port pins used as output or not.

DEPARTMENT OF ECE

Page 23

VYCET

Safe Driving Using Mobile Phones

IOPIN 310 Description GPIO pin value bits. Bit0 in IOPIN corresponds to P0.0.... Bit 31 in IOPIN corresponds to P0.31. Value after Reset undefined

Table 5.6 GPIO Port PIN Value Register (IOPIN Register) GPIO Port Output Set Register GPIO Output Set Register is a 32 bit register used to make the particular bits to high level output at the port pins if they are configured as GPIO in an output mode. Writing 1 makes a high level at the particular port pins, whereas writing 0 will have no effect. If any pin is configured as input then writing to IOSET has no effect.

IOSET 310 Description Output value SET bits. Bit0 in IOSET corresponds to P0.0.... Bit 31 in IOSET corresponds to P0.31. Value after Reset 0

Table 5.7 GPIO Port Output Set Register (IOSET Register) . GPIO Port Direction Register GPIO Direction Register is a 32 bit register used to control the direction of the pins whether the port pins used as input or output. If we write 1 then the corresponding port pin is selected or used as output. Direction bit for any pin must be set according to the pin functionality.

IOSET Description 310 Output value SET bits. Bit0 in IOSET corresponds to P0.0.... Bit 31 in IOSET corresponds to P0.31. Value after Reset 0

Table 5.8 GPIO Port Direction Register (IODIR Register).

DEPARTMENT OF ECE

Page 24

VYCET

Safe Driving Using Mobile Phones

GPIO Port Output Clear Register GPIO Output Clear Register is a 32 bit register used to produce a low level at port pins if they are configured as GPIO in output mode. In this register writing 1 will produce low level at the corresponding port pins and clears the corresponding bits in the IOSET register, because once the bits are set using IOSET register, they must be made low by using IOCLR register. Writing 0 will have no effect.

IOSET 310 Description Output value SET bits. Bit0 in IOSET corresponds to P0.0.... Bit 31 in IOSET corresponds to P0.31. Value after Reset

Table 5.9 GPIO Port Output Clear Register (IOCLR Register)

5.1.1.12. UART0

FEATURES

o It has 16 byte Transmit and Receive FIFOs. o It has built-in baud rate generator. o UART0 Register locations are confirmed to 550 industry standards.

PIN DESCRIPTION

In LPC2148 we are having only one UART which is UART0. Generally RS-232 is used as the UART0. In Every UART input is to receive the data and output is to transmit the data i.e. Receiver we will receive the input data and transmitter will output the data. TXD pin of UART0 is connected to 8th pin of port0 which is TDX1 of the processor and RXD pin of UART0 is connected to 9th pin of port0 of the processor.

IOSET Description Value after Reset

Output value SET bits. Bit0 in IOSET corresponds to P0.0.... 310 Bit 31 in IOSET corresponds to P0.31.

Table 5.10 UART0 PIN Description.

DEPARTMENT OF ECE Page 25 VYCET

Safe Driving Using Mobile Phones

REGISTER DESCRIPTION

UART0 of LPC2148 contains ten 8-bit registers. All these registers are listed below

Reset Name Descriptio

n

Bit 7 MSB LSB

Bi t6

Bi t5

Bi t4

Bit3

U0R B

Receive Buffer Register Transmit Holding Register Interrupt Enable Register

B Bit Bit0 Acc ess i 1 t READ DATA 2 RO

Value

Address

Undefine

0xE000C00 0 DLAB = 0 0xE000C00 0 DLAB = 0 0xE000C00 4 DLAB = 0

U0T HR

MSB LSB

WRITE

DATA NA WO R/ W IIR IIR0 1 RO WO 0 R/ W

U0IE R U0II R U0FC R

0 0

0 0 0 Reserve d

0 IIR II 3 R - 2

0 0x01 0

Interrupt ID Register FIFO Control register U0LC Line R Control Register U0LS R Line Status Register U0SC Scratch R Pad U0D Divisor Register LL Latch U0D Divisor LSB LM Latch MSB

FIFO Enabled Rx Trigger

0xE000C00 8 0xE000C00 8 0xE000C00 8 0xE000C00 8 0xE000C00 8 0xE000C00 8 0xE000C00 8

Rx TE FI MT FO MSB Err MSB MSB

TH RE

BI FE

DR P OE E LSB LSB RO

0x60

0 0x01 0

R/ W R/ LSB W R/ Table 5.11 Registers of UART0. W

Page 26

DEPARTMENT OF ECE

VYCET

Safe Driving Using Mobile Phones

Out of these ten register only U0RBR, U0THR, U0LCR, U0LSR U0DLL, andU0DLM are used. The role of these registers is discussed later in our project. o UART0 Receive Buffer Register (U0RBR).

o UART0 Transmitter Holding Register (U0THR). o UART0 Interrupt Enable Register (U0IER). o UART0 Interrupt Identification Register (U0IIR). o UART0 FIFO Control Register (U0FCR). o UART0 Line Control Register (U0LCR). o UART0 Line Status Register (U0LSR). o UART0 Scratch Pad Register (U0SCR). o UART0 Divisor Latch LSB (U0DLL). o UART0 Divisor Latch MSB (U0DLM). The below Figure shows all the registers of UART0 along with their bit description, their access (whether they are read only or write only or both read and write), their reset values and their address. UART0 Receiver Buffer Register In order to access UART0 Receiver buffer register, firstly we have to make the Divisor Latch Access Bit (DLAB) in Line Control Register (U0LCR) to zero. The UART0RBR is always read only. We know that U0RBR is the top byte of the UART0 Rx FIFO. Here the top byte of the Rx FIFO contains the oldest character received and can be read via the bus interface and the LSB represents the oldest received data bit. In our project we are using the characters which are less than 8-bits. If the character is less than 8-bits, the unused MSBs must me padded with zeros.

RBR 70 Function Receive Buffer Register Description The UART0 Receive Buffer Register contains the oldest received byte in the UART0 Rx FIFO. Reset value

Undefined

Table 5.12 UART0 Receive Buffer Register (U0RBR).

DEPARTMENT OF ECE Page 27 VYCET

Safe Driving Using Mobile Phones

UART0 Transmitter Holding Register In order to access UART0 Transmitter Holding Register, firstly we have to make the Divisor Latch Access Bit (DLAB) which is present in Line Control Register (U0LCR) to zero. The U0THR is always writing only. We know that U0THR is the top byte of the UART0 TX FIFO. Here the top byte is the newest character in the Tx FIFO and can be written via the bus interface. We know that the LSB represents the first bit to transmit. In our project we are keeping our command (values given to the processor in order to control the devices) in UART0 Transmitter Holding Register. If the data present in the UART0 THR matches with the predefined command, we can get control to monitor the devices on the board. We are placing the command in between $A__@ to differentiate the next command with the previous command.

U0THR

Function

Description

Reset value

70

Transmit Holding Register

Writing to the UART0 Transmit Holding Register causes the data to be stored in the UART0 Transmit FIFO.

Undefined

Table 5.13 UART0 Transmitter Holding Register (U0THR). UART0 Line Control Register The UART0 Line Control Register determines the format of the data character that is to be transmitted or received. In our project U0LCR is used to get access to U0DLL, U0DLM, U0LCR and U0THR by using the DLAB bit.

DEPARTMENT OF ECE

Page 28

VYCET

Safe Driving Using Mobile Phones

In our program we are using 8bit character length, 1 start bit with no parity. After setting the DLAB bit we can get access to set the baud rate. After setting the baud rate we have to disable this bit to keep the baud rate constant.

U0LCR Function Description 00 5 bit character length 01 6 bit character length 10 Word Length Select 2 Stop Bit Select 10 7 bit character length 11 8 bit character length 01 Stop bit 12 Stop bits (1.5 if U0LCR[10]=00) 0 0 Reset value

0 Disable parity generation and checking 3 Parity Enable 1 Enable parity generation and checking 00 Odd parity 01 Even parity 54 Parity Select 10 Forced 1 stick parity 11 Forced 0 stick parity

0 Disable break transmission 6 Break Control 1 Enable break transmission 0

Divisor Latch Access Bit

0 Disable access to Divisor Latches 1 Enable access to Divisor Latches 0

Table 5.14 UART0 Line Control Register (U0LCR).

DEPARTMENT OF ECE

Page 29

VYCET

Safe Driving Using Mobile Phones

UART0 Line Status Register The UART0 Line Status Register will provide the status information which is present on the UART0 Tx and Rx. U0LSR is a read-only register. In our project we are using this register to check whether the data is received or not. When we send a character, the control will stay there till the character is received or when next character is pressed.

UOLSR Function Description Reset Value

0 U0RBR is empty Receiver

0

1 U0RBR contains valid data

Data Ready U0LSR0 is set when the U0RBR holds an unread 0 (RDR) character and is cleared when the UART0 RBR FIFO is empty.

0 Overrun error status is in inactive state. 1 Overrun error status is in active state.

Overrun 1 Error (OE)

The overrun error condition is set as soon as it occurs. An U0LSR read clears U0LSR1. U0LSR1 is set when UART0 RSR has a new character assembled and the UART0 RBR 0 FIFO is full. In this case, the UART0 RBR FIFO will not be overwritten and the character in the UART0 RSR will be lost.

0 Parity error status is in inactive stat. 1 Parity error status is in active state. 2 Parity Error (PE) A parity error occurs, when the parity bit of a received 0 character is in the wrong state. An U0LSR read clears U0LSR2. Time of parity error detection is dependent on U0FCR0. A priority error is associated with the character being read from the UART0 RBR FIFO.

DEPARTMENT OF ECE

Page 30

VYCET

Safe Driving Using Mobile Phones

UOLSR Function Description Reset Value

0 Framing error status is in inactive state. 1 Framing error status is in active state. A framing error occurs, When the stop bit of a received character is at logic 0,. An U0LSR read clears U0LSR3. The framing error time detection is dependent on U0FCR0. Framing error is linked with the character being read from the UART0 RBR FIFO. Upon detection of a framing error, the Rx will attempt to resynchronize to the data and assume that the bad stop bit is actually an 0 early start bit. However, it cannot be assumed that the next received byte will be correct even if there is no Framing Error. 0 Break interrupt status is in inactive state. 1 Break interrupt status is in active state. When RxD0 is held in the spacing state (all 0s), a break interrupt occurs for one full character transmission (start, data, parity, stop). The receiver goes idle until RxD0 goes to marking state (all 1s),once the break condition has been detected,. An U0LSR clears the status bit when it has read. The break detection time is dependent on U0FCR0.

Framing Error (FE)

Break Interrupt (BI)

Transmitter Holding Register Empty (THRE)

The break interrupt is associated with the character being read contains from thevalid UART0 RBR FIFO. 0 U0THR data. 1 1U0THR is empty. Upon detection of an empty UART0 THR, the THRE is set immediately and is cleared on a U0THR write.

DEPARTMENT OF ECE

Page 31

VYCET

Safe Driving Using Mobile Phones

UOLSR Function Description Reset Value

Transmitter Empty (TEMT)

0 U0THR and/or the U0TSR contain valid data. 1 U0THR and U0TSR are empty. TEMT is set when both U0THR and U0TSR are empty, TEMT is cleared when either the U0TSR or the U0THR contain valid data. 0 U0RBR contains no UART0 Rx errors or U0FCR0=0. 1 UART0 RBR contains at least one UART0 Rx error. 0 1

Error in Rx 7 FIFO (RXFE)

U0LSR7 is set when a character with a Rx error such as framing error, parity error or break interrupt, is loaded into the U0RBR. This bit is cleared when the U0LSR register is read and there are no subsequent errors in the UART0 FIFO. Table 5.15 UART0 Line Status Register (U0LSR).

UART0 Divisor Latch MSB Register When we are using UART0 Divisor Latches, the DLAB bit present in the U0LCR must be one. U0DLM along with U0DLL is a 16-bit divisor. In this 16-bit divisor U0DLL will occupy the lower 8-bits and U0DLM will have higher 8-bits of the divisor. The UART0 Divisor Latch is a part of UART0 baud rate generator. It will divide the VPB clock in order to produce the baud rate clock. Baud rate clock must be 16x the desired baud rate.

U0DLM Function Description Reset value

70

Divisor Latch The UART0 Divisor Latch MSB Register along Undefined MSB with U0DLL register determines the baud rate of Register the UART0. Table 5.16 UART0 Divisor Latch MSB Register (U0DLM).

DEPARTMENT OF ECE

Page 32

VYCET

Safe Driving Using Mobile Phones

UART0 Divisor Latch LSB Register DLAB bit in U0LCR register must be one in order to access this register. By using this register we can set the baud rate which is required. Generally we use baud rate of 9600. This baud rate is achieved by passing 0x62 to this register. Diagram of UART0 Divisor Latch LSB Register is shown below

U0DLL Function Description Reset value

70

Divisor Latch The UART0 Divisor Latch LSB Register along LSB with U0DLM register determines the baud rate Undefined of the UART0. Register

Table 5.17 UART0 Divisor Latch LSB Register (U0DLL).

5.1.1.13 PIN CONNECT BLOCK

The pin connect block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on chip peripherals. Peripherals should be connected to the appropriate pins prior to being activated, and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined. Selection of a single function on a port pin completely excludes all other functions otherwise available on the same pin. The only partial exception from the above rule of exclusion is the case of inputs to the A/D converter. Regardless of the function that is selected for the port pin that also hosts the

DEPARTMENT OF ECE

Page 33

VYCET

Safe Driving Using Mobile Phones

A/D input, this A/D input can be read at any time and variations of the voltage level on this pin will be reflected in the A/D readings. However, valid analog reading(s) can be obtained if and only if the function of an analog input is selected. Only in this case proper interface circuit is active in between the physical pin and the A/D module. In all other cases, a part of digital logic necessary for the digital function to be performed will be active, and will disrupt proper behavior of the A/D. REGISTER DESCRIPTION The Pin Control Module contains 2 registers. Reset value reflects the data stored in used bits only. It does not include reserved bits content. There are two registers in the Pin Control Module. o Pin Function Select Register 0 (PINSEL0). o Pin Function Select Register 1 (PINSEL1). o Pin Function Select Register 2 (PINSEL2). In our project we are using both registers. We are using Pin Function Select Register 0 to select the UART0 by passing a value of 0x0000005 to this register (PINSEL0|=0x00000005). We are selecting Pin Function Select Register 1 to select ADC by passing a value of 0x15400000 to this register (PINSEL1|=0x15400000). (PINSEL2|=0xE002 C014).

Pin Function Select Register 0 (PINSEL0)

There are many functions provided by each port pins. This register is used to controls the functions of the pins which are shown below

PIN SEL0 10 32 54 76 98 P0.0 P0.1 P0.2 P0.3 P0.4 Pin Name Function when 00 GPIO Port0.0 GPIO Port0.1 GPIO Port0.2 GPIO Port0.3 GPIO Port0.4 Function When 01 TxD(UART0) RxD(UART0) SCL(I2C) SDA(I2C) SCK(SPI0) Function When 10 PWM1 PWM3 Capture 0.0(T0) Match 0.0(T0) Capture 0.1(T0) Function When11 Reserved EINT0 Reserved EINT1 Reserved 00 00 00 00 00 Reset Vale

DEPARTMENT OF ECE

Page 34

VYCET

Safe Driving Using Mobile Phones

PIN SEL0 1110 1312 1514 1716 1918 2120 2322 2524 2726 2928 3130 P0.5 P0.6 P0.7 P0.8 P0.9 P0.10 P0.11 P0.12 P0.13 P0.14 P0.15 Pin Name Function when 00 GPIO Port0.5 GPIO Port0.6 GPIO Port0.7 GPIO Port0.8 GPIO Port0.9 GPIO Port0.10 GPIO Port0.11 GPIO Port0.12 GPIO Port0.13 GPIO Port0.14 GPIO Port0.15 Function When 01 MISO(SPI0) MOSI(SPI0) SSEL(SPI0) TxD(UART1) RxD(UART1) RTS(UART1) CTS(UART1) DSR(UART1) DTR(UART1) CD(UART1) RI(UART1) Function When 10 Match 0.1(T0) Capture 0.2(T0) PWM2 PWM4 PWM6 Capture 1.0(T1) Capture 1.1(T1) Match 1.0(T1) Match 1.1(T1) EINT 1 EINT 2 Function When11 Reserved Reserved EINT2 Reserved EINT3 Reserved Reserved Reserved Reserved Reserved Reserved 00 00 00 00 00 00 00 00 00 00 00 Reset Vale

Table 5.18 PIN Function Select Register 0 (PINSEL0) Pin Function Select Register 1 (PINSEL1) This register is mainly used to select the UARTs of the processor and control the functions of the pins which are shown below

PIN SEL1 10 32 Pin Name P0.16 P0.17 Function when 00 GPIO Port0.16 GPIO Port0.17 Function When 01 EINT0 Capture 1.2(T1) Function When 10 Match 0.2(T0) SCK(SPl1) Function When11 Capt0.2(T0 Mat1.2(T1) Reset Value 00 00

DEPARTMENT OF ECE

Page 35

VYCET

Safe Driving Using Mobile Phones

PIN SEL1 54 76 98 110 312 514 716 918 2120 322 524 2726 928 130 Pin Name P0.18 P0.19 P0.20 P0.21 P0.22 P0.23 P0.24 P0.25 P0.26 P0.27 P0.28 P0.29 P0.30 P0.31 GPIO Port0.27 GPIO Port0.28 GPIO Port0.29 GPIO Port0.30 Function when 00 GPIO Port0.18 GPIO Port0.19 GPIO Port0.20 GPIO Port0.21 GPIO Port0.22 GPIO Port0.23 GPIO Port0.24 GPIO Port0.25 Function When 01 Capture 1.3(T1) Match 1.2(T1) Match 1.3(T1) PMW5 Reserved RD2(CAN Con2 ) TD2(CAN Con2 ) RD1(CAN Con1 ) Reserved AIN0 (ADC) AIN1 (ADC) AIN2 (ADC) AIN3 (ADC) Reserved Capture0.1(T0) Capture0.2(T0) Capture0.3(T0) EINT 3 Mat0.1(T0) Mat0.2(T0) Mat0.3(T0) Capt0.0(T0) Function When 10 MISO(SPl1) MOSI(SPl1) SSEL(SPl1) Reserved Capture0.0(T0) Reserved Reserved Reserved Function When11 Mat1.3(T1) Mat1.3(T1) EINT3 Capt1.3(T1) Mat0.0(T1) Reserved Reserved Reserved Reset Value 00 00 00 00 00 00 00 00 00 01 01 01 01 00

Table 5.19 PIN Function Select Register 1 (PINSEL1). Bit Symbol Value Function Reset value 10 - - Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined.

2 GPIO/DEBUG 0 Pins P1.31-26 are used as GPIO pins. P1.26/RTCK 1 Pins P1.36-26 are used as a Debug port. 3 GPIO/TRACE 0 Pins P1.25-16 are used as GPIO pins. P1.20/TRACESYNC

DEPARTMENT OF ECE Page 36 VYCET

Safe Driving Using Mobile Phones

1 Pins P1.25-16 are used as a Trace port. 314 - - Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined.

5.1.1.14 REAL TIME CLOCK

FEATURES o Measures the passage of time to maintain a calendar and clock. o Ultra Low Power design to support battery powered systems o Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year o Dedicated 32 kHz oscillator or programmable pre scalar from VPB clock. o Dedicated power supply pin can be connected to a battery or to the main 3.3 V DESCRIPTION

On, and optionally when it is off. It uses little power in Power-down mode. On the LPC2141/2/4/6/8, the RTC can be clocked by a separate 32.768 KHz oscillator, or by a programmable pre scale divider based on the VPB clock. Also, the RTC is powered by its, which can be connected to a battery or to the same 3.3 V supply used by the rest of the device. REGISTER DESCRIPTION The RTC includes a number of registers. The address space is split into four sections by functionality. The first eight addresses are the Miscellaneous Register Group. The second set of eight locations is the Time Counter Group. The third set of eight locations contains the Alarm Register Group. The remaining registers control the Reference Clock Divider.

The Real Time Clock includes the register shown in Table 3.19. Detailed descriptions of the registers follow.

DEPARTMENT OF ECE

Page 37

VYCET

Safe Driving Using Mobile Phones

Table 5.20 RTC register ARCHITECTURE

Figure5.4 RTC Block diagram RTC INTERRUPTS

DEPARTMENT OF ECE Page 38 VYCET

Safe Driving Using Mobile Phones

Interrupt generation is controlled through the Interrupt Location Register (ILR), Counter. Increment Interrupt Register (CIIR), the alarm registers, and the Alarm Mask Register (AMR). Interrupts are generated only by the transition into the interrupt state. The ILR separately enables CIIR and AMR interrupts. Each bit in CIIR

corresponds to one of the time counters. If CIIR is enabled for a particular counter, then every time the counter is Incremented an interrupt is generated. The alarm registers allow the user to specify a date and time for an interrupt to be generated. The AMR provides a mechanism to mask alarm Compares. If all non masked alarm registers match the value in their corresponding time counter, then an interrupt is generated. The RTC interrupt can bring the microcontroller out of power-down mode if the RTC is operating from its own oscillator on the RTCX1-2 pins. When the RTC interrupt is enabled for wakeup and its selected event occurs, XTAL1/2 pins associated oscillator wakeup cycle is started.

Table 5.21 Miscellaneous register group INTERRUPT LOCATION REGISTER (ILR - 0XE002 4000)

DEPARTMENT OF ECE Page 39 VYCET

Safe Driving Using Mobile Phones

The Interrupt Location Register is a 2-bit register that specifies which blocks are generating an interrupt writing a one to the appropriate bit clears the Clock Tick Counter is read only. It can be reset to zero through the Clock Control Register (CCR). The CTC consists of the bits of the clock divider counter.

Table 5.22 Clock Tick Counter Register (CTCR - 0xE002 4004) 5.2 ARM7TDMI PROCESSOR CORE

The ARM7TDMI processor core implements the ARMv4T Instruction Set Architecture (ISA).This is a superset of the ARMv4 ISA which adds support for the 16-bit Thumb instruction set. Software using the Thumb instruction set is compatible with all members of the ARM Thumb family, including ARM9, ARM9E, and ARM10 families.

5.2.1 REGISTERS

The ARM7TDMI core consists of a 32-bit data path and associated control logic. This data path contains 31 general-purpose 32-bit registers, 7 dedicated 32-bit registers coupled to

DEPARTMENT OF ECE Page 40 VYCET

Safe Driving Using Mobile Phones

a barrel-shifter, Arithmetic Logic Unit, and multiplier. 5.2.2 MODES AND EXCEPTIONS

The ARM7TDMI supports seven modes of operation User mode Fast Interrupt (FIQ) Interrupt (IRQ) Supervisor mode Abort mode Undefined mode and System mode. All modes other than User are privileged modes. These are used to service hardware interrupts, exceptions, and software interrupts. Each privileged mode has an associated Saved Program Status Register (SPSR). This register is use to save the state of the Current Program Status Register (CPSR) of the task immediately before the exception occurs. In these privileged modes, mode-specific banked registers are available. These are automatically restored to their original values on return to the previous mode and the saved CPSR restored from the SPSR. System mode does not have any banked registers. It uses the User mode registers. System mode runs tasks that require a privileged processor mode and allows them to invoke all classes of exception.

5.2.3 PROCESSOR STATES

The ARM7TDMI processor can be in one of two states ARM state

DEPARTMENT OF ECE Page 41 VYCET

Safe Driving Using Mobile Phones

In ARM state, 16 general registers and one or two status registers are accessible at any one time. The ARM state register set contains 16 directly accessible registers R0 to R15. All of these except R15 are general-purpose, and may be used to hold either data or addressvalues.

Figure 5.5 Register Organization in ARM state

DEPARTMENT OF ECE

Page 42

VYCET

Safe Driving Using Mobile Phones

THUMB state

Figure 5.6 Register Organization in THUMB state

DEPARTMENT OF ECE VYCET Page 43

Safe Driving Using Mobile Phones

The THUMB state register set is a subset of the ARM state set. The programmer has direct access to eight general registers, R0-R7, as well as the Program Counter (PC), a stack pointer register (SP), a link register (LR), and the CPSR. There are banked Stack Pointers, Link Registers and Saved Process Status Registers (SPSRs) for each privileged mode.

5.2.4 Exceptions

The ARM7TDMI supports seven types of exception FIQ fast interrupt IRQ normal interrupt Data abort Pre fetch abort Software interrupt Undefined instruction Reset. All exceptions have banked registers for R14 and R13. After an exception, R14 holds the return address for exception processing. This address is used both to return after the exception is processed and to address the instruction that caused the exception. R13 is banked across exception modes to provide each exception handler with a private stack pointer. The fast interrupt mode also banks registers 8 to 12 so that interrupt processing can begin without the need to save or restore these registers. 5.2.5 STATUS REGISTER

All other processor states are held in status registers. The current operating processor status in the CPSR. The CPSR holds

DEPARTMENT OF ECE

Page 44

VYCET

Safe Driving Using Mobile Phones

Four ALU flags (Negative, Zero, Carry, and Overflow) A bit to indicate ARM or Thumb execution state Five bits to encode the current processor mode. 5.2.6 CONDITIONAL EXECUTION

All ARM instructions are conditionally executed and can optionally update the four condition code flags (Negative, Zero, Carry, and Overflow) according to their result. Fifteen conditions are implemented.

5.2.7 CLASSES OF EXECUTION

The ARM and Thumb instruction sets can be divided into four broad classes of instruction Data processing instructions Load and store instructions Branch instructions Coprocessor instructions. 5.2.8 DATA PROCESSING INSTRUCTUIONS

The data processing instructions operate on data held in general-purpose registers of the two source operands, one is always a register. The other has two basic forms An immediate value

DEPARTMENT OF ECE

Page 45

VYCET

Safe Driving Using Mobile Phones

A register value optionally shifted. If the operand is a shifted register the shift amount can have an immediate value or the value of another register. Four types of shift can be specified. Most data processing instructions can perform a shift followed by a logical or arithmetic operation.

Multiply instructions come in two classes Normal, 32-bit result Long, 64-bit result variants. Both types of multiply instruction can optionally perform an accumulate operation.

5.2.9 LOAD AND STROE INSTRUCTIONS

Single or multiple registers can be loaded and stored at one time. Load and store single register instructions can transfer a 32-bit word, a 16-bit half word, or an 8-bit byte between memory and a register. Byte and half word loads can be automatically zero extended or sign extended as they are loaded. Load and store instructions have three primary addressing modes offset pre-indexed Post-indexed. The address is formed by adding or subtracting an immediate or register- based offset to or from a base register. Register-based offsets can also be scaled with shift operations. Pre-indexed and post-indexed addressing modes update the base register with the result of the offset calculation. As the PC is a general-purpose register, a 32-bit value can be loaded directly into the PC to perform a jump to any address in the 4GB memory space. Load and store multiple instructions perform a block transfer of any number of the general purpose registers to or from memory. Four addressing modes are provided

DEPARTMENT OF ECE Page 46 VYCET

Safe Driving Using Mobile Phones

Pre-increment addressing Post-increment addressing Pre-decrement addressing Post-decrement addressing The base address is specified by a register value (that can be optionally updated after the transfer). As the subroutine return address and the PC values are in general-purpose registers, very efficient subroutine calls can be constructed.

Figure 5.7 Load and store instructions 5.2.10 BRANCH INSTRUCTIONS As well as allowing any data processing or load instruction to change control flow (by modifying the PC) a standard branch instruction is provided with 24-bit signed offset, allowing forward and backward branches of up to 32MB. Branch with Link (BL) allows efficient subroutine calls, and preserves the address of the instruction after the branch in R14 (the Link Register or LR). This allows a move instruction to put the LR in to the PC and return to the instruction after the branch. The third type of branch (BX) switches between ARM and Thumb instruction sets. The return address can be preserved in the LR as an option. 5.2.11 COPROCESSOR There are three types of coprocessor instructions

DEPARTMENT OF ECE Page 47 VYCET

Safe Driving Using Mobile Phones

Coprocessor data processing instructions invoke a coprocessor specific internal operation Coprocessor register transfer instructions allow a coprocessor value to be transferred to or from an ARM register Coprocessor data transfer instructions transfer coprocessor data to or from memory, where the ARM calculates the address of the memory transfer 5.3 SYSTEM ISSUES AND THIRD PARTY SUPPORT

This section contains JTAG debug AMBA bus architecture AMBA Design Kit Current support 5.3.1 JTAG debug The internal state of the ARM7TDMI is examined through a JTAG-style serial interface. This allows instructions to be serially inserted into the pipeline of the core without using the external data bus. For example, when in debug state, a Store-Multiple (STM) instruction can be inserted into the pipeline. This exports the contents of the ARM7TDMI registers. This data can be serially shifted out without affecting the rest of the system. 5.3.2 AMBA bus architecture The ARM7 Thumb family processors are designed for use with the Advanced Microcontroller Bus Architecture (AMBA) multi-master on-chip bus architecture. AMBA is an open standard that describes a strategy for the interconnection and management of functional blocks that makes up a System-on-Chip (SoC). The AMBA specification defines three buses

DEPARTMENT OF ECE Page 48 VYCET

Safe Driving Using Mobile Phones

Advanced System Bus (ASB) Advanced High-performance Bus (AHB) Advanced Peripheral Bus (APB). ASB and AHB are used to connect high-performance system modules. APB offers a simpler interface for low-performance peripherals. 5.4 ADVANTAGES a. Small device b. Lower Power Consumption c. Simple decoding d. Higher performance e. Easy to implement an effective pipelined structure

5.5 DISADVANTAGES a. Performance depends on compiler b. Poor code density c. RISC has a fixed size of instruction format d. Small number of instructions

5.6 APPLICATIONS Using the ARMv7 architecture, ARM can strengthen its position as a lowpower/performance leader while conquering new markets to carry its cores up in high performance and down in the low-cost high-volume domain of the microcontroller ARM designs the technology that lies at the heart of advanced digital products, from wireless, networking and consumer entertainment solutions to imaging, automotive, security and storage devices.

ARM's comprehensive product offering includes 16/32-bit RISC microprocessors,

DEPARTMENT OF ECE Page 49 VYCET

Safe Driving Using Mobile Phones

data engines, 3D processors, digital libraries, embedded memories, peripherals, software and development tools, as well as analog functions and high-speed connectivity products.

5.7 GSM MODEM

Figure 5.8 GSM cell site antennas in the Detaches Museum, Munich, Germany

Figure 5.9 GSM modem with accessories

5.7.1 TECHNICAL DETAILS GSM is a cellular network, which means that mobile phones connect to it by searching for cells in the immediate vicinity. There are five different cell sizes in a GSM networkmacro, micro, Pico, femto and umbrella cells.

DEPARTMENT OF ECE

Page 50

VYCET

Safe Driving Using Mobile Phones

The coverage area of each cell varies according to the implementation environment. Macro cells can be regarded as cells where the base station antenna is installed on a mast or a building above average roof top level. Micro cells are cells whose antenna height is under average roof top level; they are typically used in urban areas. Pico cells are small cells whose coverage diameter is a few dozen meters; they are mainly used indoors. Femto cells are cells designed for use in residential or small business environments and connect to the service providers network via a broadband internet connection. Umbrella cells are used to cover shadowed regions of smaller cells and fill in gaps in coverage between those cells.

5.7.2 GSM CARRIER FREQUENCIES GSM networks operate in a number of different carrier frequency ranges (separated into GSM frequency ranges for 2G and UMTS frequency bands for 3G), with most 2G GSM networks operating in the 900 MHz or 1800 MHz bands. Where these bands were already allocated, the 850 MHz and 1900 MHz bands were used instead (for example in Canada and the United States). In rare cases the 400 and 450 MHz frequency bands are assigned in some countries because they were previously used for first-generation systems. Most 3G networks in Europe operate in the 2100 MHz frequency band. Regardless of the frequency selected by an operator, it is divided into timeslots for individual phones to use. This allows eight full-rate or sixteen half-rate speech channels per radio frequency. These eight radio timeslots (or eight burst periods) are grouped into a TDMA frame. Half rate channels use alternate frames in the same timeslot. The channel data rate for all 8 channels is 270.833 Kbit/s, and the frame duration is 4.615 ms. The transmission power in the handset is limited to a maximum of 2 watts in GSM850/900 and 1 watt in GSM1800/1900. 5.7.3 THE NETWORK IS STRUCTURED INTO A NUMBER OF DISCRETE SECTIONS The Base Station Subsystem (the base stations and their controllers).

DEPARTMENT OF ECE Page 51 VYCET

Safe Driving Using Mobile Phones

The Network and Switching Subsystem (the part of the network most similar to a fixed network). This is sometimes also just called the core network. The GPRS Core Network The Operations support system (OSS) for maintenance of the network.

5.7.4 NETWORK STRUCTURE

Figure 5.10 The structure of a GSM network

5.7.5 SUBSCRIBER IDENTITY MODULE

One of the key features of GSM is the Subscriber Identity Module, commonly known as a SIM card. The SIM is a detachable smart card containing the user's subscription information and phone book. This allows the user to retain his or her information after switching handsets.

DEPARTMENT OF ECE

Page 52

VYCET

Safe Driving Using Mobile Phones

5.8 Power Supply 5.8.1 POWER SUPPLY CIRCUIT DIAGRAM

Figure 5.11 Circuit Diagram of Power Supply

5.8.2 WORKING PRINCIPLE

The AC voltage, typically 220V rms, is connected to a transformer, which steps that ac voltage down to the level of the desired DC output. A diode rectifier then provides a fullwave rectified voltage that is initially filtered by a simple capacitor filter to produce a dc voltage. This resulting dc voltage usually has some ripple or ac voltage variation. A regulator circuit removes the ripples and also remains the same dc value even if the input dc voltage varies, or the load connected to the output dc voltage changes.

DEPARTMENT OF ECE Page 53 VYCET

Safe Driving Using Mobile Phones

5.8.3 Block Diagram

TRANSFORME R

RECTIFIER

FILTER

IC REGULATOR

LOAD

Figure.5.12 Block diagram of power supply

5.8.4 TRANSFORMER

The potential transformer will step down the power supply voltage (0-230V) to (0-6V) level. Then the secondary of the potential transformer will be connected to the precision rectifier, which is constructed with the help of opamp. The advantages of using precision rectifier are it will give peak voltage output as DC; rest of the circuits will give only RMS output.

5.8.5 BRIDGE RECTIFIER

When four diodes are connected as shown in Figure, the circuit is called as bridge rectifier. The input to the circuit is applied to the diagonally opposite corners of the network, and the output is taken from the remaining two corners. Let us assume that the transformer is working properly and there is a positive potential, at point A and a negative potential at point B. the positive potential at point A will forward bias D3 and reverse bias D4.The negative potential at point B will forward bias D1 and reverse D2. At this time D3 and D1 are forward biased and will allow current flow to pass through them; D4 and D2 are reverse biased and will block current flow.

DEPARTMENT OF ECE

Page 54

VYCET

Safe Driving Using Mobile Phones

The path for current flow is from point B through D1, up through RL, through D3, through the secondary of the transformer back to point B. this path is indicated by the solid arrows. Waveforms (1) and (2) can be observed across D1 and D3. One-half cycle later the polarity across the secondary of the transformer reverse, forward biasing D2 and D4 and reverse biasing D1 and D3. Current flow will now be from point A through D4, up through RL, through D2, through the secondary of T1, and back to point A. This path is indicated by the broken arrows. Waveforms (3) and (4) can be observed across D2 and D4. The current flow through RL is always in the same direction. In flowing through RL this current develops a voltage corresponding to that shown waveform (5). Since current flows through the load (RL) during both half cycles of the applied voltage, this bridge rectifier is a full-wave rectifier. One advantage of a bridge rectifier over a conventional full-wave rectifier is that with a given transformer the bridge rectifier produces a voltage output that is nearly twice that of the conventional full-wave circuit. This may be shown by assigning values to some of the components shown in views A and B. assume that the same transformer is used in both circuits. The peak voltage developed between points X and y is 1000 volts in both circuits. In the conventional full-wave circuit shownin view A, the peak voltage from the center tap to either X or Y is 500 volts. Since only one diode can conduct at any instant, the maximum voltage that can be rectified at any instant is 500 volts. The maximum voltage that appears across the load resistor is nearly-but never exceeds-500 v0lts, as result of the small voltage drop across the diode. In the bridge rectifier shown in view B, the maximum voltage that can be rectified is the full secondary voltage, which is 1000 volts. Therefore, the peak output voltage across the load resistor is nearly 1000 volts. With both circuits using the same transformer, the bridge rectifier circuit produces a higher output voltage than the conventional full-wave rectifier circuit.

5.8.6 IC VOLTAGE REGULATORS

Voltage regulators comprise a class of widely used ICs. Regulator IC units contain the circuitry for reference source, comparator amplifier, control device, and overload protection

DEPARTMENT OF ECE Page 55 VYCET

Safe Driving Using Mobile Phones

all in a single IC. IC units provide regulation of either a fixed positive voltage, a fixed negative voltage, or an adjustably set voltage. The regulators can be selected for operation with load currents from hundreds of milli amperes to tens of amperes, corresponding to power ratings from milli watts to tens of watts. A fixed three-terminal voltage regulator has an unregulated dc input voltage, Vi, applied to one input terminal, a regulated dc output voltage, Vo, from a second terminal, with the third terminal connected to ground. The series 78 regulators provide fixed positive regulated voltages from 5 to 24 volts. Similarly, the series 79 regulators provide fixed negative regulated voltages from 5 to 24 volts.

4.9 Microcontrollers

Microprocessors and microcontrollers are widely used in embedded systems products. Microcontroller is a programmable device. A microcontroller has a CPU in addition to a fixed amount of RAM, ROM, I/O ports and a timer embedded all on a single chip. The fixed amount of on-chip ROM, RAM and number of I/O ports in microcontrollers makes them ideal for many applications in which cost and space are critical. The Intel 8051 is Harvard architecture, single chip microcontroller (C) which was developed by Intel in 1980 for use in embedded systems. It was popular in the 1980s and early 1990s, but today it has largely been superseded by a vast range of enhanced devices with 8051-compatible processor cores that are manufactured by more than 20 independent manufacturers including Atmel, Infineon Technologies and Maxim Integrated Products. 8051 is an 8-bit processor, meaning that the CPU can work on only 8 bits of data at a time. Data larger than 8 bits has to be broken into 8-bit pieces to be processed by the CPU. 8051 is available in different memory types such as UV-EPROM, Flash and NV-RAM

Features of 8051 8K Bytes of Re-programmable Flash Memory. RAM is 256 bytes. 4.0V to 5.5V Operating Range. Fully Static Operation 0 Hz to 33 MHzs

DEPARTMENT OF ECE Page 56 VYCET

Safe Driving Using Mobile Phones

Three-level Program Memory Lock. 256 x 8-bit Internal RAM. 32 Programmable I/O Lines. Three 16-bit Timer/Counters. Eight Interrupt Sources. Full Duplex UART Serial Channel. Low-power Idle and Power-down Modes. Interrupt recovery from power down mode. Watchdog timer. Dual data pointer. Power-off flag. Fast programming time. Flexible ISP programming (byte and page mode). Description The AT89s52 is a low-voltage, high-performance CMOS 8-bit microcomputer with 8K bytes of Flash programmable memory. The device is manufactured using Atmels high density nonvolatile memory technology and is compatible with the industry-standard MCS51 instruction set. The on chip flash allows the program memory to be reprogrammed in system or by a conventional non volatile memory programmer. By combining a versatile 8bit CPU with Flash on a monolithic chip, the Atmel AT89s52 is a powerful microcomputer, which provides a highly flexible and cost-effective solution to many embedded control applications.

DEPARTMENT OF ECE

Page 57

VYCET

Safe Driving Using Mobile Phones

Figure 5.13 block diagram of AT89s52

DEPARTMENT OF ECE

Page 58

VYCET

Safe Driving Using Mobile Phones

In addition, the AT89s52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The power-down mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset.

Pin description Vcc Pin 40 provides supply voltage to the chip. The voltage source is +5V. GND Pin 20 is the ground.

Figure 5.14 Pin Configurations

DEPARTMENT OF ECE

Page 59

VYCET

Safe Driving Using Mobile Phones

Port 0 Port 0 is an 8-bit open drain bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high impedance inputs. Port 0 can also be configured to be the multiplexed low-order address/data bus during accesses to external program and data memory. In this mode, P0 has internal pullups. Port 0 also receives the code bytes during Flash programming and outputs the code bytes during Program verification. External pull-ups are required during program verification. Port 1 Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. In addition, P1.0 and P1.1 can be configured to be the timer/counter 2 external count input (P1.0/T2) and the timer/counter 2 trigger input (P1.1/T2EX), respectively, as shown in the following table. Port 1 also receives the low-order address bytes during Flash programming and verification.

Port 2 Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-up Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that uses 16-bit addresses (MOVX @ DPTR). In this

DEPARTMENT OF ECE Page 60 VYCET

Safe Driving Using Mobile Phones

application, Port 2 uses strong internal pull-ups when emitting 1s. During accesses to external data memory that uses 8-bit addresses (MOVX @ RI); Port 2 emits the contents of the P2 Special Function Register. The port also receives the high-order address bits and some control signals during Flash programming and verification. Port 3 Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pull-ups. Port 3 receives some control signals for Flash programming and verification. Port 3 also serves the functions of various special features of the AT89S52, as shown in the following

table.

RST Reset input a high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives high for 98 oscillator periods after the Watchdog times out. The DISRTO bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of bit DISRTO, the RESET HIGH out feature is enabled.

DEPARTMENT OF ECE

Page 61

VYCET

Safe Driving Using Mobile Phones

ALE/PROG Address Latch Enable (ALE) is an output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external data memory. If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.

PSEN Program Store Enable (PSEN) is the read strobe to external program memory. When the AT89S52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.

EA/VPP External Access Enable EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. EA should be strapped to VCC for internal program executions. This pin also receives the 12volt programming enable voltage (VPP) during Flash programming. XTAL1 Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

XTAL2

Output from the inverting oscillator amplifier.

DEPARTMENT OF ECE

Page 62

VYCET

Safe Driving Using Mobile Phones

Figure 5.15 Oscillator Connections

Figure 5.16 External Clock Drive Configuration