Professional Documents

Culture Documents

Solucionariaa de Microprocesadores

Uploaded by

tavuchoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Solucionariaa de Microprocesadores

Uploaded by

tavuchoCopyright:

Available Formats

Subido para ciberplex.

tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

Indicaciones: Las preguntas resaltadas con color naranja son preguntas cuyas respuestas no estn confirmadas en el libro. Las preguntas resaltadas con color rojo son preguntas cuyas respuestas no se encuentran no han sido resueltas por los autores de este solucionario.

SOLUCIONARIO DEL LIBRO MICROPROCESADORES INTEL BARRY BREY 7 EDICIN CAPITULO 01: Introduccin al microprocesador y la computadora 1. Quin desarrollo la maquina analtica? Charles Babbage 2. En el censo de 1890 se utilizo un nuevo dispositivo llamado tarjeta perforada. Quin desarrollo la tarjeta perforada? Herman Hollerith 3. Quin fue el fundador de IBM corporation? Herman Hollerith 4. Quin desarrollo la primera calculadora electrnica? Konrad Zuse

5. Para que propsito se desarrollo el primer sistema computacional electrnico?

Probablemente para diseo de aeronaves y misiles durante la II guerra mundial

6. La primera computadora programable de propsito general se llamo?

ENIAC 7. El primer microprocesador en el mundo fue desarrollado en 1971 por El Intel 4004 por Federico Faggin, Ted Hoff y Stan Mayor

8. Quin era la condesa de Lovelace?

Augusta Ada Byron 9. Quin desarrollo el primer lenguaje de programacin llamado FLOWMATIC? Grace Hopper 10. Qu es una maquina de Von Neuman? Una maquina que almacena las instrucciones de un programa en el sistema de memoria CAPITULO 02: El microprocesador y su arquitectura

1. Que son los registros visibles para los programas?

Son registros que se utilizan durante la programacin de aplicaciones y se especifican mediante las instrucciones. Los microprocesadores 8086 al Pentium II se consideran visibles para los programas.

2. El 80286 direcciona registros que son de 8 y de

16 bits.

3. Cules microprocesadores pueden direccionar los registros extendidos? Los microprocesadores 80386 y posteriores ( 80486, Pentium, Pentium Pro y Pentium II, etc.)

4. El registro extendido BX se direcciona como EBX .

5. Cul registro guarda la cuenta para algunas instrucciones?

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

ECX (conteo) 6. Cul es el propsito del registro PI/EIP? Guarda la direccin de desplazamiento del siguiente paso en el programa 7. Cules son las operaciones aritmticas que no modifican el bit de bandera de acarreo? En las transferencias de datos o cuando se realiza una operacin de control 8. Ocurrir un desbordamiento si se suma un FFH con signo a un 01H con signo? No, si suma +1 y -1 el resultado ser cero, que es un nmero valido.

9. Se dice que un numero que contiene 3 bits uno tiene paridad impar.

10. Cul bit de bandera controla la terminal INTR en el microprocesador? La bandera I CAPITULO 03: Modos de Direccionamiento JRM 1. Qu hace las siguientes instrucciones MOV? MOV AX,BX COPIAR BX EN AX MOV BX, AX COPIAR AX EN BX MOV BL,CH COPIAR CH EN BL MOV AX, CS COPIAR CS EN AX 2. Liste Los Registros De 08 Bits Que Se Utiliza Para El Direccionamiento De Registro AL, AH, BL, BH, CL, CH, DL, DH 3. Liste Los Registros De 16 Bits Que Se Utiliza Para El Direccionamiento De Los Registros. AX, BX, CX, DX, SP, BP, SI, DI 4. Liste Los Registros De 32 Bits Que Se Utilicen Para El Direccionamiento De Registros En Los Procesadores 8086 A Pentium 4 EAX, EBC, EDX, ESP, EBP, EDI, ESI 5. Liste Los Registros De 16 Bits Que Se Utiliza Para El Direccionamiento De Registros Mediante PUSH ,MOV Y POP CS, ES, DS, SS, FS y GS 6. Que Error Tiene La Instruccin MOV BL,CX? NO SE PUEDE ESPECIFICAR TAMAOS DE REGISTROS MIXTOS 7. Que Error Tiene La Instruccin MOV DS,SS? NO SE PERMITE COPIAR DE SEGMENTO A SEGMENTO 8.-Seleccione Una Instruccin Para Cada Una De Las Tareas COPIAR EBX EN EDX MOV EDX ,EBX COPIAR BL EN CL MOV CL,BL COPIAR SI EN BX MOV BX ,CI COPIAR DS EN AX MOV AX, DS COPIAR AL EN AH MOV AH,AL 9. Seleccione Una Instruccin Para Cada una De Las Siguientes Tareas MOVER 12H HACIA AL MOV AL ,12H MOVER 123H HACIA AX MOV AX,123H MOVER OCDM HACIA CL MOV CL,OCDM MOVER 100H HACIA SI MOV SI,1000H MOVER 1200A2H HACIA EBX MOV EBX,1200A2H

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

10 .-Que Smbolo Especial Se Utiliza Algunas Veces Para Denotar Datos Inmediatos. El smbolo # CAPITULO 04: Instrucciones para mover datos

1. El primer byte de una instruccin es el cdigo de operacin a menos que contenga

uno de los prefijos de sustitucin.

2. Describa el propsito de los bits D y W que se encuentran en algunas instrucciones

en lenguaje maquina. El bit D indica la direccin de flujo para los datos (REG hacia R/M o R/M hacia REG) y el bit W indica el tamao de los datos ( byte o palabra / doble palabra) 3. Qu informacin se especifica mediante el campo MOD en un instruccin en lenguaje maquina? Selecciona el modo de operacin de direccionamiento para una instruccin en lenguaje maquina

4. Si el campo de registro (REG) de una instruccin contiene 010 y W=0 Qu registro

se selecciona, suponiendo que la instruccin est en modo de 16 bits? DL 5. Como se selecciona los registros de 32 bits en el microprocesador 80486? Estableciendo el modificador .368 despus de la instruccin .MODEL

6. Qu modo de direccionamiento de memoria se especifica cuando R/M= 001, con

MOD=00 para una instruccin de 16 bits? DS:[BX+DI] 7. Identifique los registros de segmento predeterminado que se asignan a los siguientes: (a) SP (b) EBX (c) DI (d) EBP (e) SI (a): apuntador de la pila, (b): ndice de base de 32 bits, (c): ndice de destino, (d): apuntador de base de 32 bits, (e): ndice de origen 8. Convierta el nmero 8B07H de lenguaje maquina a lenguaje ensamblador. MOV AL,[BX] 9. Convierta un nmero 8B9E004CH de lenguaje maquina a lenguaje ensamblador. 10. Si parece una instruccin MOV SI,[BX+2] en un programa Cul es su equivalente en lenguaje mquina ? 8B7702 CAPITULO 05: Instrucciones aritmticas y lgicas 1. Seleccione una instruccin ADD que: a) Sume BX a AX ADD AX, BX b) Sume 12H a AL ADD AL, 12H c) Sume EDI Y EBP ADD EBP, EDI d) Sume 22H a CX ADD CX, 22H

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

e) Sume a AL los datos direccionados por SI ADD AI, [SL] f) Sume CX a los datos almacenados en la posicin de memoria RANA

RANA, CX 2. Cul es el error en la instruccin ADD ECX, AX? No pueden usar registros de tamao mixto 3. Es posible sumar CX a DS con la instruccin ADD? No porque no se permite la suma de registro de segmentos

ADD

4. Si AX=100H y DX=20FF, liste la suma y el contenido de cada bit del registro de banderas (C,A,S,Z y O) despus de ejecutar la instruccin ADD AX,DX AX=3100H, C=0, A=1, S=0, Z=0 y O=0

5. Desarrolle una secuencia corta de instrucciones para suma AL, BL, CL y AH. Almacene la

suma en el registro DH ADD DI, AL ADD DI, BL ADD DI, CL ADD DI, AH 6. Desarrolle una secuencia corta de instrucciones para sumar AX, BX, CX, DX y SP. Almacene la suma en el registro DI. ADD AX, BX ADD AX, CX ADD AX, DX ADD AX, SP ADD DI, AX 7. Desarrolle una secuencia corta de instrucciones para sumar ECX, EDX y ESI. Almacene la suma en el registro EDI. ADD EDI, ECX ADD EDI, EDX ADD EDI, ESI 8. Seleccione una instruccin para sumar BX a DX, y que tambin sume el contenido de la bandera de acarreo (C) al resultado. ADC DX, BX 9. Seleccione una instruccin que sume 1 al contenido del registro SP. INC SP -> SP=SP+1 10.Cul es el error en la instruccin INC [BX]? El ensamblador no puede determinar el tamao de la posicin de memoria Debera escribirse: INC BYTE PTR [BX] INC WORD PTR [BX] INC DWORD PTR [BX] CAPITULO 06: Instrucciones de control de programas

1. Qu es un salto (JMP) Corto?

Se llaman saltos relativos. Es una instruccin de 2 bytes que permite saltos hacia posiciones de memoria que estn dentro del rango de +127 y -128 bytes desde la direccin que sigue despus del salto. 2. Qu tipo de JMP se utiliza cuando se brinca a cualquier lugar dentro de un segmento de cdigo actual?

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

JMP cercano (intrasegmento) 3. Qu tipo de instruccin JMP permite que el programa contine su ejecucin en cualquier posicin de memoria en el sistema? JMP lejano(intersegemento) 4. Qu instruccin JMP es de 5 bytes? Un salto (JMP) lejano Los bytes 2 y 3 => contienen la nueva direccin del desplazamiento Los bytes 4 y 5 => contienen la nueva direccin del segmento

5. Cul es el rango de un salto cercano en los microprocesadores 386-Pentium 4?

El rango es de 2 Gbytes 6. Indique el tipo de instruccin JMP (corto, cercano, lejano) que se ensambla para los siguientes casos. (a) Si la distancia es de 0210H => cercana (b) Si la distancia es de 0020H => corto (c) Si la distancia es de 10000H => lejano 7. Qu puede decirse sobre una etiqueta que va seguida del signo de los 2 puntos? Que es una etiqueta externa 8. Cul registro o registros cambia el salto cercano para modificar la direccin del programa? El registro IP o EIP 9. Cul registro o registros cambia el salto lejano para modificar la direccin del programa? Los registros CS y IP 10. Explique qu hace la instruccin JMP AX. Identifquela como una instruccin de salto cercano o lejano. La instruccin JMP AX salta hacia la direccin de desplazamiento que se almacena en AX, esto solo puede ser un salto cercano. CAPITULO 07: Uso del lenguaje ensamblador con c/c++ 1.- Soporta el ensamblador en lnea macro secuencias en lenguaje ensamblador? No, la principal limitacin del ensamblador en lnea es que no puede utilizar macro secuencias o instrucciones condicionales del flujo del programa. 2.- Puede un byte definirse en el ensamblador en linea mediante el uso de la directiva DB? No, los bytes deben definirse en C++ mediante el uso de char o de_int8. 3.- Como se definen las etiquetas en el ensamblador de lnea? Se define poniendo un nombre para la etiqueta seguida de dos puntos. 4.- Que registros pueden usarse en lenguaje ensamblador (ya sea mdulos en lnea o enlazados) sin almacenarse? EAX, EBX, ECX, EDX y ES 5.- Que registro se utiliza para devolver datos enteros de lenguaje ensamblador al programa en lenguaje C++ que hizo la llamada?

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

6.- Que registro se utiliza para devolver datos tipos punto flotante de lenguaje ensamblador al programa en lenguaje C++ que hizo la llamada? La pila del coprocesador de uso flotante. 7.- Es posible utilizar la instruccin .if en el ensamblador de lnea? No, porque .if es un comando de MASM y el ensamblador en lnea no soporta los comandos condicionales del MASM 8.- En el ejemplo 7-3, explique como la instruccin mov dl, cadena1[si] accede a los datos de cadena1. Accede a los datos en el arreglo cadena1 mediante el uso del registro SI para indicar el elemento tipo cadena. 9.- En el ejemplo 7-3, explique por que se saco y se meti el registro SI. Porque solo se pueden usar AX, BX, CX, DX y ES sin usar PUSH y POP, de lo contrario podra producirse algn error. 10.- Observe que en el ejemplo 7-5 no se utilizan bibliotecas de C++ (#incluye) Piensa que el cdigo compilado para este programa es mas pequeo que para un programa que realiza la misma tarea en lenguaje C++? Por qu? Si no se utilizan encabezados para un programa en C++, ser mucho ms pequeo. CAPITULO 8: Programacin del microprocesador

1. El ensamblador convierte un archivo fuente en un archivo objeto hexadecimal

2. Qu archivos se generan a partir del archivo fuente PRUEBA.ASM, si ste se procesa mediante ML.EXE? Cuando se ensambla el archivo PRUEBA.ASM, genera el archivo PRUEBA.OBJ y el archivo PRUEBA.EXE si no aparecen modificadores en la lnea de comandos.

3. El programa enlazador vincula los archivos objeto y los archivos de biblioteca para

crear un archivo ejecutable. 4. Qu indica la directiva PUBLIC cuando se coloca en el mdulo de un programa? PUBLIC indica que hay una etiqueta disponible para otros mdulos del programa. 5. Qu indica la directiva EXTERN cuando se coloca en el mdulo de un programa? EXTERN declara que las etiquetas son externas para un mdulo 6. Qu directiva aparece con las etiquetas definidas como externas? EXTRN 7. Describa el funcionamiento de un archivo de biblioteca que se enlaza a otros archivos objeto mediante el programa enlazador El programa enlazador saca los procedimientos del archivo de biblioteca que requiere el programa y los enlaza al mismo. 8. Qu directivas de lenguaje ensamblador delinean una macrosecuencia? MACRO y ENDM 9. Qu es una macrosecuencia? Es un grupo de instrucciones para realizar una tarea. A diferencia de un procedimiento, la macro se inserta en el programa en el punto en donde va a utilizarse 10. Cmo se transfieren los parmetros a una macrosecuencia?

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

Los parmetros se pasan a una macro a travs de una lista de parmetros que va despus de la palabra clave MACRO (en la misma lnea) CAPITULO 9 1. Liste las diferencias entre los microprocesadores 8086 y 8088. Las principales diferencias entre el 8086 y el 8088 son: Un bus de datos de 8 bits en el 8088 un bus de datos de 16 bits en el 8086, una terminal en el 8088 en el lugar de terminal M/ en el 8086. en el 8086, y un terminal IO/ en el 8088 en vez de una

2. Es el 8086/8088 compatible con TTL? Explique su repuesta. S y no. El control de corriente de un cero lgico se reduce a 2.0mA y la inmunidad al ruido se reduce a 350mV. 3. Cul es el factor de salida del 8086/8088 para los siguientes dispositivos?: (a) 74XXX TTL: 1 (b) 47ALSXXX TTL: 10 (c) 74HCXXX CMOS: 10 4. Qu informacin aparece en el bus de direcciones/datos del 8088 cuando ALE esta activa? Los bits de direccin A0 - A7 . 5. Cules son los fines de los bits de estado S3 y S4? Los bits S4 y S3 muestran cual segmento se utiliza durante el ciclo de bus actual.. estos dos bits de estado podran utilizarse para direccionar cuatro bancos de memoria separados de 1 Mbyte si se decodifican como A21 y A20. 6. Qu condicin indica un 0 lgico en el terminal RD del 8086/8088? Una operacin de lectura.

7. Explique la operacin de la terminal

y de la instruccin WAIT. s es un 1 lgico,

La terminal Prueba es una entrada que se evala mediante la instruccin WAIT. Si un 0 lgico, la instruccin WAIT funciona como una instruccin NOP y si la instruccin WAIT espera a que frecuencia al coprocesador numrico. se un 0 lgico. Esta terminal se conecta con ms

8. Describa la seal que se aplica a la terminal de entrada CLK de los microprocesadores 8086/8088. El ciclo de trabajo debe ser del 33%. 9. Qu modo de operacin se selecciona cuando MN/MX se conecta a tierra? Modo mximo. 10. Qu indica la seal de estrobo WR que proviene del 8086/8088 sobre la operacin del 8086/8088? Que se est llevando a cabo una operacin de escritura. CAPITULO 10: Interfaz de memoria 1. Qu tipos de conexiones son comunes para todos los dispositivos de memoria? Son las entradas de direccin, las salidas entradas/salidas de datos, cierto tipo de entrada de seleccin y por lo menos una entrada de control.

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

2. Liste el nmero de palabras en cada dispositivo de memoria para los siguientes nmeros de conexiones de direccin a) 8 256 b) 11 2k c) 12 4k d) 13 8k 3. Liste el nmero de elementos de datos que se almacenan en c/u de los siguientes dispositivos de memoria y el nmero de bits en c/dato

a) 2Kx4 b) c) d) e)

2k posiciones de memoria de 4 bits cada una; 2048 posiciones de memoria de 4 bits cada una 1Kx1 1k (1024) posiciones de memoria de 1 bit cada una 4Kx8 4k (4096) posiciones de memoria de 8 bits cada una 16Kx1 16k (16384) posiciones de memoria de 1 bit cada una 64Kx4 64k (65536) posiciones de memoria de 4 bits cada una en un componente de memoria?

4. Cul es el propsito de la terminal 5. Cul es el propsito de la terminal 6. Cul es el propsito de la terminal

Produce una operacin de lectura.

o Selecciona o HABILITA el dispositivo de memoria.

en un dispositivo de memoria? Permite que los datos fluyan de las terminales de datos de salida de la ROM. en una SRAM?

7. Cuntos bytes de almacenamiento contienen los siguientes dispositivos de memoria EPROM? a) 2708 1k bytes b) 2716 2k bytes c) 2732 4k bytes d) 2764 8k bytes e) 27512 64k bytes 8. Por qu una EPROM de 450ns no funciona directamente con un 8088 a 5MHz? El microprocesador permite 460ns para la memoria a 5 MHz, pero como hay un pequeo retraso en las conexiones a memoria, sera mejor no utilizar un dispositivo de memoria de 450ns en dicho sistema sin un estado de espera. 9. Qu puede decirse acerca de la cantidad de tiempo que se necesita para borrar y escribir en una posicin de un dispositivo de memoria FLASH? Este dispositivo de memoria puede borrarse en el sistema mediante electricidad, pero requiere ms tiempo para borrarse que una RAM normal. Permite funcionar a velocidades muy superiores cuando los sistemas emplean lectura y escritura en diferentes puntos de esta memoria al mismo tiempo. 10. Qu tipo de dispositivo utiliza el acrnimo SRAM? La Memoria Esttica de Acceso Aleatorio CAPITULO 11: Interfaz bsica de E/S 1.- Explique en qu sentido fluyen los datos para unas instrucciones IN y OUT

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

IN.- Introduce datos desde un dispositivo de E/S externo hacia el registro AL (8bit) o AX (16 bits) OUT.- Enva datos des AL o AX hacia un dispositivo de E/S externo 2.- En dnde se almacena el nmero de puerto E/S para una instruccin de E/S fija? La direccin de E/S se almacena en el segundo byte de la instruccin. 3.- En dnde se almacena el nmero de puerto E/S para una instruccin de E/S variable? En el nmero de puerto de E/S de 16 bits.- en DX 4.- En dnde se almacena el nmero de puerto E/S para una instruccin de E/S de cadena? En el nmero de puerto de E/S de 16 bits.- en DX 5.- En cul registro se introducen datos mediante la instruccin IN de 16 bits? En el registro DX 6.- Describa la operacin de la instruccin OUTSB Se enva un byte desde la posicin de memoria del segmento de datos direccionado por SI hacia el puerto direccionado por DX, despus SI=SI=+-1 7.- Describa la operacin de la instruccin INSW Se introduce una palabra desde el puerto direccionado por DI y se almacena en la posicin de memoria del segmento extra direccionada por DI despus DI = DI=+-2 8.- Compare un sistema de E/S por asignacin de memoria con un sistema de E/S aislada E/S por asignacin de memoria No utiliza las instrucciones de memoria IN, INS, OUT y OUTS. En realidad se utiliza cualquier instruccin que transfiere datos entre el microprocesador y la memoria E/S aislada Se deben emplear las instrucciones IN, INS, OUT, OUTS

9.- Cul es la interfaz bsica de entrada? El dispositivo bsico para entrada es un conjunto de bferes (registros) de tres

estados.

10.- Cul es la interfaz bsica de salida? Es un enclavamiento que captura los datos de salida y los retiene para el dispositivo de salida. CAPITULO 12 : Interrupciones 1. Qu es lo que se interrumpe debido a una interrupcin? Interrumpe el programa que se est ejecutando en cualquier punto dado 2. Defina el termino interrupcin Una interrupcin es una llamada a una subrutina iniciada por hardware o software. 3. Qu es lo que se llama debido a una interrupcin? Se llama a un procedimiento el cual mediante el manejador de interrupciones o un procedimiento de servicio de interrupciones. 4. Por qu las interrupciones liberan tiempo para el microprocesador? Una interrupcin solo utiliza tiempo de la computadora cuando se activa. 5. Liste las terminales de interrupcin en el microprocesador

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

INTR, NMI, INTA. 6. Liste las 5 instrucciones de interrupcin para el microprocesador INT, INT3, INTO, CLI, STI. 7. Qu es un vector de interrupcin? Es un elemento imprescindible para comprender las interrupciones de hardware y software. 8. En qu parte de la memoria del microprocesador se encuentran los vectores de interrupcin? En el primer 1Kbyte del sistema de memoria en modo real y en cualquier parte de modo protegido. 9. Cuntos vectores de interrupcin distintos se encuentran en la tabla de vectores de interrupcin? 256 10. Qu vectores de interrupcin estn reservados por Intel? Del 00H al 1FH. (Las primeras 32 posiciones) CAPITULO 13: Acceso directo a memoria 1. Qu terminales del microprocesador se utilizan para solicitar y aceptar una transferencia por DMA? Hay dos seales de control que se utilizan para solicitar y admitir una transferencia de acceso directo a memoria (DMA) en el sistema basado en microprocesador. La terminal HOLD es una entrada que se utiliza para solicitar una accin de DMA y la terminal HLDA es una salida que admite la accin de DMA. 2. Explique lo que ocurre cada vez que se coloca un 1 lgico en la terminal de entrada HOLD. El microprocesador suspende la ejecucin de la instruccin actual y flota su direccin, informacin y canales para control. 3. Una lectura de DMA transfiere datos desde ____________ hacia ______________ Una lectura de DMA transfiere datos desde LA MEMORIA hacia EL DISPOSITIVO DE E/S. 4. Una escritura de DMA transfiere datos desde __________ hacia ______________ Una escritura de DMA transfiere datos desde EL DISPOSITIVO DE E/S hacia LA MEMORIA. 5. A travs de qu seales del bus selecciona el controlador de DMA para seleccionar el dispositivo de E/S que se va a utilizar durante una transferencia por DMA? Seales de control e informacin sobre direcciones de memoria durante la transferencia por DMA. 6. Cul es la terminal que utiliza el controlador de DMA para seleccionar el dispositivo de E/S que se va a utilizar durante una transferencia por DMA? Es la terminal DACK 7. Qu es una transferencia por DMA de memoria a memoria? Una transferencia DMA consiste principalmente en copiar un bloque de memoria de un dispositivo a otro. En lugar de que la CPU inicie la transferencia, la transferencia se lleva a cabo por el controlador DMA. Un ejemplo tpico es mover un bloque de memoria desde una memoria externa a una interna ms rpida. Tal operacin no ocupa el procesador y como resultado puede ser planificado para efectuar otras tareas. Un ejemplo de transferencia DMA de memoria a memoria: suponga que el contenido de las ubicaciones de memoria 10000H-13FFFH debe ser transferido a las ubicaciones de memoria

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

14000H-17FFFH. Esto se logra mediante una instruccin repetida de movimiento de cadena o, de manera ms rpida, con el controlador de DMA.

8. Describa el efecto en el microprocesador y el controlador de DMA cuando las

terminales HOLD y HLDA estn en el nivel de 1 lgico. El microprocesador es ideal y el controlador DMA gobierna al sistema. 9. Describa el efecto en el microprocesador y el controlador de DMA cuando las terminales HOLD y HLDA estn en el nivel de 0 lgico. 10. El controlador de DMA 8237 es un controlador de DMA de ___________ canales. El controlador de DMA 8237 es un controlador de DMA de CUATRO canales. CAPITULO 14: El Coprocesador aritmtico, las tecnologas MMX y SIMD 1. Liste los tres tipos de datos que se cargan o se almacenan en memoria mediante el coprocesador. Estos tipos de datos son: Entero con signo, BCD y Punto flotante. 2. Liste los tres tipos de datos enteros, el rango de los enteros que puede almacenarse en ellos y el nmero de bits que se asigna a cada uno. Palabra (16 bits, 32K) Doble Palabra (32 bits, 2 G) Palabra cudruple (64 bits, 9X1018) 3. Explique cmo el coprocesador almacena un nmero BCD en memoria. El formato decimal codificado binario (BCD) requiere 80 bits de memoria. Cada nmero se almacena como un entero empaquetado de 18 dgitos en nueve bytes de memoria con dos dgitos por byte. El dcimo byte contiene slo un bit de signo para el nmero BCD con signo de 18 dgitos. La figura a continuacin muestra el formato el numero BCD que se utiliza con el coprocesador aritmtico. Observe que tanto los nmeros positivos como los negativos se almacenan en formato real y nunca en formato de complemento a diez.

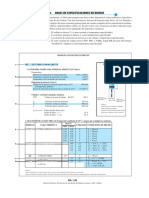

79

Byte de signo

0 D17 D16 D15 D14D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

FORMATO DE DATOS BCD PARA LA FAMILIA 80X87 DE COPROCESADORES ARITMTIOS 4. Liste los tres tipos de nmeros de punto flotante que se utilizan con el coprocesador y el nmero de bits binarios que se asignan a cada uno. Precisin simple (32 bits) Doble precisin (64 bits) Precisin temporal (128 bits) 5. Convierta los siguientes nmeros decimales en nmeros de punto flotante con precisin simple: a) 28.75 b) 624 c) -0.615 d) +0.0 e) -1000.5

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

6. Convierta los decimales: a) 11000000 b) 00111111 c) 01000011 d) 01000000 e) 01000001 f) 00000000

siguientes nmeros de punto flotante con precisin simple en 11110000 00010000 10011001 00000000 00100000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 -7.75 0.5625 76.5 2.0 10.0 0.0

7. Explique qu hace el coprocesador cuando se ejecuta una instruccin normal del microprocesador. El coprocesador aritmtico funciona en paralelo con el microporcesador 8. Explique qu hace el microprocesador cuando se ejecuta una instruccin del coprocesador. El microprocesador contina ejecutando instrucciones de microprocesador (tipo entero), mientras que el coprocesador ejecuta una instruccin de punto flotante.

9. Cul es el propsito de los bits C3 - C0 en el registro de estado?

Los bits de cdigo de condicin indican condiciones relacionadas con el coprocesador. 10. Qu operacin se logra mediante la instruccin FSTSW AX? Copia el registro de estado del coprocesador en AX. CAPITULO 15: Interfaz de Bus

1. A qu corresponde las letras ISA como acrnimo?

Corresponden a Arquitectura Estndar de la Industria 2. Qu tamao de transferencia de datos soporta del sistema de bus ISA? De 8 o de 16 bits, dependiendo de la configuracin de zcalo

3. Se utiliza la interfaz de bus ISA con frecuencia para la expansin de memoria?

Es raro que se agregue memoria a cualquier tarjeta de bus ISA ya que solo opera a una velocidad de 8 MHz 4. Desarrolle una interfaz de bus ISA con frecuencia para la expansin de la memoria

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

SD0 SD1 SD2 SD3 SD4 SD5 SD6 SD7 IOR IOW SA0 SA1 RESET

34 33 32 31 30 29 28 27 5 36 9 8 35 6

DC0 DC1 DC2 DC3 DC4 DC5 DC6 DC7 RD WR AO AI RESET CS

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

4 3 2 1 40 39 38 37 18 19 20 21 22 23 24 25 14 15 16 17 13 12 11 10

SA2 SA3 SA4 SA5 SA6 SA7 SA8 SA9 SA10 SA11

I1 I2 I3 I4 I5 I6 I7 I8 I9 I10

O1 O2 O3 O4 O5 O6 O7 O8

19 18 17 16 15 14 13 12

SA12 SA13 SA14 SA15

5. Desarrolle una interfaz de bus ISA que decodifique los puertos 0340H 0343H para controlar un temporizador 8254 6. Desarrolle una interfaz de bus PCI de 32 bits que agregue una EPROM 27c256 en las direcciones de memoria FFFF0000H-FFF7FFFH

SA0 SA1 SA2 SA3 SA4 SA5 SA6 SA7 SA8 SA9 SA10 SA11 SA12 SA13 SA14 SMEMR 10 9 8 7 6 5 4 3 25 24 21 23 2 26 27 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 CE OE VPP O0 O1 O2 O3 O4 O5 O6 O7 11 12 13 15 16 17 18 19 SD7 SD6 SD5 SD4 SD3 SD2 SD1 SD0

_____ 10k --SA15 SA16 SA17 SA18 SA19 SA20 SA21 SA22 SA23 I1 I2 I3 I4 I5 I6 I7 I8 I9 I10 O1 O2 O3 O4 O5 O6 O7 O8 19 18 17 16 15 14 13 12

7. Suponiendo que cuenta con un bfer 24LS244 y un enclavamiento 74LS374, desarrolle una interfaz de bus ISA que contenga un puerto de entrada de 8 bits en la direccin E/S 308H y un puerto de salida de 8bits en la direccin E/S 30AH

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

3 4 7 8 13 14 17 18 D0 D1 D2 D3 D4 D5 D6 D7 2 4 6 8 11 13 15 17 1 19 _______ -------1A1 1A2 1A3 1A4 2A1 2A2 2A3 2A4 1G 2G 1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4 10 16 14 12 9 7 5 3 1 _______ --------

D0 D1 D2 D3 D4 D5 D6 D7 OC CLK

O0 O1 O2 O3 O4 O5 O6 O7

2 5 6 9 12 15 16 19

8. Cree una interfaz de bus ISA que permita 4 canales de seales de salida analgicas, de 0 a 5.0V cada una. Estos 4 canales debern codificarse en las direcciones de E/S 300H, 310H, 320H y 330H tambin desarrolle el software que soporte los 4 canales

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

CS WR1 WR2 SD0 SD1 SD2 SD3 SD4 SD5 SD6 SD7 2 4 6 8 11 13 15 17 1A1 1A2 1A3 1A4 2A1 2A2 2A3 2A4 1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4 D10 D11 D12 D13 D14 D15 D16 D17

VREF

RFB

9 415

IOUT2 IOUT1

12 11

2 3

1 1G 19 2G ______ ------

XFER ILE DGND AGND

SA0 SA1 SA2 SA3 SA4 SA5 SA6 SA7 SA8 SA9

1 2 3 4 5 6 7 8 9 11

I1 I2 I3 I4 I5 I6 I7 I8 I9 I10

O1 O2 O3 O4 O5 O6 O7 O8

CS WR1 WR2 D10 D11 D12 D13 D14 D15 D16 D17

VREF

RFB

9 415

IOUT2 IOUT1

12 11

2 3

SA10 SA11

XFER ILE DGND AGND

SA12 SA13 SA14 SA15

1 2 4 5

CS WR1 WR2 D10 D11 D12 D13 D14 D15 D16 D17

VREF

IOW

9 10 12 13

RFB

9 415

IOUT2 IOUT1

12 11

2 3

XFER ILE DGND AGND

CS WR1 WR2 D10 D11 D12 D13 D14 D15 D16 D17

VREF

RFB

9 415

IOUT2 IOUT1

12 11

2 3

XFER ILE DGND AGND

______ -------

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

9. Haga de nuevo la pregunta 8, solo en vez de 4 canales de salida usar 4 ADCs para crear 4 canales de entrada analgicas en las mismas direcciones. 10. Mediante el uso de un temporizador o de varios temporizadores 8254, desarrolle un temporizador cuarto oscuro en una tarjeta de bus ISA. Su temporizador deber generar un 0 lgico para intervalos de 1/100 segundos, desde 1/100 segundos hasta 5 minutos. Use el reloj del sistema de 8 MHz como fuente de sincronizacin. El software que desarrolle deber permitir al usuario seleccionar el tiempo desde el teclado. La seal de salida del temporizador deber ser un 0 lgico durante el tiempo seleccionado y pasar a travs de un inversor para habilitar un relevador de estado solido que controle el ampliador fotogrfico CAPITULO 16: Los microprocesadores 80186 80188 y 80286 1. Liste las diferencias entre los microprocesadores 8086/8088 y 80186/80188 Gran diferencia entre estos es la anchura de los buses 80186 al igual que el 8086 contiene un bus de datos de 16 bits 80188 al igual que el 8088 trae un bus de datos de 8 bits Las estructuras internas de estos son idnticas. Pero el 80186/80188 contienen vectores de interrupcin reservados adicionales y algunas caractersticas de E/S integrados muy poderosas conocidas como controladores integrados 2. Qu mejoras se agregaron al 80186/80188 que no estn presente en el 8086/8088? Las mejoras de hardware incluyen temporizadores internos entradas de interrupcin adicionales, lgica de seleccin de chip, puertos de comunicaciones en serie, terminales en paralelo, controlador de DMA y un controlador de interrupciones. 3. En que tipos de circuitos integrados viene empaquetado el 80186/80188? En 4 versiones CMOS: 80C186XL y 80C188XL versiones bsicas y 80C186EC y 80C188EC versiones avanzadas

4. Si el cristal de 20MHz se conecta a X1 y X2 Qu seal de frecuencia se encuentra en

CLKOUT? 10 MHz 5. Describa las diferencias entre las versiones 80C188XL y 80C188EB del controlador integrado 80188 La versin 80C188EB contiene algunas nuevas caractersticas que no estaban a versiones anteriores. Estas son: - 2 puertos de E/S (P1 y P2) que se comparten con otras funciones - 2 interfaces de comunicaciones en serie que estn integradas en el procesador A diferencia de la versin XL esta no contiene un controlador DMA 6. El factor de salida de cualquier terminal del 80186/80188 es. Para un 0 lgico 3 mA 7. Cuntos periodos de reloj se encuentran en un ciclo de bus del 80186/80188? 4 periodos 8. Cul es la principal diferencia entre la sincronizacin del 8086/8088 y del 80186/80188? El punto en el que aparece la direccin 9. Cul es la importancia del tiempo de acceso a memoria?

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

Tiempo de acceso es el que se asigna a la memoria y a la E/S, para que proporcionen datos al microprocesador, una vez que este enva su direccin a la memoria o a la E/S 10. Cunto tiempo de acceso a memoria permite el 80186/80188 si se opera con un reloj de 10MHz? 260 ns para la versin de 16 MHz que opera a 10MHz CAPITULO 17 1. El microprocesador 80386 direcciona.. bytes de memoria en el modo protegido 4G 2. El microprocesador 80386 direcciona.. bytes de memoria virtual mediante la unidad de administracin de memoria. 64T 3. Describa las diferencias entre el 80386DX y el 80386SX El 80386DX utiliza bancos de memoria a travs de BLE y BHE, en el 80386SX los bancos de memoria se utilizan a travs de habilitacin de banco, BE3-BE0 El 80386SX no contiene la terminal de direccin A0 debido a que esta decodificada en las seales BLE y BHE El 80386DX no contiene las conexiones de direccin A0 y A1 porque estn codificadas como las seales de habilitacin de banco. El 80386SX tiene un bus de direcciones de 16 bits y el 80386DX de 32 bits 4. Dibuje el mapa de memoria del 80386 cuando se opera en el (a) modo protegido; (b) modo real.

FFFFFFFF

0000FFFF

Mapa de Memoria en Modo Real

Mapa de Memoria en Modo Protegido

00000000

00000000

5. Cunta corriente hay disponible en las diversas conexiones de las terminales de salida del 80386?compare estas corriente con las corrientes disponibles en la conexin de terminal de salida de un microprocesador 8086 Cada una de las terminales de salida del 80386 son capaces de suministrar 4.0 mA (conexiones de direccin y de datos) o 5.0 mA (otras conexiones), representando un aumento en comparacin de los 2.0 mA disponibles en las terminales de salida del 8086 6. Describa el sistema de memoria del 80386; explique el propsito y la operacin de las seales de seleccin de banco. El tema de memoria tiene hasta 4 Gbytes y las seales de habilitacin de banco seleccionan uno o ms de los bancos de memoria de 8 bits. 7. Explique la accin de un reinicio de hardware en las conexiones del bus de direcciones del 80386

Subido para ciberplex.tk

Desarrollado en la Universidad Nacional Jorge Basadre Grohmann por los estudiantes de la ESIS

el reinicio inicializa el 80386, con lo cual empieza a ejecutarse el software en la posicin de memoria FFFFFFF0H. el 80386 se reinicializa en modo real, en tanto que las 12 conexiones de direccin de mas a la izquierda se mantienen en el nivel de 1 lgico (FFFH) hasta que se ejecutan un salto lejano. Facilitando la compatibilidad con los microprocesadores antiguos 8. Explique como la canalizacin extiende el tiempo de acceso para muchas referencias a memoria en el sistema basado en el microprocesador 80386 La canalizacin permite que el microprocesador envi la direccin de la siguiente posicin de la memoria mientras retiene los datos de la operacin de la memoria anterior. Le permite a la memoria un tiempo adicional para acceder a los datos

9. Describa en forma breve como funciona el sistema de memoria cach

La memoria cache es un bfer que permite que el 80386 funcione de una manera mas eficiente con menores velocidades de DRAM. Mejora el rendimiento general de los sistemas de memoria para los datos que se utilizan ms de una vez. Por lo general los dispositivos de memoria cache son componentes de memoria RAM esttica con tiempos de acceso menores a 10 ns. 10. En el 80386, los puertos de E/S comienzan en la direccin de E/S___________ y se extienden hasta la direccin de E/S__________________ 0000H-FFFFH

You might also like

- Unidad 1 - Familias Logicas de ICDocument15 pagesUnidad 1 - Familias Logicas de ICCarlos OrtegaNo ratings yet

- Parcial Circuito Digital EsDocument1 pageParcial Circuito Digital EsFernando OrtizNo ratings yet

- Practica - 03 - 1S - 2021 LABORATORIO ELECTRONICA 6 USACDocument2 pagesPractica - 03 - 1S - 2021 LABORATORIO ELECTRONICA 6 USACPedro SalojNo ratings yet

- Conectores de Audio y VídeoDocument3 pagesConectores de Audio y VídeoCarlos Feenando Campos MonterrosaNo ratings yet

- Laboratorio 3.5 PresiónDocument4 pagesLaboratorio 3.5 PresiónERIK GABRIEL FALCON CAPILLANo ratings yet

- Conectores de AudioDocument12 pagesConectores de AudioJose Joaquin Jara ChapilliquenNo ratings yet

- Practica 3Document8 pagesPractica 3Andrea Alexandra Trujillo OrellanaNo ratings yet

- Informe 4 Eelc 2Document3 pagesInforme 4 Eelc 2Fabian Andres BeleñoNo ratings yet

- Lab Nº3 - Corte y Saturación - 2011-IDocument2 pagesLab Nº3 - Corte y Saturación - 2011-IBruno Adolfo Castillo SoteloNo ratings yet

- SimulacionesDocument16 pagesSimulacionesJaime Sebastian CardenasNo ratings yet

- Digitales 1 Previo 5Document11 pagesDigitales 1 Previo 5jorgeNo ratings yet

- Sistema Básico de Entrada y Salida El BiosDocument27 pagesSistema Básico de Entrada y Salida El BiosWildines LópezNo ratings yet

- Articulo IEEE Curvas Del DiodoDocument4 pagesArticulo IEEE Curvas Del DiodoEveth De la CruzNo ratings yet

- Digitales Ejercicios de MSS y ASMDocument4 pagesDigitales Ejercicios de MSS y ASMRonny BritoNo ratings yet

- Andy Ramirez Parte III InteresanteDocument25 pagesAndy Ramirez Parte III InteresanteGERARDO CABRERANo ratings yet

- Modulacion AMDocument23 pagesModulacion AMAlexis ParienteNo ratings yet

- Amplificador DiferencialDocument6 pagesAmplificador DiferencialDanielQCNo ratings yet

- Trabajo Preparatorio 6 Sistemas DigitalesDocument5 pagesTrabajo Preparatorio 6 Sistemas DigitalesIan BaqueroNo ratings yet

- Rubrica PCBDocument2 pagesRubrica PCBRaul OrtegaNo ratings yet

- Los Microprocesadores 8086 y 8088Document109 pagesLos Microprocesadores 8086 y 8088ICENLERNo ratings yet

- 13 - El Transistor Como Amplificador PDFDocument18 pages13 - El Transistor Como Amplificador PDFChomps Guerrero50% (2)

- Guias CilindricasDocument12 pagesGuias Cilindricasgabriel olivasNo ratings yet

- PIC Bootloader TinyDocument7 pagesPIC Bootloader TinyEver CaliNo ratings yet

- Compuertas LogicasDocument27 pagesCompuertas Logicaszzzxxx666No ratings yet

- Compuertas Logicas Con Tecnologia TTLDocument11 pagesCompuertas Logicas Con Tecnologia TTLjose_sanguino_2No ratings yet

- Informe # 3 Modulacion AmDocument4 pagesInforme # 3 Modulacion AmanderelelectronicNo ratings yet

- Informe AluDocument4 pagesInforme AluSergio Pabon SueldoNo ratings yet

- Registro de Segmento Del MicroprocesadorDocument6 pagesRegistro de Segmento Del MicroprocesadorStevenFelipeQuinteroMartínezNo ratings yet

- Manipulacion de Puertos en Lenguaje CDocument12 pagesManipulacion de Puertos en Lenguaje CSalvador Soria SalgadoNo ratings yet

- MonografiaDocument30 pagesMonografiaxxzagaxxNo ratings yet

- Uni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Quinto LaboratorioDocument3 pagesUni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Quinto LaboratorioAlfred PILLACA GOMEZNo ratings yet

- Clase8 IDocument33 pagesClase8 IGerson Bustillo CruzNo ratings yet

- HCIDocument3 pagesHCILuis RodriguezNo ratings yet

- Codificacion DigitalDocument11 pagesCodificacion DigitalEdgar Eduardo Ortiz OsorioNo ratings yet

- Lab 01 - ELC 115Document14 pagesLab 01 - ELC 115Nestor VasquezNo ratings yet

- Reporte SimulacionesDocument8 pagesReporte SimulacionesKevin Josué López MedranoNo ratings yet

- Universidad Nacional de Ingenieria Facultad de Electrotecnia y Computación Circuitos Eléctricos IIDocument11 pagesUniversidad Nacional de Ingenieria Facultad de Electrotecnia y Computación Circuitos Eléctricos IIGerald AburtoNo ratings yet

- Protocolo ARPDocument4 pagesProtocolo ARPeduardo_manjarrezNo ratings yet

- Difracción de Fresnel TrabajoDocument6 pagesDifracción de Fresnel Trabajocristian estradaNo ratings yet

- Informe Deber Antena Dipolo LargoDocument2 pagesInforme Deber Antena Dipolo LargoJorgeSandoval50% (2)

- 1.3.1polarizacion Del JfetDocument21 pages1.3.1polarizacion Del Jfetelectronico169No ratings yet

- Instrucción ADDLWDocument2 pagesInstrucción ADDLWHector Calisaya HuarcayaNo ratings yet

- Datasheetdiodos PDFDocument4 pagesDatasheetdiodos PDFNiko Argota LemmeNo ratings yet

- Ci MM74C922Document9 pagesCi MM74C922JOSE FRANCIA ZORRILLANo ratings yet

- Multimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásDocument9 pagesMultimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásArmando Campos SalazarNo ratings yet

- Nombre Cinthia Gámez en EnsambladorDocument14 pagesNombre Cinthia Gámez en EnsambladorDayber CruzNo ratings yet

- Implementacion de Termometro Digital Con LM35Document3 pagesImplementacion de Termometro Digital Con LM35Jesus MedranoNo ratings yet

- Practica 2 DisplayDocument2 pagesPractica 2 DisplayKevin DavidNo ratings yet

- Primer Examen Parcial de Microprocesadores IDocument3 pagesPrimer Examen Parcial de Microprocesadores IGustavoPaolo MaldonadoCallisaya100% (1)

- Salida Colector o Drenador AbiertoDocument5 pagesSalida Colector o Drenador AbiertoCarlos Ortega100% (1)

- CMOSDocument21 pagesCMOSJonathanDavidNo ratings yet

- Colector Abierto en TTL y CmosDocument8 pagesColector Abierto en TTL y CmosMauricio NavarreteNo ratings yet

- Introducción A Las Redes y Dispositivos de InterconexiónDocument29 pagesIntroducción A Las Redes y Dispositivos de InterconexiónJulio100% (1)

- PIC16F819 6to AñoDocument33 pagesPIC16F819 6to AñoAntonio Gonzalez100% (1)

- Hoja de Trabajo Capacitancia PDFDocument6 pagesHoja de Trabajo Capacitancia PDFElian FuentesNo ratings yet

- Máquinas EléctricasDocument191 pagesMáquinas EléctricasAntonio Fuster MonzoNo ratings yet

- 13 Tipos de Funciones MatemáticasDocument47 pages13 Tipos de Funciones MatemáticasJimmy Alexander Muñoz ForeroNo ratings yet

- Solucionario Microprocesadores Intel - Barry BreyDocument18 pagesSolucionario Microprocesadores Intel - Barry Breyciberjovial67% (6)

- Arquitectura CompletoDocument13 pagesArquitectura CompletoGustavo Chinchilla RinconNo ratings yet

- Compilador C CCS y Simulador Proteus para Microcontroladores PICFrom EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICRating: 2.5 out of 5 stars2.5/5 (5)

- Pirometro Utilizado en MedicionDocument1 pagePirometro Utilizado en MediciontavuchoNo ratings yet

- Manual de Instrucciones Control de NivelDocument2 pagesManual de Instrucciones Control de NiveltavuchoNo ratings yet

- Manual Variador Mitsubishi FR-E700Document106 pagesManual Variador Mitsubishi FR-E700tavucho100% (1)

- Manual de Instrucciones Control de NivelDocument2 pagesManual de Instrucciones Control de NiveltavuchoNo ratings yet

- Manual de Instrucciones Control de NivelDocument2 pagesManual de Instrucciones Control de NiveltavuchoNo ratings yet

- Manual de Instrucciones Control de NivelDocument2 pagesManual de Instrucciones Control de NiveltavuchoNo ratings yet

- Pirometro Utilizado en MedicionDocument1 pagePirometro Utilizado en MediciontavuchoNo ratings yet

- Secretos de Sistemas de Encendido ElectronicoDocument42 pagesSecretos de Sistemas de Encendido ElectronicoFerosama95% (22)

- Secretos de Sistemas de Encendido ElectronicoDocument42 pagesSecretos de Sistemas de Encendido ElectronicoFerosama95% (22)

- 80 Adjetivos Comunes para Aprender InglésDocument4 pages80 Adjetivos Comunes para Aprender InglésRicardo Marín Tälero75% (20)

- Errores ComunesDocument34 pagesErrores ComunestavuchoNo ratings yet

- 80 Adjetivos Comunes para Aprender InglésDocument4 pages80 Adjetivos Comunes para Aprender InglésRicardo Marín Tälero75% (20)

- 80 Adjetivos Comunes para Aprender InglésDocument4 pages80 Adjetivos Comunes para Aprender InglésRicardo Marín Tälero75% (20)

- InglesDocument23 pagesInglesMafe BenitezNo ratings yet

- 1100 Acertijos de IngenioDocument153 pages1100 Acertijos de IngeniotavuchoNo ratings yet

- InglesDocument23 pagesInglesMafe BenitezNo ratings yet

- 80 Adjetivos Comunes para Aprender InglésDocument4 pages80 Adjetivos Comunes para Aprender InglésRicardo Marín Tälero75% (20)

- Sumas RestasDocument20 pagesSumas RestascprgraenaNo ratings yet

- 80 Adjetivos Comunes para Aprender InglésDocument4 pages80 Adjetivos Comunes para Aprender InglésRicardo Marín Tälero75% (20)

- 80 Adjetivos Comunes para Aprender InglésDocument4 pages80 Adjetivos Comunes para Aprender InglésRicardo Marín Tälero75% (20)

- Matematicas Basica I PDFDocument35 pagesMatematicas Basica I PDFtavuchoNo ratings yet

- 80 Adjetivos Comunes para Aprender InglésDocument4 pages80 Adjetivos Comunes para Aprender InglésRicardo Marín Tälero75% (20)

- Sumas RestasDocument20 pagesSumas RestascprgraenaNo ratings yet

- 80 Adjetivos Comunes para Aprender InglésDocument4 pages80 Adjetivos Comunes para Aprender InglésRicardo Marín Tälero75% (20)

- Aallen Bradley InstrucDocument12 pagesAallen Bradley InstrucJan AlejandreNo ratings yet

- Curso de Inyeccion ElectronicaDocument58 pagesCurso de Inyeccion ElectronicatavuchoNo ratings yet

- Aallen Bradley InstrucDocument12 pagesAallen Bradley InstrucJan AlejandreNo ratings yet

- Aallen Bradley InstrucDocument12 pagesAallen Bradley InstrucJan AlejandreNo ratings yet

- Inyeccion Electronica de AutosDocument12 pagesInyeccion Electronica de AutostavuchoNo ratings yet

- Programacion de PLCDocument46 pagesProgramacion de PLCtavuchoNo ratings yet

- Sistema de CotasDocument12 pagesSistema de CotasAndré Rossi MartinezNo ratings yet

- Memoria Descriptiva-La MarDocument3 pagesMemoria Descriptiva-La MarnelsonNo ratings yet

- Air 1Document8 pagesAir 1amorsantoNo ratings yet

- FORMATO - DE.ANALISIS de Costos CRHDocument6 pagesFORMATO - DE.ANALISIS de Costos CRHbetsabeNo ratings yet

- Invariantes Arquitectonicas Notas Sobre Una Antropologia Del Habitat - Angelique TrachanaDocument184 pagesInvariantes Arquitectonicas Notas Sobre Una Antropologia Del Habitat - Angelique TrachanaFernanda SaenzNo ratings yet

- Capítulo 3 - 3.6 Diseño de Una Malla de Puesta A TierraDocument11 pagesCapítulo 3 - 3.6 Diseño de Una Malla de Puesta A TierraJairo Gutarra RocaNo ratings yet

- Asesoria Cuatro - Investigación ExplicativaDocument37 pagesAsesoria Cuatro - Investigación Explicativasandra MedinaNo ratings yet

- Ejemplos Confiables Centro CivicoDocument9 pagesEjemplos Confiables Centro CivicoFrancy Marca0% (1)

- Calculo de Estructuras Con Cypecad 2015 Completo PDFDocument474 pagesCalculo de Estructuras Con Cypecad 2015 Completo PDFRaul Bedoya HerediaNo ratings yet

- 20 Tipos de CartusDocument16 pages20 Tipos de CartusWilliam DíazNo ratings yet

- Muro InclinadoDocument22 pagesMuro InclinadoMeli OrellanaNo ratings yet

- Triptico de UniversalDocument2 pagesTriptico de UniversaladrianaNo ratings yet

- Términos de Referencia N Contrato PuenteDocument8 pagesTérminos de Referencia N Contrato PuenteSONIACLEMENTENo ratings yet

- Est1 PDFDocument1 pageEst1 PDFMilitho GueGoNo ratings yet

- Solucion Complementos de Office 2013Document4 pagesSolucion Complementos de Office 2013edwin OviedoNo ratings yet

- Capitel - Anatomia ArtisticaDocument202 pagesCapitel - Anatomia Artisticaluisito5588100% (2)

- Comentarios de Temas y SubtemasDocument1 pageComentarios de Temas y SubtemasFonoteca Buap Isaías Noriega de la VegaNo ratings yet

- Manual Instalación y Configuración Equipos PDFDocument86 pagesManual Instalación y Configuración Equipos PDFJonathan Caicedo UniNo ratings yet

- VIE158 - Memoria DescriptivaDocument14 pagesVIE158 - Memoria Descriptivaandresmtzalv28No ratings yet

- Teleferico de CaracasDocument16 pagesTeleferico de CaracasMilay ColmenaresNo ratings yet

- Arquitectura Moodle 2 - 0Document12 pagesArquitectura Moodle 2 - 0Adelardo Sánchez CanoNo ratings yet

- Impresora Multifuncional Bizhub 367Document4 pagesImpresora Multifuncional Bizhub 367Erik FloresNo ratings yet

- Desniveles Con Cartón para MaquetasDocument15 pagesDesniveles Con Cartón para MaquetasAlonso CanoNo ratings yet

- Análisis Del Proceso Constructivo en El Sistema Aporticado para Mejorar La Calidad de Las Edificación en El Barrio de ShancayanDocument30 pagesAnálisis Del Proceso Constructivo en El Sistema Aporticado para Mejorar La Calidad de Las Edificación en El Barrio de ShancayanPedro Fernando Colonia FuentesNo ratings yet

- Instalacion de Unis Remote ManagerDocument10 pagesInstalacion de Unis Remote Managermaverick_libra3164No ratings yet

- Casa de Los VientosDocument1 pageCasa de Los VientosdamianNo ratings yet

- BABILONIADocument1 pageBABILONIAMarolyn Huaman JulianNo ratings yet

- Cuadro - Comunidades Virtuales - ColaborativoDocument3 pagesCuadro - Comunidades Virtuales - ColaborativoHamida MarhuNo ratings yet

- CS 4-6-2 Desafio Con DynagenDocument4 pagesCS 4-6-2 Desafio Con DynagenMiguel Angel Davelouis CasanaNo ratings yet

- Nuevo Documento de TextoDocument62 pagesNuevo Documento de TextoFredy AlejandroNo ratings yet